1.本发明涉及一种逐次逼近型模数转换器,尤其涉及一种减少电容和开关数量的逐次逼近型模数转换器。

背景技术:

2.逐次逼近型模数转换器(sar adc)是一种中高精度和中等速度的模数转换器,因其低功耗、面积小等优点,常用于移动设备、生物信号处理、医疗设备等场合。

3.saradc模数转换器其原理是采用二进制搜索算法(binary search algorithm),系统结构利用一个dac产生一系列模拟电压值和输入信号电压通过电压比较器进行比较,逐步确定最终的数字编码d[0],d[1],

……

,d[n]。在理想的转换器中,输入电压信号vin等于电容中冗余电压v

residual

与已转换的dac电压v

dac

之和。当最后一次转换完成后,冗余电压v

residual

应为0v,此时输入电压vin等于dac电压v

dac

,说明系统已将输入信号全部转换为了数字信号。

[0004]

但在实际中,由于电容数量过多、开关数量巨大,会导致电容失配、能耗开销过大等问题,最终使得输入信号无法全部被转换,从而造成线性和非线性误差。现常用的模数转换器电路中,为了减少电容数量一般会采用电容分段阵列,即采用桥接电容将原来的电容阵列分成两段,且每段都按照二进制权值赋值于电容。而电容接入不同参考电平也决定了所使用开关数量的多少,在计算能量时,电容本身并无能量消耗,消耗的能量是开关切换时所产生的能耗,所以减少开关数量也可降低系统能耗。现在的设计一般存在如下几个问题:1、传统的电容阵列所需电容数量较多,可引入分段电容技术对电容阵列进行分段,但如何分段最优尚未解决,实际大多根据经验确定;2、采用栅压自举开关在采样时会受到衬底偏置效应的影响而使得导通电阻与输入信号有关,影响线性度,且在传统的结构中一半需要使用2n个栅压自举开关,带来了很大的功耗和面积开销;3、在保证电容阵列精度的同时,要考虑如何减少开关数量。

技术实现要素:

[0005]

发明目的:针对以上问题,本发明提出一种减少电容和开关数量的逐次逼近型模数转换器,有效降低了所需的电容数量,并且节省了开关开销。

[0006]

技术方案:本发明所采用的技术方案是一种减少电容和开关数量的逐次逼近型模数转换器,一种减少电容和开关数量的逐次逼近型模数转换器,包括顺次电连接的dac模块、电压比较器和sar逻辑控制电路,sar逻辑控制电路输出开关控制信号控制dac模块输出,在电压比较器完成比较,所述dac模块包括同相端处理模块和反相端处理模块,所述同相端处理模块包括同相端电容阵列、同相端开关控制电路和同相端采样电路,所述同相端电容阵列被串联的耦合电容分为低电位段电容阵列和高电位段电容阵列,每段电容阵列均是以二进制的权值顺序并联的电容,所述高电位段电容阵列的最高权重位由分裂电容组c9和c9s构成,两个分裂电容组中的并联电容数量相等;除所述分裂电容组以外的同相端高电

位电容阵列的自由点通过同相端开关控制电路选择连接共模电平vcm、同相参考电平vrp、反相参考电平vrn或者同相输入信号v

ip

,所述分裂电容组的自由点通过同相端开关控制电路选择接入同相参考电平vrp、反相参考电平vrn或者同相输入信号v

ip

;所述同相端电容阵列的公共点作为同相端处理模块的输出接电压比较器的同相输入端;反相端处理模块的电路结构与同相端处理模块对称,其输出接入电压比较器的反相输入端。

[0007]

所述高电位段电容阵列还包括一个单位电容cc,对单位电容cc输入采样信号,可代替对低电位段电容的采样,以此节省2

l-1个开关。

[0008]

进一步的,所述电容阵列的总电容数的计算公式为:

[0009][0010]

其中,c

tot

为电容阵列的总电容,cu表示单位电容,l表示低电位段位数,m表示高电位段位数,m l=n,n为逐次逼近型模数转换器的位数,当且仅当m=l时,等号成立。

[0011]

所述共模电平vcm、同相参考电平vrp和反相参考电平vrn的关系式为:vcm=1/2(vrp vrn)。

[0012]

所述逐次逼近型模数转换器为10bit,所述同相端低电位段电容阵列由c1、c2、c3和c4共4个单位电容组组成,同相端高电位段电容阵列由单位电容cc以及c5、c6、c7、c8、c9和c9s共6个电容组组成;所述电容组c1位有1个单位电容,电容组c2位由2个单位电容并联,电容组c3位由4位单位电容并联,电容组c4位由8个单位电容并联;所述电容组c5有1个单位电容,电容组c6由2个单位电容并联,电容组c7由4个单位电容并联,电容组c8由8个单位电容并联,电容组c9由8个单位电容并联,电容组c9s由8个单位电容并联。

[0013]

所述同相端开关控制阵列包括10个pmos管m1~m10,18个nmos管m11~m28;其中,pmos管m1~m10的源极接电平vrp,栅极分别接反馈信号p《1》~p《9》和p《9s》;nmos管m11~m18的源极接共模电平vcm,栅极分别接反馈信号m《1》~m《8》;nmos管m19~m28的源极接反相参考电平vrn,栅极分别接反馈信号n《1》~n《9》和n《9s》。

[0014]

pmos管m1的漏极、nmos管m11的漏极以及nmos管m19的漏极相接形成节点s

p1

,pmos管m2的漏极、nmos管m12的漏极以及nmos管m20的漏极相接形成节点s

p2

,pmos管m3的漏极、nmos管m13的漏极以及nmos管m21的漏极相接形成节点s

p3

;pmos管m4的漏极、nmos管m14的漏极以及nmos管m22的漏极相接形成节点s

p4

,pmos管m5的漏极、nmos管m15的漏极以及nmos管m23的漏极相接形成节点s

p5

,pmos管m6的漏极、nmos管m16的漏极以及nmos管m24的漏极相接形成节点s

p6

,pmos管m7的漏极、nmos管m17的漏极以及nmos管m25的漏极相接形成节点s

p7

,pmos管m8的漏极、nmos管m18的漏极以及nmos管m26的漏极相接形成节点s

p8

,pmos管m9的漏极和nmos管m27的漏极相接形成节点s

p9

;pmos管m10的漏极和nmos管m28的漏极相接形成节点s

p9s

。

[0015]

所述同相端采样电路包括7个pmos管m1、m5、m6、m9、m10、m13和m14,8个nmos管m2、m3、m4、m7、m8、m11、m12和m15。其中,pmos管m1的源极接正相输入信号v

ip

,栅极接时钟信号nc_2,漏极与nmos管m2的漏极连接,nmos管m2的栅极接时钟信号nc_2,源极接入共模电平vcm,nmos管m3源极接正相输入信号v

ip

,栅极接入时钟信号c_2,漏极与m1的漏极以及m2的漏极相连,此节点还与电容阵列中耦合电容cs的下极板连接;nmos管m4的漏极接正相输入信号v

ip

,栅极接入时钟信号c_2,源极与pmos管m5的源极连接,同时与开关控制阵列节点s

p5

连接,pmos管m5的漏极接正相输入信号v

ip

,栅极接时钟信号nc_2;pmos管m6源极接正相输入信

号v

ip

,栅极接时钟信号nc_2,漏极与nmos管m7的漏极相连,同时接开关控制阵列中的节点s

p6

;nmos管m7源极接正相输入信号v

ip

,栅极接时钟信号c_2;nmos管m8的漏极接正相输入信号v

ip

,栅极接时钟信号c_2,源极与pmos管m9的源极相连,同时与开关控制阵列的节点s

p7

相连,pmos管m9的漏极接正相输入信号v

ip

,栅极接入时钟信号nc_2;pmos管m10源极接入正相输入信号v

ip

,栅极接时钟信号nc_2,漏极同nmos管m11的漏极相连,同时接开关控制阵列节点s

p8

,nmos管m11的源极接正相输入信号v

ip

,栅极接时钟信号c_2;nmos管m12的漏极接正相输入信号v

ip

,栅极接时钟信号c_2,源极与pmos管m13的源极相连,同时接开关控制阵列的节点s

p9s

,pmos管m13的漏极接正相输入信号v

ip

,栅极接时钟信号nc_2;pmos管m14源极接正相输入信号v

ip

,栅极接时钟信号nc_2,漏极同nmos管m15相连,同时接节点s

p9

,nmos管m15源极接正相输入信号v

ip

,栅极接时钟信号c_2。

[0016]

有益效果:相比现有技术,本发明具有以下优点:1、电容阵列采用分段电容结构,并利用电荷转移,使第一次比较无需进行参考建立这一过程,可节省一位电容组开销;提出最少电容数量的分段计算方法,通过计算得出分段电容可使用的最少电容数量,使得电容阵列的电容数量不再以指数形式增长,有效降低了所需的电容数量,本发明与传统电容阵列相比可节省近96%的电容数,与其他形式的分段电容结构相比可节省37%~90%的电容数量;同时引入共模电平vcm作为基准电压,极大地减少了开关在转换过程中的动态能耗;2、没有采用能耗大、面积大的栅压自举开关,使用更为简单的cmos互补开关作为开关,进一步在高电位段增加一个单位电容,并使其输入采样信号,从而使低电位段电容无需采样,进而节省了开关开销;3、通过对高电位段最高权重组电容进行分裂,使其在电荷转移阶段无需通过开关接入共模电平vcm,由此可以节省近20%的开关开销。

附图说明

[0017]

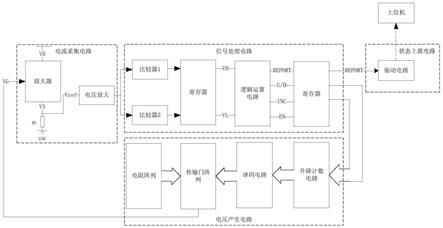

图1是本发明所述的10位sar adc的电路图;

[0018]

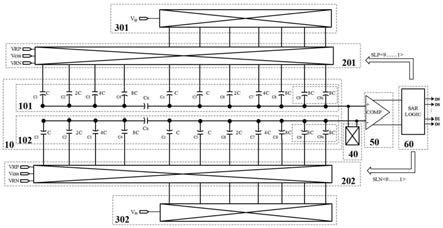

图2是本发明所述的10位sar adc正相端处理模块的电容阵列、开关控制电路以及采样开关电路的连接图(反相端处理模块同正相端处理模块对称);

[0019]

图3是本发明所述的n位sar adc的分段电容结构分析图;

[0020]

图4是本发明所述的n位sar adc的分段电容结构等效电路图,其中(a)为高电位段电容阵列的等效电路图,(b)为低电位段电容阵列的等效电路图。

具体实施方式

[0021]

下面结合附图和实施例对本发明的技术方案作进一步的说明。

[0022]

以10bit的逐次逼近型模数转换器为例,本发明所述的一种减少电容和开关数量的逐次逼近型模数转换器的电路图如图1所示。该结构包括电容阵列10、开关控制电路、采样电路、vcm采样电路40、电压比较器50和sar逻辑控制电路60。其中,电容阵列10又分为正相端电容阵列101和反相端电容阵列102;开关控制电路包括正相端开关控制电路201和反相端开关控制电路202;采样电路包括正相端采样电路301和反相端采样电路302。

[0023]

正相端电容阵列101通过正相端开关控制电路201以及正相端采样电路301可接入正相输入信号v

ip

,反相端电容阵列102通过反相端开关控制电路202以及反相端采样电路302可接入反相输入信号v

in

,正相端电容阵列101与电压比较器50的正相输入端相连,反相

端电容阵列102同电压比较器50的反相输入端相连;电压比较器50的输出端与sar逻辑控制电路60的输入端相连;sar逻辑控制电路60的输出端输出正相开关控制信号slp和反相开关控制信号sln,正相端开关控制信号slp接入正相端开关控制电路201,反相端开关控制信号sln接入反相端开关控制电路202。开关控制电路组成双端信号输入,电容阵列10双端输入输出,所用信号为差分输入信号。其中共模电平vcm取值为:vcm=1/2(vrp vrn),vrp为正相参考电平、vrn为反相参考电平。vcm采样电路40是通过采样开关接入共模电平vcm到电容阵列10的自由点,采样结束后开关断开。

[0024]

正相端电容阵列101包括正相端低电位段电容阵列、耦合电容cs和正相端高电位段电容阵列;其中,正相端低电位段由c1、c2、c3和c4共4个单位电容组组成,正相端高电位段由cc、c5、c6、c7、c8、c9和c9s共7个单位电容组组成。其中,正相端高电位段的最高权重位由分裂电容组c9和c9s构成。耦合电容cs将低电位段和高电位段电容阵列串联,每段电容阵列内部均为电容并联。每段电容阵列均以二进制的权值顺序排列,正相端低电位段电容阵列中的c1有1个单位电容,c2由2个单位电容并联,c3由4个单位电容并联,c4由8个单位电容并联,共需15个单位电容;正相端高电位段电容阵列中cc有1个单位电容,c5有1个单位电容,c6由2个单位电容并联,c7由4个单位电容并联,c8由8个单位电容并联,c9由8个单位电容并联,c9s由8个单位电容并联,共需32个单位电容;耦合电容cs的值等于单位电容值,所以,正相端电容阵列的总电容数为48个单位电容。

[0025]

正相端低电位电容阵列中4个单位电容组的顶板同高电位电容阵列中7个单位电容组的顶板通过耦合电容cs串联形成公共点,并与电压比较器50的正相输入端连接,同时通过vcm采样电路40连接共模电平vcm;正相端高电位段电容阵列(除最高权重电容组c9和电容组c9s)的底板(自由点)通过正相端开关控制电路201可连接共模电平vcm、正相参考电平vrp、反相参考电平vrn或者接入正相输入信号v

ip

,最高位权重电容组c9和c9s的底板通过正相端开关控制电路201可接入正相参考电平vrp、反相参考电平vrn或者正相输入信号v

ip

;正相端低电位电容阵列四个单位电容组的底板(自由点)通过正相端开关控制电路201可连接共模电平vcm、正相参考电平vrp、反相参考电平vrn。

[0026]

参照图2,所述正相端开关控制阵列201包括10个pmos管m1~m10,18个nmos管m11~m28。

[0027]

其中,pmos管m1~m10的源极接电平vrp,栅极分别接反馈信号p《i》~p《9》和p<9s》;nmos管m11~m18的源极接共模电平vcm,栅极分别接反馈信号m《1》~m《8》;nmos管m19~m28的源极接反相参考电平vrn,栅极分别接反馈信号n《1》~n《9》和n<9s》;pmos管m1的漏极、nmos管m11的漏极以及nmos管m19的漏极相接形成节点s

p1

,pmos管m2的漏极、nmos管m12的漏极以及nmos管m20的漏极相接形成节点s

p2

,pmos管m3的漏极、nmos管m13的漏极以及nmos管m21的漏极相接形成节点s

p3

;pmos管m4的漏极、nmos管m14的漏极以及nmos管m22的漏极相接形成节点s

p4

,pmos管m5的漏极、nmos管m15的漏极以及nmos管m23的漏极相接形成节点s

p5

,pmos管m6的漏极、nmos管m16的漏极以及nmos管m24的漏极相接形成节点s

p6

,pmos管m7的漏极、nmos管m17的漏极以及nmos管m25的漏极相接形成节点s

p7

,pmos管m8的漏极、nmos管m18的漏极以及nmos管m26的漏极相接形成节点s

p8

,pmos管m9的漏极和nmos管m27的漏极相接形成节点s

p9

;pmos管m10的漏极和nmos管m28的漏极相接形成节点s

p9s

。

[0028]

pmos管m1的宽长为3.7um/550nm,pmos管m2为4.6um/550nm,pmos管m3为9.2um/

550nm,pmos管m4为13.4um/550nm,pmos管m5为3.7um/550nm,pmos管m6为4.6um/550nm,pmos管m7位9.2um/550nm,pmos管m8、m9和m10均为18.4um/nm;nmos管m11为1.7um/500nm,nmos管m12为2.2um/500nm,nmos管m13为4.2um/500nm,nmos管m14位8.4um/500nm,nmos管m15为1.7um/500nm,nmos管m16为2.2um/500nm,nmos管m17为4.2um/500nm,nmos管m18为8.4um/500nm;nmos管m19和m23均为1.1um/500nm,nmos管m20和m24均为1.4um/50nm,nmos管m21和m25均为2.8um/500nm,nmos管m22、m26、m27和m28均为5.6um/500nm。

[0029]

正相端采样电路301包括7个pmos管m1、m5、m6、m9、m10、m13和m14,8个nmos管m2、m3、m4、m7、m8、m11、m12和m15。

[0030]

其中,pmos管m1的源极接正相输入信号v

ip

,栅极接时钟信号nc_2,漏极与nmos管m2的漏极连接,nmos管m2的栅极接时钟信号nc_2,源极接入共模电平vcm,nmos管m3源极接正相输入信号v

ip

,栅极接入时钟信号c_2,漏极与m1的漏极以及m2的漏极相连,此节点还与电容阵列中耦合电容cs的下极板连接;nmos管m4的漏极接正相输入信号v

ip

,栅极接入时钟信号c_2,源极与pmos管m5的源极连接,同时与开关控制阵列节点s

p5

连接,pmos管m5的漏极接正相输入信号v

ip

,栅极接时钟信号nc_2;pmos管m6源极接正相输入信号v

ip

,栅极接时钟信号nc_2,漏极与nmos管m7的漏极相连,同时接开关控制阵列中的节点s

p6

;nmos管m7源极接正相输入信号v

ip

,栅极接时钟信号c_2;nmos管m8的漏极接正相输入信号v

ip

,栅极接时钟信号c_2,源极与pmos管m9的源极相连,同时与开关控制阵列的节点s

p7

相连,pmos管m9的漏极接正相输入信号v

ip

,栅极接入时钟信号nc_2;pmos管m10源极接入正相输入信号v

ip

,栅极接时钟信号nc_2,漏极同nmos管m11的漏极相连,同时接开关控制阵列节点s

p8

,nmos管m11的源极接正相输入信号v

ip

,栅极接时钟信号c_2;nmos管m12的漏极接正相输入信号v

ip

,栅极接时钟信号c_2,源极与pmos管m13的源极相连,同时接开关控制阵列的节点s

p9s

,pmos管m13的漏极接正相输入信号v

ip

,栅极接时钟信号nc_2;pmos管m14源极接正相输入信号v

ip

,栅极接时钟信号nc_2,漏极同nmos管m15相连,同时接节点s

p9

,nmos管m15源极接正相输入信号v

ip

,栅极接时钟信号c_2。

[0031]

pmos管m1的宽长比为3.7um/550nm,nmos管m2为1.7um/500nm,nmos管m3和m4均为1.1um/500nm,pmos管m5为3.7um/500nm,pmos管m6为5.5um /550nm,nmos管m7为1.7um/500nm,nmos管m8为2.8um/500nm,pmos管m9为9.2um/550nm,pmos管m10、m13和m14均为18.4um/550nm,nmos管m11、m12和m15均为5.6um/500nm。

[0032]

参照图2,为本实施例所使用的电容阵列和开关的具体连接图。其中,根据传统结构,对于nbit的saradc需要2n个单位电容,按照本实施例设计的10bit,共需要1024个单位电容,电容数量过多,实现不易。所以引入分段电容结构,通过耦合电容cs将电容阵列分成两个小阵列。提出最少电容数量的分段结构计算方法如下,即可得到单位电容数量最少的sar adc结构,并在此基础上结合其他方法能进一步减少电容数量。

[0033]

参照图3,是经典的分段结构电容阵列,若在点

①

和点

②

处分别输入一个幅度为v的阶跃信号,计算点v0处的输出信号改变量,通过简化电路得图4(a)和图4(b),有:

[0034]v01

=kcu(cs c

l

)v/x

ꢀꢀꢀ

(1)

[0035]v02

=(2

l-1

cscu)v/x

ꢀꢀꢀ

(2)

[0036]

其中,cu表示单位电容,k表示有k个cu,cs是耦合电容,c

l

表示低电位段总电容数,cm为高电位段总电容数,l表示低电位段位数,m表示高电位段位数,cd为接地电容,节点v0、

点

①

和点

②

;具体的:c

l

=(2

l-1)cu c

d2

,cm=(2

m-1)kcu c

d1

,x=cm(cs c

l

) csc

l

,m l=n。为了保持阵列的正确权重,确保adc线性,应有v

01

=2v

02

,可得:

[0037]

k(cs cu)=2

l

cs

ꢀꢀ

(3)

[0038]

进一步整理可得:

[0039][0040]

由c

l

总电容可知:

[0041]cl

≥(2

l-1)cuꢀꢀꢀ

(5)

[0042]

结合式(4)和式(5),令k=1,可得:

[0043]cl

=(2

l-1)cuꢀꢀꢀ

(6)

[0044]

cs=cu,c

d2

=0,c

d1

=cuꢀꢀꢀ

(7)

[0045]

如此,结合式(7)和(8),分段结构电容的总电容数为:

[0046][0047]

式(8)中,当且仅当m=l时,等号才成立。即对于n位的sar adc,当高电位数和低电位数相等时,可得到最少电容数,并且能保持adc的线性要求。结合底板采样中电荷转移阶段,将电荷转移到电容项板(公共点)时,电荷可直接输入到比较器的两个输入端,即可进行第一次比较,从而节省一位电容组,所以m或l可以在原来的基础上再少一,即总电容数变为c

tot

=2

m-1

2

l

或c

tot

=2m 2

l-1

。本实施例共需96个单位电容,与传统电容阵列相比可节省近96%的电容数,与其他形式的分段电容结构相比可节省37%~90%的电容数量。

[0048]

在本实施例中,通过在高电位段增加一个电容cc,其数值等于单位电容,并对其输入采样信号,则低电位段电容无需采样,可节省2

l-1个开关;此外,高电位段的最高权重组通过分裂电容组以得到共模电压vcm,而不是直接通过接入vcm电平,所以最高权重组位可以节省2m个vcm开关;所以在本实施例中,一共只需要154个开关,比原结构节省了近20%的开关数量。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。