具有动态范围增强器的模数转换器

背景技术:

1.一些应用处理音频信号。例如,语音支持应用包括接收并处理音频模拟输入信号(例如,语音信号)的信号链。信号链可以包括放大器、模数转换器(adc)、滤波器等。具有远场拾音的语音支持应用的增长得益于较大的动态范围。遗憾的是,信号路径的信噪比(snr)限制了动态范围。

技术实现要素:

2.在一个示例中,一种电路包括可编程增益放大器(pga),pga具有pga输出。该电路还包括具有耦合至pga输出的输入的δ

‑

σ调制器。该电路还包括数字滤波器和动态范围增强器(dre)电路。数字滤波器耦合至δ

‑

σ调制器输出。dre电路耦合至δ

‑

σ调制器输出和pga。dre电路被配置为监测δ

‑

σ调制器输出的信号电平。响应于信号电平小于dre阈值,dre电路被配置为将pga编程为大于单位增益的增益水平并且致使数字滤波器实现与待编程到pga中的增益水平相同幅值的衰减。

附图说明

3.为了对各种示例进行详细说明,现在将参考附图,在附图中:

4.图1示出了具有动态范围增强的adc的示例性示意图。

5.图2和图3例示了来自δ

‑

σ调制器的输出信号与adc的可编程增益设置之间的关系。

6.图4示出了在启用和未启用动态范围增强的情况下对通过adc的信号路径的snr的影响。

7.图5示出了图1的具有动态范围增强的adc的实施的示例。

8.图6示出了图1的adc的实施的另一示例。

具体实施方式

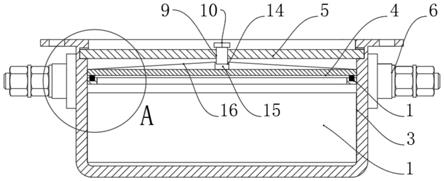

9.图1示出了可用于例如处理来自音频源(例如,麦克风)的电信号的adc100的示例性示意图。在该示例中,adc 100包括可编程增益放大器(pga)102、δ

‑

σ调制器104、级联积分梳状滤波器(cic)抽取器106、抽取滤波器112、可编程高通滤波器114、增益比例系数粗调116、增益比例系数细调118、可编程双二次滤波器(biquads)120、数字混频器122、音量控制124和动态范围增强(dre)电路110。抽取滤波器112、可编程高通滤波器114、增益比例系数粗调116、增益比例系数细调118、可编程双二次滤波器120、数字混频器122、音量控制124均包括数字信号链。pga 102包括接收待由adc 100转换至数字信号的模拟信号(例如,音频信号)的输入。pga 102的增益是可编程的。在一项实施中,例如,pga 102的增益可以被编程为处于单位增益(零db)以0.5db的增量至60db的上限增益设置的范围内(即,0db、0.5db、1db、1.5db等)。

10.该示例中的模数转换过程使用了δ

‑

σ调制器104。δ

‑

σ调制器104的输出被提供

至cic抽取器106的输入。cic抽取器106降低δ

‑

σ调制器104的数据输出率,从而减小后续数字逻辑的功率消耗。来自cic抽取器106的输出信号用x(n)表示。信号x(n)被dre电路110修改并被提供至抽取滤波器112,该抽取滤波器继续使过采样数据率降低至输出信号的期望奈奎斯特(nyquist)抽样率。可编程高通滤波器114包括去除信号的dc分量的数字滤波器。根据由增益比例系数粗调116和增益比例系数细调118实现的增益设置修改来自可编程高通滤波器114的滤波信号。总体增益比例系数补偿了模拟输入信号和/或麦克风之间的任何增益偏差。可编程双二次滤波器120向用户提供定制的频域整形。数字混频器122通过将同一输入馈送至多个信道并且同等地对它们求和,提供将多个信道组合成单个输出或改善输入信号的信噪比(snr)的能力。最终,音量控制124提供对输出信号电平的精细控制。pga 102、δ

‑

σ调制器104、cic抽取器106、抽取滤波器112、滤波器114、增益比例系数调节116和118、可编程双二次滤波器120、数字混频器122和音量控制124均包括通过adc 100的模拟信号的信号路径,以将模拟信号转换成数字信号。

11.dre电路110包括cic预处理器130、dre高通滤波器132、绝对值生成器134、db转换器136、增益计算器138、电平计算器139、平均器140、群延迟补偿器142和对数至线性转换器144。dre电路110通过将针对阈值电平以下的信号电平(x(n))的pga 102的增益增加并且然后使滤波信号数字衰减与pga 102的增益相同的幅值,来提高δ

‑

σ调制器的动态范围。例如,如果pga 102待由dre电路110编程﹢24db的增益,则﹣24db的衰减将被施加至数字滤波信号。结果,信号链将会使单位增益实现为其输入与输出之间。在一项实施中,信号链的增益可以为单位增益以外的增益(例如,大于单位增益),并且无论总体增益为单位增益或是不同的增益系数,本文所述的增益增加和后续的衰减都将保持总的信道增益不变。通过针对低电平输入信号增加pga 102的增益,信号电平被升高至δ

‑

σ调制器104的输入参考噪音电平之上。由此,δ

‑

σ调制器104将会以其他方式将低电平输入信号转换为具有较低噪声的数字码,这允许使用较低性能(例如,较高噪声)、较低成本的δ

‑

σ调制器104,同时保持更加昂贵的δ

‑

σ调制器的高动态范围。

12.dre电路110的cic预处理器130接收x(n)作为输入信号。在一项示例性实施中,cic预处理器130对若干cic输出样本取平均,并且去除先前施加的pga增益。cic预处理器130在至少一个示例中实现以下逻辑:

[0013][0014]

其中,invpgaagain是逆pga增益,并且n是一起取平均的cic输出的数量。这降低了dre的功率消耗并且由输入电平的估计消平任何快速改变的信号。

[0015]

来自cic预处理器130的处理信号被提供至dre高通滤波器132,该dre高通滤波器去除dc偏差以对输入信号电平进行精确计算。在一个示例中,dre高通滤波器132由以下给出:

[0016]

h(n)=b1g(n) b2g(n

‑

1)

‑

a2h(n

‑

1)

ꢀꢀ

(2)

[0017]

其中,h(n)是来自滤波器132的当前输出值,b1、b2和a2是滤波器系数,g(n)是到滤波器的当前输入值,g(n

‑

1)是到滤波器132的前一输入值,并且h(n

‑

1)是来自滤波器132的前一输出值。在一个示例中,dre高通滤波器132具有4hz的3

‑

db拐角。

[0018]

来自dre高通滤波器132的滤波输出h(n)被提供至绝对值生成器134,该绝对值生成器输出滤波器输出的绝对值。db转换器136将来自绝对值生成器134的输出从线性值转换

至db值h

db

(n)。db转换器136的输出h

db

(n)是:

[0019]

h

db

(n)=20*log

10

(|h(n)|)

ꢀꢀ

(3)

[0020]

在一个示例中,db转换器136包括查找表(lut),该lut将输入信号h(n)映射至输出db值h

db

(n)以降低db转换的功率消耗。db转换器136的输出被提供至增益计算器138。

[0021]

在该示例中,利用用于处理输入值h

db

(n)的参数对增益计算器138进行编程以生成输出值y

db

(n)。由增益计算器138使用的参数包括例如攻击值150、max gain(最大增益)值151、保持值152、阈值值153和释放值154。在一个示例中,增益计算器138计算y

db

(n)如下:

[0022][0023]

当输入值大于阈值时,增益计算器的输出值y

db

(n)因而等于输入值h

db

(n),意味着应将pga 102编程为单位增益(0db)。如果输入值h

db

(n)小于阈值但又大于阈值减去编程的max gain值(maxgain),则应使来自增益计算器138的输出信号电平保持在阈值的值。如果输入低于阈值

‑

maxgain,则增益计算器的输出将被计算为h

db

(n) maxgain。

[0024]

来自增益计算器138的计算输出y

db

(n)被提供至电平计算器139,该电平计算器计算:

[0025]

y

l

(n)=h

db

(n)

‑

y

db

(n)

ꢀꢀ

(5)

[0026]

负值y

l

(n)是应是为pga 102设置的增益值。

[0027]

来自电平计算器130的输出y

l

(n)被提供至平均器140,该平均器实现多种平滑化技术中的任一种以避免pga的输出信号电平中的干扰(例如,突然断连)。平均器140的输出用于为pga 103编程增益设置。在一项实施中,平均器140实现平滑解耦平均化技术(smooth decoupled averaging technique),该技术在到平均器140的输入大于阈值并不断增加的情况下使用攻击值150,或者在到平均器140的输入相对较低的情况下使用释放值154。攻击率可以不同于释放率。平滑解耦技术的一项实施如下:

[0028]

z

g

(n)=release*z

g

(n

‑

1) (1

‑

release)*y

l

(n)

ꢀꢀ

(6)

[0029][0030]

公式(6)和公式(7)将攻击和释放之间变化期间的输出信号的断连和失真最小化。attack(攻击)和release(释放)可以是相同值或不同值。实际上,攻击率比释放率小(并且有时候显著更小)以防止信号在输入信号快速增大时在δ

‑

σ调制器中缩剪。releasehold

(释放保持)值、attackhold(攻击保持)值和滞后(hysteresis)值防止在输入信号不断从高电平切换至低电平(或者反之亦然)时输出信号的伪影。释放计数(releasecount)是攻击后出现的连续释放次数。类似地,攻击计数(attackcount)是释放后出现的连续攻击次数。当攻击紧接释放或者释放紧接攻击时,攻击计数和释放计数被清零。滞后是在算法不响应改变时信号电平从前一状态围绕阈值的改变量。这允许输入信号跨阈值电平来回交叉,而不会导致由于dre增益开关的不断切换引起的输出失真。

[0031]

在其他实施中,平均器140实现加权指数移动平均(wema)或平滑分枝。wema的示例性实施包括将输出z

l

(n)值计算为以下的平均器:

[0032]

z

l

(n)=release*z

g

(n

‑

1) (1

‑

attack)*y

l

(n)

ꢀꢀ

(8)

[0033]

平滑分枝的示例性实施包括将z

l

(n)计算为以下的平均器140:

[0034][0035]

其中,以类似于平滑解耦技术的方式定义滞后和释放计数。

[0036]

如上所述,能够操作dre电路110以针对低于阈值的信号电平(x(n))增加pga 102的增益,并且致使由数字滤波器实现对应量的衰减,以使pga 102的增益增加和数字滤波器中的衰减的净效果互相抵消,并且由adc 100的信号链实现的净增益为0db。响应于信号y

db

(n)高于阈值,pga 102被设置为单位增益。

[0037]

图2示出到增益计算器138的输入(h(db))与被计算为编程到pga102中的增益设置以及被编程到数字滤波器中的对应衰减之间的关系。在高于阈值(threshold)153的输入信号电平处,pga 102的增益被设置为单位增益(0db)。然而,在低于阈值153的输入信号电平处,到pga 102的增益随着输入信号电平减小而增加。增益随着输入信号减小而增加,直至增益设置达到编程的max gain值151。在输入信号进一步减小时,pga 102的增益设置保持在max gain 151。图2还示出逆衰减被施加于数字后端。因而,在大于阈值153的信号电平处,单位增益被施加至数字后端,而对于低于阈值153并且不断增大的输入信号,衰减被施加至数字后端,以抗衡被编程到pga102中的增益设置,从而保持通过整个信号链的单位增益。

[0038]

图3示出针对h

db

(n)的范围被编程到pga 102中的增益的效果。对于高于阈值的h

db

(n),单位增益被编程到pga 102中,并且因而pga的输出追随其输入(即,pga输出信号电平等于输入信号电平)。对于低于阈值的h

db

(n),pga的增益被增加至单位增益以上以使pga输出保持在等于阈值的恒定电平,直至达到max gain。

[0039]

回头参考图1,由平均器142向pga 102提供的增益设置还被提供至群延迟补偿器142。群延迟补偿器142包括一个或更多个延迟元件,以延迟向数字后端施加对应的衰减值,从而导致通过信号链的延迟,信号链包括pga 102、δ

‑

σ调制器104和cic抽取器106以及针对每个信道的dre的处理元件。群延迟补偿器因此致使将逆衰减施加到数字后端中,以与由pga 102、δ

‑

σ调制器104和cic抽取器106的输出施加的采样一致。来自群延迟补偿器142

的延迟衰减值被提供至对数至线性转换器144,该对数至线性转换器将衰减db值转换至被施加至dre数字增益元件146的线性值。在一个示例中,对数至线性转换器144包括查找表,该查找表将db衰减值映射至对应的线性值以降低系统的功率消耗。

[0040]

在图1中,dre信号电平估计出现在δ

‑

σ调制器106与数字滤波器之间。在其他实施中,dre电路110可以耦合至数字滤波器的输出(例如,抽取滤波器112的输出)。

[0041]

图4提供了例示dre电路110的益处的示例。图4示出了麦克风402、pga 404、δ

‑

σ制器406和数字滤波器408。跨越附图顶部的值集合410、412、414、416、418和420表示沿信号链的各个点处的snr、噪声等的示例值。如410的示例所示,麦克风402具有70db的snr、相对于2vrms的均方根电压的114db的动态范围、和4微伏rms(4μvrms)的输出噪声值。值412例示:pga 404具有相对于2vrms的12db的snr,针对0db的增益设置,并且具有2μvrms的输入参考噪声值。pga 414的输出处的均方根噪声在404处被示出为4.47μvrms,并且为4μvrms麦克风输出噪声和2μvrms输入参考噪声的均方根。在该示例中,δ

‑

σ调制器406相对于2vrms具有108db的snr值,并且增加7.96μvrms的噪声。pga的输出4.47vrms和δ

‑

σ调制器的7.96μvrms的均方根在418处被计算为9.13μvrms。附图标号420示出:最终输出噪声因而为9.13μvrms。因此,由于pga 404、δ

‑

σ调制器406和数字滤波器408的信号路径引起的动态范围劣化为20xlog(9.13μvrms/4μvrms)=7.17db。由此,若是没有得益于dre电路110的话,adc的动态范围将为114db

‑

7.17db=106.83db。

[0042]

如图4所示,dre电路110基于来自δ

‑

σ调制器406的输出信号调节pga 404的增益。底部值集合430、432、434、436和438例示了dre电路110的效果。在该示例中对增益的调节在430处被示出为﹢24db的增益设置。在412处,pga 404被设置0db的增益,但是在430处,由于δ

‑

σ调制器输出低于阈值,所以pga的增益被设置为﹢24db。数字滤波器408被设置针对如438处所示的﹣24db的对应衰减。pga的输入参考噪声仍为2μvrms(430),但是pga 404的输出处的均方根噪声在432处被示出为70.88μvrms,其为4μvrms麦克风输出噪声和2μvrms pga输入参考噪声的均方根,施加的增益为24db。如434处所示,δ

‑

σ调制器406的噪声相同,为7.96μvrms。因而,δ

‑

σ调制器406的输出处的组合均方根噪声为71.31μvrms,如434处所示。附图标号438示出:在通过数字滤波器408施加24db的衰减之后,最终的输出噪声为4.50μvrms。因而,由于pga 404、δ

‑

σ调制器406和数字滤波器408的信号路径引起的动态范围劣化为20xlog(4.50μvrms/4μvrms)=1.02db。由此,得益于dre电路110,adc的动态范围将为114db

‑

1.02db=112.98db,这一动态范围显著高于没有dre电路110的情况下将得到的106.83db。

[0043]

在这些示例中,对pga 102的增益的修改均基于输入信号的幅值。如上文所述,输入信号的rms幅值被确定并用于设置pga的增益。在另一示例中,输入信号的平均值可以被确定并用于设置pga的增益。在又一示例中,输入信号的峰值可以被确定并用于设置pga的增益。在上述示例中基于δ

‑

σ调制器406的输出确定输入信号电平。在另一示例中,可以使用来自数字滤波器408的输出信号确定信号电平。更进一步地,在图1和图4中示出基于δ

‑

σ调制器的adc。在其他实施中,使用除基于δ

‑

σ调制器的架构之外的adc。例如,可以使用基于逐次逼近寄存器(sar)的adc。

[0044]

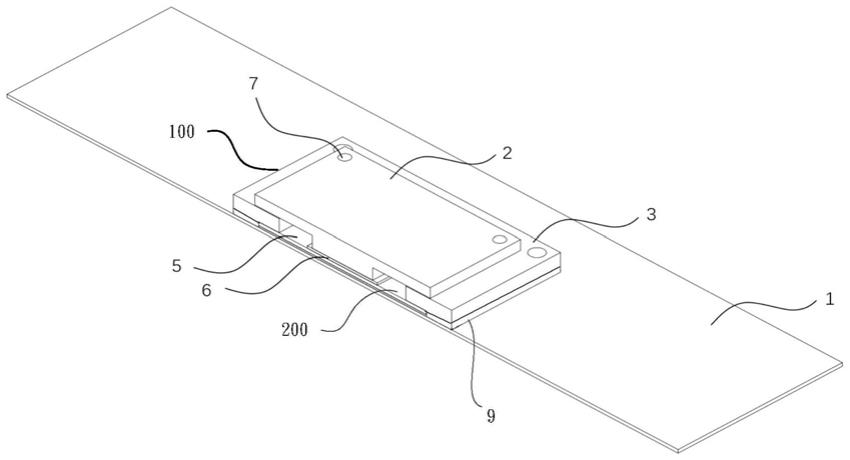

图5将图1的adc 100的例示性实施示出为adc 500。该示例中的adc 500提供多个输入信道(模拟输入1、模拟输入2、模拟输入3、

…

、模拟输入n)。为每个模拟输入信道提供了

pga 102、基于δ

‑

σ调制器的adc 104和cic抽取器106。在该示例中,n个输入信道的pga 102、基于δ

‑

σ调制器的adc 104和cic抽取器106耦合至并共享包括db转换器136、群延迟补偿器142、对数至线性转换器144、处理器508和存储装置510等所示其他部件。存储装置510包括任何合适类型的固态存储装置,诸如易失性存储器(例如,随机存取存储器)或非易失性存储装置(例如,只读存储器)。在一项实施中,处理器为数字信号处理器(dsp)。在执行指令512时,处理器508执行cic预处理器130、dre高通滤波器132、绝对值生成器134、增益计算器138、电平计算器139、平均器140、dre数字增益146、抽取滤波器112、可编程高通滤波器114、增益比例系数粗调116、增益比例系数细调118、可编程双二次滤波器120、数字混频器122和音量控制124的功能。

[0045]

图6示出包含四个adc信道—信道1至信道4的集成电路(ic)600的示例性实施。每个adc信道包括耦合至δ

‑

σ调制器adc 604的pga 602。δ

‑

σ调制器adc 604耦合至数字电路610,该数字电路包括上述dre电路110以及数字滤波器、双二次滤波器等。串行接口620耦合至数字电路610,数字输出代码可以通过该数字电路被提供至外部逻辑。包括控制接口630,可以通过该控制接口将参数attack 150、max gain 151、hold(保持)152和threshold(阈值)154编程到ic中并存储在控制接口630内的寄存器或其他类型的存储元件或ic 600内的其他地方。

[0046]

在本说明书中,术语“耦合(couple或couples)”意指间接或直接的有线连接或无线连接。因而,如果第一装置耦合至第二装置,则该连接可以通过直接连接或通过经由其他装置和连接的间接连接。叙述“基于”意指“至少部分地基于”。因此,如果x基于y,则x可以为y与任何数量的其他因素的函数。可以对所述实施方案作出修改,并且在权利要求的范围内,其他实施方案是可能的。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。