应用于数字开关电源的混合型dpwm电路

技术领域

1.本发明涉及混合信号集成电路领域,特别涉及数字开关电源与工业控制系统,广泛应用在测量、通信、功率控制与变换等许多领域中,对被控系统进行精确的脉宽调制。

背景技术:

2.开关电源是工作在高频开关状态下的供电装置,具有效率高、损耗小、发热低的特点,现已在工业自动化控制、照明、通讯设备、电子数码产品等领域广泛应用。现阶段开关电源普遍采用传统的模拟控制方式,然而模拟电源存在着非线性、误差、漂移、老化等问题,且随着电力电子技术和控制技术的不断发展,为进一步提高开关电源性能并丰富开关电源的控制方式,数字开关电源已成为新的研究热点。

3.随着数字开关电源在电源管理领域中飞速发展,数字dc-dc已逐渐成为了学术界和工业界的热点。与模拟电源相比,数字电源在效率、建立性和移植性等方面具有优势,因此数字电源广受工业界的青睐。

4.虽然数字控制在电源领域有着明显的优势,但目前仍处于研究阶段,尚有很多问题亟待解决。而数字脉宽调制器(dpwm,digital pulse width modulation)是数字开关电源中最重要的模块之一,用于提供数字控制反馈环路的输出,因此dpwm的性能直接影响着数字控制部分的性能。随着开关频率的不断提高,如何解决dpwm分辨率与时钟频率之间的矛盾成为数字控制电源的主要研究热点之一。开关电源输出电压的精度越高,要求dpwm的分辨率就越高,所需系统时钟频率也随之提高,这样必将导致系统功耗剧增,引发散热、系统效率降低等一系列的问题。在满足输出电压精度的同时降低系统时钟频率,是小功率高频数字电源所面临的挑战。因此,高频率高分辨率的dpwm是高性能数字开关电源设计的关键。

技术实现要素:

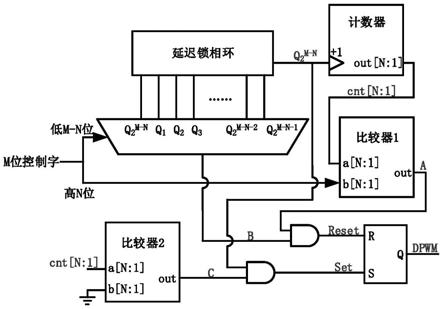

5.为克服现有技术的不足,本发明旨在提出一种应用于数字开关电源的混合型dpwm电路结构,实现高频率、高线性度、高分辨率的数字脉宽调制(dpwm)。为此,本发明采取的技术方案是,应用于数字开关电源的混合型dpwm电路,包括延迟锁相环、多路选择器、计数器、比较器、rs触发器,外部输入m位占空比控制字,将m位控制字拆分为高n位和低m-n位,延迟锁相环构成闭环结构,通过外部的起振信号开始振荡和延迟,输出q1、q2、q3……q2m-n

共2

m-n

个延迟信号,2

m-n

个延迟信号送入多路选择器,多路选择器为2

m-n

:1选择器;低m-n位控制字作为2

m-n

:1选择器的选择信号,输出与之对应的延迟信号b;所述的q

2m-n

信号作为n位计数器的时钟信号,在每个上升沿到来时,计数器的值cnt[n:1]相应加1;计数值cnt[n:1]送入比较器1中,实时与高n位控制字进行比较,当两者相等时,输出高电平信号a;信号a与信号b通过与门产生复位信号reset;同时,计数值cnt[n:1]送入比较器2中,当计数值cnt[n:1]全为0时,输出高电平信号c,上述的q

2m-n

信号和信号c通过与门产生置位信号set;rs触发器根据置位信号set将其输出信号dpwm拉高至高电平,根据复位信号reset将输出信号dpwm拉低至

低电平。

[0006]

本发明的特点及有益效果是:

[0007]

本发明提出了一种应用于数字开关电源的混合型dpwm电路结构,可实现高频率、高分辨率、高分辨率的pwm波输出。

[0008]

本发明提出的结构克服了传统的计数型dpwm和延迟型dpwm的缺点。计数型dpwm当精度较高时,其工作频率将成指数形式上升,同时带来较大的面积与功耗损失。延迟型dpwm由于温度或工艺偏差的存在,会导致延迟链的延迟时间不相等,同时延迟型dpwm占用面积很大。然而本发明提出的混合型dpwm结合了二者的结构特点,将计数型dpwm线性度高、分辨率高的优势,以及延迟型dpwm无需额外的时钟信号的优势结合起来,采用闭环的延迟锁相环,在其内部产生固定振荡周期的信号作为时钟信号。

[0009]

本发明提出的混合型dpwm结构,能够在高分辨率与高频率的矛盾之间进行折中,同时具备高线性度等优势,并且极大地缩小了电路面积。

附图说明:

[0010]

图1整体电路的结构图。

[0011]

图2 4位混合型dpwm的结构图。

[0012]

图3延时锁相环的结构图。

[0013]

图4延迟锁相环的时序图。

[0014]

图5输入4’b1011的时序图。

具体实施方式

[0015]

本发明提出一种高分辨率的混合型dpwm电路结构,由延迟锁相环(dll)、多路选择器、计数器、比较器、rs触发器等模块构成,其结构如图1所示。

[0016]

外部输入m位占空比控制字,将m位控制字拆分为高n位和低m-n位,对高位和低位分别进行处理。延迟锁相环构成闭环结构,通过外部的起振信号开始振荡和延迟,输出q1、q2、q3……q2m-n

共2

m-n

个延迟信号。2

m-n

个延迟信号送入2

m-n

:1选择器,低m-n位控制字作为选择信号,输出与之对应的延迟信号b。上述的q

2m-n

信号作为n位计数器的时钟信号,在每个上升沿到来时,计数器的值cnt[n:1]相应加1。计数值cnt[n:1]送入比较器1中,实时与高n位控制字进行比较,当两者相等时,输出高电平信号a。信号a与信号b通过与门产生复位信号reset。同时,计数值cnt[n:1]送入比较器2中,当计数值cnt[n:1]全为0时,输出高电平信号c,上述的q

2m-n

信号和信号c通过与门产生置位信号set。rs触发器根据置位信号set将输出信号dpwm拉高至高电平,根据复位信号reset将输出信号dpwm拉低至低电平。由此,最终输出占空比可调的方波信号dpwm,通过m位占空比控制字进行脉宽调制。

[0017]

本发明提出一种高分辨率的混合型dpwm电路结构,其结构如图1所示。本电路由延迟锁相环(dll)、多路选择器、计数器、比较器、rs触发器等模块构成。外部输入m位占空比控制字,将m位控制字拆分为高n位和低m-n位,对高位和低位分别进行处理。延迟锁相环构成闭环结构,通过外部的起振信号开始振荡和延迟,输出q1、q2、q3……q2m-n

共2

m-n

个延迟信号。2

m-n

个延迟信号送入2

m-n

:1选择器,低m-n位控制字作为2

m-n

:1选择器的选择信号,输出与之对应的延迟信号b。上述的q

2m-n

信号作为n位计数器的时钟信号,每个上升沿到来时,计数器

b1011一致。其工作时序图如图5所示。

[0021]

以上所述仅为本发明的较佳实施例,并不用以限制本发明,凡在本发明的精神和原则之内,所作的任何修改、等同替换、改进等,均应包含在本发明的保护范围之内。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。