1.本技术案主张2020年8月24日申请的美国正式申请案第17/000,921号的优先权及益处,该美国正式申请案的内容以全文引用的方式并入本文中。

2.本公开是关于一种半导体结构及其制备方法。特别是关于一种具有强化图案的半导体结构及其制备方法。

背景技术:

3.半导体元件对于许多现代应用是不可或缺的。随着电子技术的进步,半导体结构尺寸越来越小,同时也提供了更多的功能且包括更大量的集成电路(integrated circuitry;ic)。

4.微影是使用光阻作为掩膜来产生图案化结构的制程。因此,光阻的稳固性对于图案定义是非常重要的。随着先进技术推动尺寸持续缩小,也出现了各种技术问题。举例而言,有一些半导体结构因为其微缩化尺寸而不能被成功地形成,还有一些半导体结构具有缺陷,例如难以移除的光阻。因此,需要改良半导体制程,特别是微影制程。

5.上文的「先前技术」说明仅是提供背景技术,并未承认上文的「先前技术」说明揭示本公开的标的,不形成本公开的先前技术,且上文的「先前技术」的任何说明均不应作为本案的任一部分。

技术实现要素:

6.本公开提供一种半导体结构的制备方法。该制备方法包括:提供一基板;形成一掩膜层于该基板上,该掩膜层包括一周围区域和邻接该周围区域的一阵列区域;形成一第一蚀刻周围图案于该周围区域中和一第一蚀刻阵列图案于该阵列区域中,其中该第一蚀刻周围图案和该第一蚀刻阵列图案具有一顶表面、一侧壁和一底表面,该侧壁将该顶表面连接到该底表面;形成一第二周围图案于该第一蚀刻周围图案上并形成一第二阵列图案于该第一蚀刻阵列图案上;以及使用该第一蚀刻周围图案和该第二周围图案作为一蚀刻掩膜来蚀刻该掩膜层以形成一蚀刻掩膜层于该周围区域中。

7.在一些实施例中,该基板包括一金属层。

8.在一些实施例中,该掩膜层包括一氮化物层。

9.在一些实施例中,形成该第一蚀刻周围图案和该第一蚀刻阵列图案包括:形成一第一光阻层于该掩膜层上;以及通过一第一光阻掩膜将该第一光阻层暴露于紫外线辐射,其中该第一光阻掩膜包括对应于该第一蚀刻周围图案和该第一蚀刻阵列图案的一第一透明部分和一第一不透明部分。

10.在一些实施例中,在将该第一光阻层暴露于紫外线辐射之后,进行一显影制程以形成一第一图案。

11.在一些实施例中,该第一图案包括位于该周围区域中的一第一周围图案和位于该阵列区域中的一第一阵列图案。

12.在一些实施例中,在进行该显影制程之后,使用该第一图案作为一蚀刻掩膜来进行一蚀刻制程,以形成该第一蚀刻周围图案和该第一蚀刻阵列图案。

13.在一些实施例中,形成该第二周围图案和该第二阵列图案包括:形成一第二光阻层于该第一蚀刻周围图案上和该第一蚀刻阵列图案上;以及通过一第二光阻掩膜将该第二光阻层暴露于紫外线辐射,其中该第二光阻掩膜包括对应于该第二周围图案的一第二透明部分和一第二不透明部分。

14.在一些实施例中,形成该第二光阻层包括以该第二光阻层覆盖该第一蚀刻周围图案和该第一蚀刻阵列图案。

15.在一些实施例中,在将该第二光阻层暴露于紫外线辐射之后,进行一显影制程以形成该第二周围图案和该第二阵列图案。

16.在一些实施例中,该第二周围图案形成于该周围区域中的该第一蚀刻周围图案的该底表面上且与该侧壁分离。

17.在一些实施例中,该第二阵列图案覆盖该阵列区域中的该第一蚀刻阵列图案的该顶表面和该底表面。

18.在一些实施例中,该第一蚀刻周围图案的一第一节距(pitch)与该第一蚀刻阵列图案的一第二节距不同。

19.在一些实施例中,该第二周围图案的一第一高度大于该第一蚀刻周围图案的一第二高度。

20.本公开另提供一种半导体结构。该半导体结构包括:一基板,该基板包括一周围区域和邻接该周围区域的一阵列区域;位于该基板上的一第一蚀刻图案,其中该第一蚀刻图案包括一第一蚀刻周围图案和一第一蚀刻阵列图案,该第一蚀刻周围图案和该第一蚀刻阵列图案具有一顶表面、一侧壁和一底表面,该侧壁将该顶表面连接到该底表面;一第二周围图案,形成于该周围区域中;一第二阵列图案,形成于该阵列区域中。

21.在一些实施例中,该第二周围图案形成于该第一蚀刻周围图案的该底表面上且与该侧壁分离。

22.在一些实施例中,该第二阵列图案覆盖该第一蚀刻阵列图案的该顶表面和该底表面。

23.在一些实施例中,该基板包括一金属层。

24.在一些实施例中,该第一蚀刻周围图案的一第一节距与该第一蚀刻阵列图案的一第二节距不同。

25.在一些实施例中,该第二周围图案的一第一高度大于该第一蚀刻周围图案的一第二高度。

26.利用上述制备半导体结构的方法和半导体的构造,在金属零(m0)层上的周围图案的制备期间形成阵列图案。m0层的制备包括两个单独的制程,周围区域制程和阵列区域制程。在周围区域制程中形成的阵列图案并非用来定义其下方层中的轮廓;相反地,阵列图案是用于降低显影剂的流速。其结果,周围图案更为耐用并且能够抵抗被显影剂移除。因此,在周围区域制程期间,周围图案在暴露于显影剂后不会塌陷。此外,由于阵列区域中的图案光阻覆盖率不过度,因此蚀刻制程期间的负载效应(loading effect)较小,并且在硬掩膜剥离制程(strip process)之后没有掩膜剩余。综上所述,阵列图案的形成有助于形成稳固

的周围图案。

27.上文已相当广泛地概述本公开的技术特征及优点,而使下文的本公开详细描述得以获得较佳了解。形成本公开的权利要求标的的其它技术特征及优点将描述于下文。本公开所属技术领域中具有通常知识者应了解,可相当容易地利用下文揭示的概念与特定实施例可做为修改或设计其它结构或制程而实现与本公开相同的目的。本公开所属技术领域中具有通常知识者亦应了解,这类等效建构无法脱离后附的权利要求所界定的本公开的精神和范围。

附图说明

28.本公开各方面可配合以下图式及详细说明阅读以便了解。要强调的是,依照工业上的标准惯例,各个部件(feature)并未按照比例绘制。事实上,为了清楚的讨论,可能任意的放大或缩小各个部件的尺寸。

29.图1例示本公开第一比较例的半导体结构的周围区域的制程的代表性流程图。

30.图2例示在进行图1中步骤s101之后的半导体结构的剖面示意图。

31.图3例示本公开第一比较例在制备周围图案的中间阶段期间的半导体结构的俯视示意图。

32.图4例示本公开第一比较例的图3的半导体结构的剖面示意图。

33.图5例示本公开实施例在划线附近dram单元的光学显微镜影像。

34.图6例示本公开实施例在在硬掩膜剥离制程(lift-off process)之后的晶圆的照片。

35.图7例示本公开第二比较例在制备周围图案的中间阶段期间的半导体结构的剖面示意图。

36.图8示图7的周围图案的sem影像。

37.图9例示本公开一实施例在在制备周围图案的中间阶段中的显影制程期间的半导体结构的俯视示意图。

38.图10例示本公开显影剂的流动如何影响周边图案的示意图。

39.图11例示本公开实施例在制备半导体结构的周围区域制程的流程图。

40.图12例示本公开一实施例在周围区域制程中的第一曝光步骤期间的半导体结构的剖面示意图。

41.图13例示本公开一实施例在周围区域制程中的第一显影步骤期间的半导体结构的俯视示意图。

42.图14例示本公开第一比较例的图13的半导体结构的剖面示意图。

43.图15例示本公开一实施例在完成第一微影阶段之后的半导体结构的透视示意图。

44.图16例示本公开一实施例在稳固地形成的第一周围图案的sem影像。

45.图17例示本公开一实施例在周围区域制程中的第一蚀刻制程期间的半导体结构的剖面示意图。

46.图18例示本公开一实施例在图17的半导体结构(包括第一蚀刻图案)的局部放大图。

47.图19例示本公开一实施例在完成第一蚀刻阶段之后的半导体结构的透视示意图。

48.图20例示本公开一实施例在周围区域制程中的涂布步骤期间的半导体结构的剖面示意图。

49.图21例示本公开一实施例在周围区域制程中的第二曝光步骤期间的半导体结构的剖面示意图。

50.图22例示本公开一实施例在周围区域制程中的第二显影步骤期间的半导体结构的剖面示意图。

51.图23例示本公开一实施例在完成第二微影阶段之后的半导体结构的透视示意图。

52.图24例示本公开一实施例在周围区域制程中的第二蚀刻制程期间的半导体结构的剖面示意图。

53.图25例示本公开一实施例在完成第二蚀刻阶段之后的半导体结构的透视示意图。

54.其中,附图标记说明如下:

55.10:制备方法

56.20:制备方法

57.100:基板

58.102:掩膜层

59.102-2:经蚀刻的掩膜层

60.104:多层光阻层

61.104-2:经蚀刻的mlr层

62.104-2a:水平mlr部分

63.104-2b:垂直mlr部分

64.104-3:经蚀刻的mlr层

65.106:硬掩膜层

66.106-2:经蚀刻的硬掩膜层

67.108:第一光阻层

68.110:第二光阻层

69.112:第一透明部分

70.114:第一不透明部分

71.116:第二透明部分

72.118:第二不透明部分

73.120:深紫外光

74.df:流动

75.df1:显影剂

76.df2:显影剂

77.e1:第一蚀刻图案

78.e2:第二蚀刻图案

79.ea1:第一蚀刻周围图案

80.ea2:第一蚀刻阵列图案

81.eb1:第二蚀刻周围图案

82.eb2:第二蚀刻阵列图案

83.et1:第一蚀刻阶段

84.et2:第二蚀刻阶段

85.f1:毛细管力

86.f2:冲击力

87.h1:第一高度

88.h2:第二高度

89.ma:第一光罩

90.mb:第二光罩

91.p1:第一节距

92.p2:第二节距

93.pa:第一图案

94.pa1:第一周围图案

95.pa2:第一阵列图案

96.pb:第二图案

97.pb1:第二周围图案

98.pb2:第二阵列图案

99.ph1:第一微影阶段

100.ph2:第二微影阶段

101.pp1:第一光阻图案

102.pp2:光阻块

103.r1:周围区域

104.r2:阵列区域

105.s1:顶表面

106.s2:侧壁

107.s3:底表面

108.s101:步骤

109.s103:步骤

110.s105:步骤

111.s107:步骤

112.s109:步骤

113.s111:步骤

114.s113:步骤

115.s115:步骤

116.s200:步骤

117.s201:步骤

118.s202:步骤

119.s203:步骤

120.s204:步骤

121.s205:步骤

122.s206:步骤

123.s207:步骤

124.s208:步骤

125.st:染剂

具体实施方式

126.现在使用特定的语言描述图式所示的本公开实施例或示例。应理解的是,此处无意限制本公开的范围。所述实施例的任何改变或修改,以及本文所述原理的任何进一步应用,都被视为是本公开相关技术领域具有通常知识者可思及的。本公开可能在不同实施例中重复参照符号,但即使它们共用相同的参照符号,也不一定意味着一实施例的部件适用于另一实施例。

127.应理解的是,尽管本文可以使用用语第一、第二、第三等来描述各种元件、构件、区域、层、或部分,但是这些构件、区域、层、或部分不受到这些用语的限制。相反地,这些用语仅用于区分一个元件、构件、区域、层、或部分与另一个元件、构件、区域、层、或部分。因此,例如,在不脱离本公开概念的情况下,以下所讨论的第一元件、构件、区域、层、或部分可以被称为第二元件、构件、区域、层、或部分。

128.本文使用的用语仅出于描述特定示例实施例的目的,并且不用以限制本公开的概念。如本文所使用的,除非上下文另外明确指出,单数形式的“一(a/an)”和“该”也包括复数形式。应理解的是,在本说明书中使用用语“包括(comprises)”和“包含(comprising)”时指出所述的部件、整数、步骤、操作、元件、或构件的存在,但不排除存在或增加一个或多个其他部件、整数、步骤、操作、元件、构件、或前述的组合

129.此外,此处用到与空间相关的用词,例如:“在

…

下方”、“下方”、“较低的”、“之上”、“较高的”、及其类似的用词是为了便于描述图式中所示的一个元件或部件与另一个元件或部件之间的关系。这些空间关系词是用以涵盖图式所描绘的方位之外的使用中或操作中的元件的不同方位。装置可能被转向不同方位(旋转90度或其他方位),则其中使用的空间相关形容词也可相同地照着解释。

130.如本文中所使用的,本公开使用用语“图案化(patterning)”和“图案化(patterned)”来描述在表面上形成预定图案的操作。图案化操作包括各种步骤和制程,并且根据不同的实施例而变化。在一些实施例中,采用图案化制程来图案化既有的膜或层。图案化制程包括形成掩膜于既有的膜或层上,并通过蚀刻或其他移除制程来移除未被掩膜的膜或层。掩膜可以是光阻或硬掩膜。在一些实施例中,采用图案化制程以在表面上直接形成图案化层。图案化制程包括形成感光膜于表面上、进行微影制程、以及进行显影制程。剩余的感光膜被保留并集成到半导体元件中。

131.在先进技术中,制程窗口需要更多的关注。dram单元中的阵列区域和周围区域具有不同的图案密度,并在dram单元完成其生产制程后具有不同的功能。因此,阵列区域与周围区域之间的制程窗口差异显著。一般来说,它们各自的电路图案可能不会同时形成。

132.金属零(m0)层是关键层,因为它连接到多个后续的内连线结构。在一些实施例中,m0层的制备包括两个单独的制程,周围区域制程和阵列区域制程。周围区域制程用来将图案形成于dram单元的周围区域中。阵列区域制程用来将图案形成于dram单元的阵列区域

中。在一些实施例中,周围区域制程在阵列区域制程之前执行。周围区域制程包括四个阶段:第一微影阶段(ph1)、第一蚀刻阶段(et1)、第二微影阶段(ph2)、和第二蚀刻阶段(et2)。因此,前述周围区域制程使用双重图案化技术(double patterning technology;dpt)或微影-蚀刻-微影-蚀刻(litho-etch-litho-etch;lele)技术,其需要在单层中使用两个光罩。在一些其他实施例中,也可以使用lele技术来进行阵列区域制程。

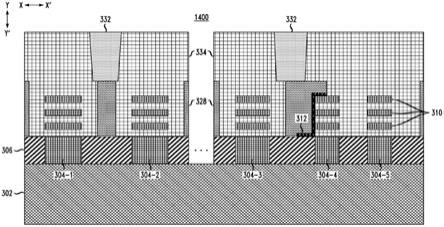

133.图1例示本公开第一比较例的半导体结构的周围区域的制备方法10的代表性流程图。图2显示在进行图1中步骤s101之后的半导体结构的剖面示意图。如图2所示,提供一基板100。在一些实施例中,基板100包括一金属层。接着沉积一掩膜层102于基板100上。在一些实施例中,掩膜层102包括一氮化物层。随后,沉积多层光阻(multilayer resist;mlr)层104于掩膜层102上。mlr层104是各种膜的组合,并且用于在基板100上定义图案。随后,形成一硬掩膜层106于mlr层104上。最后,涂布一第一光阻层108于硬掩膜层106上。掩膜层102、mlr层104、硬掩膜层106、和第一光阻层108一起在基板100上形成多层膜。图2中的垂直虚线代表dram单元中的周围区域r1和阵列区域r2之间的边界。在一些实施例中,周围区域r1和阵列区域r2包括相同的多层膜组合。

134.在步骤s103中,使用第一光罩将第一光阻层108暴露于深紫外(deep ultraviolet;duv)光。因为周围区域的制备方法10是用来形成图案于周围区域r1中,所以第一光罩中的布局仅对应于周围区域r1。实际上,在第一比较例中,阵列区域r2完全不暴露于duv光。因此,在步骤s105中进行第一显影之后,阵列区域r2被光阻块(photoresist bulk)占据,而在周围区域r1中形成多个第一光阻图案。

135.图3例示进行步骤s105之后的半导体结构的俯视示意图。如方形虚线所示,被包围在阵列区域r2中的区域包括光阻块pp2。周围区域r1中的水平线和垂直线代表第一光阻图案pp1。

136.图4是沿着图3中的虚线a-a'截取的剖面示意图。形成光阻块pp2和第一光阻图案pp1且两者分别位于不同的区域中。在步骤s107至s115中,对第一光阻图案pp1进行后续处理以将其轮廓转移至下方层,而在周围区域的制备方法10中,不使用光阻块pp2进行任何图案定义。

137.参照图1,在步骤s109中,再次以光阻涂布阵列区域r2。在步骤s111和113中,既不曝光也不显影累积在阵列区域r2中的光阻。其结果,光阻在阵列区域r2中的累积导致在步骤s115之后进行的光阻剥离制程中的沉重负荷。阵列区域r2中的沉重光阻阻止了光阻的完全剥离,导致硬掩膜剥离产生困难。一个常见的问题是,在周围区域的制备方法10完成之后,由于光阻残留在硬掩膜层106的顶部,所以不能完全移除阵列区域r2中的硬掩膜层106。

138.图5是一光学显微镜(optical microscope;om)影像,其中十字形区域表示晶圆上的划线(例如切割线)。多个矩形块是dram单元。每个单元具有位在中央的阵列区域r2,以及围绕阵列区域r2的周围区域r1。一如在多个单元的中心可看到的,染剂st残留在阵列区域r2中。划线附近的单元具有较多的染色,这意味着有较多的硬掩膜残留在单元上。

139.图6例示在硬掩膜剥离制程(lift-off process)之后的晶圆的照片。由于硬掩膜残留在多个单元上,因此晶圆的中心出现了染色。

140.在本公开的第二比较例中,周围区域制程类似于第一比较例的周围区域制程。和第一比较例一样,第二比较例也显示在图1的流程图中,唯一的差别在于在步骤s103中所形

成的第一光掩膜的布局不同。其他所有步骤与第一比较例中的那些步骤相同。在第二比较例中,阵列区域r2完全暴露于duv光。因此,在步骤s105之后,阵列区域r2未被任何光阻覆盖。

141.图7例示第二比较例的制备半导体结构的中间阶段的剖面示意图。阵列区域r2没有任何光阻,而周围区域r1具有位于硬掩膜层106上的多个第一光阻图案pp1。在第二比较例中,光阻不累积在阵列区域r2中。因此,阵列区域r2的蚀刻负载不如第一比较例的蚀刻负载重,从而改善了参照第一比较例描述的硬掩膜残留的问题。

142.然而,第二比较例中的制程可能无法成功地进行,特别是在技术节点缩小的情况下。随着线宽变窄,光阻线变得更脆弱。具体地,在第一微影阶段(ph1)中,第一光阻图案pp1在进行第一显影制程之后(步骤s105)塌陷。

143.图8显示第一光阻图案pp1塌陷的sem影像。从影像中可以看出,垂直光阻线的一部分已经塌陷。该现象的可能机制可能是显影剂在冲洗期间于第一光阻图案pp1上施加不平衡的力。图9显示在半导体结构中间阶段中的显影制程的俯视示意图。弯曲的箭头表示显影剂的流动df。在显影剂沉积到晶圆上之后,随后的旋转驱动显影剂在晶圆表面上移动。一般来说,显影剂在旋转过程中会从晶圆中心逐渐扩散到晶圆边缘。以显微镜观察正在进行显影制程的区域,发现显影剂在开放区域中流动得更快。比较周围区域r1和阵列区域r2,后者因为没有在显影制程之前或之后形成图案,所以没有任何障碍。因此,当具有更快速流动df的显影剂从阵列区域r2移动到周围区域r1时,产生了很强的不平衡力。不平衡力是由于显影剂从开放区域(阵列区域r2)到达拥挤区域(周围区域r1)而产生的。

144.图10例示显影剂的流动如何影响第一光阻图案pp1的示意图。当显影剂df1穿过两个相邻的第一光阻图案pp1之间的中央通道时,第一光阻图案pp1的内侧壁遭受毛细管力f1。第一光阻图案pp1被毛细管力f1向外推动。类似地,当显影剂df2与第一光阻图案pp1的外侧壁碰撞时,第一光阻图案pp1遭受冲击力f2。第一光阻图案pp1被冲击力f2向内推动。当毛细管力f1和冲击力f2的强度不相等时,第一光阻图案pp1将往向外或向内的方向塌陷。

145.综上所述,在显影期间,显影剂在周围区域r1和阵列区域r2之间来回移动。当晶圆旋转时,显影剂在光阻线上施加不平衡的力。当单元中的阵列区域r2没有任何障碍时,不平衡力增大,因此导致第一光阻图案pp1的不稳定性,从而造成塌陷。

146.上述的第一和第二比较例遭遇到不同的问题,并且不能用来制备稳固的图案。因此,从两个比较例得到一权衡方案,可以有效地解决技术问题。根据光罩布局的各种设计及其相应的实验,公开了在周围区域制程期间所形成的第一微影阶段(ph1)中阵列区域r2的合适图案。

147.图11例示本公开一实施例的半导体结构的周围区域的制备方法20的流程图。在步骤s200中,形成多层于一基板100上。在一些实施例中,基板100包括一金属层。接着沉积一掩膜层102于基板100上。在一些实施例中,掩膜层102包括一氮化物层。随后,沉积mlr层104于掩膜层102上。随后,形成一硬掩膜层106于mlr层104上。参照图11中周围区域的制备方法20的步骤s201,沉积一第一光阻层108于硬掩膜层106上。

148.图12例示周围区域的制备方法20中的第一曝光步骤的剖面示意图。参照图12和图11中制备方法20的步骤s202,使用具有第一透明部分112和第一不透明部分114的第一光罩ma。第一光阻层108暴露于深紫外(duv)光120。在一些实施例中,当进行周围区域的制备方

法20时,将第一光掩膜ma用来制造特定的光阻图案于阵列区域r2中。在一些实施例中,只在第一微影阶段(ph1)中应用第一光罩ma。

149.参照图13和图14,图14是沿着图13中的水平虚线b-b'显示周围区域的制备方法20中的第一显影步骤的剖面示意图。图13中的矩形虚线等同于图14中的垂直虚线,并且将周围区域r1与阵列区域r2分开。参照图13,在进行图11中制备方法20的步骤s203之后,形成第一图案pa。第一图案pa包括第一周围图案pa1和第一阵列图案pa2,它们各自分别位于周围区域r1和阵列区域r2中。根据一实施例,第一阵列图案pa2以网格状结构形成,但是不限于此。

150.在一些实施例中,根据光罩布局的设计,第一阵列图案pa2可以具有不同的图案密度。阵列区域r2中不同的光阻图案密度具有在进行后续蚀刻制程之前减少残留在阵列区域r2中的光阻量的优点。减少光阻的使用的目的是避免在完成周围区域r1的双重图案化之后残留光阻。此外,第一阵列图案pa2作为障碍物,在阵列区域r2中提供了粗糙的表面。当显影剂在阵列区域r2中遇到粗糙表面时,显影剂撞击在光阻线上的机制改变。当在显影期间旋转晶圆时,粗糙表面可降低显影剂的流速。当显影剂的流速降低时,由第一周围图案pa1接收的毛细管力也会降低。因此,第一周围图案pa1可以稳固地形成于周围区域r1中。第一阵列图案pa2的配置代表在阵列区域r2中没有光阻覆盖和光阻完全覆盖之间的折衷。这种技术特征既可以解决光阻残留的问题又可以解决图案塌陷的问题。

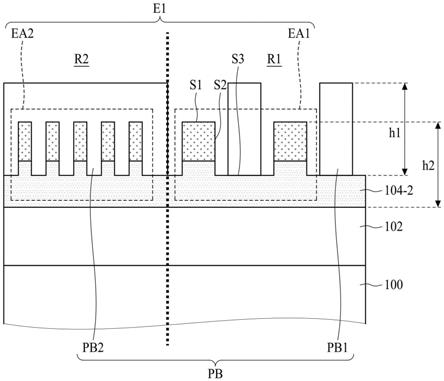

151.在一些实施例中,第一周围图案pa1和第一阵列图案pa2在包括步骤s201至s203的第一微影阶段(ph1)中具有不同的功能。第一周围图案pa1用来定义将要在周围区域的制备方法20的最后阶段期间进行转移的电路图案。然而,第一阵列图案pa2并非用来将轮廓定义至下方层中。在一些实施例中,第一阵列图案pa2用于降低显影剂的流速。第一阵列图案pa2有助于形成稳固的第一周围图案pa1,且并非用于图案定义。

152.图15例示完成第一微影阶段(ph1)(包括图11所示的步骤s201至s203)之后的半导体结构的透视示意图。半导体结构的四分之一是阵列区域r2,而其他四分之三属于周围区域r1。参照图14和图15,第一周围图案pa1和第一阵列图案pa2分别位于同一硬掩膜层106上的周围区域r1和阵列区域r2中。然而,两种图案在第一微影阶段(ph1)中具有不同的功能。第一周围图案pa1用来定义将要在周围区域的制备方法20的最后阶段进行转移的电路图案。相反地,第一阵列图案pa2并非用来将轮廓定义至下方层中。在一些实施例中,第一阵列图案pa2用于降低显影剂的流速。第一阵列图案pa2有助于形成稳固的第一周围图案pa1,且并非用于图案定义。

153.图16例示稳固地形成的第一周围图案pa1的sem影像。在晶圆进行显影之后,周围区域r1中的光阻图案不会塌陷。

154.图17例示周围区域的制备方法20中的第一蚀刻制程的剖面示意图。在图11中制备方法20的步骤s204中,第一蚀刻制程消耗未被第一图案pa保护的硬掩膜层106的一部分和mlr层104的一部分。在一些实施例中,将mlr层104的一部分蚀刻到一预定深度,而在mlr层104中产生多个凹陷。其结果,留下剩余的经蚀刻的硬掩膜层106-2和剩余的经蚀刻的mlr层104-2。

155.仍然参照图17,在移除第一图案pa之后,形成第一蚀刻图案e1,其包括经蚀刻的硬掩膜层106-2和经蚀刻的mlr层104-2。此外,第一蚀刻图案e1包括分别位于周围区域r1和阵

列区域r2中的第一蚀刻周围图案ea1和第一蚀刻阵列图案ea2。在一些实施例中,第一蚀刻周围图案ea1的第一节距p1与第一蚀刻阵列图案ea2的第二节距p2不同。在一些实施例中,第一蚀刻图案e1具有顶表面s1、侧壁s2和底表面s3,其中侧壁s2将顶表面s1连接到底表面s3。顶表面s1是经蚀刻的硬掩膜层106-2的一部分。侧壁s2包括经蚀刻的硬掩膜层106-2的一部分和经蚀刻的mlr层104-2的一部分。底表面s3是经蚀刻的mlr层104-2的一部分。

156.图18是图17中第一蚀刻周围图案ea1的局部放大图。可以看出,经蚀刻的mlr层104-2包括水平mlr部分104-2a和垂直mlr部分104-2b。如图17所示,水平mlr部分104-2a位于掩膜层102上。如图18所示,垂直mlr部分104-2b中介于(interposed)水平mlr部分104-2a和经蚀刻的硬掩膜层106-2之间。

157.图19例示完成第一蚀刻阶段(et1)之后的半导体结构的透视示意图。图19显示在周围区域r1的图案化中完成的第一微影-蚀刻阶段(ph1和et1)。图中暴露出来的顶表面是经蚀刻的硬掩膜层106-2的顶表面。

158.图20例示周围区域的制备方法20中的一第二涂布步骤的剖面示意图。参照图11中制备方法20的步骤s205,沉积第二光阻层110于经蚀刻的mlr层104-2和经蚀刻的硬掩膜层106-2上。在一些实施例中,图14中所示的第一周围图案pa1在沉积第二光阻层110之前被剥离。在替代实施例中,可以在沉积第二光阻层110之前保留第一周围图案pa1。

159.请参照图11中的步骤s206和图21,图21显示周围区域的制备方法20中的第二曝光步骤的剖面示意图。使用第二光罩mb对第二光阻层110进行duv光120的第二曝光。第二光罩mb包括第二透明部分116和第二不透明部分118。应注意的是,第二光罩mb用来定义周围电路的图案。因此,在一些实施例中,第二透明部分116和第二不透明部分118的配置仅对应于周围区域r1。

160.图22例示周围区域的制备方法20中的第二显影步骤的剖面示意图。在图11的步骤s207中,显影经曝光的第二光阻层110,然后形成第二图案pb。第二图案pb包括第二周围图案pb1和第二阵列图案pb2,它们各自分别位于周围区域r1和阵列区域r2中。在此阶段,最初被第二光阻层110覆盖的第一蚀刻周围图案ea1被部分地暴露出来。在一些实施例中,第二周围图案pb1的第一高度h1大于第一蚀刻周围图案ea1的第二高度h2。更具体地,在周围区域r1中,第二周围图案pb1形成于第一蚀刻周围图案ea1的底表面s3上并且与侧壁s2分离。在阵列区域r2中,第二阵列图案pb2完全覆盖第一蚀刻阵列图案ea2的顶表面s1和底表面s3。

161.图23例示完成第二微影阶段(ph2)(包括图11中所示的步骤s205至s207)之后的半导体结构的透视示意图。应注意的是,第二周围图案pb1具有间隔开的光阻线,而第二阵列图案pb2则是在第一蚀刻阵列图案ea2上具有完全覆盖的光阻。

162.图24例示周围区域的制备方法20中的第二蚀刻制程的剖面示意图。请参照图11中的步骤s208和图22和图24。在第二蚀刻制程中,使用图22中所示的第一蚀刻图案e1和第二图案pb作为蚀刻掩膜来蚀刻掩膜层102。在剥离剩余的光阻之后,形成第二蚀刻图案e2。第二蚀刻图案e2包括第二蚀刻周围图案eb1和第二蚀刻阵列图案eb2。第二蚀刻周围图案eb1和第二蚀刻阵列图案eb2分别位于周围区域r1和阵列区域r2中。第二蚀刻周围图案eb1包括经蚀刻的mlr层104-3和经蚀刻的掩膜层102-2。具体地,使用图22中所示的第一蚀刻周围图案ea1和第二周围图案pb1作为蚀刻掩膜来形成经蚀刻的掩膜层102-2。然而,第二蚀刻阵列

图案eb2不包含任何图案化的掩膜层102,因为在第二蚀刻制程中,阵列区域完全被光阻(亦即,第二阵列图案pb2)覆盖。因此,完成了周围区域的图案化中的第二微影-蚀刻步骤(ph2和et2)。应注意的是,在周围区域r1中,第二蚀刻图案e2具有经蚀刻的掩膜层102-2,亦即,周围区域r1中的掩膜层102被图案化。然而,在阵列区域r2中,掩膜层102完全没有被图案化。

163.图25例示完成第二蚀刻阶段(et2)之后的半导体结构的透视示意图。已通过一系列图案化制程形成周围区域r1,而最初在阵列区域r2中于第一微影阶段(ph1)中所定义的图案没有被转移到掩膜层102。因此,在阵列区域r2中,mlr层104和掩膜层102不具有光阻图案。在金属零层上,在完成周围区域的制备方法20之后,才开始阵列区域制程。

164.本公开提供一种双重图案化技术以定义dram单元中的周围图案(例如周围电路图案)。由于线宽的考量,周围图案线需要进行两次微影制程和两次蚀刻制程。在m0层上制备周围图案时,在阵列区域r2中添加光阻图案可以增加周围图案线的稳定性。因此,周围图案被加强并且能够抵抗显影剂的冲洗。周围图案线在经过显影剂冲洗之后不会塌陷。此外,由于阵列区域中的图案光阻覆盖率不过度,因此降低了蚀刻制程期间的负载效应,并且避免了光阻残余物的产生。

165.虽然已详述本公开及其优点,然而应理解可进行各种变化、取代与替代而不脱离权利要求所定义的本公开的精神与范围。例如,可用不同的方法实施上述的许多制程,且以其他制程或前述的组合替代上述的许多制程。

166.再者,本技术案的范围并不受限于说明书中该的制程、机械、制造、物质形成物、手段、方法与步骤的特定实施例。该技艺的技术人士可自本公开的揭示内容理解可根据本公开而使用与本文该的对应实施例具有相同功能或是达到实质上相同结果的现存或是未来发展的制程、机械、制造、物质形成物、手段、方法、或步骤。据此,此等制程、机械、制造、物质形成物、手段、方法、或步骤是包含于本技术案的权利要求内。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。