1.本技术的实施例涉及集成电路器件及其形成方法。

背景技术:

2.许多现代电子器件都包含电子存储器。电子存储器可以是易失性存储器或非易失性存储器。非易失性存储器能够在没有电源的情况下保留其存储的数据,而易失性存储器在断电时会丢失其存储的数据。需要频繁刷新的动态随机存取存储器(dram)是易失性存储器。非易失性电子存储器包括例如电阻随机存取存储器(rram)、磁阻随机存取存储器(mram)、铁电随机存取存储器(feram)、相变存储器(pcm)等。

技术实现要素:

3.本技术的一些实施例提供了一种集成电路器件,包括:材料层,包括hf

x

zr

1-x

o2,其中,0≤x≤1;其中,所述材料层具有小于1ppm的氯。

4.本技术的另一些实施例提供了一种集成电路器件,包括:存储器单元,包括在源极和漏极之间延伸的沟道、栅电极以及所述栅电极和所述沟道之间的铁电层;其中,所述存储器单元具有泄漏电流和与时间依赖性介电击穿速率(tddb速率),其中,所述时间依赖性介电击穿速率定义为所述泄漏电流的初始值除以所述泄漏电流从所述初始值加倍的操作时间;以及时间依赖性介电击穿速率小于如果将1ppm的氯添加至所述铁电层时所述时间依赖性介电击穿速率将增加的量。

5.本技术的又一些实施例提供了一种形成集成电路器件的方法,所述方法包括:使用无氯前体通过原子层沉积形成铁电层。

附图说明

6.当结合附图进行阅读时,从以下详细描述可最佳理解本发明的各个方面。应该指出,根据工业中的标准实践,各个部件未按比例绘制。实际上,为了清楚的讨论,各个部件的尺寸可以任意地增大或减小。

7.图1a示出了根据本教导的一些方面的集成电路器件的截面侧视图。

8.图1b示出了根据本教导的一些其它方面的集成电路器件的截面侧视图。

9.图2示出了根据本教导的一些其它方面的集成电路器件的截面侧视图。

10.图3至图6是举例说明形成诸如图1a的器件的器件的方法的一系列截面图。

11.图7提供了示出根据本教导的形成包括铁电层的集成电路器件的方法的流程图。

具体实施方式

12.本发明提供了许多用于实现本发明的不同特征的不同实施例或实例。下面描述了组件和布置的具体实例以简化本发明。当然,这些仅仅是实例,而不旨在限制本发明。例如,以下描述中,在第二部件上方或者上形成第一部件可以包括第一部件和第二部件直接接触

形成的实施例,并且也可以包括在第一部件和第二部件之间可以形成额外的部件,从而使得第一部件和第二部件可以不直接接触的实施例。此外,本发明可在各个实例中重复参考标号和/或字符。该重复是为了简单和清楚的目的,并且其本身不指示所讨论的各个实施例和/或配置之间的关系。

13.而且,为了便于描述,在此可以使用诸如“在...之下”、“在...下方”、“下部”、“在...之上”、“上部”等空间相对术语,以描述如图所示的一个元件或部件与另一个(或另一些)元件或部件的关系。除了图中所示的方位外,空间相对术语旨在包括器件在使用或操作中的不同方位。器件可以以其它方式定向(旋转90度或在其它方位上),而本文使用的空间相对描述符可以同样地作出相应的解释。

14.各种集成电路器件包括铁电材料层。例如,某些存储器器件使用铁电层作为数据存储层。在这些存储器器件的一些中,铁电层通过保持电偶极子的极化来存储数据。这些电偶极子的第一取向可以表示逻辑“1”,并且第二取向可以表示逻辑“0”。存在可以采用铁电材料的多种存储器结构。在铁电存储器的一些实施例中,铁电层设置在存储数据的电容器中的两个极板之间。例如,1t-1c存储器架构可以使用铁电电容器。在铁电存储器的其它实施例中,铁电层设置在存储数据的晶体管结构中的栅电极和沟道之间。铁电场效应晶体管(fefet)是实例。不管铁电层出现的结构如何,希望器件具有长寿命和高可靠性。可能限制寿命的一种机制是铁电层中与时间相关的介电击穿(tddb)。虽然tddb的机制尚不明确,但是可以观察到,通过铁电层的泄漏电流在延长的操作周期中增加。可以限制可靠性的一种机制是偏置温度不稳定性(bti),诸如正偏置温度不稳定性(pbti)和负偏置温度不稳定性(nbti)。bti可以与铁电层中的电荷俘获有关,并且表现为包括铁电层的器件在连续操作周期中的阈值电压的变化。

15.本发明的发明人已经确定,tddb和bti可以通过从铁电层消除氯残留来改善。它们已经确定,低至1ppm的氯可以产生tddb/bti,并且通过生产具有小于1ppm的氯的铁电材料可以大大降低tddb/bti。特别是在成分hf

x

zr

1-x

o2的铁电材料中观察到了这种现象。预期结果将扩展至其它铁电材料。在分子式中,x具有0至1的范围。根据分子式的实例包括hfo2、hfzro2和zro2。

16.铁电层通常使用金属氯化物前体通过原子层沉积(ald)来产生。铁电层的性能受到层厚度的强烈影响。ald允许精确控制厚度。金属氯化物前体具有非常适合于ald工艺的挥发性和反应速率。但是,根据本发明的一些实施例,铁电层由包括无氯金属化合物的前体产生。使用无氯金属化合物的前体可以消除氯残留。

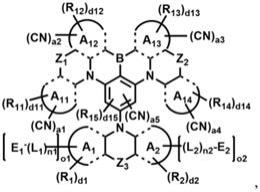

17.在一些实施例中,前体包括金属化合物,其中金属直接结合至氧、氮、碳或它们的组合。在一些实施例中,前体包括金属化合物,其中金属直接结合至碳。在一些实施例中,前体包括金属化合物,其中金属直接结合至氧。在一些实施例中,前体包括金属化合物,其中金属仅仅直接结合至氧和/或碳。在一些实施例中,前体包括金属化合物,其中金属直接结合至氮。在一些实施例中,前体包括金属化合物,其中金属仅仅直接结合至氮。利用形式为m(nr1r2)4的前体已获得了优异的结果,其中m是锆(zr)、铪(hf)等,并且r1和r2是有机官能团。在一些实施例中,有机官能团是烷烃、烯烃、炔烃、醇、胺、醚、醛、酮、羧酸、酯、酰胺等。在一些实施例中,前体包括以下一种或多种:叔丁醇锆(iv)(zr[oc(ch3)3]4或ztb);双(甲基-η5-环戊二烯基)甲氧基甲基锆(zr[ch3c5h4]2ch3och3、zrcmmm或zrd-co4);四(二甲基氨基)锆

(iv)(zr[n(ch3)2]4或tdmaz);四(乙基甲基氨基)锆(iv)(zr[n(ch3)(c2h5)]4或temaz);双(甲基-η5-环戊二烯基)二甲基铪(hf[ch3c5h4]2ch3och3、hfcmme或hfd-co2);双(甲基-η5-环戊二烯基)甲氧基甲基铪(hfch3och3[c5h4]2或hfd-co4);四(二甲基氨基)铪(iv)(hf[n(ch3)2]4或tdmah);四(乙基甲基氨基)铪(iv)(hf[n(ch3)(c2h5)]4或temah);等。

[0018]

铁电层可以并入任何类型的集成电路器件中。在一些实施例中,铁电层包括在存储器器件的存储器单元中。存储器可以是任何类型。在一些实施例中,铁电存储器包括晶体管结构中的铁电层。在一些实施例中,晶体管具有底部栅极。在一些实施例中,晶体管具有顶部栅极。在一些实施例中,晶体管是三维(3d)存储器阵列。在一些实施例中,晶体管具有金属铁电半导体(mfs)结构。在一些实施例中,晶体管具有金属铁电绝缘半导体(mfis)结构。在一些实施例中,铁电存储器包括电容器结构中的铁电层。在一些实施例中,存储器是铁电随机存取存储器(feram),其中铁电电容器耦接至场效应晶体管(fet)的漏极区域。在一些实施例中,存储器具有金属铁电金属绝缘半导体(mfmis)结构,其中铁电电容器耦接至fet的栅极。

[0019]

与铁电层中仅多于1ppm的氯的等效铁电存储器单元相比,根据本教导的铁电存储器单元具有较低的与时间依赖性介电击穿速率(tddb速率)和较低的bti速率。tddb速率在短操作周期中可能无法很好地表征,但是当在较长操作周期中(诸如泄漏电流加倍的周期或威布尔斜率减小的周期)考虑时可以一致地确定。因此,为了用于比较,tddb速率可以定义为初始泄漏电流除以初始泄漏电流加倍的操作时间。可选地,tddb速率可以在威布尔斜率减小的周期中确定。

[0020]

根据本发明的铁电存储器单元的铁电层可以利用无氯前体形成。比较铁电存储器单元的铁电层可以通过将一些氯化物前体添加至工艺气体混合物来形成。根据本教导,比较铁电存储器单元将具有比铁电存储器单元的tddb速率大的tddb速率。在一些实施例中,tddb速率是在铁电层中具有多于1ppm的氯的比较存储器单元的一半或更小。在一些实施例中,定义为阈值电压在连续操作期间改变的速率的bti速率是比较存储器单元的速率的一半或更小。

[0021]

在一些实施例中,根据本教导的器件具有铁电层,该铁电层是分子式hf

x

zr

1-x

o2的hfzro层。其中x在0至1的范围内。在一些实施例中,铁电层是hf

x

zr

1-x

o2。其中x在0.1至0.9的范围内。在一些实施例中,铁电层107a是hf

0.5

zr

0.5

o2。在一些实施例中,铁电层具有大于50%的组合t相(四方相)、o相(斜方相)和c相(立方相)以及小于50%的m相(单斜相)的hfzro。在一些实施例中,hfzro掺杂有增加2pr的较小半径离子。较小半径离子包括铝(al)、硅(si)等离子。在一些实施例中,hfzro掺杂有增加2pr的较大半径离子。较大半径离子包括镧(la)、钪(sc)、钙(ca)、钡(ba)、钆(gd)、钇(y)等离子。2pr是铁电材料的转换极化的量度。在一些实施例中,铁电层具有小于1ppm的氯。在一些实施例中,铁电层是无氯的。在一些实施例中,铁电层具有氧空位。

[0022]

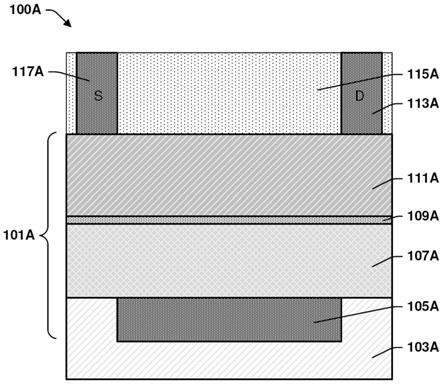

图1a示出了根据本教导的一些方面的具有存储器单元101a的集成电路器件100a。存储器单元101a包括晶体管结构中的铁电层107a。晶体管结构包括铁电层107a、沟道层111a、栅电极105a、源极耦合件117a和漏极耦合件113a。铁电层107a位于沟道层111a和栅电极105a之间。可选地,铁电层107a和沟道层111a由介电层109a分隔开。栅电极105a位于铁电层107a下面。因此,栅电极105a是底部栅极。栅电极105a可以掩埋在衬底103a中。源极耦合

件117a和漏极耦合件113a可以是层间电介质115a中的通孔,并且可以与形成在衬底103a上方的金属互连结构连接。

[0023]

铁电层107a具有很少或没有氯残留。在一些实施例中,铁电层107a是具有1ppm或更少的氯的hfzro。在一些实施例中,铁电层107a是无氯的。在一些实施例中,铁电层107a是掺杂有钪(sc)等的氮化铝(aln)。铁电层107a可以可选地是具有很少或没有氯的另一种铁电材料,例如1ppm或更少。可以使用的其它铁电材料的实例包括但不限于氧化铪铝(hfalo)、氧化铪镧(hflao)、氧化铪锆(hfzro)、氧化铪铈(hfceo)、氧化铪(hfo)、氧化铪硅(hfsio)、氧化铪钆(hfgdo)等。

[0024]

在一些实施例中,铁电层107a的厚度为0.1nm至100nm。在一些实施例中,铁电层107a的厚度为1nm至30nm。如果铁电层107a太薄,则它可能无法在存储器单元101a中提供足够的阈值电压切换。如果铁电层107a太厚,则它可能不具有期望的氧空位浓度。

[0025]

介电层109a(如果存在)可以是绝缘层或阻挡层。在一些实施例中,介电层109a具有在0.1nm至10nm范围内的厚度。在一些实施例中,介电层109a具有在0.3nm至3nm范围内的厚度。如果介电层109a太薄,则它可能无法起作用。如果介电层109a太厚,则它可能会干扰存储器单元101a的操作。介电层109a可以包括硅(si)、镁(mg)、铝(al)、钇(y)、镧(la)、锶(sr)、钆(gd)、钪(sc)、钙(ca)、它们的化合物、它们的组合等。在一些实施例中,介电层109a包括氧化铪(hfo2)。在一些实施例中,介电层109a包括氧化铪(hfo2)和硅(si),其中硅的原子比为10%或更高。

[0026]

沟道层111a可以是或包括半导体。在一些实施例中,沟道层111a是或包括氧化物半导体。可以适合于沟道层111a的氧化物半导体包括但不限于氧化锌(zno)、氧化镁(mgo)、氧化钆(gdo)、氧化铟钨(inwo)、氧化铟镓锌(ingazno)、氧化铟锌(inzno)、氧化铟镓锌锡(ingaznsno或igzto)、氧化铟锡(insno或ito)、它们的组合等。在一些实施例中,沟道层111a是或包括多晶硅、非晶硅、硅锗(sige)等。在一些实施例中,沟道层111a具有在0.1nm至100nm范围内的厚度。在一些实施例中,沟道层111a具有在2nm至30nm范围内的厚度。在一些实施例中,沟道层111a具有在5nm至20nm范围内的厚度。

[0027]

源极耦合件117a、漏极耦合件113a和栅电极105a可以由任何合适的导电材料形成。合适的导电材料可以包括掺杂的多晶硅、石墨烯、金属等。在一些实施例中,源极耦合件117a、漏极耦合件113a和栅电极105a利用金属形成。可以使用的金属的一些实例是钨(w)、铜(cu)、钌(ru)、钼(mo)、钴(co)、铝(al)、镍(ni)、银(ag)、金(au)等和它们的合金。源极耦合件117a、漏极耦合件113a和栅电极105a中的一个或多个可以进一步包括扩散阻挡层、胶层或其它这种层。可以用于扩散阻挡层或胶层的材料的一些实例是氮化钛(tin)、氮化钽(tan)、氮化钼(mon)、氮化锆(zrn)、氮化铪(hfn)等。

[0028]

层间电介质115a可以是未掺杂的硅酸盐玻璃(usg)等。在一些实施例中,层间电介质115a是低k电介质。在一些实施例中,层间电介质115a是极低k电介质。低k电介质是具有比二氧化硅的介电常数低的介电常数的材料。低k电介质的实例包括有机硅酸盐玻璃(osg)(诸如碳掺杂的二氧化硅、氟掺杂的二氧化硅(也称为氟化石英玻璃或fsg))和有机聚合物低k电介质。有机聚合物低k电介质的实例包括聚亚芳基醚、聚酰亚胺(pi)、苯并环丁烯和无定形聚四氟乙烯(ptfe)。极低k电介质是具有约2.1或更小的介电常数的材料。极低k电介质可以通过以使得它具有孔隙率或气隙的这种方式沉积极低k电介质,由此包括孔和气隙的

复合材料的有效介电常数为2.1或更小。

[0029]

衬底103a可以是从诸如硅晶圆等的晶圆切割的管芯。衬底103a可以是半导体衬底,诸如块状半导体、绝缘体上半导体(soi)衬底等。也可以使用其它衬底,诸如多层衬底或梯度衬底。在一些实施例中,衬底103a的半导体材料是或包括硅、锗、碳化硅、砷化镓、磷化镓、磷化铟、砷化铟和/或锑化铟、硅锗、磷砷化镓、砷化铝铟、砷化铝镓、砷化镓铟、磷化镓铟、磷砷化镓铟、它们的组合等。衬底103a可以是或包括介电材料。例如,衬底103a可以是介电衬底,或者可以包括半导体衬底上的介电层。介电材料可以是:氧化物,诸如氧化硅;氮化物,诸如氮化硅;碳化物,诸如碳化硅;它们的组合,诸如氮氧化硅、碳氧化硅、碳氮化硅等或任何其它合适的电介质。

[0030]

在存储器单元101a中,在栅电极105a上存在阈值电压,在该阈值电压下,沟道层111a开始在源极耦合件117a和漏极耦合件113a之间导电。该阈值电压可以通过改变铁电层107a内的电偶极子的极化的写入和擦除操作来改变。那些电偶极子的第一取向提供了可以表示逻辑“1”的第一阈值电压,并且那些电偶极子的第二取向提供了可以表示逻辑“0”的第二阈值电压。

[0031]

用于存储器单元101a的写入操作可以包括将栅电极105a设置为编程电压v

th

,同时将源极耦合件117a和漏极耦合件113a接地。v

th

可以是用于存储器单元101a的最高可能阈值电压。对于擦除操作,可以将栅电极105a设置为-v

th

,同时将源极耦合件117a和漏极耦合件113a接地。读取操作可以包括将栅电极105a设置为介于第一阈值电压和第二阈值电压之间的电压,例如1/

2vth

,将源极耦合件117a设置为v

dd

,设置漏极耦合件113a,并且确定结果电流是高于还是低于阈值。存储器单元101a的操作包括读取、写入和擦除操作的组合。可以设置具体的操作协议用于确定tddb速率或bti速率。在一些实施例中,操作协议包括施加恒定电压应力(cvs)。对于bti速率,可以施加小栅极电压脉冲以测量v

th

,同时连续保持电压应力。

[0032]

图1b示出了根据本教导的一些其它方面的具有存储器单元101b的集成电路器件100b。存储器单元101b具有包括源极区域118b、漏极区域104b、沟道层111b、铁电层107b和栅电极105b的晶体管结构。源极区域118b、漏极区域104b和沟道层111b全部由衬底103b的半导体部分提供。源极区域118b和漏极区域104b具有一种掺杂类型,并且沟道层111b具有相反的掺杂类型。源极耦合件117b与源极区域118b连接。漏极耦合件113b与漏极区域104b连接。源极耦合件117b和漏极耦合件113b是层间电介质115b中的通孔,并且可以与形成在衬底103b上方的金属互连结构连接。栅电极105b位于铁电层107b和沟道层111b之上,这使得栅电极105b是顶部栅极。铁电层107b位于沟道层111b和栅电极105b之间。可选地,铁电层107b和沟道层111b由介电层109b分隔开。存储器单元101b中的层厚度和成分可以如针对存储器单元101a中的对应结构所描述。

[0033]

虽然存储器单元101b已经表示为存储器单元,但是在具有金属氧化物半导体结构(mosfet)的常规场效应晶体管中可以使用相同的材料布置。具有相同成分的铁电层107b可以用作高k介电层,但是不同的厚度可能更适合该应用。如在存储器单元应用中,低氯有助于实现低tddb。

[0034]

图2示出了根据本教导的一些方面的具有包括晶体管227和铁电电容器235的1t1c存储器器件的集成电路器件200。铁电电容器235包括顶部电极237和底部电极211之间的铁电层107c。铁电电容器235可以设置在形成在半导体衬底239上方的金属互连结构223中。金

属互连结构223包括可以由层间电介质115c围绕的线231和通孔233。铁电电容器235可以设置在金属互连结构223中的第三金属互连层和第四金属互连层之间、第四金属互连层和第五金属互连层之间或任何其它相邻的金属互连层对之间。晶体管227可以包括形成在半导体衬底239的掺杂区域228上方的栅电极225和栅极电介质229。源极/漏极区域221可以由半导体衬底239的具有相反掺杂类型的其它区域形成。

[0035]

铁电层107c是具有如形成铁电层107a描述的成分的材料。同样,层间电介质115c具有层间电介质115a的成分替代物。铁电电容器235可以通过向字线(wl)、位线(bl)和源极线(sl)施加合适的电压而作为存储器单元来操作。如果铁电层107c具有合适的厚度和操作模式,则它将根据电偶极子的极化存储数据。在这种情况下,铁电电容器235是铁电存储器单元。如果铁电层107c具有合适的厚度和操作模式,则它将根据电容器上的电荷存储数据。在这种情况下,铁电电容器235是动态随机存取存储器(dram)单元。

[0036]

图3至图6是举例说明根据本教导的形成具有根据本教导的铁电层的存储器单元的方法的截面图。虽然参考方法的各个实施例描述了图3至图6,但是应该理解,图3至图6所示的结构不限于该方法,而是可以独立于该方法而独立存在。虽然将图3至图6描述为一系列步骤,但是应该理解,在其它实施例中可以改变步骤的顺序。虽然图3至图6示出并且描述了一组具体的步骤,但是在其它实施例中可以省略示出和/或描述的一些步骤。此外,在其它实施例中可以包括未示出和/或描述的步骤。虽然根据形成集成电路器件100a描述了图3至图6的方法,但是该方法可以用于形成其它集成电路器件。

[0037]

如图3的截面图300所示,该方法可以通过在衬底103a中形成栅电极105a开始。栅电极105a可以例如通过:在衬底103a上方形成光刻胶掩模;蚀刻以在衬底103a中形成沟槽;剥离光刻胶掩模;利用用于栅电极105a的金属或其它导电材料填充沟槽;以及化学机械抛光(cmp)以去除沟槽外部的任何金属或其它导电材料来形成。利用金属填充沟槽可以包括原子层沉积(ald)、化学汽相沉积(cvd)、物理汽相沉积(pvd)、电镀、化学镀等或任何其它合适的工艺。

[0038]

如图4的截面图400所示,该方法可以继续形成铁电层107a。铁电层107a使用无氯气态前体通过化学汽相沉积(cvd)、原子层沉积(ald)等来形成。在一些实施例中,铁电层107a通过ald形成,如下面更全面描述。

[0039]

如图5的截面图500所示,该方法可以继续形成沟道层111a,并且可选地形成介电层109a。介电层109a和沟道层111a可以通过化学汽相沉积(cvd)、物理汽相沉积(pvd)、原子层沉积(ald)、它们的任何组合等或任何其它合适的一种或多种工艺来形成。

[0040]

如图6的截面图600所示,该方法可以继续在沟道层111a上方形成层间电介质115a。层间电介质115a可以通过cvd、诸如旋涂玻璃工艺的液体工艺等来形成。在一些实施例中,层间电介质115a是通过利用硅烷(sih4)或正硅酸乙酯(teos)的cvd形成的未掺杂的硅酸盐玻璃(usg)。

[0041]

如图6进一步所示,可以形成用于在层间电介质115a中蚀刻沟槽603的光刻胶掩模601。蚀刻沟槽603可以包括诸如等离子体蚀刻的干蚀刻工艺或任何其它合适的工艺。沟槽603可以利用导电材料通过原子层沉积(ald)、化学汽相沉积(cvd)、物理汽相沉积(pvd)、电镀、化学镀等或任何其它合适的工艺以及随后的平坦化来填充,以形成如图1a所示的结构。平坦化可以是cmp或任何其它合适的工艺。

[0042]

图7呈现了可以用于形成根据本发明的集成电路器件的工艺700的流程图。工艺700包括用于形成图1a的集成电路器件100a的步骤,并且也包括根据本发明的其它实施例的形成可以用于形成其它铁电层的铁电层107a的方法。虽然本文将图7的工艺700示出和描述为一系列步骤或事件,但是应该理解,这样的步骤或事件的示出顺序不应解释为限制意义。例如,除了本文示出和/或描述的那些步骤或事件之外,一些步骤可以以不同的顺序发生和/或与其他步骤或事件同时发生。此外,可能不需要全部示出的步骤实现本文的描述的一个或多个方面或实施例,并且本文描述的一个或多个步骤可以在一个或多个单独的步骤和/或阶段中实施。

[0043]

工艺700可以开始步骤701,形成底部电极。图3的截面图提供了说明性实例。

[0044]

该工艺继续步骤703,形成铁电层。图4的截面图提供了说明性实例,但是应该理解,根据本教导的铁电层可以以不同的结构或在处理的不同阶段形成。步骤703可以包括如进一步由步骤711至步骤725示出的原子层沉积(ald)工艺。

[0045]

在形成铁电层之后,工艺700可以继续步骤705,形成介电层,并且继续步骤707,形成沟道层。图5的截面图提供了说明性实例。步骤707,形成介电层是可选的。

[0046]

该工艺可以继续步骤709,形成源极和漏极结构。图5与图1a一起提供了实例。

[0047]

步骤703,形成铁电层,可以是ald。ald涉及循环重复一系列步骤,由此均匀地并且以可控的速率沉积铁电层。如图所示,ald工艺可以开始步骤711,利用水蒸气等脉冲。

[0048]

脉冲意味着在有限的时间周期内将试剂引入工艺气流中。工艺气体可以包括惰性载体,连续流过包含衬底的室的诸如氮或氩。室可以通过真空系统连续排气。在一些实施例中,ald工艺在次大气压的压力下实施。在一些实施例中,该工艺在等于或低于50torr的压力下实施。在一些实施例中,该工艺在约1torr至约10torr范围内的压力下实施。在一些实施例中,该工艺在约2torr至约5torr范围内的压力下实施。

[0049]

通过吸收或吸附,水蒸气层形成在衬底的表面上。水在形成铁电层的化学反应中提供氧源。另一合适的氧气源可以代替水,诸如o2、o3或等离子体o2或等离子体o3。继续脉冲直至形成表面层。在一些实施例中,水脉冲为60秒或更短。在一些实施例中,水脉冲在一秒至10秒的范围内。

[0050]

在水已经在表面上形成层之后,该工艺可以继续步骤713,净化室。净化室可以利用非反应性气体净化。氮可以是非反应性气体。在一些实施例中,净化持续30秒或更短。在一些实施例中,净化持续一秒至10秒。在一些实施例中,净化持续5秒或更短。

[0051]

该工艺可以继续步骤715,利用无氯的锆前体脉冲。无氯的锆前体是与表面上的氧源反应以形成包括锆的层的锆化合物。该前体选择为在工艺条件下是挥发性的,以仅沉积至受表面上存在的诸如水的氧源的量限制的程度,并且以具有可接受的反应速率。在一些实施例中,锆前体脉冲持续60秒或更短。在一些实施例中,锆前体脉冲持续0.5秒至10秒。在一些实施例中,锆前体脉冲持续约1秒至约5秒。

[0052]

在一些实施例中,锆前体是锆化合物,其中锆直接结合至碳。双(甲基-η5-环戊二烯基)甲氧基甲基锆(zr[ch3c5h4]2ch3och3或zrcmmm)是实例。在一些实施例中,锆前体是锆化合物,其中锆直接结合至氧。叔丁醇锆(iv)(zr[oc(ch3)3]4或ztb)是实例。在一些实施例中,锆前体是锆化合物,其中锆直接结合至氮。在一些实施例中,锆前体具有形式zr(nr1r2)4,其中r1和r2是有机官能团。四(二甲基氨基)锆(iv)(zr[n(ch3)2]4或tdmaz)和四(乙

基甲基氨基)锆(iv)(zr[n(ch3)(c2h5)]4或temaz)是实例。在一些实施例中,锆前体是以下表格中所示的那些中的一个等:

[0053][0054][0055]

在步骤715之后是步骤717,另一净化。该净化可以类似于步骤713的净化。然后可以是步骤719,类似于步骤711的另一水脉冲,和步骤721,另一净化。步骤719和721可以与步骤711和713类似或相同并且允许相同的描述。

[0056]

该工艺可以继续步骤723,利用无氯的铪前体脉冲。无氯的铪前体是与表面上的氧源反应以形成包括铪的层的铪化合物。该前体选择为在工艺条件下是挥发性的,以仅沉积至受表面上存在的水等的量限制的程度,并且以具有可接受的反应速率。在一些实施例中,铪前体脉冲持续60秒或更短。在一些实施例中,铪前体脉冲持续0.5秒至10秒。在一些实施例中,铪前体脉冲持续约1秒至约5秒。

[0057]

在一些实施例中,铪前体是铪化合物,其中铪直接结合至碳。双(甲基-η5-环戊二烯基)二甲基铪(hf[ch3c5h4]2ch3och3或hfd-co2)和双(甲基-η5-环戊二烯基)甲氧基甲基铪(hfch3och3[c5h4]2或hfd-co4)是实例。在一些实施例中,铪前体是铪化合物,其中铪直接结合至氧。在一些实施例中,铪前体是铪化合物,其中铪直接结合至氮。在一些实施例中,铪前体具有形式hf(nr1r2)4,其中r1和r2是有机官能团。四(二甲基氨基)铪(iv)(hf[n(ch3)2]4或tdmah)和四(乙基甲基氨基)铪(iv)(hf[n(ch3)(c2h5)]4或temah)是实例。在一些实施例中,铪前体是以下表格中描述的那些中的一个或多个等:

[0058][0059][0060]

在步骤723之后是步骤725,另一净化并且重复步骤,直至铁电层已经建立至期望的厚度。在所描述的工艺中,将锆并入铁电层中的步骤与将铪并入铁电层中的步骤交替进行。可选地,改变这些步骤的比例,或者仅使用合并锆的步骤,或者仅使用合并铪的步骤。在一些实施例中,每60秒或以更高的频率沉积一层。选择合适的前体允许实现期望的速率。

[0061]

在一些实施例中,锆前体或铪前体包括提供金属离子的额外的前体。可以由额外的前体提供的金属离子的实例包括铝(al)、硅(si)、镧(la)、钪(sc)、钙(ca)、钡(ba)、钆(gd)、钇(y)等。在一些实施例中,前体是以下表格所示的那些中的一个等:

[0062]

[0063]

[0064][0065]

在一些实施例中,金属离子是铝(al)等。在一些实施例中,金属离子是硅(si)等。在一些实施例中,金属离子是镧(la)等。在一些实施例中,金属离子是钆(gd)等。在一些实施例中,金属离子是钇(y)等。在一些实施例中,额外的前体包括直接结合至氧、氮、碳或它们的组合的金属离子。在一些实施例中,额外的前体包括直接结合至碳的金属离子。在一些实施例中,额外的前体包括直接结合至氧的金属离子。在一些实施例中,额外的前体包括仅直接结合至氧和/或碳的金属离子。在一些实施例中,额外的前体包括直接结合至氮的金属离子。

[0066]

本教导的一些方面涉及集成电路器件,该集成电路器件包括:材料层,包括hf

x

zr

1-x

o2,其中,0≤x≤1,其中,材料层具有小于1ppm的氯。该层是铁电的,并且可以用作存储器器件中的数据存储层。

[0067]

本教导的一些方面涉及集成电路器件,该集成电路器件包括:存储器单元,包括在源极和漏极之间延伸的沟道、栅电极以及栅电极和沟道之间的铁电层,存储器单元具有泄漏电流和时间依赖性介电击穿速率(tddb速率)。tddb速率定义为泄漏电流的初始值除以泄漏电流从初始值加倍的操作时间。tddb速率小于如果将1ppm的氯添加至铁电层时tddb速率将增加的量。

[0068]

本教导的一些方面涉及形成集成电路器件的方法,该方法包括:使用无氯前体通过原子层沉积形成铁电层。无氯前体可以包括锆(zr)前体、铪前体或这两种类型的前体。

[0069]

本技术的一些实施例提供了一种集成电路器件,包括:材料层,包括hf

x

zr

1-x

o2,其中,0≤x≤1;其中,所述材料层具有小于1ppm的氯。在一些实施例中,所述材料层是数据存储层。在一些实施例中,所述数据存储层包括hfzro2。在一些实施例中,所述数据存储层是无氯的。在一些实施例中,所述数据存储层设置在铁电场效应晶体管中的沟道和栅电极之间。在一些实施例中,所述栅极掩埋在半导体衬底中。在一些实施例中,所述数据存储层位于铁电电容器中。

[0070]

本技术的另一些实施例提供了一种集成电路器件,包括:存储器单元,包括在源极和漏极之间延伸的沟道、栅电极以及所述栅电极和所述沟道之间的铁电层;其中,所述存储器单元具有泄漏电流和与时间依赖性介电击穿速率(tddb速率),其中,所述时间依赖性介电击穿速率定义为所述泄漏电流的初始值除以所述泄漏电流从所述初始值加倍的操作时间;以及时间依赖性介电击穿速率小于如果将1ppm的氯添加至所述铁电层时所述时间依赖性介电击穿速率将增加的量。在一些实施例中,所述铁电层包括hf

x

zr

1-x

o2,其中,0≤x≤1。

在一些实施例中,x=0.5。在一些实施例中,所述铁电层的厚度为1nm至30nm。在一些实施例中,所述铁电层为晶体管结构。

[0071]

本技术的又一些实施例提供了一种形成集成电路器件的方法,所述方法包括:使用无氯前体通过原子层沉积形成铁电层。在一些实施例中,所述无氯前体包括锆(zr)前体。在一些实施例中,所述无氯前体包括铪(hf)前体和锆(zr)前体。在一些实施例中,所述无氯前体还包含铝(al)、硅(si)、镧(la)、钪(sc)、钙(ca)、钡(ba)、钆(gd)或钇(y)的化合物。在一些实施例中,所述无氯前体包括金属化合物,其中氮结合至金属。在一些实施例中,所述无氯前体包括金属化合物,其中碳结合至金属。在一些实施例中,所述无氯前体包括形式为m-(n-r)n的金属化合物,其中,m是金属,r是有机官能团,并且n是整数。在一些实施例中,所述有机官能团是烷烃、烯烃、炔烃、醇、胺、醚、醛、酮、羧酸、酯或酰胺。

[0072]

上面概述了若干实施例的特征,使得本领域技术人员可以更好地理解本发明的方面。本领域技术人员应该理解,它们可以容易地使用本发明作为基础来设计或修改用于实施与本文所介绍实施例相同的目的和/或实现相同优势的其它工艺和结构。本领域技术人员也应该意识到,这种等同构造并不背离本发明的精神和范围,并且在不背离本发明的精神和范围的情况下,本文中它们可以做出多种变化、替换以及改变。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。