1.本发明是关于一种具有光子集成电路的封装结构。更进一步地,本发明涉及一种光学模组内嵌于光子集成电路的封装结构。

背景技术:

2.图1为一种现有的封装结构1的示意图。如图1所示,封装结构1具有芯片10、光学模组20、载体30及电路板40。芯片10与光学模组20相邻地通过例如树脂粘贴在载体30上,材料为陶瓷或硅材的背板41通过例如树脂粘贴在电路板40的背面上,并至少部分从电路板40的开口区域露出,载体30通过例如树脂粘贴固定于从电路板40的开口区域露出的背板41上,而电路板40上的电路则对应地设置在载体30周围。其中,电路板40的开口区域是用来降低芯片10与光学模组20设置于电路板40后的突出高度。

3.在现有的封装结构1中,由于光学模组20的厚度通常高于芯片10的厚度,因此为了设置光学模组20,会通过载体30来同时承载芯片10与光学模组20,而芯片10与光学模组20则与电路板40上的电路通过打线接合。

4.然而,由于芯片10与光学模组20与电路板40上的电路利用打线接合,封装结构1的射频性能(rf performance)会受到接合线长度的影响。亦即,电路板40上的电路、芯片10及光学模组20的设置位置必须较为精确,若相对位置与设计有些微差异,都有可能造成接合线长度的不同,进而使得封装结构1的射频性能受到影响。换言之,在现有的封装结构1中,其设置电路板40上的电路、芯片10及光学模组20时的容错率较低。另外,芯片10及光学模组20粘贴固定于载体30上,载体30粘贴固定于电路板40背面的背板41上,粘贴固定后较难重新分离及结合,也会造成现有的结构难以重工(rework)的问题。

5.更进一步来说,由于芯片10与光学模组20相邻地设置在载体30上,彼此的电信号也可能产生串扰(crosstalk)等问题。另外,在现有的封装结构1中,需要分别对于入射光的光路及出射光的光路设置光纤,而会使得成本提高。

6.上文的“背景技术”说明仅提供背景技术,并未承认上文的“背景技术”说明公开本发明的目标,不构成本发明的背景技术,且上文的“背景技术”的任何说明均不应做为本技术的任一部分。

技术实现要素:

7.本发明的实施例提供一种封装结构,包括一基板、一芯片及一光学模组。芯片具有一光波导结构及一凹部。光波导结构邻设于凹部。凹部面对基板,芯片覆晶接合于基板。光学模组设置于芯片的凹部。

8.在一些实施例中,基板具有一光学模组用凹部,且该光学模组延伸至该光学模组用凹部内。

9.在一些实施例中,光学模组包括一光源及一透镜,光源产生的光线穿过透镜后入射至芯片的光波导结构。

10.在一些实施例中,芯片是覆晶型光子集成电路。

11.在一些实施例中,芯片与一光波导连接组件连接。

12.在一些实施例中,基板具有一光波导连接组件用凹部,且光波导连接组件延伸至光波导连接组件用凹部内。

13.本发明的实施例提供另一种封装结构,包括一基板、一第一芯片、一第二芯片、一第三芯片及一光学模组。第一芯片覆晶接合于基板。第二芯片覆晶接合于基板,并与第一芯片间隔设置。第三芯片设置于第一芯片及第二芯片上。光学模组设置于第三芯片,并位于基板与第三芯片之间。

14.在一些实施例中,第三芯片具有一凹部,其面对基板并位于第一芯片与第二芯片之间,且光学模组位于凹部。

15.在一些实施例中,基板具有一光学模组用凹部,且光学模组延伸至光学模组用凹部内。在一些实施例中,光学模组包括一光源及一透镜,光源产生的光线穿过透镜后入射至第一芯片、第二芯片或第三芯片。

16.在一些实施例中,第三芯片与一光波导连接组件连接。

17.在一些实施例中,基板具有一光波导连接组件用凹部,且光波导连接组件延伸至光波导连接组件用凹部内。

18.在本发明中,封装结构的芯片是通过覆晶接合于基板,且光学模组设置在基板与芯片之间。因此,由于本发明的封装结构的芯片利用覆晶接合来连接,而可避免通过打线接合时的接合线长度而造成射频性能影响的问题。亦即,在本发明的封装结构中,芯片、光学模组及基板的相对位置的容错率高于现有的封装结构。并且,本发明的封装结构将基板、芯片及光学模组封装后,不需要通过载体而可直接与其他电路板连接,换言的,本发明的封装结构与其他电路板较容易进行重新分离及结合,亦即相比于现有的结构较容易进行重工。

19.此外,本发明的封装结构中,光学模组例如内嵌于芯片内,因此可通过将彼此的电信号路径分开,而避免串扰的问题,且不需要分别对于入射光的光路及出射光的光路设置光纤,可使得成本降低。

20.上文已相当广泛地概述本发明的技术特征及优点,从而使下文的本发明详细描述得以获得较佳了解。构成本发明的申请专利范围目标的其它技术特征及优点将描述于下文。本发明所属技术领域中具有通常知识者应了解,可相当容易地利用下文公开的概念与特定实施例可做为修改或设计其它结构或制造方法而实现与本发明相同的目的。本发明所属技术领域中具有本领域技术人员还应了解,这类等效建构无法脱离所附的申请专利范围所界定的本发明的精神和范围。

附图说明

21.参阅详细说明与申请专利范围结合考量附图时,可以更全面了解本技术的公开内容,附图中相同的附图标记指相同的元件。

22.图1为一种现有的封装结构的示意图。

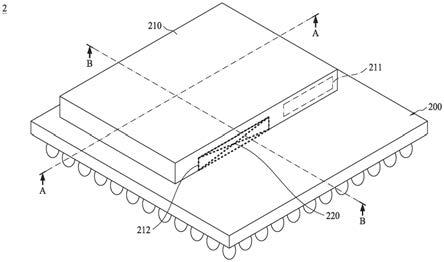

23.图2为本发明的一种封装结构的立体示意图。

24.图3a为沿图2的a-a直线的封装结构的剖面图,图3b为沿图2的b-b直线的封装结构的剖面图。

25.图3c为本发明的一种封装结构与电路板结合的立体示意图,图3d为沿图3c的a-a直线的封装结构的剖面图。

26.图4a为本发明的一种芯片及光学模组的仰视图,图4b为本发明的一种芯片及光学模组的侧视图。

27.图5a为本发明的另一种封装结构的示意图,图5b为如图5a的封装结构与光波导连接组件的连接方式的示意图。

28.图6a为本发明的另一种基板的示意图,图6b为本发明的另一种封装结构的示意图。

29.图7为本发明的另一种封装结构的示意图。

30.图8为本发明的另一种封装结构的示意图。

31.图9为本发明的另一种封装结构的示意图。

32.图10a~图10f为本发明的一种如图5a及图5b的封装结构的制造流程示意图。

33.附图标记说明

34.1、2、5、6、7、8、9

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

封装结构

35.10、210、510、610

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

芯片

36.20、220、520、640、740、840、940 光学模组

37.30

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

载体

38.40、400

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

电路板

39.200、500、600、700、800、900

ꢀꢀꢀꢀ

基板

40.201、501、701

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

凸块或锡球

41.211、511、711

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

光波导结构

42.212、512、612、931

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

凹部

43.213、713

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

微凸块或锡球

44.221

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

光源

45.222

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

透镜

46.502、602

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

光波导连接组件用凹部

47.504、514

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

焊垫

48.603、803、903

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

光学模组用凹部

49.710、810、910

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

第一芯片

50.712、812、912

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

空间

51.720、820、920

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

第二芯片

52.730、830、930

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

第三芯片

[0053]9ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

光波导连接组件

[0054]

91

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

光纤

[0055]eꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

路径

[0056]

l

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

光路。

具体实施方式

[0057]

附图所示的公开内容的实施例或范例是以特定语言描述。应理解此非意图限制本

发明的范围。所述实施例的任何变化或修饰以及本技术所述原理任何进一步应用,对于本发明相关领域的技术人员而言为可正常发生。附图标记可重复于各实施例中,但即使它们具有相同的附图标记,实施例中的特征并非必定用于另一实施例。

[0058]

应理解虽然在本文中可使用第一、第二、第三等用语描述各种元件、组件、区域、层或区段,然而,这些元件、组件、区域、层或区段应不受限于这些用语。这些用语仅用于区分一元件、组件、区域、层或区段与另一区域、层或区段。因此,以下所述的第一元件、组件、区域、层或区段可被称为第二元件、组件、区域、层或区段,而仍不脱离本发明的发明概念的教示内容。

[0059]

本发明所使用的语词仅用于描述特定例示实施例的目的,并非用以限制本发明概念。如本文所使用,单数形式“一”与“该”也用以包含复数形式,除非本文中另有明确指示。应理解说明书中所使用的“包括”一词专指所称特征、整数、步骤、操作、元件或组件的存在,但不排除一或多个其他特征、整数、步骤、操作、元件、组件或其群组的存在。

[0060]

图2为本发明的一种封装结构2的立体示意图,图3a为沿图2的a-a直线的封装结构2的剖面图,图3b为沿图2的b-b直线的封装结构2的剖面图。

[0061]

如图2、图3a及图3b所示,在某些实施例中,封装结构2包括基板200、芯片210及光学模组220。基板200例如是电路板,其具有的电路结构非限制性,例如可以是多层式电路结构、或者其他合适的电路结构。在某些实施例中,在基板200上,相对于芯片210的另一面可以设置有多个凸块或锡球201,以使封装结构2可与其他元件电性连接。

[0062]

芯片210具有光波导结构211及凹部212。光波导结构211邻设于凹部212,凹部212面对基板200。换言的,凹部212位于芯片210与基板200之间,而光波导结构211则位于凹部212的一侧。进一步来说,凹部212的形状非限制性,其可以是长槽状并延伸过芯片210的两侧(如图3a所示,芯片210呈ㄇ字型),或者是凹槽状且没有延伸过芯片210的两侧。另外,须注意的是,光波导结构211的结构非限制性。芯片210利用覆晶(flip chip)接合于基板200。在某些实施例中,多个微凸块或锡球213设置在芯片210与基板200之间,以使芯片210与基板200电性连接。芯片210例如可以是覆晶型光子集成电路(photonic integrated circuit,pic)。

[0063]

光学模组220设置于芯片210的凹部212中。光学模组220位于芯片210与基板200之间,且与芯片210及基板200电性连接。在某些实施例中,光学模组220可以经由芯片210与基板200电性连接,亦即光学模组220设置于芯片210,并经由芯片210覆晶接合于基板200而与基板200电性连接。

[0064]

图4a为本发明的一种芯片210及光学模组220的仰视图,图4b为本发明的一种芯片210及光学模组220的侧视图。如图4a所示,在某些实施例中,光学模组220可以具有光源221及透镜222,光源221及透镜222设置于凹部212中。光源221所产生的光线可沿光路l经由透镜222入射至芯片210的光波导结构211中,并出射至与芯片210相接的外部元件(例如,光纤91)。如图4b所示,光学模组220的光源221例如经由芯片210覆晶接合于基板200而与基板200电性连接(例如,经由路径e)。光源221例如可以是激光二极管(laser diode)或发光二极管(light emitting diode)。

[0065]

综上所述,本发明的封装结构2的芯片210通过覆晶接合于基板200,且光学模组220设置在基板200与芯片210之间。因此,由于封装结构2的芯片210利用覆晶接合来连接,

而可避免通过打线接合时的接合线长度而造成射频性能影响的问题。亦即,在封装结构2中,芯片210、光学模组220及基板200的相对位置的容错率高于现有的封装结构1(如图1所示)。

[0066]

图3c为本发明的一种封装结构2与电路板400结合的立体示意图,图3d为沿图3c的a-a直线的封装结构2的剖面图。如图3c及图3d所示,封装结构2并不需要通过载体固定于电路板400,亦可增加封装结构2的重工的自由度。

[0067]

此外,本发明的封装结构2中,光学模组220例如内嵌于凹部212内,因此可通过使光学模组220的电信号路径(例如,图4b的左侧路径e)与芯片210的电信号路径(例如,图4b的右侧路径e)不同,避免串扰的产生。再者,本发明的封装结构2可不需要分别对于入射光的光路及出射光的光路设置光纤,使得成本降低。

[0068]

图5a为本发明的另一种封装结构5的示意图,图5b为如图5a的封装结构5与光波导连接组件9的连接方式的示意图。在某些实施例中,光波导连接组件9以悬挂在芯片510上的形式与芯片510连接。

[0069]

如图5a及图5b所示,封装结构5包括基板500、芯片510及光学模组520。其中,芯片510及光学模组520与图2、图3a、图3b、图4a、图4b的芯片210及光学模组220的结构类似,于此不再赘述。

[0070]

封装结构5与图2、图3a、图3b、图4a、图4b的封装结构2的差异在于:基板500具有光波导连接组件用凹部502,光波导连接组件用凹部502在俯视视角上与芯片510不重叠,且光波导连接组件用凹部502没有被芯片510所覆盖。然而这是非限制性的,光波导连接组件用凹部502也可以部分被芯片510所覆盖,亦即,光波导连接组件用凹部502至少部分设置于基板500上与芯片510重叠的区域外。

[0071]

因此,封装结构5除具有如封装结构2的上述各种功效外,当光波导连接组件9的尺寸较大,通过基板500的光波导连接组件用凹部502,可使光波导连接组件9以悬挂的形式与芯片510连接时,光波导连接组件9不会受到基板500的影响,而可延伸至基板500的光波导连接组件用凹部502内,从而可避免光波导连接组件9与基板500接触,以让光波导连接组件9的光纤91更准确地与芯片510的光波导结构511对接。需注意的是,光波导连接组件9的尺寸较小(例如,不会延伸至基板500)时,则可不需设置光波导连接组件用凹部502。

[0072]

图6a为本发明的另一种基板600的示意图,图6b为本发明的另一种封装结构6的示意图。

[0073]

如图6a及图6b所示,封装结构6包括基板600、芯片610及光学模组640。其中,芯片610及光学模组640与图2、图3a、图3b、图4a、图4b的芯片210及光学模组220的结构类似,于此不再赘述。

[0074]

封装结构6与图2、图3a、图3b的封装结构2的差异在于:基板600具有光波导连接组件用凹部602及光学模组用凹部603,光波导连接组件用凹部602设置于基板600上与芯片610重叠的区域外,光学模组用凹部603设置于基板600上与芯片610的凹部612重叠的区域,然而这是非限制性的,光波导连接组件用凹部602可以至少部分设置于基板600上与芯片610重叠的区域外,光学模组用凹部603可以至少部分设置于基板600上与芯片610的凹部612重叠的区域。光学模组640设置在芯片610上并延伸至光学模组用凹部603内。需注意的是,于此以光波导连接组件用凹部602及光学模组用凹部603连通为例作说明,然而这是非

限制性的,光波导连接组件用凹部602及光学模组用凹部603也可彼此不连通,例如基板600的一部分在光波导连接组件用凹部602及光学模组用凹部603之间以隔离光波导连接组件用凹部602及光学模组用凹部603。再者,在某些实施例中,也可以仅在基板600上设置光波导连接组件用凹部602或光学模组用凹部603。

[0075]

因此,封装结构6除具有如封装结构2的上述各种功效外,当光波导连接组件9的尺寸较大,通过基板600的光波导连接组件用凹部602,可使光波导连接组件9(如图5b所示)以悬挂的形式与芯片610连接时,光波导连接组件9不会受到基板600的影响,而可延伸至基板600的光波导连接组件用凹部602内,从而可避免光波导连接组件9与基板600接触,以让光波导连接组件9的光纤91(如图5b所示)更准确地与芯片610的光波导结构611对接。通过基板600的光学模组用凹部603,例如可减少芯片610的凹部612的所需深度,也可以增加基板600与芯片610之间容纳光学模组640的容纳空间。换句话说,芯片610的凹部612与基板600的光学模组用凹部603可以互相匹配来形成容纳光学模组640的容纳空间,由此可以依要求对凹部612或光学模组用凹部603的深度作调整(例如,使凹部612变浅,并相应地使光学模组用凹部603变深等),并同时维持容纳光学模组640的所需空间。

[0076]

图7为本发明的另一种封装结构7的示意图。在某些实施例中,封装结构7包括基板700、第一芯片710、第二芯片720、第三芯片730及光学模组740。基板700例如是电路板,其具有的电路结构非限制性,例如可以是多层式电路结构、或者其他合适的电路结构。在某些实施例中,在基板700上,相对于第一芯片710、第二芯片720及第三芯片730的另一面可以设置有多个凸块或锡球701,以使基板700可与其他元件电性连接。

[0077]

第一芯片710、第二芯片720及第三芯片730可以是相同芯片或不同芯片。第一芯片710覆晶接合于基板700,第二芯片720覆晶接合于基板700,并与第一芯片710间隔设置,第三芯片730设置于第一芯片710及第二芯片720上。在某些实施例中,第三芯片730覆晶接合于第一芯片710及第二芯片720。在某些实施例中,第三芯片730与第一芯片710及/或第二芯片720电性连接。

[0078]

在某些实施例中,第一芯片710及第二芯片720可以是空白芯片(dummy chip),用来与第三芯片730共同形成空间712。在某些实施例中,第三芯片730堆叠在第一芯片710及第二芯片720上,且未与第一芯片710及/或第二芯片720电性连接。在另外一些实施例中,第一芯片710、第二芯片720及第三芯片730可以是具有不同功能的芯片,同时共同形成空间712。第一芯片710、第二芯片720及第三芯片730的任一者或者全部可以具有光波导结构711。在本示例中,以第一芯片710具有光波导结构711为例作说明,但这是非限制性的。光波导结构711邻设于空间712,空间712面对基板700。换言之,空间712位在基板700、第一芯片710、第二芯片720及第三芯片730与基板700之间,而光波导结构711位于空间712的一侧(例如,设置于第一芯片710)。另外,须注意的是,光波导结构711的结构非限制性。在某些实施例中,多个微凸块或锡球713设置在第一芯片710、第二芯片720与基板700之间,以使第一芯片710、第二芯片720与基板700电性连接。第一芯片710、第二芯片720及第三芯片730例如可以是覆晶型光子集成电路。

[0079]

光学模组740设置于第三芯片730,并位于基板700与第三芯片730之间。光学模组740位于第一芯片710、第二芯片720及第三芯片730形成的空间712内,与第三芯片730及基板700电性连接。光学模组740可以包括光源及透镜,光源产生的光线穿过透镜后入射至第

一芯片710、第二芯片720或第三芯片730。光学模组740与图2、图3a、图3b、图4a、图4b的光学模组220的结构类似,于此不再赘述。

[0080]

综上所述,本发明的封装结构7通过第一芯片710、第二芯片720及第三芯片730形成空间712,且光学模组740设置在空间712。因此,由于封装结构7的第一芯片710、第二芯片720及第三芯片730可以利用覆晶接合来连接,而可避免通过打线接合时的接合线长度而造成射频性能影响的问题。亦即,在封装结构7中,第一芯片710、第二芯片720、第三芯片730、光学模组740及基板700的相对位置的容错率高于现有的封装结构1(如图1所示)。并且,封装结构7并不需要通过载体固定于电路板(未图示),也可增加封装结构7的重工的自由度。

[0081]

此外,本发明的封装结构7中,光学模组740例如内嵌于第一芯片710、第二芯片720及第三芯片730形成的空间712内,因此可通过使光学模组740的电信号路径与第一芯片710、第二芯片720及第三芯片730的电信号路径不同,避免串扰的产生。再者,本发明的封装结构2可不需要分别对于入射光的光路及出射光的光路设置光纤,使得成本降低。

[0082]

图8为本发明的另一种封装结构8的示意图。如图8所示,封装结构8包括基板800、第一芯片810、第二芯片820、第三芯片830及光学模组840。其中,第一芯片810、第二芯片820、第三芯片830及光学模组840与图7的第一芯片710、第二芯片220、第三芯片730及光学模组740的结构类似,于此不再赘述。

[0083]

封装结构8与图7的封装结构7的差异在于:基板800具有光学模组用凹部803,光学模组用凹部803设置于基板800上与第一芯片810、第二芯片820及第三芯片830形成的空间812重叠的区域。然而这是非限制性的,光学模组用凹部803也可以至少部分设置于基板800上与第一芯片810、第二芯片820及第三芯片830形成的空间812重叠的区域。

[0084]

因此,封装结构8除具有如封装结构7的上述各种功效外,通过基板800的光学模组用凹部803与空间812重叠的区域,例如可以增加基板800、第一芯片810、第二芯片820及第三芯片830之间容纳光学模组840的容纳空间。进一步地,由此可以依要求对第一芯片810及第二芯片820的厚度作调整(例如,使第一芯片810及第二芯片820变薄浅,并相应地使光学模组用凹部803变深等),并同时维持容纳光学模组840的所需空间。

[0085]

图9为本发明的另一种封装结构9的示意图。如图9所示,封装结构9包括基板900、第一芯片910、第二芯片920、第三芯片930及光学模组940。其中,第一芯片910、第二芯片920及光学模组940与图7的第一芯片910、第二芯片920及光学模组940的结构类似,于此不再赘述。

[0086]

封装结构9与图7、8的封装结构7、8的差异在于:基板900具有光学模组用凹部903,第三芯片930也具有凹部931。光学模组用凹部903设置于基板900上与第三芯片930的凹部931重叠的区域,然而这是非限制性的,光学模组用凹部903也可以至少部分设置于基板900上与第三芯片930的凹部931重叠的区域。

[0087]

因此,封装结构9除具有如封装结构7、8的上述各种功效外,通过第三芯片930也具有凹部931,例如可以增加基板900、第一芯片910、第二芯片920及第三芯片930之间容纳光学模组940的容纳空间。进一步地,由此可以依要求对第一芯片910及第二芯片920的厚度作调整(例如,使第一芯片910及第二芯片920变薄浅,并相应地使光学模组用凹部903及凹部931变深等),并同时维持容纳光学模组940的所需空间。

[0088]

另外,值得一提的是,如图6a的基板600具有光波导连接组件用凹部602,图7、图8

及图9的基板700、800、900也可分别具有光波导连接组件用凹部(图未示),且使光波导连接组件用凹部分别至少部分设置于基板700、800、900上与第一芯片710、810、910、第二芯片820、820、920及第三芯片730、830、930重叠的区域外,以使光波导连接组件9(如图5b所示)可延伸至光波导连接组件用凹部内。

[0089]

图10a~图10f为本发明的一种如图5a及图5b的封装结构5的制造流程示意图。如图10a所示,于芯片510上可以先形成多个焊垫514及多个微凸块或锡球513。如图10b所示,接着,于芯片510上蚀刻形成凹部512。蚀刻方式例如可以是干式蚀刻或湿式蚀刻。

[0090]

值得一提的是,若是如图7、8所示的封装结构7、8,这些芯片上可以不需要形成凹部,而可以通过将这些芯片彼此接合来形成与凹部相似的空间。若是如图9所示的封装结构9,则可以先于第三芯片930上形成凹部931后,再将第三芯片930与第一芯片910及第二芯片920接合。

[0091]

如图10c所示,将光学模组520设置于凹部512内。光学模组520例如可以具有光源521及透镜522,光学模组520于凹部512内的设置位置并非限制性。如图10d所示,将芯片510覆晶接合于基板500,基板500可以先设置有光波导连接组件用凹部502。值得一提的是,基板可如图2的基板200不具有凹部,也可以如图6a的基板600,具有光波导连接组件用凹部602及光学模组用凹部603。关于光波导连接组件用凹部602及光学模组用凹部603已于图6a、图6b中详述,于此不再赘述。

[0092]

如图10e所示,在基板500上相对于芯片的另一面设置多个焊垫504及多个凸块或锡球501,以使封装结构5(如图5a或图10f所示)可与其他元件电性连接。如图10f所示,将光波导连接组件9与封装结构5连接。在某些实施例中,光波导连接组件9可以利用悬挂的形式设置于芯片510上,并延伸至基板500的光波导连接组件用凹部502内。

[0093]

需注意的是,上述流程步骤并非限制性,依不同需要可有不同的顺序,依不同结构设计也可以增加或减少流程步骤。

[0094]

虽然已详述本发明及其优点,然而应理解可进行各种变化、取代与替代而不脱离申请专利范围所定义的本发明的精神与范围。例如,可用不同的方法实施上述的许多制造方法,并且以其他制造方法或其组合替代上述的许多制造方法。

[0095]

再者,本技术的范围并不受限于说明书中所述的制造方法、机械、制造、物质组成物、手段、方法与步骤的特定实施例。该领域的技术人员可自本发明的公开内容理解可根据本发明而使用与本文所述的对应实施例具有相同功能或是达到实质相同结果的现存或是未来发展的制造方法、机械、制造、物质组成物、手段、方法、或步骤。据此,这些制造方法、机械、制造、物质组成物、手段、方法、或步骤包含于本技术的申请专利范围内。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。