1.本发明涉及半导体领域,特别是涉及一种半导体静电保护器件。

背景技术:

2.随着半导体制程越来越先进,半导体器件越来越小,结深越来越浅,氧化层也越来越薄,静电保护器件的可靠性面临的挑战越来越大。

3.目前,动态随机存取存储器的速度变得越来越快,这就要求i/o接口不仅要有可靠的静电保护能力,同时要有比较小的寄生电容,现有技术中的静电保护器件的寄生电容已经越来越难以满足要求。

技术实现要素:

4.基于此,有必要针对上述问题,提供一种半导体静电保护器件。

5.一种半导体静电保护器件,包括:

6.衬底,所述衬底内形成有第一导电类型的深阱区;

7.第一二极管,所述第一二极管的阳极接第一电压,所述第一二极管的阴极接输入输出端;

8.第二二极管,所述第二二极管的阳极接所述输入输出端,所述第二二极管的阴极接第二电压;

9.所述第一二极管和所述第二二极管均位于所述第一导电类型的深阱区内。

10.在其中一个实施例中,保护环,所述深阱区位于所述保护环内,所述保护环具有第二导电类型。

11.在其中一个实施例中,还包括:第一导电类型的掺杂阱区和第二导电类型的掺杂阱区,所述第一导电类型的掺杂阱区和第二导电类型的掺杂阱区均位于所述深阱区内,所述第一二极管位于所述第一导电类型的掺杂区,所述第二二极管位于所述第二导电类型的掺杂区。

12.在其中一个实施例中,所述第一导电类型的掺杂阱区和第二导电类型的掺杂阱区相邻接。

13.在其中一个实施例中,所述第一二极管包括第一导电类型的第一掺杂区和第二导电类型的第二掺杂区,所述第一掺杂区为所述第一二极管的阳极,所述第二掺杂区为所述第一二极管的阴极;

14.所述第二二极管包括第二导电类型的第三掺杂区和第一导电类型的第四掺杂区,所述第四掺杂区为所述第二二极管的阳极,所述第三掺杂区为所述第二二极管的阴极。

15.在其中一个实施例中,所述第一掺杂区和所述第二掺杂区沿第一方向交替间隔排布;所述第三掺杂区和所述第四掺杂区沿所述第一方向交替间隔排布。

16.在其中一个实施例中,所述第一掺杂区围成多个第一环形,所述第二掺杂区位于所述第一环形内;所述第三掺杂区围成多个第二环形,所述第四掺杂区位于所述第二环形

内。

17.在其中一个实施例中,多个所述第二掺杂区沿第二方向间隔排布;多个所述第四掺杂区沿所述第二方向间隔排布。

18.在其中一个实施例中,所述第一掺杂区与所述第二掺杂区之间、所述第一掺杂区与所述第三掺杂区之间、所述第三掺杂区与所述第四掺杂区之间,均布置浅沟槽隔离结构。

19.在其中一个实施例中,所述第一电压为电源电压,所述第二电压为接地电压。

20.在其中一个实施例中,所述第一电压为接地电压,所述第二电压为电源电压。

21.在其中一个实施例中,所述第一二极管的数量为至少两个,且依次串接;

22.所述第二二极管的数量为至少两个,且依次串接。

23.上述方案中,当芯片暴露于静电环境时,静电电荷会通过第一二极管和/或第二二极管泄放出去,避免了芯片内部的半导体器件被静电电荷所产生高电压所损伤;同时由于第一二极管和第二二极管均位于深阱区内部,第一二极管与第二二极管被深阱区所隔离,可以避免对外部器件的干扰;且第一二极管与第二二极管寄生电容较小,因此在具有良好的静电保护能力的前提下,也能够满足动态随机存取存储器对接口寄生电容的越来越高的要求。

附图说明

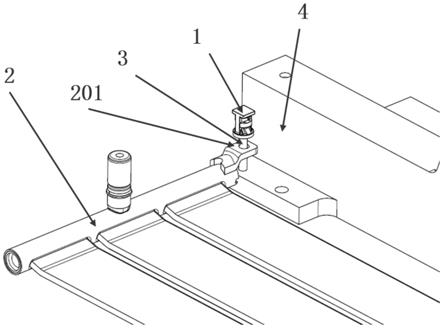

24.图1为本发明一个实施例中展示半导体静电保护器件的俯视图;

25.图2为图1中沿aa’方向的截面结构示意图;

26.图3为本发明另一个实施例中展示半导体静电保护器件的俯视图;

27.图4为本发明又一个实施例中展示的半导体静电保护器件的截面结构示意图。

28.附图标记:10、衬底;12、深阱区;13、保护环;14、第一导电类型的掺杂阱区;15、第二导电类型的掺杂阱区;16、浅沟槽隔离结构;20、第一二极管;201、第一掺杂区;202、第二掺杂区;21、第二二极管;211、第三掺杂区;212、第四掺杂区;22、第五掺杂区。

具体实施方式

29.为了便于理解本发明,下面将参照相关附图对本发明进行更全面的描述。附图中给出了本发明的首选实施例。但是,本发明可以以许多不同的形式来实现,并不限于本文所描述的实施例。相反地,提供这些实施例的目的是使对本发明的公开内容更加透彻全面。

30.除非另有定义,本文所使用的所有的技术和科学术语与属于本发明的技术领域的技术人员通常理解的含义相同。本文中在本发明的说明书中所使用的术语只是为了描述具体的实施例的目的,不是旨在于限制本发明。本文所使用的术语“及/或”包括一个或多个相关的所列项目的任意的和所有的组合。

31.在本发明的描述中,需要理解的是,术语“上”、“下”、“竖直”、“水平”、“内”、“外”等指示的方位或位置关系为基于附图所示的方法或位置关系,仅是为了便于描述本发明和简化描述,而不是指示或暗示所指的装置或元件必须具有特定的方位、以特定的方位构造和操作,因此不能理解为对本发明的限制。

32.接口电路为了在具有良好的静电保护性能的前提下,还具有较小的寄生电容,如图1和图2所示,本发明提供了一种半导体静电保护器件,包括:衬底10,衬底10内形成有第

一导电类型的深阱区12;第一二极管20,第一二极管20的阳极接第一电压,第一二极管20的阴极接输入输出端;第二二极管21,第二二极管21的阳极接输入输出端,第二二极管21的阴极接第二电压;第一二极管20和第二二极管21均位于第一导电类型的深阱区12内。

33.第一二极管20的阳极接第一电压,阴极接输入输出端,第二二极管21的阳极接输入输出端,阴极接第二电压,因此,当芯片位于静电环境中时,瞬时的静电电荷会通过输入输出引脚进入芯片的接口电路,当通过输入输出引脚进入芯片内部的静电电荷产生的电压低于第一二极管20与第二二极管21的反向击穿电压或正向导通电压时,不会对静电保护器件和芯片内部电路造成损伤;当静电电荷产生的电压超过第一二极管20与第二二极管21的正向导通电压或反向击穿电压时,从而使得第一二极管20和/或反向击穿或正向导通,进而将静电电荷泄放出去,避免了芯片内部的半导体器件被静电电荷所损伤。由于第一二极管20和第二二极管21均位于深阱区12内,第一二极管20与第二二极管21被深阱区12所隔离,可以避免和芯片内部其他半导体器件的相互干扰;且第一二极管20与第二二极管21电容较小,因此在具有良好的静电泄放性能的前提下,其寄生电容大小也能够满足动态随机存取存储器越来越高的要求。

34.在一个可选的实施例中,衬底10材料可以为硅、锗、gaas(砷化镓)、inp(磷化铟)或gan(氮化镓)等,即衬底10可以为硅衬底、锗衬底、gaas衬底、inp衬底或gan衬底;本实施例中,衬底10可以为硅衬底。

35.在一个示例中,深阱区12可以为n型深阱区12或p型深阱区12,在一个可选的实施例中,深阱区12为n型深阱区12。

36.在一个可选的实施例中,深阱区12内形成有第五掺杂区22,第五掺杂区22为第二导电类型,即与深阱区12为同一导电类型,可以为n型重掺杂区,第五掺杂区22可以作为深阱区12的引出区。第五掺杂区22呈环形,第一二极管20和第二二极管21均位于第五掺杂区22形成的环内。

37.在一个可选的实施例中,第一电压为电源电压vdd,第二电压为接地电压vss。即第一二极管20的阳极接电源端,阴极接输入输出端,第二二极管21的阳极接输入输出端,阴极接接地端,因此,当输入输出端与电源端之间发生静电时,且静电电荷产生的电压大于第一二极管20的反向击穿电压时,静电电荷从第一二极管20泄放出去;当输入输出端与接地端之间发生静电时,且当静电电荷产生的电压大于第二二极管21的正向导通电压时,静电电荷从第二二极管21泄放出去。

38.在另一个可选的实施例中,第一电压为接地电压vss,第二电压为电源电压vdd。即第一二极管20的阳极接接地端,阴极接输入输出端,第二二极管21的阳极接输入输出端,阴极接电源端,因此,当输入输出端与电源端之间发生静电时,且静电电荷产生的电压大于第一二极管20的正向导通电压时,静电电荷从第一二极管20泄放出去;当输入输出端与接地端之间发生静电时,且当静电电荷产生的电压大于第二二极管21的反向击穿电压时,静电电荷从第二二极管21泄放出去。

39.如图2所示,在一个可选的实施例中,第一二极管20中的第一掺杂区201均通过引线外接第一电压,第一电压例如可以是接地电压vss,第一二极管20中的第二掺杂区202均通过引线外接输入输出端(图中为i/o端);第二二极管21中的第四掺杂区212均通过引线外接输入输出端(图中为i/o端),第二二极管21中的第三掺杂区211均通过引线外接第二电

压,第二电压例如可以是电源电压vss。同时,第一二极管20和第二二极管21外围的第五掺杂区22外接第二电压,第五掺杂区22外围的保护环13外接第一电压。

40.在一个可选的实施例中,衬底10内还包括第一导电类型的掺杂阱区14和第二导电类型的掺杂阱区15,第一导电类型的掺杂阱区14和第二导电类型的掺杂阱区15均位于深阱区12内,第一二极管20位于第一导电类型的掺杂区,第二二极管21位于第二导电类型的掺杂阱区15。第一导电类型的掺杂阱区14和第二导电类型的掺杂阱区15均可以通过对衬底10进行离子注入的方式形成。第一二极管20包括第一导电类型的第一掺杂区201和第二导电类型的第二掺杂区202,第一掺杂区201为第一二极管20的阳极,第二掺杂区202为第一二极管20的阴极;第二二极管21包括第二导电类型的第三掺杂区211和第一导电类型的第四掺杂区212,第四掺杂区212为第二二极管21的阳极,第三掺杂区211为第二二极管21的阴极。

41.在一个可选的实施例中,第一导电类型为p型,即,第一导电类型的掺杂阱区14为p型掺杂阱区,第二导电类型为n型,即第二导电类型的掺杂阱区15为n型掺杂阱区,第一二极管20位于p型掺杂阱区内,第二二极管21位于n型掺杂阱区内。第一二极管20包括p型的第一掺杂区201和n型的第二掺杂区202,第一掺杂区201和第二掺杂区202均位于p型掺杂阱区内部,且第一掺杂区201外接第一电压,第二掺杂区202外接输入输出电压;第二二极管21包括n型的第三掺杂区211和p型的第四掺杂区212,第三掺杂区211和第四掺杂区212位于n型掺杂阱区的内部,且第三掺杂区211外接第二电压,第四掺杂区212外接输入输出电压。

42.在一个示例中,第一二极管20包括的p型的第一掺杂区201和n型的第二掺杂区202的数量可以根据实际需要进行设定,第一二极管20包括的p型的第一掺杂区201和n型的第二掺杂区202的数量可以均为1个,也可以均为多个;同样,第二二极管21包括n型的第三掺杂区211和p型的第四掺杂区212的数量也可以为1个或多个;本实施例中,第一二极管20包括的p型的第一掺杂区201和n型的第二掺杂区202的数量可以均为多个,第二二极管21包括n型的第三掺杂区211和p型的第四掺杂区212的数量也可以均为多个,这样第一二极管20及第二二极管21就包括了多个并联的子二极管,从而可以提高静电保护器件的静电泄放能力。

43.在一个可选的实施例中,第一掺杂区201和第二掺杂区202沿第一方向间隔排布;第三掺杂区211和第四掺杂区212沿第一方向间隔排布。即,在静电保护器件包括至少一个第一二极管20和至少一个第二二极管21时,第一掺杂区201和第二掺杂区202沿着第一方向间隔排布,第三掺杂区211和第四掺杂区212沿着第一方向间隔排布。

44.在一个可选的实施例中,如图1所示,位于一个第二掺杂区202两侧的第一掺杂区201于两端相连,形成一个环绕第二掺杂区202的第一环形,第二掺杂区202位于第一环形内并与第一环形的内壁存在间距,并不与第一环形接触;位于一个第四掺杂区212两侧的第三掺杂区211于两端相连,形成环绕第四掺杂区212的第二环形,第四掺杂区212位于第二环形内并与第二环形的内壁之间存在间距,并不与第二环形接触。

45.在一个可选的实施例中,第一掺杂区201与第二掺杂区202之间、第一掺杂区201与第三掺杂区211之间、第三掺杂区211与第四掺杂区212之间,均设有浅沟槽隔离结构16。即,第二掺杂区202与第一环形之间有浅沟槽隔离结构16,,隔离第二掺杂区202与第一环形,第四掺杂区212与第二环形之形成有浅沟槽隔离结构16,隔离第四掺杂区212与第二环形之间。

46.在一个可选的实施例中,第一导电类型的掺杂阱区14和第二导电类型的掺杂阱区15相邻接,即图2中所示的的p型掺杂区与n型掺杂区相邻接,此时靠近第二导电类型的掺杂阱区15的第一掺杂区201与靠近第一导电类型的掺杂阱区14的第三掺杂区211相互靠近,但第一掺杂区201于第三掺杂区211之间存在间距,两者之间同样形成有浅沟槽隔离结构16,浅沟槽隔离结构16能够隔离第一掺杂区201与第三掺杂区211。

47.在一个可选的实施例中,沿第二方向包括多个第二掺杂区202,即多个第二掺杂区202沿第二方向间隔排布;沿第二方向包括多个第四掺杂区212,即多个第四掺杂区212沿第二方向间隔排布。第二方向可以与第一方向相垂直,沿第二方向呈一行排布的多个第二掺杂区202均位于同一个第一环形内,沿第二方向呈一行排布的多个第四掺杂区212均位于同一个第二环形内,当第一环形内存在多个排列呈一行的第二掺杂区202时,静电电荷的泄放能够较为均匀的分摊在第一环形内的各个第二掺杂区202上,静电电荷泄放较为均匀;同理,当第二环形内存在多个排列呈一行的第四掺杂区212时,静电电荷的泄放能够较为均匀的分摊在第二环形内的各个第四掺杂区212上,静电电荷泄放较为均匀。

48.如图3所示,在其他可选的实施例中,第一环形内可仅存在有一呈长条状的第二掺杂区202,第二环形内可仅存在有一呈长条状的第四掺杂区212,在此实施例中,静电电荷的泄放较为集中,但这样的设置提高了静电保护器件的泄放能力。

49.在一个可选的实施例中,半导体静电保护器件,还包括:保护环13,深阱区12位于保护环13内,保护环13具有第二导电类型,保护环13可以为p型,保护环13形成于深阱区12的外围,环绕深阱区12,同时环绕第五掺杂区22。保护环13能够阻止少子在保护环13的内外移动,从而减少保护环13外的半导体器件和保护环13内的静电保护器件之间的相互影响。

50.在一个可选的实施例中,第一掺杂区201和第二掺杂区202沿第一方向交替间隔排布;第三掺杂区211和第四掺杂区212沿第一方向交替间隔排布。即,在半导体静电保护器件包括至少两个第一二极管20和至少两个第二二极管21时,第一掺杂区201和第二掺杂区202沿着第一方向交替间隔排布,从而形成串接的若干第一二极管20,第三掺杂区211和第四掺杂区212沿着第一方向交替间隔排布,从而形成串接的若干第二二极管21。

51.在一个可选的实施例中,第一掺杂区201围成多个第一环形,第二掺杂区202位于第一环形内;第三掺杂区211围成多个第二环形,第四掺杂区212位于第二环形内。

52.如图4所示,在一个可选的实施例中,第一二极管20的数量为至少两个,且依次串接,可以为2个、3个或更多个;第二二极管21的数量为至少两个,且依次串接,可以为2个、3个或更多个,但上述数值仅为具体实施例中的示例,第一二极管20的数量和第二二极管21的数量不以上述数值为限制。以第一二极管20为例,若半导体静电保护器件内包含两个第一二极管20,则两个第一二极管20串联于第一电压和输入输出电压之间,因此导通或反向击穿两个第一二极管20的静电电荷产生的电压为两个第一二极管20导通电压或反向击穿之和,第二二极管21同理。通过改变第一二极管20和第二二极管21的数量,第一二极管20的阳极及第二二极管21的阴极所接电压可以互换,这时第一二极管20及第二二极管21二者中反接的一个在正常工作是不会被导通,只有静电电荷产生的电压大于反接的所有二极管的导通电压之和才会导通,这使得本发明的静电保护器件能够将静电电荷产生的电压钳位至多个第一二极管20的导通电压之和。

53.在一个可选的实施例中,如图4所示,位于第一导电类型的掺杂阱区14最左端的第

一二极管20中的第一掺杂区201均外接第一电压,例如第一电压为vss,其第二掺杂区202均通过引线与第一导电类型的掺杂阱区14右端第一二极管20内的第一掺杂区201电连接;第一导电类型的掺杂阱区14右端第一二极管20内的第二掺杂区202则通过引线与输入输出端i/o电连接。位于第二导电类型的掺杂阱区15左端的第二二极管21内的第四掺杂区212均通过引线与输入输出端i/o电连接,其第三掺杂区211均与位于第二导电类型的掺杂阱区15右端的第二二极管21内的第四掺杂区212电连接;位于第二导电类型的掺杂阱区15右端的第二二极管21内的第三掺杂区211均通过引线外接第二电压,例如第二电压为vdd。同时,保护环13外接第一电压vss,第五掺杂区22外接第二电压vdd。

54.通过上述技术方案,当芯片暴露于静电环境时,若进入芯片输入输出管脚的静电电荷产生的电压超过了第一二极管20和/或第二二极管21的反向击穿电压或正向导通电压,静电电荷会通过第一二极管20和/或第二二极管21泄放出去,避免了芯片的内部电路被静电电荷所损伤,同时由于第一二极管20和第二二极管21均位于深阱区12内部,因此第一二极管20与第二二极管21被深阱区12所隔离,可以避免对芯片内部电路的干扰,且第一二极管20与第二二极管21的寄生电容较小,能够满足动态随机存取存储器对输入输出管脚越来越高的要求。

55.以上所述实施例的各技术特征可以进行任意的组合,为使描述简洁,未对上述实施例中的各个技术特征所有可能的组合都进行描述,然而,只要这些技术特征的组合不存在矛盾,都应当认为是本说明书记载的范围。

56.以上所述实施例仅表达了本发明的几种实施方式,其描述较为具体和详细,但并不能因此而理解为对发明专利范围的限制。应当指出的是,对于本领域的普通技术人员来说,在不脱离本发明构思的前提下,还可以做出若干变形和改进,这些都属于本发明的保护范围。因此,本发明专利的保护范围应以所附权利要求为准。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。