半导体装置

1.相关申请的交叉引用

2.本技术要求于2020年7月31日在韩国知识产权局提交的韩国专利申请no.10-2020-0095799的优先权,其公开内容通过引用整体合并于此。

技术领域

3.本发明构思涉及半导体装置和设计半导体装置的方法。

背景技术:

4.已经开发了具有在单个封装件中安装的多个半导体装置的系统级封装(sip)。然而,sip可能由于多个半导体装置而具有增大的尺寸,并且可能难以实现多个半导体装置之间的高速通信。具有使用贯穿硅通路(tsv)的垂直堆叠的多个半导体装置的3d半导体装置的开发可以减小半导体装置在封装件中所占据的面积,并且可以提供半导体装置之间的高速通信。

技术实现要素:

5.本发明构思的实施例包括具有tsv的半导体装置的通信速度增加的半导体装置以及设计半导体装置的方法。

6.根据本发明构思的实施例,一种半导体装置包括设置在半导体衬底上并且彼此间隔开的第一集成电路和第二集成电路。布线结构设置在所述半导体衬底上并且被配置为将所述第一集成电路和所述第二集成电路电连接。第一tsv区域和第二tsv区域设置在所述第一集成电路和所述第二集成电路之间。所述第一tsv区域和所述第二tsv区域分别包括穿过所述半导体衬底的多个第一tsv结构和多个第二tsv结构。所述布线结构在所述第一tsv区域和所述第二tsv区域之间穿过。

7.根据本发明构思的实施例,一种半导体装置包括半导体衬底,所述半导体衬底包括导电区域。半导体结构位于所述半导体衬底上。所述半导体结构包括被配置为电连接到所述导电区域的多个单独器件和被配置为电连接到所述多个单独器件的布线结构。多个tsv结构穿过所述半导体衬底和所述半导体结构的至少局部部分。所述多个tsv结构在平行于所述半导体衬底的上表面的第一方向上布置。所述多个单独器件包括在垂直于所述第一方向的第二方向上通过所述多个tsv结构间隔开的多个第一单独器件和多个第二单独器件。所述布线结构在所述第二方向上在所述多个tsv结构之间穿过。所述布线结构被配置为将所述多个第一单独器件中的每个第一单独器件的至少局部部分电连接到所述多个第二单独器件中的相应第二单独器件的至少局部部分。

8.根据本发明构思的实施例,一种半导体装置包括彼此间隔开的第一集成电路和第二集成电路。布线结构被配置为将所述第一集成电路和所述第二集成电路电连接。多个tsv区域设置在所述第一集成电路和所述第二集成电路之间。所述多个tsv区域在第一方向上彼此间隔开并且包括以矩阵形式布置的多个tsv结构。掩埋元件设置在所述多个tsv区域的

至少局部部分中。所述掩埋元件被配置为电连接到所述多个tsv结构的至少局部部分。所述布线结构在垂直于所述第一方向的第二方向上在所述多个tsv区域之间穿过。

9.根据本发明构思的实施例,一种设计半导体装置的方法包括:在半导体装置的区域内确定输入/输出区域、第一集成电路区域、第二集成电路区域、第一tsv区域和第二tsv区域的位置。分别在所述第一tsv区域和所述第二tsv区域中设置多个第一tsv结构和多个第二tsv结构。分别在所述第一集成电路区域和所述第二集成电路区域中设置硬核。分别在所述第一集成电路区域和所述第二集成电路区域中设置多个第一单元和多个第二单元。所述多个第一单元和所述多个第二单元不与所述硬核交叠。布线结构设置在所述第一tsv区域和所述第二tsv区域之间并且在所述第一tsv区域和所述第二tsv区域之间穿过。所述布线结构将所述硬核、所述多个第一单元和所述多个第二单元的至少局部部分电连接。

10.根据本发明构思的实施例,一种半导体装置包括设置在半导体衬底上并且彼此间隔开的多个集成电路。多个tsv区域彼此间隔开并且设置在所述多个集成电路的相邻的集成电路之间。所述多个tsv区域包括穿过所述半导体衬底的多个tsv结构。布线结构设置在所述半导体衬底上并且在所述多个tsv区域中的最靠近所述布线结构的相邻的tsv区域之间穿过。所述布线结构被配置为将所述多个集成电路电连接。

附图说明

11.通过以下结合附图对本发明构思的实施例的详细描述,将更加清楚地理解本发明构思的以上以及其他方面、特征和优点,在附图中:

12.图1a是示出了根据本发明构思的实施例的半导体装置的透视图和放大局部透视图;

13.图1b是示出了根据本发明构思的实施例的沿着图1a的线i-i'截取的半导体装置的截面图;

14.图1c是示出了根据本发明构思的实施例的沿着图1a的线ii-ii'截取的半导体装置的截面图;

15.图2a至图2b是示出了根据本发明构思的实施例的在图1b中示出的一些组件的截面图;

16.图3a至图3c是示出了根据本发明构思的实施例的半导体装置的组件的一部分的局部放大图;

17.图4是示出了根据本发明构思的实施例的半导体装置的透视图和放大局部透视图;

18.图5是示出了根据本发明构思的实施例的在图4的半导体装置中包括的组件的一部分的布局图;

19.图6是示出了根据本发明构思的实施例的半导体装置的透视图;

20.图7是示出了根据本发明构思的实施例的半导体装置的透视图;

21.图8是示出了根据本发明构思的实施例的半导体装置的透视图;

22.图9是示出了根据本发明构思的实施例的半导体装置的透视图;以及

23.图10是示出了根据本发明构思的实施例的设计3维半导体装置的方法的流程图。

具体实施方式

24.在下文中,将参考附图描述实施例。

25.图1a是示出了根据本发明构思的实施例的半导体装置100a的透视图和放大局部透视图。图1b是沿着图1a的线i-i'截取的截面图,并且图1c是沿着图1a的线ii-ii'截取的截面图。

26.参考图1a,半导体装置100a可以包括主体10、多个集成电路20、布线结构30和多个tsv结构40。如在图1b的实施例中所示,主体10可以包括半导体衬底110以及位于稍后将描述的半导体衬底110上的第一半导体结构120和第二半导体结构130。

27.多个集成电路20形成在主体10中,并且可以彼此间隔开预定距离。例如,多个集成电路20可以包括彼此间隔开的第一集成电路20-1和第二集成电路20-2。例如,如在图1a的实施例中所示,第一集成电路20-1和第二集成电路20-2可以在沿着与半导体衬底110的上表面平行的y轴(在下文中,被称为“y方向”)延伸的第二方向上彼此间隔开。在实施例中,第一集成电路20-1和第二集成电路20-2可以包括逻辑电路或存储电路(或存储块),逻辑电路包括逻辑单元,存储电路包括存储单元。

28.例如,在实施例中,第一集成电路20-1可以包括多个第一逻辑单元21-1,并且第二集成电路20-2可以包括多个第二逻辑单元21-2。彼此间隔开(例如,在y方向上)的多个第一逻辑单元21-1和多个第二逻辑单元21-2可以通过布线结构30彼此电连接。在实施例中,第一集成电路20-1和第二集成电路20-2可以包括诸如中央处理单元(cpu)、图形处理单元(gpu)和现场可编程门阵列(fpga)、数字信号处理器(dsp)、加密处理器、微处理器、微控制器、模数转换器、专用集成电路(asic)等的逻辑电路。然而,本发明构思的实施例不限于此。

29.布线结构30可以将彼此分开的多个集成电路20电连接。布线结构30可以在沿第一方向布置的多个tsv结构40之间穿过,第一方向沿着与半导体衬底110的上表面平行并且垂直于y方向的x轴(在下文中,被称为“x方向”)延伸。布线结构30将彼此间隔开的多个集成电路20电连接。布线结构30可以在彼此间隔开(例如,在x方向上)的多个tsv区域40r之间穿过,从而通过相对最短的距离连接第一集成电路20-1和第二集成电路20-2。例如,如在图1a中的放大局部透视图中所示,布线结构30在多个tsv区域40r中的彼此相邻(例如,在x方向上)的第一tsv区域40r1和第二tsv区域40r2之间穿过,以将第一集成电路20-1和第二集成电路20-2电连接,而不在第一tsv区域40r1或第二tsv区域40r2内延伸。例如,布线结构30可以在绕过多个相应的tsv区域40r的两端的同时将第一集成电路20-1和第二集成电路20-2电连接。如在图1a的实施例中所示,布线结构30可以穿过多个最近的tsv区域40r之间的空间,从而通过相对最短的距离连接第一集成电路20-1和第二集成电路20-2。因此,布线结构30可以不集中在tsv区域40r的局部部分的一个横向侧或两个横向侧,而是可以形成为穿过多个tsv区域40r中的相邻两个tsv区域40r之间的空间。布线结构30可以包括位于主体10内部的通路和布线层。除了将第一集成电路20-1和第二集成电路20-2电连接的部分之外,布线结构30还可以包括将第一集成电路20-1中的各单元彼此连接或将第二集成电路20-2中的各单元彼此连接的部分。

30.如在图1a的实施例中所示,多个tsv结构40可以以矩阵形式设置在彼此间隔开的多个tsv区域40r中。例如,第一tsv区域40r1可以包括以m

×

n矩阵形式设置的多个第一tsv结构40-1,并且第二tsv区域40r2可以包括以i

×

j矩阵形式设置的多个第二tsv结构40-2。

第一tsv区域40r1和第二tsv区域40r2设置在第一集成电路20-1和第二集成电路20-2之间(例如,在y方向上),并且可以在x方向上彼此间隔开。上述“m”和“i”分别指示多个第一tsv结构40-1在分别与第一tsv区域40r1和第二tsv区域40r2的布置方向相同的x方向上布置的数目和多个第二tsv结构40-2在分别与第一tsv区域40r1和第二tsv区域40r2的布置方向相同的x方向上布置的数目。上述“n”和“j”分别指示多个第一tsv结构40-1在与x方向垂直的y方向上布置的数目和多个第二tsv结构40-2在与x方向垂直的y方向上布置的数目。在实施例中,“m”和“i”可以是大于或等于2的相同的整数,并且“n”和“j”可以是大于或等于2的相同的整数。然而,本发明构思的实施例不限于此。

31.多个第一tsv结构40-1和多个第二tsv结构40-2可以布置为具有基本上相同的节距。例如,第一tsv结构40-1之中的相邻的(例如,在y方向上相邻的)第一tsv结构的中心之间的第一间隔p1和多个第二tsv结构40-2之中的相邻的(例如,在y方向上相邻的)第二tsv结构的中心之间的第二间隔p2可以彼此基本上相同。在实施例中,第一间隔p1和第二间隔p2均可以在大约30μm至大约50μm的范围内。然而,本发明构思的实施例不限于此。

32.第一tsv区域40r1和第二tsv区域40r2可以是在tsv结构40周围禁止形成诸如晶体管的元件的禁区(keep-out zone),以防止由于作用在tsv结构40及其周围的应力而导致的裂纹或者器件功能的劣化。例如,第一tsv区域40r1可以是与距多个第一tsv结构40-1之中的设置在最外侧的第一tsv结构第一距离e1(例如,在x方向和y方向中的每个方向上的长度)内的范围对应的区域,并且第二tsv区域40r2可以是与距多个第二tsv结构40-2之中的设置在最外侧的第二tsv结构第二距离e2(例如,在x方向和y方向中的每个方向上的长度)内的范围对应的区域。换而言之,第一tsv区域40r1可以是其边界距多个第一tsv结构40-1之中的设置在最外侧的第一tsv结构第一距离e1的区域,第二tsv区域40r2可以是其边界距多个第二tsv结构40-2之中的设置在最外侧的第二tsv结构第二距离e2的区域。在实施例中,第一距离e1和第二距离e2可以分别在大约20μm至大约40μm的范围内。半导体装置之间的高速通信可能需要相对大量的tsv结构40,这可能导致tsv区域40r的面积增加。为了显著减小由tsv区域40r的面积增加引起的负担,具有精细节距的布线结构30所穿过的第一tsv区域40r1和第二tsv区域40r2之间的间隔d(例如,在x方向上的长度)可以小于或等于第一距离e1和第二距离e2中的每一者。

33.多个tsv结构40可以穿过主体10的至少一部分。例如,如在图1b的实施例中所示,多个tsv结构40可以在第三方向上穿过主体10的至少一部分,第三方向沿着垂直于x方向和y方向的z轴(在下文中,被称为“z方向”)延伸并且是半导体衬底110的厚度方向。例如,每个tsv结构40可以具有穿过主体10的圆柱形状,并且多个第一tsv结构40-1和多个第二tsv结构40-2可以均具有在大约3μm至大约5μm的范围内的直径。集成电路20可以通过多个tsv结构40电连接到将堆叠在半导体装置100a上和/或下方的另一半导体装置的集成电路。

34.构成3d半导体装置的每个半导体装置可以包括将半导体装置彼此电连接的tsv结构。通过确保tsv结构所集中的第一tsv区域和第二tsv区域之间的空间,可以缩短连接通过tsv区域分开的第一集成电路和第二集成电路的布线的路径。在实施例中,在x方向上间隔开的第一tsv区域40r1和第二tsv区域40r2可以设置在沿y方向间隔开的第一集成电路20-1和第二集成电路20-2之间。另外,布线结构30在y方向上在第一tsv区域40r1和第二tsv区域40r2之间穿过(例如,纵长地延伸),以将第一集成电路20-1和第二集成电路20-2彼此电连

接。

35.参考图1a和图1b以及图1c的实施例,半导体装置100a可以包括半导体衬底110、第一半导体结构120和第二半导体结构130以及多个tsv结构40。

36.半导体衬底110可以包括半导体层111以及形成在半导体层111中的多个导电区域112和隔离区域113。在实施例中,半导体衬底110可以是半导体晶片。在实施例中,半导体层111可以包括诸如硅或锗的半导体元素或者诸如碳化硅(sic)、砷化镓(gaas)、砷化铟(inas)和磷化铟(inp)的化合物半导体。导电区域112可以是例如掺杂有杂质的阱或者掺杂有杂质的结构。隔离区域113是具有浅沟槽隔离(sti)结构的器件隔离结构,并且可以包括氧化硅等。半导体衬底110的下表面可以被由氧化硅膜、氮化硅膜、聚合物或它们的组合形成的绝缘层覆盖。

37.半导体结构可以包括堆叠在半导体衬底110上的第一半导体结构120和第二半导体结构130。第一半导体结构120可以包括设置在半导体衬底110的上表面s1上的第一层间绝缘层121和诸如第一单独器件id1和第二单独器件id2的多个单独器件。诸如第一单独器件id1和第二单独器件id2的多个单独器件可以彼此组合以形成图1a的集成电路20。在实施例中,第一层间绝缘层121可以包括氧化硅或氮化硅。在实施例中,诸如第一单独器件id1和第二单独器件id2的多个单独器件可以包括各种微电子器件,例如,金属氧化物半导体场效应晶体管(mosfet)、系统大规模集成(lsi)、微机电系统(mems)、有源元件、无源元件等。在实施例中,诸如第一单独器件id1和第二单独器件id2的多个单独器件可以包括栅极结构125。如在图1c的实施例中所示,栅极结构125可以包括设置在半导体衬底110上的栅极绝缘层122、设置在栅极绝缘层122上的栅电极123以及包围栅极绝缘层122和栅电极123的栅极间隔物124。在实施例中,栅极绝缘层122可以包括氧化硅或氮化硅。栅电极123可以包括金属氧化物或金属材料。栅极间隔物124可以由氮化硅膜、siocn膜、sicn膜或它们的组合形成。诸如第一单独器件id1和第二单独器件id2的多个单独器件可以电连接到半导体衬底110的导电区域112。诸如第一单独器件id1和第二单独器件id2的多个单独器件均可以通过第一层间绝缘层121与其他相邻的单独器件电隔离。

38.第二半导体结构130可以包括设置在第一半导体结构120上的第二层间绝缘层131以及第一布线结构132和第二布线结构134,第一布线结构132和第二布线结构134包括金属布线层和接触通路。除了第一布线结构132和第二布线结构134之外,第二半导体结构130还可以包括将第一半导体结构120的诸如第一单独器件id1和第二单独器件id2的单独器件彼此连接或连接到其他单独器件或布线的多个布线结构。第二层间绝缘层131可以设置在第一半导体结构120上,并且可以包括氧化硅或氮化硅。第一布线结构132设置在tsv结构40上,并且可以将tsv结构40和上连接端子151电连接。例如,如在图1c的实施例中所示,第一布线结构132的下表面直接接触tsv结构40的上表面,并且第一布线结构132的上表面直接接触上连接端子151的下表面。第二布线结构134可以在y方向上纵长地延伸,从而将通过tsv区域40r分开的诸如第一单独器件id1和第二单独器件id2的多个单独器件电连接。在实施例中,第二布线结构134可以形成为包括多个金属布线层和多个接触通路的多层布线结构。

39.在实施例中,多个单独器件可以通过tsv结构40分离为在y方向上彼此间隔开的多个第一单独器件id1和多个第二单独器件id2。另外,多个第一单独器件id1和多个第二单独

器件id2可以通过在y方向上在第一tsv结构40-1和第二tsv结构40-2之间穿过的第二布线结构134彼此电连接。第二布线结构134可以在距多个第一tsv结构40-1之中的设置在外侧的第一tsv结构40-1第一距离e1内不与tsv区域40r1交叠,并且可以在距多个第二tsv结构40-2之中的设置在外侧的第二tsv结构40-2第二距离e2内不与第二tsv区域40r2交叠。第二布线结构134在第一tsv结构40-1和第二tsv结构40-2之间穿过,以缩短第一单独器件id1和第二单独器件id2之间的连接路径的总长度并且提高第一单独器件id1和第二单独器件id2之间的通信速度。

40.多个tsv结构40可以在z方向上穿过半导体衬底110和第一半导体结构120。多个tsv结构40可以在x方向上布置。多个tsv结构40可以包括导电插塞42和包围导电插塞42的阻挡层41。在实施例中,导电插塞42可以包括金属材料,例如从钨(w)、钛(ti)、铝(al)和铜(cu)中选择的至少一种。导电插塞42可以通过镀覆工艺、pvd工艺或cvd工艺来形成。阻挡层41可以包括金属化合物,例如从氮化钨(wn)、氮化钛(tin)和碳化钽(tan)中选择的至少一种化合物。阻挡层41可以通过pvd工艺或cvd工艺来形成。

41.半导体装置100a还可以包括位于第二半导体结构130上的上连接端子151和位于半导体衬底110下方的下连接端子152。例如,如在图1b和图1c的实施例中所示,下连接端子152的上表面可以直接接触半导体衬底110的下表面和穿过半导体衬底110的tsv结构40的下表面,并且上连接端子151的下表面可以直接接触第二半导体结构130的上表面。上连接端子151和下连接端子152可以通过tsv结构40和第一布线结构132彼此电连接。在本发明构思的实施例中,上连接端子151和下连接端子152不限于在图中示出的形状,并且可以具有焊料球、焊料凸块或焊盘的形状。或者,在实施例中,可以省略上连接端子151和下连接端子152中的至少一者。

42.图2a至图2b是分别示出了根据本发明构思的实施例的在图1b中示出的组件的截面图。图2a至图2b示出了根据本发明构思的实施例的图1b的tsv结构40。

43.参考图2a的实施例,可以在半导体衬底110上形成第一半导体结构120和第二半导体结构130之后形成tsv结构40a。因此,tsv结构40a可以穿过(例如,在z方向上)半导体衬底110以及第一半导体结构120和第二半导体结构130的总体厚度。tsv结构40a的上表面可以直接接触上连接端子151的下表面,并且tsv结构40a的下表面可以直接接触下连接端子152的上表面。然而,tsv结构40a与上连接端子151和下连接端子152之间的连接结构不限于在图2a中示出的结构。例如,在实施例中,tsv结构40a的上表面可以不直接接触上连接端子151,并且可以在第二半导体结构130上进一步形成连接tsv结构40a和上连接端子151的上布线。

44.参考图2b的实施例,可以在形成第一半导体结构120和第二半导体结构130之前形成tsv结构40b。因此,tsv结构40b可以仅穿过(例如,在z方向上)半导体衬底110,并且可以不穿过第一半导体结构120和第二半导体结构130。tsv结构40b可以通过形成在第一半导体结构120中的第三布线结构126连接到第二半导体结构130的第一布线结构132。在图2b中示出的实施例中,第三布线结构126的下表面可以直接接触tsv结构40b的上表面,并且通路形状的第三布线结构126直接连接到tsv结构40b。然而,本发明构思的实施例不限于图2b中示出的tsv结构40b和第三布线结构126之间的连接结构。例如,第三布线结构126还可以包括覆盖tsv结构40b的上表面的布线或焊盘形状的金属布线层。

45.图3a至图3c是分别示出了根据本发明构思的实施例的半导体装置100a、100b和100c的一些组件的局部放大图。图3a至图3c是示出了半导体装置100a、100b和100c的第一tsv区域40-1和第二tsv区域40-2的局部放大图。

46.参考图3a的实施例,在半导体装置100a中,第一tsv区域40r1中的第一tsv结构40-1以m

×

n矩阵形式布置,并且第二tsv区域40r2中的第二tsv结构40-2可以以i

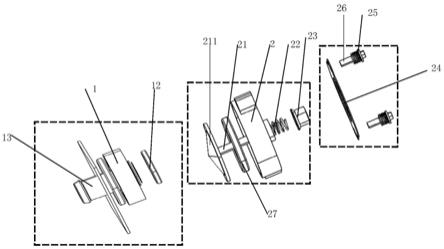

×

j矩阵的形式布置。在该实施例中,“m”和“i”可以包括大于或等于2的不同的整数,并且“n”和“j”可以包括大于或等于2的相同的整数。“m”和“i”分别是tsv结构40在x方向上布置的数目,并且“n”和“j”分别是tsv结构40在y方向上布置的数目。例如,如在图3a的实施例中所示,“n”和“j”可以为2,“m”可以为3,并且“i”可以为2。

47.参考图3b的实施例,在半导体装置100b中,第一tsv区域40r1中的第一tsv结构40-1以m

×

n矩阵形式布置,并且第二tsv区域40r2中的第二tsv结构40-2可以以i

×

j矩阵的形式布置。在该实施例中,“m”和“i”可以包括大于或等于2的相同的整数,并且“n”和“j”可以包括大于或等于2的不同的整数。“m”和“i”分别是tsv结构40在x方向上布置的数目,并且“n”和“j”分别是tsv结构在y方向上布置的数目。例如,如图3b所示,“m”和“i”可以为3,“n”可以为2,并且“j”可以为3。

48.参考图3c的实施例,在半导体装置100c中,第一tsv区域40r1中的第一tsv结构40-1以m

×

n矩阵形式布置,并且第二tsv区域40r2中的第二tsv结构40-2可以以i

×

j矩阵的形式布置。在该实施例中,“m”和“i”可以包括大于或等于2的不同的整数,并且“n”和“j”可以包括大于或等于2的不同的整数。“m”和“i”分别是tsv结构40在x方向上布置的数目,并且“n”和“j”分别是tsv结构40在y方向上布置的数目。例如,如在图3c的实施例中所示,“m”可以为3,“i”可以为2,“n”可以为2,并且“j”可以为3。

49.在一些实施例中,包括多个tsv结构40的矩阵的尺寸可以不同地修改,并且多个tsv区域40r的尺寸可以彼此不同。在一些实施例中,多个tsv结构40的布置可以包括图1a和图3a至图3c中示出的布置中的两种或更多种。可以通过改变多个tsv区域40r的形状和尺寸来高效地设计单元布置空间。

50.图4是示出了根据本发明构思的实施例的半导体装置100b的透视图和放大局部透视图,并且图5是示出了包括在图4的半导体装置100b中的掩埋元件50的一部分的布局。图5示出了作为图4的掩埋元件50的示例的去耦电容器的布局。

51.参考图4的实施例,半导体装置100b还可以包括设置在tsv区域40r中的掩埋元件50。通过在tsv区域40r中设置掩埋元件50,可以提高半导体装置的面积效率。掩埋元件50设置在多个tsv区域40r的至少局部部分中,并且可以电连接到多个tsv结构40的至少局部部分。如在图4的实施例中所示,掩埋元件50可以设置为使得其不与tsv结构40的阻挡区域br交叠。阻挡区域br可以设置在围绕tsv结构40的预定半径内的范围中。在实施例中,阻挡区域br可以设置在距离tsv结构40的大约10μm至大约20μm的范围中的半径内。掩埋元件50可以通过tsv结构40连接到地面和/或电源。掩埋元件50可以通过设置在掩埋元件50和/或tsv结构40上的额外布线结构电连接到相应的tsv结构40。在实施例中,掩埋元件50可以包括去耦电容器或虚设单元。例如,去耦电容器可以包括平面晶体管、凹槽沟道阵列晶体管(rcat)和掩埋单元阵列晶体管(bcat)中的至少一种。

52.虚设单元可以与第一集成电路和第二集成电路绝缘。虚设单元可以包括例如工程

更改指令(engineering change order,eco)单元。eco单元可以包括经编程的功能单元和未编程的基本单元。eco单元可以与包括在集成电路20中的第一单元21-1和第二单元21-2绝缘。当修改半导体装置的布局时,eco单元可以用集成电路20中的标准单元进行布线。

53.在实施例中,去耦电容器可以具有图5中示出的布局。参考图5的实施例,去耦电容器可以包括成对的电源布线层(例如,第一电源布线层vdd和第二电源布线层vss)、第一有源区ar1和第二有源区ar2、栅极线、多个接触通路cv和多个连接布线层(例如,第一布线层m1、第二布线层m2、第三布线层m3和第四布线层m4)。去耦电容器可以提高电源的压降(例如,ir降),并且去除电源噪声。可以通过在tsv区域40r中设置去耦电容器来提高半导体装置的面积效率。

54.诸如第一电源布线层vdd和第二电源布线层vss的成对的电源布线层在x方向上纵长地延伸,并且可以在y方向上彼此平行地布置。诸如第一电源布线层vdd和第二电源布线层vss的电源布线层可以向集成电路20供电。在实施例中,电源布线层可以包括供应正电压的第一电源布线层vdd和供应负电压的第二电源布线层vss。第一电源布线层vdd和第二电源布线层vss可以电连接到tsv结构40的至少局部部分。

55.第一有源区ar1和第二有源区ar2在第一电源布线层vdd和第二电源布线层vss之间在x方向上纵长地延伸,并且可以在y方向上彼此平行地布置。第一有源区ar1和第二有源区ar2可以在y方向上彼此间隔开,并且可以具有不同的导电类型。除了第一有源区ar1和第二有源区ar2之外的区域可以为掺杂有杂质的阱区。例如,在实施例中,与第一有源区ar交叠的区域可以为n阱(n)区,并且与第二有源区ar2交叠的区域可以为p阱(p)区。

56.栅极线gl可以在第一有源区ar1和第二有源区ar2上在y方向上延伸,并且可以在x方向上彼此平行地设置。栅极线gl可以包括与第一有源区ar1交叠(例如,在z方向上)的第一栅极线gl1和与第二有源区ar2交叠(例如,在z方向上)的第二栅极线gl2。

57.多个连接布线层m可以包括连接第一有源区ar1和第一电源布线层vdd的第一连接布线层m1、连接第二有源区ar2和第一栅极线gl1的第二连接布线层m2、连接第一有源区ar1和第二栅极线gl2的第三连接布线层m3以及连接第二有源区ar2和第二电源布线层vss的第四连接布线层m4。在实施例中,连接布线层m可以具有单层结构或者包括不同水平高度的布线层的多层结构。

58.接触通路cv可以连接设置在不同水平高度的栅极线gl、第一有源区ar1和第二有源区ar2、第一电源布线层vdd和第二电源布线层vss以及诸如第一连接布线层m1、第二连接布线层m2、第三连接布线层m3和第四连接布线层m4的多个连接布线层。

59.图6是示出了根据本发明构思的实施例的半导体装置100c的透视图。

60.参考图6的实施例,在半导体装置100c中,第一集成电路20-1可以包括第一存储块22-1和第一外围电路23-1,并且第二集成电路20-2可以包括第二存储块22-2和第二外围电路23-2。第一外围电路23-1可以电连接到第一存储块22-1。第二外围电路23-2可以电连接到第二存储块22-2。另外,第一外围电路23-1和第二外围电路23-2可以通过在tsv区域40r之间穿过的布线结构30彼此电连接。第一存储块22-1和第二存储块22-2可以包括多个存储单元、多条字线和多条位线。在实施例中,例如,半导体装置100c可以为诸如动态随机存取存储器(dram)或静态ram(sram)的易失性存储装置,或者诸如相变ram(pram)、磁性ram(mram)、电阻ram(rram)、闪存等的非易失性存储装置。

61.布线结构30可以在彼此间隔开的tsv区域40r之间穿过而不在tsv区域40r内延伸,以缩短第一外围电路23-1和第二外围电路23-2之间的连接路径的总长度。通过连接第一外围电路23-1和第二外围电路23-2,由tsv区域40r分开的第一存储块22-1和第二存储块22-2的多平面操作可以以相对高的速度执行。

62.图7是示出了根据本发明构思的实施例的半导体装置200的透视图。

63.参考图7的实施例,半导体装置200可以包括堆叠的(例如,在z方向上)并且通过tsv结构40互连的诸如第一半导体装置210和第二半导体装置220的多个半导体装置。在实施例中,诸如第一半导体装置210和第二半导体装置220的多个半导体装置可以是包括第一逻辑电路211和第二逻辑电路221的逻辑芯片。在实施例中,诸如第一半导体装置210和第二半导体装置220的多个半导体装置可以包括诸如图像信号处理器(isp)的处理器、诸如sram的存储元件、寄存器、电压发生器、定时发生器和/或信号发生器、输出缓冲器、放大电路或者各种其他公共逻辑电路。在实施例中,第一半导体装置210的第一逻辑电路211可以包括cpu电路,并且第二半导体装置220的第二逻辑电路221可以包括输入/输出电路、模拟电路或sram电路。

64.图8是示出了根据本发明构思的实施例的半导体装置300的透视图。

65.参考图8的实施例,半导体装置300可以包括第一半导体装置310和堆叠在第一半导体装置310上(例如,在z方向上)的多个第二半导体装置320-1、320-2和320-n,第一半导体装置310和多个第二半导体装置320-1、320-2和320-n通过tsv结构40互连。第二半导体装置320-1、320-2和320-n可以均包括集成电路321,集成电路321包括存储块322和外围电路323。

66.在实施例中,第一半导体装置310可以为逻辑芯片,并且多个第二半导体装置320-1、320-2和320-n可以为包括存储单元的存储芯片。尽管图8的实施例示出了包括三层的多个第二半导体装置320-1、320-2、320-n,但是多个第二半导体装置320-1、320-2和320-n可以具有更多数目的层。如在图8的实施例中所示,多个第二半导体装置320-1、320-2和320-n可以在z方向(例如,垂直方向)上布置,或者也可以以z方向和水平方向(例如,x和/或y方向)的组合形式布置。

67.在实施例中,多个第二半导体装置320-1、320-2和320-n可以基于从第一半导体装置310传输的地址命令和控制命令存储或输出数据。例如,多个第二半导体装置320-1、320-2和320-n可以为dram、sram或闪存芯片。

68.图9是示出了根据本发明构思的实施例的半导体装置400的透视图。

69.参考图9的实施例,半导体装置400可以包括在z方向上堆叠的第一半导体装置410、第二半导体装置420和第三半导体装置430。

70.在实施例中,第一半导体装置410可以包括彼此间隔开(例如,在x方向上)的多个中央tsv区域40r以及集成电路411,集成电路411包括存储块412和电连接到存储块412的外围电路413。在实施例中,例如,存储块412可以包括诸如金属-绝缘体-金属(mim)电容器、电荷捕获器件、磁性隧道结(mtj)器件和锗(ge)-锑(sb)-碲(te)(gst)器件的存储器件。第一半导体装置410可以通过多个中央tsv结构40电连接到第二半导体装置420。

71.第二半导体装置420可以包括:边缘tsv区域60r,边缘tsv区域60r包括多个边缘tsv结构60;多个中央tsv区域40r,多个中央tsv区域40r包括多个中央tsv结构40;第一逻辑

电路421-1;以及第二逻辑电路421-2。第二半导体装置420可以通过边缘tsv结构60电连接到第三半导体装置430。在实施例中,第一逻辑电路421-1可以包括驱动第三半导体装置430的像素阵列431所需的行驱动器、读出电路、列驱动器和控制逻辑。第二逻辑电路421-2可以包括电源电路、输入/输出接口、图像信号处理电路等。第一逻辑电路421-1和第二逻辑电路421-2中的每一者所占据的面积和布置形式可以以各种方式修改。

72.第三半导体装置430可以包括布置有边缘tsv结构60的边缘tsv区域60r和布置有多个像素432的像素阵列431。第三半导体装置430的边缘tsv区域60r可以与第二半导体装置420的边缘tsv区域60r交叠(例如,在z方向上)。第三半导体装置430可以通过边缘tsv结构60电连接到第二半导体装置420。像素阵列431可以通过多条行线和多条列线连接到第一逻辑电路421-1和第二逻辑电路421-2。

73.图10是示出了根据本发明构思的实施例的设计3d半导体装置的方法的流程图。

74.参考图10,根据本发明构思的实施例的设计3d半导体装置的方法可以包括:在框d110中,在多个半导体装置的各个区域内确定输入/输出区域、第一集成电路区域、第二集成电路区域、第一tsv区域和第二tsv区域的位置。在框d120中,在3d半导体装置中分别设置多个第一tsv结构和多个第二tsv结构。在框d130中,在3d半导体装置中设置硬核(hard macro)。在框d140中,在3d半导体装置中分别设置多个第一单元和多个第二单元。在框d150中,将硬核的至少一部分与多个第一单元和多个第二单元电连接。

75.在框d110中执行的确定输入/输出区域、第一集成电路区域、第二集成电路区域、第一tsv区域和第二tsv区域的位置的操作是布图规划(floor plan)操作,在布图规划操作中,在芯片上粗略地设置网表的框,以减小半导体装置的使用面积。在实施例中,在构成三维半导体装置的多个半导体装置(例如,堆叠件1、堆叠件2、

…

、堆叠件n)的各个区域内确定输入/输出区域、第一集成电路区域、第二集成电路区域、第一tsv区域和第二tsv区域的位置。在每个半导体装置(例如,堆叠件1、堆叠件2、

…

、堆叠件n)的区域内,第一集成电路区域和第二集成电路区域彼此间隔开,并且第一tsv区域和第二tsv区域可以设置在第一集成电路区域和第二集成电路区域之间。

76.在框d120中执行的分别设置多个第一tsv结构和多个第二tsv结构可以包括在每个半导体装置(例如,堆叠件1、堆叠件2、

…

、堆叠件n)的第一tsv区域和第二tsv区域中分别以矩阵形式设置多个第一tsv结构和多个第二tsv结构。在多个第一tsv结构之中,设置在外侧的第一tsv结构可以与第一tsv区域间隔开第一距离(例如,在x方向和y方向中的每个方向上间隔开第一距离)。在多个第二tsv结构之中,设置在外侧的第二tsv结构可以与第二tsv区域间隔开第二距离(例如,在x方向和y方向中的每个方向上间隔开第二距离)。在实施例中,在布线结构不在第一tsv区域和第二tsv区域内延伸的情况下布线结构所穿过的第一tsv区域和第二tsv区域之间的间隔可以小于或等于第一距离和第二距离。

77.在框d130中执行的设置硬核的操作是在每个半导体装置(例如,堆叠件1、堆叠件2、

…

、堆叠件n)的第一集成电路区域和第二集成电路区域中设置硬核或硬块的操作。“核(macro)”是可以在asic或fpga的制造中使用的功能电路元件或逻辑的构建块。“硬核”可以指在物理实现中不能更改的固定布线图案。另一方面,“软核”不指定布线图案,因此在物理实现中具有灵活性。硬核是例如其中形成有模拟电路块、sram、cpu等的区域,并且可以与标准单元区域分开地形成。

78.在框d140中执行的设置多个第一单元和多个第二单元的操作可以是以使得第一单元和第二单元不与硬核交叠的方式分别在每个半导体装置(例如,堆叠件1、堆叠件2、

…

、堆叠件n)的第一集成电路区域和第二集成电路区域中设置第一单元和第二单元的操作。在实施例中,多个第一单元可以设置在第一集成电路区域的外边缘上以与第一tsv区域和第二tsv区域相邻,并且多个第二单元可以设置在第二集成电路区域的外边缘上以与第一tsv区域和第二tsv区域相邻。多个第一单元和多个第二单元均可以包括逻辑单元。

79.在框d150中执行的将硬核、多个第一单元和多个第二单元中的至少一些电连接的操作是使用在每个半导体装置(堆叠件1、堆叠件2、

…

、堆叠件n)的第一tsv区域和第二tsv区域之间穿过而不在第一tsv区域或第二tsv区域内延伸的布线结构对每个半导体装置(例如,堆叠件1、堆叠件2、

…

、堆叠件n)内的硬核、多个第一单元和多个第二单元进行布线的步骤。之后,在最初不满足所需的操作速度的实施例中,通过测量各个半导体装置(例如,堆叠件1、堆叠件2、

…

、堆叠件n)的定时(例如,时钟速度),可以再次执行操作“d130”、“d140”或“d150”。定时可以以赫兹(hz)为单位来测量,其为每秒的时钟周期数。

80.在实施例中,通过使用在第一tsv区域和第二tsv区域之间穿过的布线结构将第一集成电路区域和第二集成电路区域中的单元互连,可以缩短布线路径的总长度。因此,可以显著地减少由布线的绕行导致的延迟现象。

81.如上所述,根据本发明构思的实施例,通过引入在tsv之间穿过的布线结构,可以提供具有提高的通信速度的半导体装置和设计半导体装置的方法。

82.尽管上面已示出并描述了本发明构思的实施例,但是对于本领域技术人员而言将明显的是,在不脱离如所附权利要求限定的本发明构思的范围的情况下,可以进行修改和改变。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。