1.本发明涉及一种像素阵列基板。

背景技术:

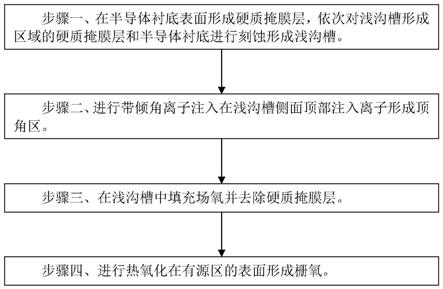

2.一般而言,显示面板的信号线发生断线的情况,会对显示面板进行修补,以提升良率。具体而言,可熔接断开的信号线与修补线及/或切割修补线,以利用修补线电性连接断开的信号线的两个部分。

3.显示面板的修补线可分为设置于周边区的外部修补线及设置于显示区的内部修补线。外部修补线的长度长,本身的负载大。利用外部修补线修补信号线时,与被修补的信号线电性连接的多个像素结构易使显示画面出现异常(例如:亮线/或暗线)。因此,外部修补线并不适合应用在大面积及/或高分辨率的显示面板中。目前大面积及/或是高分辨率的显示面板的修补技术主流是使用内部修补线。然而,内部修补线设置于显示区,内部修补线与信号线之间的距离近,寄生电容大,造成信号线的负载增加,进而降低像素结构的充电效率,不利于显示品质。

技术实现要素:

4.本发明提供一种像素阵列基板,性能佳。

5.本发明的像素阵列基板包括多个像素结构、多条数据线、多条栅极线以及多个第一共用电极。每一像素结构包括薄膜晶体管及电性连接至薄膜晶体管的像素电极。多条数据线沿第一方向排列,且电性连接至多个像素结构的多个薄膜晶体管。多条栅极线沿第二方向排列,且电性连接至多个像素结构的多个薄膜晶体管,其中第一方向与第二方向交错。每一第一共用电极包括沿第一方向排列的多个线段,且多个线段的相邻两者于结构上分离以定义一间隙。在像素阵列基板的俯视图中,对应的一数据线穿越所述间隙。

附图说明

6.图1为本发明一实施例的像素阵列基板10的俯视示意图。

7.图2为本发明一实施例的像素阵列基板10的一区域r的俯视示意图。

8.图3为本发明一实施例的像素阵列基板10的局部r的放大示意图。

9.图4为本发明一实施例的像素阵列基板10的剖面示意图。

10.图5为本发明一实施例的像素阵列基板10’的俯视示意图。

11.附图标记说明:

12.10、10’:像素阵列基板

13.110:基底

14.120:第一金属层

15.122:第一共用电极

16.122a、122b、122b-1、122b-2:线段

17.122g:间隙

18.124:第二共用电极

19.130:栅绝缘层

20.140:第二金属层

21.142:连接图案

22.144:第三共用电极

23.144a、144b、144c、144d:一处

24.144m:主要部

25.150:第一钝化层

26.160:彩色滤光图案

27.170:第二钝化层

28.180:第一透明导电层

29.182:透明屏蔽图案

30.182a:开口

31.182a-1、182a-2:凹陷部

32.190:平坦层

33.130a、192:接触窗

34.200:第二透明导电层

35.202:像素电极

36.cspx:像素行

37.c1:第一断开处

38.c2:第二断开处

39.c3:第三断开处

40.c4:第四断开处

41.c5:第五断开处

42.c6:第六断开处

43.c7:第七断开处

44.c8:第八断开处

45.dl:数据线

46.dlo:断开处

47.dl-1:第一部分

48.dl-2:第二部分

49.dm1:第一菱格纹

50.dm2:第二菱格纹

51.gl:栅极线

52.gl:转接线

53.gla:主要部

54.glo:断开处

55.gl-1:第一部分

56.gl-2:第二部分

57.r:区域

58.r:局部

59.rspx:像素列

60.s

dl

:数据信号

61.s

gl

:栅极驱动信号

62.spx:像素结构

63.t:薄膜晶体管

64.ta:源极

65.tb:漏极

66.tc:栅极

67.td:半导体图案

68.w1:第一熔接处

69.w2:第二熔接处

70.w3:第三熔接处

71.w4:第四熔接处

72.w5:第五熔接处

73.w6:第六熔接处

74.w7:第七熔接处

75.w8:第八熔接处

76.x1:第一交错处

77.x2:第二交错处

78.x3:第三交错处

79.x4:第四交错处

80.x:第一方向

81.y:第二方向

82.i-i’:剖线

具体实施方式

83.现将详细地参考本发明的示范性实施例,示范性实施例的实例说明于附图中。只要有可能,相同元件符号在附图和描述中用来表示相同或相似部分。

84.应当理解,当诸如层、膜、区域或基板的元件被称为在另一元件“上”或“连接到”另一元件时,其可以直接在另一元件上或与另一元件连接,或者中间元件可以也存在。相反,当元件被称为“直接在另一元件上”或“直接连接到”另一元件时,不存在中间元件。如本文所使用的,“连接”可以指物理及/或电性连接。再者,“电性连接”或“耦合”可以是二元件间存在其它元件。

85.本文使用的“约”、“近似”、或“实质上”包括所述值和在本领域普通技术人员确定的特定值的可接受的偏差范围内的平均值,考虑到所讨论的测量和与测量相关的误差的特定数量(即,测量系统的限制)。例如,“约”可以表示在所述值的一个或多个标准偏差内,或

±

30%、

±

20%、

±

10%、

±

5%内。再者,本文使用的“约”、“近似”或“实质上”可依光学性质、蚀刻性质或其它性质,来选择较可接受的偏差范围或标准偏差,而可不用一个标准偏差适用全部性质。

86.除非另有定义,本文使用的所有术语(包括技术和科学术语)具有与本发明所属领域的普通技术人员通常理解的相同的含义。将进一步理解的是,诸如在通常使用的字典中定义的那些术语应当被解释为具有与它们在相关技术和本发明的上下文中的含义一致的含义,并且将不被解释为理想化的或过度正式的意义,除非本文中明确地这样定义。

87.图1为本发明一实施例的像素阵列基板10的俯视示意图。

88.图2为本发明一实施例的像素阵列基板10的一区域r的俯视示意图。图2对应图1的区域r。

89.图1示意性地绘出基底110、栅极线gl及转接线gl,而省略图2的像素阵列基板10的其它构件。

90.图3为本发明一实施例的像素阵列基板10的局部r的放大示意图。图3对应图2的局部r。

91.图4为本发明一实施例的像素阵列基板10的剖面示意图。图4对应图3的剖线i-i’。

92.请参照图1、图2、图3及图4,像素阵列基板10包括基底110。基底110主要用以承载像素阵列基板10的多个构件。举例而言,在本实施例中,基底110的材质可以是玻璃。然而,本发明不限于此,根据其它实施例,基底110的材质也可以是石英、有机聚合物、不透光/反射材料(例如:晶圆、陶瓷等)、或是其它可适用的材料。

93.请参照图1、图2及图3,像素阵列基板10包括多条数据线dl和多条栅极线gl。多条数据线dl和多条栅极线gl设置于基底110上。多条数据线dl沿第一方向x排列,多条栅极线gl沿第二方向y上排列,其中第一方向x与第二方向y交错。举例而言,在本实施例中,第一方向x与第二方向y可垂直,但本发明不以此为限。

94.请参照图3及图4,另外,数据线dl与栅极线gl属于不同的膜层。举例而言,在本实施例中,栅极线gl可选择性地属于第一金属层120,数据线dl可选择性地属于第二金属层140,但本发明不以此为限。

95.基于导电性的考量,在本实施例中,数据线dl与栅极线gl是使用金属材料。然而,本发明不限于此,根据其他实施例,数据线dl与栅极线gl也可以使用其他导电材料,例如:合金、金属材料的氮化物、金属材料的氧化物、金属材料的氮氧化物、或是金属材料与其它导电材料的堆叠层。

96.请参照图2及图3,像素阵列基板10包括多个像素结构spx,设置于基底110上。每一像素结构spx包括薄膜晶体管t及电性连接至薄膜晶体管t的像素电极202。多条数据线dl电性连接至多个像素结构spx的多个薄膜晶体管t。多条栅极线gl电性连接至多个像素结构spx的多个薄膜晶体管t。

97.请参照图3及图4,具体而言,在本实施例中,每一薄膜晶体管t具有源极ta、漏极tb、栅极tc及半导体图案td,栅绝缘层130夹设于栅极tc与半导体图案td之间,源极ta和漏极tb分别与半导体图案td的不同两区电性连接,源极ta电性连接至对应的一条数据线dl,且栅极tc电性连接至对应的一条栅极线gl。举例而言,在本实施例中,栅极tc可选择性地属于第一金属层120,源极ta和漏极tb可选择性地属于第二金属层140,但本发明不以此为限。

98.每一薄膜晶体管t的漏极tb电性连接至对应的一像素电极202。举例而言,在本实施例中,每一像素结构spx还包括设置于栅绝缘层130上且与薄膜晶体管t的漏极tb电性连接的一连接图案142;像素阵列基板10还可包括设置于第二金属层140上的第一钝化层150、设置于第一钝化层150上的彩色滤光图案160、设置于彩色滤光图案160上的第二钝化层170及设置于第二钝化层170上的平坦层190;像素电极202可设置平坦层190上,且通过平坦层190的接触窗192电性连接至连接图案142,其中连接图案142电性连接像素电极202与薄膜晶体管t的漏极tb。

99.在本实施例中,像素电极202可属于第二透明导电层200。第二透明导电层200的材质可包括金属氧化物,例如:铟锡氧化物、铟锌氧化物、铝锡氧化物、铝锌氧化物、铟锗锌氧化物、其它合适的氧化物、或者是上述至少二者的堆叠层,但本发明不以此为限。

100.请参照图2,像素阵列基板10还包括多个第一共用电极122。每一第一共用电极122包括沿第一方向x排列的多个线段122a、122b;多个线段122a、122b的相邻两者于结构上分离,以定义间隙122g;在像素阵列基板10的俯视图中,对应的一数据线dl穿越间隙122g。

101.换言之,每一第一共用电极122包括彼此断开的多个线段122a、122b;在像素阵列基板10的俯视图中,像素阵列基板10的每一数据线dl至少会穿过至少一个第一共用电极122的断开处(即间隙122g),而不会与每一个第一共用电极122都重叠。因此,数据线dl与第一共用电极122之间的寄生电容小,使得数据线dl的负载减轻,进而增进像素结构spx的充电效率、提升像素阵列基板10的性能。

102.在本实施例中,每一第一共用电极122的多个线段122a、122b包括多个第一线段122a及多个第二线段122b,每一第一线段122a与至少一数据线dl交错设置,每一第二线段122b与对应的一像素结构spx的连接图案142交错且未与数据线dl重叠。

103.于正常的情况下(或者说,第一共用电极122未被用以修补像素阵列基板10的情况下),每一第一共用电极122的多个第一线段122a及多个第二线段122b是各自电性连接至对应的一第二共用电极124;第一共用电极122的多个第一线段122a、第一共用电极122的多个第二线段122b及第二共用电极124具有相同的参考电位;但本发明不以此为限。

104.举例而言,在本实施例中,每一第一线段122a可与三条数据线dl交错设置,且左右相邻的两个第一线段122a之间可设有分别与两个连接图案142交错的两个第二线段122b-1、122b-2。然而,本发明不以此为限,与同一第一线段122a交错的数据线dl的数量及/或位于相邻两个第一线段122a之间的第二线段122b的数量均可视实际需求而改变。

105.值得一提的是,在本实施例中,第二线段122b的设置可使得分别对应第一线段122a及第二线段122b的多个像素结构spx与第一共用电极122之间的寄生电容较为接近。如此一来,分别对应第一线段122a及第二线段122b的多个像素结构spx可具有相近的光学表现,以提升具有像素阵列基板10的显示面板(未示出)的整体显示品质。

106.请参照图2,在本实施例中,分别对应多个像素列rspx的多个第一共用电极122的多个第一线段122a及多个第二线段122b-1可在第一方向x上及第二方向y上交替排列。换言之,分别对应于多个第一线段122a的多群像素结构spx的连线大致上可呈第一菱格纹dm1,且分别对应于多个第二线段122b-1的多个像素结构spx的连线大致上可呈第二菱格纹dm2。因此,即便分别对应于多个第一线段122a及多个第二线段122b的多个像素结构spx的光学表现(例如:亮度)略有差异,也不易过度影响具有像素阵列基板10的显示面板的整体显示

品质。

107.举例而言,在本实施例中,第一共用电极122可选择性地属于第一金属层120,但本发明不以此为限。基于导电性的考量,在本实施例中,第一共用电极122是使用金属材料。然而,本发明不限于此,根据其他实施例,第一共用电极122也可以使用其他导电材料,例如:合金、金属材料的氮化物、金属材料的氧化物、金属材料的氮氧化物、或是金属材料与其它导电材料的堆叠层。

108.请参照图2,在本实施例中,像素阵列基板10还包括多个第二共用电极124;多个像素结构spx排成多个像素列rspx,每一像素列rspx的多个像素结构spx沿第一方向x排列;每一第二共用电极124与对应的一像素列rspx的多个像素结构spx的多个像素电极202部分地重叠。每一第二共用电极124用以与多个像素电极202形成多个像素结构spx的存储电容。在像素阵列基板10的俯视图中,每一第一共用电极122可设置于对应的一条栅极线gl与对应及一个第二共用电极124之间。

109.举例而言,在本实施例中,第二共用电极124可选择性地属于第一金属层120,但本发明不以此为限。基于导电性的考量,在本实施例中,第二共用电极124是使用金属材料。然而,本发明不限于此,根据其他实施例,第二共用电极124也可以使用其他导电材料,例如:合金、金属材料的氮化物、金属材料的氧化物、金属材料的氮氧化物、或是金属材料与其它导电材料的堆叠层。

110.请参照图1及图2,在本实施例中,像素阵列基板10还包括多条转接线gl。多条转接线gl设置于基底110上,且在第一方向x上排列。在第一方向x上排列的多条转接线gl分别电性连接至在第二方向y上排列的多条栅极线gl。请参照图2,在本实施例中,多个像素结构spx排成多个像素行cspx,每一像素行cspx的多个像素结构spx沿第二方向y排列;在像素阵列基板10的俯视图中,每一转接线gl设置于多个像素行cspx的相邻两者之间。

111.请参照图1、图2及图3,举例而言,在本实施例中,多条栅极线gl可选择性地属于第一金属层120,多条转接线gl的主要部gla可选择性地属于第二金属层140,第一金属层120与第二金属层140之间设有栅绝缘层130(绘于图4),栅绝缘层130具有多个接触窗130a(绘于图1),多条转接线gl的主要部gla可通过栅绝缘层130的多个接触窗130a分别与多条栅极线gl电性连接,但本发明不以此为限。

112.请参照图2、图3及图4,在本实施例中,像素阵列基板10还可选择性地包括透明屏蔽图案182。透明屏蔽图案182设置于转接线gl所属的至少一膜层与像素电极202所属的膜层之间,以屏蔽转接线gl的栅极驱动信号对像素电极202的电位的干扰。举例而言,在本实施例中,透明屏蔽图案182所属的第一透明导电层180可设置于转接线gl的主要部gla所属的第二金属层140与像素电极202所属的第二透明导电层200之间。

113.请参照图4,具体而言,在本实施例中,透明屏蔽图案182可选择性地设置于第二钝化层170上,且位于平坦层190与第二钝化层170之间,但本发明不以此为限。根据其它实施例,透明屏蔽图案182也可设置于转接线gl与像素电极202之间的其它位置;或者,也可省略透明屏蔽图案182的设置。

114.请参照图2,在本实施例中,于像素阵列基板10的俯视图中,第一共用电极122的线段122a与数据线dl具有第一交错处x1,且第一交错处x1可重叠于透明屏蔽图案182的开口182a。换言之,透明屏蔽图案182的实体在第一共用电极122与数据线dl的第一交错处x1让

开且未与第一交错处x1重叠。

115.请参照图2,在本实施例中,像素阵列基板10还包括多个第三共用电极144,沿第一方向x排列;在像素阵列基板10的俯视图中,每一第三共用电极144设置于多个像素行cspx的相邻两者之间。

116.举例而言,在本实施例中,第三共用电极144具有跨越多条栅极线gl的主要部144m,第三共用电极144的主要部144m可属于第二金属层140,但本发明不以此为限。基于导电性的考量,在本实施例中,第三共用电极144是使用金属材料。然而,本发明不限于此,根据其他实施例,第三共用电极144也可以使用其他导电材料,例如:合金、金属材料的氮化物、金属材料的氧化物、金属材料的氮氧化物、或是金属材料与其它导电材料的堆叠层。

117.在本实施例中,第一共用电极122的线段122a与第三共用电极144具有第二交错处x2,且第二交错处x2重叠于透明屏蔽图案182的开口182a。换言之,透明屏蔽图案182的实体在第一共用电极122与第三共用电极144的第二交错处x2让开且未与第二交错处x2重叠。

118.在本实施例中,于像素阵列基板10的俯视图中,第一共用电极122的一线段122a与一转接线gl具有第三交错处x3,且第三交错处x3重叠于透明屏蔽图案182的开口182a。换言之,透明屏蔽图案182的实体在第一共用电极122与转接线gl的第三交错处x3让开且未与第三交错处x3重叠。

119.在本实施例中,于像素阵列基板10的俯视图中,第一共用电极122的线段122a与另一第三共用电极144具有第四交错处x4,且第四交错处x4重叠于透明屏蔽图案182的开口182a。换言之,透明屏蔽图案182的实体在第一共用电极122的线段122a与另一第三共用电极144的第四交错处x4让开且未与第四交错处x4重叠。

120.值得注意的是,当信号线(例如:数据线dl及/或转接线gl)断线时,可使用横向设置的第一共用电极122及直向设置的第三共用电极144来修补,以下以图5为例说明。

121.图5为本发明一实施例的像素阵列基板10’的俯视示意图。图5的像素阵列基板10’与图2的像素阵列基板10类似,因此相同或相似的元件以相同或相似的元件符号表示,以下说明两者的差异处,两者相同或相似处请参照上述说明,于此便不再重述。此外,为清楚示出起见,图5省略像素电极202的示出。

122.图2的像素阵列基板10是正常的(或者说,未修补的)像素阵列基板,而图5的像素阵列基板10’是修过的像素阵列基板。

123.请参照图5,具体而言,在本实施例中,一数据线dl具有断开处dlo,断开处dlo将数据线dl分为第一部分dl-1及第二部分dl-2,其中数据线dl的第一部分dl-1位于断开处dlo的上方,且数据线dl的第二部分dl-2位于断开处dlo的下方。

124.为修补断开的数据线dl,在本实施例中,可熔接数据线dl的第一部分dl-1和与其交错的第一共用电极122的一线段122a,以使第一共用电极122的一线段122a与数据线dl的第一部分dl-1具有第一熔接处w1并彼此电性连接。在本实施例中,于像素阵列基板10’的俯视图中,第一熔接处w1可重叠于透明屏蔽图案182的开口182a,但本发明不以此为限。

125.在本实施例中,还可熔接与数据线dl的第一部分dl-1交错的第一共用电极122的线段122a与一第三共用电极144的一处144a,以使第一共用电极122的线段122a与第三共用电极144具有第二熔接处w2并彼此电性连接。在本实施例中,于像素阵列基板10’的俯视图中,第二熔接处w2可重叠于透明屏蔽图案182的开口182a,但本发明不以此为限。

126.在本实施例中,还可熔接第三共用电极144的另一处144b和与其交错的另一第一共用电极122的一线段122a,以使另一第一共用电极122的一线段122a与第三共用电极144的另一处144b具有第五熔接处w5并彼此电性连接。在本实施例中,于像素阵列基板10’的俯视图中,第五熔接处w5可重叠于透明屏蔽图案182的另一开口182a,但本发明不以此为限。

127.在本实施例中,还可熔接数据线dl的第二部分dl-2和与其交错的另一第一共用电极122的一线段122a,以使另一第一共用电极122的一线段122a与数据线dl的第二部分dl-2具有第六熔接处w6并彼此电性连接。在本实施例中,于像素阵列基板10’的俯视图中,第六熔接处w6可重叠于透明屏蔽图案182的另一开口182a,但本发明不以此为限。

128.在本实施例中,还可使具有第二熔接点w2及第五熔接点w5的第三共用电极144的一部分与第三共用电极144的其它部分断开。具体而言,在本实施例中,第三共用电极144可具有位于第二熔接点w2上方的一第一断开处c1以及位于第五熔接点w5下方的一第三断开处c3。在本实施例中,透明屏蔽图案182的开口182a可具有凹陷部182a-1,重叠于第一断开处c1,但本发明不此为限。

129.此外,在本实施例中,还可使具有第一熔接点w1及第二熔接点w2的一线段122a与相邻的第二共用电极124具有一第四断开处c4,使具有第五熔接点w5及第六熔接点w6的另一线段122a与相邻的第二共用电极124具有一第五断开处c5。

130.在形成上述的第一熔接点w1、第二熔接点w2、第五熔接点w6、第六熔接点w6、第一断开处c1、第三断开处c3、第四断开处c4及第五断开处c5后,数据线dl的第一部分dl-1的数据信号s

dl

便可通过第一熔接点w1、与数据线dl的第一部分dl-1交错的一第一共用电极122的线段122a、第二熔接点w2、被第一断开处c1及第三断开处c3截出的第三共用电极144的一部分、第五熔接点w5、与数据线dl的第二部分dl-2交错的另一第一共用电极122的线段122a及第六熔接点w6传递至数据线dl的第二部分dl-2,进而使像素阵列基板10’能正常运行。

131.请参照图5,在本实施例中,一转接线gl具有断开处glo,断开处glo将转接线gl分为第一部分gl-1及第二部分gl-2,其中转接线gl的第一部分gl-1位于断开处glo的上方,且转接线gl的第二部分gl-2位于断开处glo的下方。

132.在本实施例中,可熔接转接线gl的第一部分gl-1和与其交错的一第一共用电极122的一线段122a,以使第一共用电极122的一线段122a与转接线gl的第一部分gl-1具有第三熔接处w3并彼此电性连接。在本实施例中,于像素阵列基板10’的俯视图中,第三熔接处w3可重叠于透明屏蔽图案182的开口182a,但本发明不以此为限。

133.在本实施例中,还可熔接与转接线gl的第一部分gl-1交错的第一共用电极122的线段122a与另一第三共用电极144的一处144c,以使第一共用电极122的线段122a与第三共用电极144具有第四熔接处w4并彼此电性连接。在本实施例中,于像素阵列基板10’的俯视图中,第四熔接处w4可重叠于透明屏蔽图案182的开口182a,但本发明不以此为限。

134.在本实施例中,还可熔接所述另一第三共用电极144的另一处144d和与其交错的另一第一共用电极122的线段122a,以使另一第一共用电极122的线段122a与第三共用电极144的另一处144d具有第七熔接处w7并彼此电性连接。在本实施例中,于像素阵列基板10’的俯视图中,第七熔接处w7可重叠于透明屏蔽图案182的另一开口182a,但本发明不以此为限。

135.在本实施例中,还可熔接转接线gl的第二部分gl-2和与其交错的另一第一共用电

极122的线段122a,以使另一第一共用电极122的线段122a与转接线gl的第二部分gl-2具有第八熔接处w8并彼此电性连接。在本实施例中,于像素阵列基板10’的俯视图中,第八熔接处w8可重叠于透明屏蔽图案182的另一开口182a,但本发明不以此为限。

136.在本实施例中,还可使具有第四熔接点w4及第七熔接点w7的第三共用电极144的一部分与第三共用电极144的其它部分断开。具体而言,第三共用电极144可具有位于第四熔接点w4上方的一第二断开处c2,且具有位于第七熔接点w7下方的一第六断开处c6。在本实施例中,透明屏蔽图案182的开口182a可具有凹陷部182a-2,重叠于第二断开处c2,但本发明不此为限。

137.此外,在本实施例中,还可使具有第三熔接点w3及第四熔接点w4的第一共用电极122的第一线段122a与相邻的第二共用电极124具有一第七断开处c7,具有第七熔接点w7及第八熔接点w8的第一共用电极122的第一线段122a与相邻的第二共用电极124具有一第八断开处c8。

138.在形成上述的第三熔接点w3、第四熔接点w4、第七熔接点w7、第八熔接点w8、第二断开处c2、第六断开处c6、第七断开处c7及第八断开处c8后,转接线gl的第一部分gl-1的栅极驱动信号s

gl

便可通过第三熔接点w3、与转接线gl的第一部分gl-1交错的第一共用电极122的线段122a、第四熔接点w4、被第二断开处c2及第六断开处c6截出的第三共用电极144的一部分、第七熔接点w7、与转接线gl的第二部分gl-2交错的另一第一共用电极122的线段122a及第八熔接点w8传递至转接线gl的第二部分gl-2,进而使像素阵列基板10’能正常运行。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。