1.本发明涉及一种半导体集成电路制造方法,特别是涉及一种栅氧的形成方法。

背景技术:

2.在半导体集成电路中,半导体器件如cmos,vdmos,igbt等都会采用栅氧,栅氧的顶部会形成栅导电材料层如多晶硅栅,被多晶硅栅所覆盖的阱区作为沟道区,通过在将栅极电压加到所述多晶硅栅之后,所述多晶硅栅会使沟道区的表面反型并形成导电沟道,载流子在导电沟道中流动形成沟道电流。栅氧则作为多晶硅栅和沟道区之间的隔离层,防止沟道区和多晶硅栅之间产生漏电流,所以,栅氧的质量较好时能降低漏电流,提高器件的可靠性。

3.但是,在通过栅氧控制电压的器件在工艺过程中,经常会出现电荷或热载流子等相关因素导致栅氧的电学参数在测试过程中失效,漏电流增大从而降低可靠性的情况。其中,影响栅氧的电学性能的电荷包括栅氧中的界面态俘获的电荷;热载流子则是在器件导通中经过电场加速的沟道区表面的载流子,通常在漏区电压较大时会对沟道区产生耗尽从而形成较大的电场,电场会使载流子加速形成热载流子,热载流子能量较大时会进入到栅氧或穿过栅氧从而使栅氧的电学性能变差。

4.为了改进这种状况,也即为了防止栅氧在电荷或热载流子的作用下而导致的电学参数变差这种状况,一种方面,需要提高栅氧本身的品质,降低界面态,减少俘获电荷,提升本征击穿电压。另一方面,改善栅氧的形貌也逐渐的提到日程上来。如何形成符合要求的形貌成为技术关键点。

技术实现要素:

5.本发明所要解决的技术问题是提供一种栅氧的形成方法,能改善栅氧的形貌,从而能提高器件的击穿电压和可靠性。

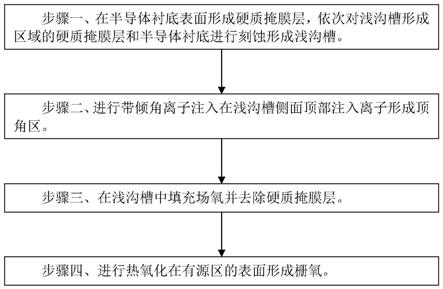

6.为解决上述技术问题,本发明提供的栅氧的形成方法包括如下步骤:

7.步骤一、在半导体衬底表面形成硬质掩膜层,依次对浅沟槽形成区域的所述硬质掩膜层和所述半导体衬底进行刻蚀形成浅沟槽,有源区由位于所述浅沟槽之间的所述半导体衬底组成,所述有源区表面的所述硬质掩膜层保留。

8.步骤二、进行带倾角离子注入在所述浅沟槽侧面顶部注入离子形成顶角区,所述顶角区位于所述有源区的外侧边缘。

9.步骤三、在所述浅沟槽中填充场氧并去除所述硬质掩膜层。

10.步骤四、进行热氧化在所述有源区的表面形成栅氧;在所述栅氧的热氧化过程中,所述顶角区中注入的离子使所述顶角区的热氧化速率增加,使所述栅氧在所述顶角区的表面的厚度增加并从而使所述栅氧在所述顶角区的具有圆化形貌。

11.进一步的改进是,所述半导体衬底为硅衬底。

12.进一步的改进是,所述硬质掩膜层由氮化层组成或者由氧化层和氮化层叠加而

成。

13.进一步的改进是,步骤二中,所述带倾角离子注入的注入能量的最大值要求保证注入的离子不会穿过所述硬质掩膜层到达所述硬质掩膜层底部的所述有源区的表面。

14.进一步的改进是,所述带倾角离子注入的注入能量为500kev~5kev。

15.进一步的改进是,步骤二中,所述顶角区的纵向深度由所述硬质掩膜层的厚度、所述浅沟槽的顶部开口宽度以及所述带倾角离子注入的注入角度;所述硬质掩膜层的厚度和所述浅沟槽的顶部开口宽度为固定值,所述带倾角离子注入的注入角度为可设定值,通过设定所述带倾角离子注入的注入角度设定所述顶角区的纵向深度。

16.进一步的改进是,步骤二中,所述带倾角离子注入的注入总剂量分多次完成。

17.进一步的改进是,步骤二中,所述带倾角离子注入的注入过程中,所述半导体衬底的法线沿着所述带倾角离子注入的注入方向自转。

18.进一步的改进是,步骤二中,所述带倾角离子注入的注入离子包括氩离子或氟离子。

19.进一步的改进是,步骤四中,所述栅氧的热氧化的温度为800℃~1100℃。

20.进一步的改进是,步骤三中,所述场氧的淀积工艺采用hdpcvd工艺。

21.进一步的改进是,所述场氧的淀积工艺完成后还包括对所述场氧进行回刻或化学机械研磨,使所述场氧仅填充于所述浅沟槽中。

22.进一步的改进是,步骤四完成后还包括如下步骤:

23.形成栅极导电材料层。

24.对所述栅极导电材料层进行图形化,图形化后的所述栅极导电材料层仅位于栅极结构的形成区域,由所述栅氧和顶部的所述栅极导电材料层叠加而成。

25.进一步的改进是,所述栅极导电材料层的材料包括多晶硅。

26.进一步的改进是,采用所述栅氧的半导体器件包括cmos,vdmos和igbt。

27.针对本发明所要解决的技术问题,本发明在栅氧形成之前预先对半导体衬底进行处理,具体为在浅沟槽形成之后以及在浅沟槽中填充场氧之前,增加了带倾角离子注入,带倾角离子注入能将离子注入到浅沟槽侧面的顶部并形成顶角区而且能调节顶角区的纵向深度,由于有源区是由浅沟槽定义的,有源区的边缘正好位于顶角区,故顶角区中注入的离子能增加栅氧的热氧化工艺中的热氧化速率,从而能增加顶角区表面的栅氧厚度并使栅氧在顶角区的具有圆化形貌。

28.而现有工艺中,在本发明对应的顶角区中没有注入离子,在栅氧的热氧化工艺中,顶角区表面的热氧化速率会慢于有源区的内部区域表面的热氧化速率且二者相差较大,有源区的内部区域表面为位于顶角区内侧的有源区表面,这样会使顶角区表面的栅氧的厚度和有源区的内部区域表面的栅氧的差异较大,使得顶角区表面的栅氧成为整个有源区表面的栅氧的薄弱环节,从而容易在顶角区表面的栅氧处发生击穿,并降低器件的可靠性。

29.而本发明通过增加顶角区表面的栅氧厚度后,能使顶角区表面的栅氧厚度和有源区的内部区域表面的栅氧厚度的差异变小且能使顶角区的栅氧更加圆化,能提升在顶角区表面的栅氧处耐压能力,最后能提高整个有源区表面的栅氧的耐压能力,从而能提高器件的击穿电压和可靠性。

附图说明

30.下面结合附图和具体实施方式对本发明作进一步详细的说明:

31.图1是本发明实施例栅氧的形成方法的流程图;

32.图2a-图2f是本发明实施例方法各步骤中的器件结构图;

33.图3是本发明实施例方法的步骤二中顶角区的纵向深度和带倾角离子注入的注入角度的关系示意图;

34.图4a是现有技术中未进行本发明实施例方法的带倾角离子注入时形成的栅氧的照片;

35.图4b是本发明实施例方法形成的栅氧的照片。

具体实施方式

36.如图1所示,是本发明实施例栅氧7的形成方法的流程图;如图2a至图2f所示,是本发明实施例方法各步骤中的器件结构图;本发明实施例栅氧7的形成方法包括如下步骤:

37.步骤一、如图2a所示,在半导体衬底1表面形成硬质掩膜层。

38.本发明实施例方法中,所述半导体衬底1为硅衬底。

39.所述硬质掩膜层由氧化层2和氮化层3叠加而成。在其他实施例方法中,也能为:所述硬质掩膜层由氮化层组成。

40.依次对浅沟槽4形成区域的所述硬质掩膜层和所述半导体衬底1进行刻蚀形成浅沟槽4,有源区由位于所述浅沟槽4之间的所述半导体衬底1组成,所述有源区表面的所述硬质掩膜层保留。

41.本发明实施例方法中,浅沟槽4的形成区域通过光刻工艺形成的光刻胶图形定义;在刻蚀所述硬质掩膜层之后,去除所述光刻胶图形,之后再以所述硬质掩膜层为掩膜对底部的所述半导体衬底1进行刻蚀形成所述浅沟槽。

42.步骤二、进行带倾角离子注入在所述浅沟槽4侧面顶部注入离子形成顶角区5,所述顶角区5位于所述有源区的外侧边缘。

43.本发明实施例中,所述带倾角离子注入的注入能量的最大值要求保证注入的离子不会穿过所述硬质掩膜层到达所述硬质掩膜层底部的所述有源区的表面。较佳为,所述带倾角离子注入的注入能量为500kev~5kev。

44.所述带倾角离子注入的注入离子包括氩离子或氟离子。

45.所述带倾角离子注入的注入总剂量分多次完成。所述带倾角离子注入的注入过程中,所述半导体衬底1的法线沿着所述带倾角离子注入的注入方向自转。

46.如图2b所示,是所述半导体衬底1在一个方向时进行所述带倾角离子注入时的示意图,箭头线201表示所述带倾角离子注入,注入角度为所述带倾角离子注入的注入方向和所述半导体衬底1的法线方向的夹角。在图2b中,所述带倾角离子注入仅能对所述浅沟槽4的一个侧面的顶部进行注入,注入形成的所述顶角区单独用标记5a表示。

47.如图2c所示,是所述半导体衬底1转动到另一个方向时进行所述带倾角离子注入时的示意图,可以看出,所述带倾角离子注入会对所述浅沟槽4的另一个侧面的顶部进行注入,该次注入形成的所述顶角区单独用标记5b表示。

48.随着所述半导体衬底1的法线沿着所述带倾角离子注入的注入方向自转并进行分

批次的注入,能确保最后形成的各所述浅沟槽4顶部的所述顶角区5的注入剂量均匀,如图2d所示,是完成所述带倾角离子注入时的示意图。

49.所述顶角区5的纵向深度由所述硬质掩膜层的厚度、所述浅沟槽4的顶部开口宽度以及所述带倾角离子注入的注入角度;所述硬质掩膜层的厚度和所述浅沟槽4的顶部开口宽度为固定值,所述带倾角离子注入的注入角度为可设定值,通过设定所述带倾角离子注入的注入角度设定所述顶角区5的纵向深度。图2d中,d1表示所述硬质掩膜层的厚度。d2表示所述顶角区5的底部处的所述浅沟槽4的宽度,如果所述浅沟槽4的侧面垂直的话,d2等于所述浅沟槽4的顶部开口宽度;如果所述浅沟槽4的侧面倾斜的话,d2也能从所述浅沟槽4的顶部开口宽度得到,通常d2约等于所述浅沟槽4的顶部开口宽度。dx表示表示所述顶角区5的宽度。α表示所述带倾角离子注入的注入角度。

50.如图3所示,是本发明实施例方法的步骤二中顶角区的纵向深度和带倾角离子注入的注入角度的关系示意图;图2d中对应的d1、d2和dx以及α也在图3中标出,图3中的三角形的斜边对应于所述带倾角离子注入的注入方向,从图3可以得到:tg(α)=d2/(d1 dx);

51.进行变化可以得到:dx=(d2-d1*tg(α))/tg(α)。

52.由于上述公式可以看出,d1和d2为固定值,例如d1能取d2能取d1和d2的具体值能根据实际工艺变化,但是一旦设定之后就不再改变,也即在步骤二中不会再改变。但是在步骤二中能调节α,且是通过调节α调节dx。

53.步骤三、如图2e所示,在所述浅沟槽4中填充场氧6并去除所述硬质掩膜层。

54.本发明实施例方法中,所述场氧6的淀积工艺采用hdpcvd工艺。

55.所述场氧6的淀积工艺完成后还包括对所述场氧6进行回刻或化学机械研磨,使所述场氧6仅填充于所述浅沟槽4中。

56.步骤四、如图2f所示,进行热氧化在所述有源区的表面形成栅氧7;在所述栅氧7的热氧化过程中,所述顶角区5中注入的离子使所述顶角区5的热氧化速率增加,使所述栅氧7在所述顶角区5的表面的厚度增加并从而使所述栅氧7在所述顶角区5的具有圆化形貌。图2f中,和未进行所述带倾角离子注入相比,本发明实施例方法能使虚线圈102处的所述场氧7的厚度增加且形貌更加圆化。

57.本发明实施例方法中,所述栅氧7的热氧化的温度为800℃~1100℃。

58.为了进一步详细说明本发明实施例方法形成的所述栅氧7在所述顶角区5的表面的厚度会增加,现结合所述栅氧7对应的照片进行说明:

59.如图4a所示,是现有技术中未进行本发明实施例方法的带倾角离子注入时形成的栅氧的照片;图4a中,所述半导体衬底单独用标记1a标出,所述场氧单独用标记6a标出,所述栅氧单独用标记7a标出。所述顶角区的表面的所述栅氧7a位于虚线圈102a,所述顶角区的表面的所述栅氧7a的厚度用d4a表示,所述顶角区内侧的所述有源区表面的所述栅氧7b的厚度用d3a表示;d3a的大小为d4a的大小为d4a和d3a的比值为76.88%。d4a和d3a的比值表示现有方法形成的所述栅氧7a的台阶覆盖能力。

60.如图4b所示,是本发明实施例方法形成的栅氧的照片;图4b中,所述半导体衬底单独用标记1b标出,所述场氧单独用标记6b标出,所述栅氧单独用标记7b标出。所述顶角区的表面的所述栅氧7b位于线框102b中,所述顶角区的表面的所述栅氧7b的厚度用d4b表示,所

述顶角区内侧的所述有源区表面的所述栅氧7b的厚度用线宽103中的d3b表示;d3b的大小为d4b的大小为d4b和d3b的比值为88.89%。d4b和d3b的比值表示本发明实施例方法形成的所述栅氧7b的台阶覆盖能力,可以看出本发明实施例方法形成的所述栅氧7b的台阶覆盖能力得到显著的增加即从76.88%增加到了88.89%。

61.步骤四完成后还包括如下步骤:

62.形成栅极导电材料层。通常,所述栅极导电材料层的材料包括多晶硅。

63.对所述栅极导电材料层进行图形化,图形化后的所述栅极导电材料层仅位于栅极结构的形成区域,由所述栅氧7和顶部的所述栅极导电材料层叠加而成。

64.采用所述栅氧7的半导体器件包括cmos,vdmos和igbt。

65.针对本发明所要解决的技术问题,本发明实施例在栅氧7形成之前预先对半导体衬底1进行处理,具体为在浅沟槽4形成之后以及在浅沟槽4中填充场氧6之前,增加了带倾角离子注入,带倾角离子注入能将离子注入到浅沟槽4侧面的顶部并形成顶角区5而且能调节顶角区5的纵向深度,由于有源区是由浅沟槽4定义的,有源区的边缘正好位于顶角区5,故顶角区5中注入的离子能增加栅氧7的热氧化工艺中的热氧化速率,从而能增加顶角区5表面的栅氧7厚度并使栅氧7在顶角区5的具有圆化形貌。

66.而现有工艺中,在本发明实施例对应的顶角区5中没有注入离子,在栅氧7的热氧化工艺中,顶角区5表面的热氧化速率会慢于有源区的内部区域表面的热氧化速率且二者相差较大,有源区的内部区域表面为位于顶角区5内侧的有源区表面,这样会使顶角区5表面的栅氧7的厚度和有源区的内部区域表面的栅氧7的差异较大,使得顶角区5表面的栅氧7成为整个有源区表面的栅氧7的薄弱环节,从而容易在顶角区5表面的栅氧7处发生击穿,并降低器件的可靠性。

67.而本发明实施例通过增加顶角区5表面的栅氧7厚度后,能使顶角区5表面的栅氧7厚度和有源区的内部区域表面的栅氧7厚度的差异变小且能使顶角区5的栅氧7更加圆化,能提升在顶角区5表面的栅氧7处耐压能力,最后能提高整个有源区表面的栅氧7的耐压能力,从而能提高器件的击穿电压和可靠性。

68.以上通过具体实施例对本发明进行了详细的说明,但这些并非构成对本发明的限值。在不脱离本发明原理的情况下,本领域的技术人员还可做出许多变形和改进,这些也应视为本发明的保护范围。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。