技术特征:

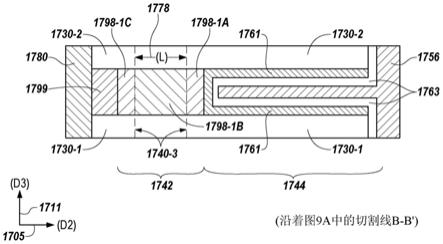

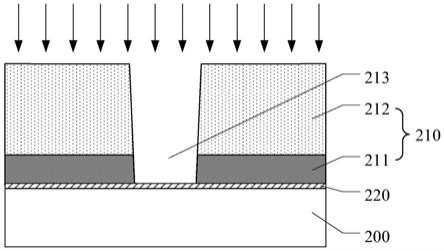

1.一种用于形成竖直堆叠的存储器单元(110,1810)的阵列(101)的方法,所述阵列具有水平定向的存取装置(230,330,998)和竖直定向的存取线(103,203,540,640,740,840,940,1640,1740),其包括:以重复迭代沉积介电材料(430,530,630,730,830,930)和牺牲材料(432,532,632,732)的交替层以形成竖直堆叠(401);使用第一蚀刻过程形成第一竖直开口(500),从而暴露所述竖直堆叠(401)中邻近所述牺牲材料(432,532,632,732)的第一部分的竖直侧壁(514);选择性地蚀刻所述牺牲材料(432,532,632,732)的第一部分以形成第一水平开口(833),所述第一水平开口在第一区(742,842,942,1042,1242,1342,1442,1542,1642)中去除所述牺牲材料(432,532,632,732)并与所述第一竖直开口(500)相隔第一水平距离,以形成通过沟道区(225,325,938-1b,1798-1b)水平地分隔开的第一源极/漏极区(221,321,998-1a,1798-1a)和第二源极/漏极区(223,323,998-1c,1798-1c);以及在所述第一水平开口(833)中沉积多层第一源极/漏极材料(1071-1,1171-1,1271-1,1371-1,1471-1,1571-1,1671-1)、沟道材料(1398,1798-1b)和第二源极/漏极材料(1798-1c),以形成竖直堆叠的存储器单元(110,1810)的所述阵列(101)当中的存储器单元(110,1810)的三节点存取装置(230,330,998)。2.根据权利要求1所述的方法,其中沉积所述多层第一源极/漏极材料(1071-1,1171-1,1271-1,1371-1,1471-1,1571-1,1671-1)包括沉积第一材料(1071-1,1171-1,1271-1,1371-1,1471-1,1571-1,1671-1)以在所述第一水平开口(833)相对于所述第一竖直开口(500)的远端处形成与存储节点(227,327,1744)的电性接触。3.根据权利要求1至2中任一权利要求所述的方法,其中沉积所述多层第一源极/漏极材料(1071-1,1171-1,1271-1,1371-1,1471-1,1571-1,1671-1)包括在所述第一水平开口(833)中沉积在与氧化物半导体沟道材料(1398,1798-1b)接触时不氧化的金属层作为第一材料(1071-1,1171-1,1271-1,1371-1,1471-1,1571-1,1671-1)。4.根据权利要求1至2中任一权利要求所述的方法,其中沉积所述多层第一源极/漏极材料(1071-1,1171-1,1271-1,1371-1,1471-1,1571-1,1671-1)包括在所述第一水平开口(833)中沉积在与氧化物沟道材料(1398,1798-1b)接触时形成导电氧化物的金属层作为第一材料(1071-1,1171-1,1271-1,1371-1,1471-1,1571-1,1671-1)。5.根据权利要求1至2中任一权利要求所述的方法,其进一步包括使用原子层沉积ald过程在所述第一水平开口(833)中沉积与所述第一材料(1071-1,1171-1,1271-1,1371-1,1471-1,1571-1,1671-1)电性接触的第二材料(1798-1c),其中所述第二材料(1798-1c)是具有低于所述沟道材料(1398,1798-1b)的电子带隙的电子带隙的第二半导体材料(1798-1c)。6.一种用于形成竖直堆叠的存储器单元(110,1810)的阵列(101)的方法,所述阵列具有水平定向的存取装置(230,330,998)和竖直定向的存取线(103,203,540,640,740,840,940,1640,1740),其包括:以重复迭代沉积介电材料(430,530,630,730,830,930)和牺牲材料(432,532,632,732)的交替层以形成竖直堆叠(401);形成多个第一竖直开口(500),其具有第一水平方向(109,209,509,609,709,809,909)

和第二水平方向(105,205,305,505,605,705,805,905,1005,1205,1305,1405,1505,1605,1705)、穿过所述竖直堆叠(401),且主要在所述第二水平方向(105,205,305,505,605,705,805,905,1005,1205,1305,1405,1505,1605,1705)上延伸以在所述竖直堆叠(401)中形成带侧壁(514)的细长竖直柱形列(513,542);在所述第一竖直开口(500)中的栅极介电材料(304,538,638,738,838,938)上保形地沉积第一导电材料(1071-1,1171-1,1271-1);去除所述第一导电材料(1071-1,1171-1,1271-1)的部分,以沿着所述细长竖直柱形列(513,542)的所述侧壁(514)形成多个单独的竖直存取线(103,203,540,640,740,840,940,1640,1740);形成第二竖直开口(871,971),从而暴露所述竖直堆叠(401)中邻近所述牺牲材料(432,532,632,732)的第一部分的竖直侧壁(514);选择性地蚀刻所述牺牲材料(432,532,632,732)的所述第一部分以形成第一水平开口(833),所述第一水平开口在第一区(742,842,942,1042,1242,1342,1442,1542,1642)中去除所述牺牲材料(432,532,632,732)且与所述第一竖直开口(500)相隔第一水平距离;以及使用选择性沉积过程以在所述第一水平开口(833)中沉积:多层第一源极/漏极材料(1071-1,1171-1,1271-1,1371-1,1471-1,1571-1,1671-1),其与所述第一水平开口(833)相对于所述第一竖直开口(500)的远端处的存储节点(227,327,1744)电性接触;沟道材料(1398,1798-1b);以及多层第二源极/漏极材料(1798-1c),用于形成竖直堆叠的存储器单元(110,1810)的所述阵列(101)当中的存储器单元(110,1810)的三节点存取装置(230,330,998)。7.根据权利要求6所述的方法,其进一步包括:沉积所述多层第一源极/漏极材料(1071-1,1171-1,1271-1,1371-1,1471-1,1571-1,1671-1)的第n源极/漏极材料(1275-1,1375-1,1475-1,1575-1,1675-1),其具有在先前(第n-1)源极/漏极材料(1273-1,1373-1,1473-1,1573-1,1673-1)的电子带隙和所述沟道材料(1398,1798-1b)的电子带隙中间的电子带隙;以及沉积所述多层第一源极/漏极材料(1071-1,1171-1,1271-1,1371-1,1471-1,1571-1,1671-1)的第n源极/漏极材料(1275-1,1375-1,1475-1,1575-1,1675-1),其具有在先前(第n-1)源极/漏极材料(1273-1,1373-1,1473-1,1573-1,1673-1)的导带偏移和所述沟道材料(1398,1798-1b)的导带偏移中间的导带偏移。8.根据权利要求6至7中任一权利要求所述的方法,其进一步包括沉积所述多层第一源极/漏极材料(1071-1,1171-1,1271-1,1371-1,1471-1,1571-1,1671-1)的所述第n源极/漏极材料(1275-1,1375-1,1475-1,1575-1,1675-1),配合沉积先前(第n-1)源极/漏极材料(1273-1,1373-1,1473-1,1573-1,1673-1)以形成在组成上分级的接触材料。9.根据权利要求6至7中任一权利要求所述的方法,其进一步包括沉积具有反馈沟道钝化材料且与第n源极/漏极材料(1275-1,1375-1,1475-1,1575-1,1675-1)电性接触的沟道材料(1398,1798-1b)。10.根据权利要求9所述的方法,其进一步包括:沉积富含铟的氧化铟镓锌igzo沟道材料(1398,1798-1b)以形成与栅极电介质(304,

2)电性接触。13.根据权利要求11至12中任一权利要求所述的方法,其中沉积所述多层第二源极/漏极材料(1798-1c)包括:沉积所述第一半导体材料(1475-2,1575-2,1675-2);沉积与所述第一半导体材料(1475-2,1575-2,1675-2)电性接触的所述第二半导体材料(1673-2);以及沉积基于具有在所述第一半导体材料(1475-2,1575-2,1675-2)的电子带隙和所述后续半导体材料(1699)的电子带隙中间的电子带隙而选择的所述第二半导体材料(1673-2),所述后续半导体材料形成为与所述第二半导体材料(1673-2)电性接触。14.根据权利要求11至12中任一权利要求所述的方法,其中沉积所述多层第二源极/漏极材料(1798-1c)包括:沉积所述第一半导体材料(1475-2,1575-2,1675-2);沉积与所述第一半导体材料(1475-2,1575-2,1675-2)电性接触的所述第二半导体材料(1673-2);以及沉积基于具有在所述第一半导体材料(1475-2,1575-2,1675-2)的导带偏移和后续半导体材料(1699)的导带偏移中间的导带偏移而选择的所述第二半导体材料(1673-2),所述后续半导体材料形成为与所述第二半导体材料(1673-2)电性接触。15.根据权利要求11至12中任一权利要求所述的方法,其进一步包括集成水平定向的数字线(107-1,107-2,107-q,207-1,20-2,207-p,307,999-1,999-2,999-3,999-n,1699,1799)以形成与所述多层第二源极/漏极材料(1798-1c)的电性接触,从而形成所述存储器单元(110,1810)的所述三节点存取装置(230,330,998-1,998-2,998-3,998-n)而无需体接触。16.根据权利要求11至12中任一权利要求所述的方法,其进一步包括将所述竖直定向的存取线(103,203,540,640,740,840,940,1640,1740)形成为具有水平宽度(w)(1679),所述水平宽度大于所述沟道材料(1398,1798-1b)的水平长度(l)(1678,1778)且与所述多层第二源极/漏极材料(1798-1c)和所述第一源极/漏极材料(1071-1,1171-1,1271-1,1371-1,1471-1,1571-1,1671-1)两者水平地重叠。17.根据权利要求11至12中任一权利要求所述的方法,其进一步包括将所述竖直定向的存取线(103,203,540,640,740,840,940,1640,1740)形成为具有水平宽度(w)(1679),所述水平宽度小于所述沟道材料(1398,1798-1b)的水平长度(l)(1678,1778)且与所述多层第二源极/漏极材料(1798-1c)和所述第一源极/漏极材料(1071-1,1171-1,1271-1,1371-1,1471-1,1571-1,1671-1)两者水平地部分重叠。18.一种存储器装置,其包括:竖直堆叠的存储器单元(110,1810)的阵列(101),竖直堆叠的存储器单元(110,1810)的所述阵列(101)包括:水平定向的三节点存取装置(230,330,998),其具有通过沟道区(225,325,938-1b,1798-1b)分隔开的多层第一源极/漏极区(221,321,998-1a,1798-1a)和多层第二源极/漏极区(223,323,998-1c,1798-1c),以及与所述沟道区(225,325,938-1b,1798-1b)相对且通过栅极电介质(304,538,638,738,838,938)与其分隔开的栅极,其中所述三节点存取装置

(230,330,998)不具有与所述三节点存取装置(230,330,998)的主体区或所述沟道区(225,325,938-1b,1798-1b)的直接电性体接触;竖直定向的存取线(103,203,540,640,740,840,940,1640,1740),其耦合到所述栅极且通过所述栅极电介质(304,538,638,738,838,938)与所述沟道区(225,325,938-1b,1798-1b)分隔开;水平定向的存储节点(227,327,1744),其电耦合到所述三节点存取装置(230,330,998)的所述多层第一源极/漏极区(221,321,998-1a,1798-1a);以及水平定向的数字线(107,207,307,999,1699,1799),其电耦合到所述三节点存取装置(230,330,998)的所述多层第二源极/漏极区(223,323,998-1c,1798-1c)。19.根据权利要求18所述的存储器装置,其中所述三节点存取装置(230,330,998)具有三个节点,包括所述多层第一源极/漏极区(221,321,998-1a,1798-1a)(1)、所述多层第二源极/漏极区(223,323,998-1c,1798-1c)(2)以及与所述沟道区(225,325,938-1b,1798-1b)相对的所述栅极(3),且不具有所述直接电性体接触。20.根据权利要求18至19中任一权利要求所述的存储器装置,其中所述沟道区(225,325,938-1b,1798-1b)包括二维2d材料,其包括过渡金属二硫属化物中的一或多种。21.根据权利要求18至19中任一权利要求所述的存储器装置,其中所述沟道区(225,325,938-1b,1798-1b)包括具有与所述栅极电介质(304,538,638,738,838,938)接触的富含铟的氧化铟镓锌igzo沟道材料(1398,1798-1b)的第一层和作为反馈沟道钝化材料的氧化镓(gao

x

)泄漏抑制层。22.根据权利要求18至19中任一权利要求所述的存储器装置,其中所述水平定向的存储节点(227,327,1744)与所述三节点存取装置(230,330,998)的所述第一源极/漏极区(221,321,998-1a,1798-1a)在与所述第一源极/漏极区(221,321,998-1a,1798-1a)齐平的相同平面上直接电性接触。23.根据权利要求18至19中任一权利要求所述的存储器装置,其中所述水平定向的数字线(107,207,307,999,1699,1799)与所述三节点存取装置(230,330,998)的所述第二源极/漏极区(223,323,998-1c,1798-1c)在与所述第二源极/漏极区(223,323,998-1c,1798-1c)齐平的相同平面上直接电性接触。

技术总结

本申请涉及竖直三维3D存储器的三节点存取装置中的源极/漏极集成。实例方法包含用于形成竖直堆叠的存储器单元的阵列的方法,所述阵列具有水平定向的存取装置和竖直定向的存取线。所述方法包含以重复迭代沉积介电材料和牺牲材料的交替层以形成竖直堆叠。使用蚀刻过程来形成第一竖直开口,从而暴露所述竖直堆叠中邻近所述牺牲材料的第一区的竖直侧壁。所述第一区经选择性蚀刻以形成去除所述牺牲材料且与所述第一竖直开口相隔第一水平距离的第一水平开口。在所述第一水平开口中沉积多层第一源极/漏极材料、沟道材料和第二源极/漏极材料以形成所述竖直堆叠的存储器单元的阵列当中的存储器单元的三节点存取装置。中的存储器单元的三节点存取装置。中的存储器单元的三节点存取装置。

技术研发人员:S

受保护的技术使用者:美光科技公司

技术研发日:2021.06.29

技术公布日:2022/2/18

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。