1.本公开总体上涉及存储器装置,并且更具体地涉及用于半导体装置的沟道和体区域形成。

背景技术:

2.存储器经常在电子系统(如计算机、手机和手持式装置等)中实施。存在许多不同类型的存储器,包含易失性存储器和非易失性存储器。易失性存储器可能需要电力来维持其数据并且可以包含随机存取存储器(ram)、动态随机存取存储器(dram)、静态随机存取存储器(sram)和同步动态随机存取存储器(sdram)。非易失性存储器可以在未通电时通过保留所存储的数据来提供持久性数据,并且可以包含nand闪存、nor闪存、氮化物只读存储器(nrom)、相变存储器(例如,相变随机存取存储器)、电阻式存储器(例如,电阻式随机存取存储器)、交叉点存储器、铁电随机存取存储器(feram)等。

3.随着设计规则缩小,较少的半导体空间可用于制造包含dram阵列的存储器。用于dram的相应存储器胞元可以包含具有由沟道和体区域分开的第一源极/漏极区域和第二源极/漏极区域的存取装置,例如晶体管。栅极可以与沟道区域相对并且通过栅极电介质与所述沟道区域分开。如字线等存取线电连接到dram胞元的栅极。dram胞元可以包含通过存取装置耦接到数位线的存储节点,如电容器胞元。存取装置可以被耦接到存取晶体管的存取线激活(例如,以选择胞元)。电容器可以存储与相应胞元的数据值 (例如,逻辑“1”或“0”)相对应的电荷。

技术实现要素:

4.一方面,本公开提供了一种方法,其包括:在重复迭代中竖直地形成第一介电材料、半导体材料和第二介电材料的层以形成竖直堆叠;使用蚀刻剂工艺形成竖直开口以暴露所述竖直堆叠中的竖直侧壁;在所述竖直堆叠中的所述竖直侧壁上沉积晶种材料;以及在温度和时间参数下加工所述竖直堆叠,使得所述半导体材料的所述侧壁上的所述晶种材料向所述半导体材料前进第一距离,以将所述第一距离的所述半导体材料的一部分转变为晶体结构。

5.另一方面,本公开进一步提供了一种方法,其包括:在重复迭代中竖直地沉积氧化物材料、硅材料和氮化物材料的层以形成竖直堆叠;使用蚀刻剂工艺形成竖直开口以暴露所述竖直堆叠中的竖直侧壁;选择性地沉积金属晶种材料,以在所述竖直堆叠的所述竖直开口中的所述硅材料的竖直侧壁上形成金属硅化物;以及在温度和时间参数下加工所述竖直堆叠,使得所述金属硅化物水平地前进穿过由所述氧化物材料和所述氮化物材料界定的所述硅材料,并且沿距所述竖直开口第一距离的长度将所述硅材料的一部分从非晶硅结构转变为单晶硅结构。

6.在仍另一方面,本公开进一步提供了一种方法,其包括:在重复迭代中竖直地沉积氧化物材料、非晶硅材料和氮化物材料的层以形成竖直堆叠;使用蚀刻剂工艺形成竖直开

口以暴露所述竖直堆叠中的竖直侧壁;选择性地在所述非晶硅的竖直侧壁上沉积金属晶种材料,以使用原子层沉积(ald)工艺形成金属硅化物;以及在温度和时间参数下加工所述竖直堆叠,以使所述金属硅化物水平地前进穿过所述非晶硅距所述竖直开口第一距离,将所述非晶硅再结晶为单晶硅结构,以在所述竖直堆叠中限定第一区域。

7.在又另一方面,本公开进一步提供了一种存储器胞元阵列,其包括:彼此堆叠的多个存取晶体管,所述存取晶体管中的每个存取晶体管包含水平地布置的第一源极/漏极区域、第二源极/漏极区域和在其之间的沟道区域以及体区域,其中所述沟道区域和所述体区域各自由单晶半导体材料形成;至少一条存取线,所述至少一条存取线竖直地伸长并且在栅极电介质介入下耦接到所述多个存取晶体管的所述沟道区域中的每个沟道区域;彼此堆叠的多个存储电容器,所述多个存储电容器中的每个存储电容器水平地放置并且耦接到所述多个存取晶体管的所述第二源极/漏极区域中的对应一个第二源极/漏极区域;多条数位线,所述多条数位线中的每条数位线耦接到所述多个存取晶体管的所述第一源极/漏极区域中的对应一个第一源极/漏极区域;以及体触点,所述体触点竖直地伸长并且耦接到所述多个存取晶体管的所述体区域中的每个体区域。

附图说明

8.图1是根据本公开的许多实施例的竖直三维(3d)存储器的示意图。

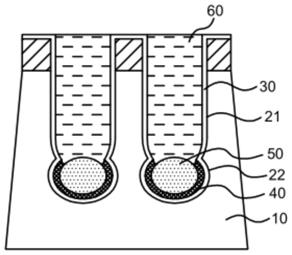

9.图2是展示根据本公开的许多实施例的半导体装置的三节点存取装置的沟道和体区域的透视图。

10.图3是展示根据本公开的许多实施例的半导体装置的三节点存取装置的沟道和体区域的透视图。

11.图4a-4f是根据本公开的许多实施例的在半导体制造工艺的多个阶段处用于形成竖直堆叠的存储器胞元阵列以形成用于半导体装置的沟道和体区域的横截面视图。

12.图5a-5b展示了根据本公开的许多实施例的在半导体制造工艺的另一个阶段处用于形成具有用于半导体装置和竖直定向的存取线的沟道和体区域的竖直堆叠的存储器胞元阵列的示例方法。

13.图6a到6e展示了根据本公开的许多实施例的在半导体制造工艺的另一个阶段处用于形成具有用于半导体装置的沟道和体区域的竖直堆叠的存储器胞元阵列的示例方法。

14.图7a到7e展示了根据本公开的许多实施例的在半导体制造工艺的另一个阶段处用于形成具有用于半导体装置的沟道和体区域的竖直堆叠的存储器胞元阵列的示例方法。

15.图8a到8e展示了根据本公开的许多实施例的在半导体制造工艺的另一个阶段处用于形成具有用于半导体装置的沟道和体区域的竖直堆叠的存储器胞元阵列的示例方法。

16.图9是根据本公开的许多实施例的呈包含存储器装置的计算系统的形式的设备的框图。

具体实施方式

17.本公开的实施例描述了用于半导体装置的沟道和体区域形成。通过竖直堆叠的存储器胞元阵列中的水平存取装置形成沟道和体区域。水平存取装置与竖直定向的存取线整合在一起并与水平定向的数位线整合在一起。由于沟道中的非晶硅材料的晶粒大小增加并

且晶界密度减小,因此沟道可以提供改进的电子迁移率。减小的晶界密度还可以减少电子空穴对发生并且减小截止电流(ioff)的数值。进一步地,金属诱导侧向结晶(milc) 距离可以是使得仅覆盖于沟道区域。与本文没有公开的其它工艺相比,这可以减少退火工艺时间。

18.本文中的附图遵循编号惯例,其中一或多个第一数字与图的附图编号相对应,并且剩余数字标识图中的元件或组件。可以通过使用类似的数字来标识不同附图之间类似的元件或组件。例如,附图标记104可以引用图1中的元件“04”,并且类似的元件可以引用为图2中的204。一个图中的多个相似元件可以用附图标记后跟连字符和另一数字或字母来引用。例如,302-1可以引用图3中的元件302-1,而302-2可以引用可能与元件302-1类似的元件302-2。通常可以在没有连字符和额外的数字或字母的情况下引用这种类似元件。例如,元件302-1和302-2或其它类似元件总体上可以引用为302。

19.图1是根据本公开的许多实施例的设备的框图。图1展示了示出根据本公开的实施例的三维(3d)半导体存储器装置的胞元阵列的电路图。图1展示了可以具有多个子胞元阵列101-1、101-2、

……

、101-n的胞元阵列。子胞元阵列101-1、101-2、

……

、101-n 可以沿第二方向(d2)105布置。子胞元阵列中的每个子胞元阵列(例如,子胞元阵列101-2) 可以包含多条存取线103-1、103-2、

……

、103-q(其也可以被称为字线)。而且,子胞元阵列中的每个子胞元阵列(例如,子胞元阵列101-2)可以包含多条数位线107-1、 107-2、

……

、107-p(其也可以被称为位线、数据线或读出线)。在图1中,展示了在第一方向(d1)109上延伸的数位线107-1、107-2、

……

、107-p,并且展示了在第三方向(d3) 111上延伸的存取线103-1、103-2、

……

、103-q。根据实施例,第一方向(d1)109和第二方向(d2)105可以被认为是在水平(“x-y”)面上。第三方向(d3)111可以被认为是在竖直(“z”)面上。因此,根据本文描述的实施例,存取线103-1、103-2、

……

、103-q 在竖直方向(例如,第三方向(d3)111)上延伸。

20.存储器胞元(例如,110)可以包含定位于每条存取线103-1、103-2、

……

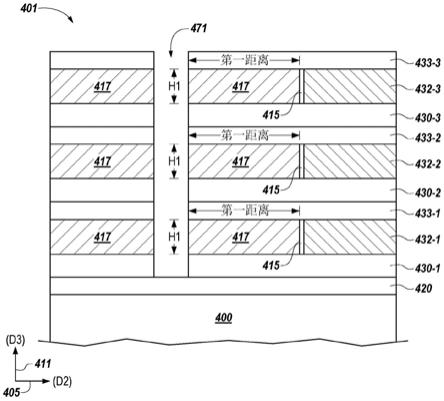

、103-q和每条数位线107-1、107-2、

……

、107-p的交叉点处的存取装置(例如,存取晶体管)和存储节点(例如,存储电容器)。可以使用存取线103-1、103-2、

……

、103-q和数位线107-1、 107-2、

……

、107-p写入或读取存储器胞元。数位线107-1、107-2、

……

、107-p可以沿每个子胞元阵列101-1、101-2、

……

、101-n的平行列使存储器胞元导电互连,并且存取线103-1、103-2、

……

、103-q可以沿每个子胞元阵列101-1、101-2、

……

、101-n 的竖直行使存储器胞元导电互连。一个存储器胞元(例如,110)可以定位在一条存取线(例如,103-2)与一条数位线(例如,107-2)之间。每个存储器胞元可以通过存取线103-1、 103-2、

……

、103-q和数位线107-1、107-2、

……

、107-p的组合来唯一寻址。

21.数位线107-1、107-2、

……

、107-p可以是或包含安置在衬底上并与衬底间隔开的导电图案(例如,金属线)。数位线107-1、107-2、

……

、107-p可以在第一方向(d1)109 上延伸。一个子胞元阵列中的数位线107-1、107-2、

……

、107-p(例如,101-2)可以在竖直方向(例如,第三方向(d3)111)上彼此间隔开。

22.存取线103-1、103-2、

……

、103-q可以是或包含相对于衬底在竖直方向(例如,第三方向(d3)111)上延伸的导电图案(例如,金属线)。一个子胞元阵列中的存取线(例如, 101-2)可以在第一方向(d1)109上彼此间隔开。

23.存储器胞元(例如,存储器胞元110)的栅极可以连接到存取线(例如,103-2),并且存储器胞元110的存取装置(例如,晶体管)的第一导电节点(例如,第一源极/漏极区域) 可

以连接到数位线(例如,107-2)。存储器胞元(例如,存储器胞元110)中的每个存储器胞元可以连接到存储节点(例如,电容器)。存储器胞元110的存取装置(例如,晶体管) 的第二导电节点(例如,第二源极/漏极区域)可以连接到存储节点(例如,电容器)。虽然第一源极/漏极区域和第二源极/漏极区域的引用在本文中用于表示两个单独且不同的源极/漏极区域,但被称为“第一”和/或“第二”源极/漏极区域的源极/漏极区域并不旨在具有某些独特的含义。源极/漏极区域中的一个源极/漏极区域仅旨在连接到数位线(例如,107-2),并且另一个源极/漏极区域可以连接到存储节点。

24.图2展示了示出根据本公开的一些实施例的作为阵列中的竖直定向的存储器胞元堆叠的三维(3d)半导体存储器装置(例如,图1所示的子胞元阵列101-2的一部分)的透视图。图3展示了示出图2所示的3d半导体存储器装置的单位胞元(例如,图1所示的存储器胞元110)的透视图。

25.如图2所示,衬底200可以在其上形成结合图1所述的多个子胞元阵列中的一个子胞元阵列,例如101-2。例如,衬底200可以是或包含硅衬底、锗衬底或硅锗衬底等。然而,实施例并不限于这些实例。

26.如图2的示例实施例所示,衬底200可以在其上制造在竖直方向(例如,第三方向(d3) 111)上延伸的竖直定向的存储器胞元堆叠,例如图1中的存储器胞元110。根据一些实施例,竖直定向的存储器胞元堆叠可以被制造成使得在多个竖直水平(例如,第一水平 (l1)、第二水平(l2)和第三水平(l3))上形成每个存储器胞元,例如图1中的存储器胞元 110。重复的竖直水平l1、l2和l3可以在竖直方向(例如,图1所示的第三方向(d3)111) 上布置,例如堆叠,并且通过绝缘材料220与衬底200分开。重复的竖直水平l1、l2 和l3中的每个重复的竖直水平可以包含侧向定向的存取装置230(例如,晶体管和存储节点(例如,电容器))的多个分立组件(例如,区域),所述存取装置包含存取线203-1、 203-2、

……

、203-q连接和数位线207-1、207-2、

……

、207-p连接。侧向定向的存取装置230(例如,晶体管)的多个分立组件可以在每个水平内,在多个竖直的重复层迭代中形成,如结合图4a-4f在下文更详细描述的,并且可以在与图1所示的第二方向(d2) 105类似的第二方向(d2)205上水平延伸。

27.侧向定向的存取装置230(例如,晶体管)的多个分立组件可以包含通过沟道和体区域225分开、在第二方向(d2)205上侧向延伸并且在存取装置的体中形成的第一源极/ 漏极区域221和第二源极/漏极区域223。在一些实施例中,沟道区域225可以包含硅、锗、硅锗和/或铟镓锌氧化物(igzo)。在一些实施例中,第一源极/漏极区域221和第二源极/漏极区域223可以包含在存取装置的p型掺杂体中形成的n型掺杂剂区域,以形成 n型导电晶体管。在一些实施例中,第一源极/漏极区域221和第二源极/漏极区域223 可以包含在存取装置的n型掺杂体中形成的p型掺杂剂区域,以形成p型导电晶体管。通过实例而非限制,n型掺杂剂可以包含磷(p)原子,并且p型掺杂剂可以包含在多晶硅半导体材料的相对掺杂的体区域中形成的硼(b)原子。然而,实施例并不限于这些实例。

28.存储节点227(例如,电容器)可以连接到存取装置的一个相应端。如图2所示,存储节点227(例如,电容器)可以连接到存取装置的第二源极/漏极区域223。存储节点可以是或包含能够存储数据的存储器元件。存储节点中的每个存储节点可以是使用电容器、磁性隧道结图案和/或包含相变材料等的可变电阻体之一的存储器元件。然而,实施例并不限于这

些实例。在一些实施例中,与单位胞元(例如,图1中的存储器胞元110) 的每一存取装置相关联的存储节点可以在与图1所示的第二方向(d2)105类似的第二方向(d2)205上类似地延伸。

29.如图2所示,多个水平定向的数位线207-1、207-2、

……

、207-p在与图1中的第一方向(d1)109类似的第一方向(d1)209上延伸。所述多个水平定向的数位线207-1、 207-2、

……

、207-p可以类似于图1所示的数位线107-1、107-2、

……

、107-p。所述多个水平定向的数位线207-1、207-2、

……

、207-p可以沿第三方向(d3)211布置,例如“堆叠”。所述多个水平定向的数位线207-1、207-2、

……

、207-p可以包含导电材料。例如,导电材料可以包含以下中的一或多种:掺杂半导体(例如,掺杂硅、掺杂锗等)、导电金属氮化物(例如,氮化钛、氮化钽等)、金属(例如,钨(w)、钛(ti)、钽(ta)等)和/ 或金属半导体化合物(例如,硅化钨、硅化钴、硅化钛等)。然而,实施例不限于这些实例。

30.在竖直水平(l1)213-1、(l2)213-2和(l3)213-m中的每个竖直水平中,水平定向的存储器胞元(例如,图1中的存储器胞元110)可以在第一方向(d1)209上水平地彼此间隔开。然而,如结合图4a-4e在下文中更详细地描述,可以在每一水平内在不同竖直层内形成侧向定向的存取装置230的在第二方向(d2)205上侧向延伸的多个分立组件(例如,通过沟道和体区域225分开的第一源极/漏极区域221和第二源极/漏极区域223)以及在第一方向(d1)209上侧向延伸的多个水平定向的数位线207-1、207-2、

……

、207-p。例如,在第一方向(d1)209上延伸的所述多个水平定向的数位线207-1、207-2、

……

、207-p 可以被安置在第一源极/漏极区域221的顶表面上并且与所述顶表面电接触,并且与在第二方向(d2)205上侧向延伸的侧向定向的存取装置230(例如,晶体管)正交。在一些实施例中,与形成侧向定向的存取装置的分立组件(例如,通过沟道和体区域225分开的第一源极/漏极区域221和第二源极/漏极区域223)的层相比,在水平内,例如在水平(l1)内,在更加远离衬底200的更高的竖直层中形成在第一方向(d1)209上延伸的所述多个水平定向的数位线207-1、207-2、

……

、207-p。在一些实施例中,在第一方向(d1)209上延伸的所述多个水平定向的数位线207-1、207-2、

……

、207-p可以直接和/或通过包含金属硅化物的另外的触点连接到第一源极/漏极区域221的顶表面。

31.如图2的示例实施例所示,存取线203-1、203-2、

……

、203-q相对于衬底200在竖直方向上(例如,在第三方向(d3)211上)延伸。进一步地,如图2所示,一个子胞元阵列(例如,图1中的子胞元阵列101-2)中的存取线203-1、203-2、

……

、203-q可以在第一方向(d1)209上彼此间隔开。可以提供在第三方向(d3)211上、在一对侧向定向的存取装置230(例如,晶体管)之间相对于衬底200竖直延伸的存取线203-1、203-2、

……

、 203-q,所述存取线在第二方向(d2)205上侧向延伸但在第一方向(d1)209上在水平(例如,第一水平(l1))上彼此相邻。存取线203-1、203-2、

……

、203-q中的每条存取线可以在第三方向(d3)上、在竖直堆叠的多个侧向定向的存取装置230(例如,晶体管)的相应存取装置的侧壁上竖直延伸。

32.例如,并且如图3更详细所示,竖直延伸的存取线中的第一条存取线(例如,203-1) 可以邻近第一水平(l1)213-1中的侧向定向的存取装置230(例如,晶体管)中的第一存取装置的沟道和体区域225的侧壁、邻近第二水平(l2)213-2中的侧向定向的存取装置230 (例如,晶体管)中的第一存取装置的沟道和体区域225的侧壁并且邻近第三水平(l3) 213-m中的侧向定向的存取装置230(例如,晶体管)中的第一存取装置的沟道和体区域 225的侧壁

330(例如,晶体管)的体326的上部。例如,第一源极/漏极区域321可以具有在侧向定向的存取装置330的体326内的底表面324,所述底表面被定位成在第三方向(d3)311 上竖直地高于侧向上水平定向的存取装置330的体326的底表面。如此,侧向上水平定向的晶体管330可以具有低于第一源极/漏极区域321的体部分326并且与体触点(例如,图2所示的250)电接触。进一步地,如图3的示例实施例所示,与图2所示的数位线207-1、 207-2、

……

、207-p和图1所示的数位线107-1、107-2、

……

、107-p类似的数位线(例如,307-1)可以安置在第一源极/漏极区域321的顶表面322上并且与其电耦接。

39.如图3的示例实施例所示,与图2中的存取线203-1、203-2、

……

、203-q和图1 中的存取线103-1、103-2、

……

、103-q类似的存取线(例如,303-1)可以在第三方向(d3) 311上邻近侧向定向的存取装置330(例如,晶体管)的体326的沟道区域325部分的侧壁竖直延伸,所述存取装置沿第二方向(d2)305在第一源极/漏极区域321与第二源极/ 漏极区域323之间水平导电。栅极介电材料304可以插置于存取线303-1(其一部分形成侧向定向的存取装置330(例如,晶体管)的栅极)与沟道区域325之间。栅极介电材料304 可以包含例如高k介电材料、氧化硅材料、氮化硅材料、氮氧化硅材料等或其组合。实施例不限于此。例如,在高k介电材料实例中,栅极介电材料304可以包含以下中的一或多种:氧化铪、氧化硅铪、氧化镧、氧化锆、氧化硅锆、氧化钽、氧化钛、氧化钛锶钡、氧化钛钡、氧化钛锶、氧化锂、氧化铝、氧化钽铅钪、铅锌铌矿等。

40.图4a-4f是根据本公开的许多实施例的在半导体制造工艺的多个阶段处用于形成竖直堆叠的存储器胞元阵列以形成用于半导体装置的沟道和体区域的横截面视图。

41.图4a是根据本公开的许多实施例的在半导体制造工艺的一个阶段处用于形成竖直堆叠的存储器胞元阵列以形成水平定向的存取装置的沟道和体区域的横截面视图。

42.在图4a所示的示例实施例中,所述方法包括在重复迭代中沉积第一介电材料 430-1、430-2、

……

、430-n(统称为第一介电材料430)、半导体材料432-1、432-2、

……

、 432-n(统称为介电材料432)和第二介电材料433-1、433-2、

……

、433-n(统称为介电材料433)的交替层以在半导体衬底400的工作面上形成竖直堆叠401。在一些实施例中,可以使用化学气相沉积(cvd)工艺沉积第一介电材料430、半导体材料432和第二介电材料433。在一个实施例中,第一介电材料430可以被沉积为具有在二十(20)纳米(nm) 到六十(60)nm范围内的厚度,例如,在第三方向(d3)上的竖直高度。在一个实施例中,半导体材料432可以被沉积为具有在二十(20)nm到一百(100)nm范围内的厚度,例如,竖直高度。在一个实施例中,第二介电材料433可以被沉积为具有在十(10)nm到三十(30) nm范围内的厚度,例如,竖直高度。然而,实施例并不限于这些实例。如图4a-4f所示,竖直方向411展示为与图1-3中所示的在第一方向、第二方向和第三方向中的第三方向(d3)类似的第三方向(d3),例如,x-y-z坐标系中的z方向。

43.在一些实施例中,第一介电材料430-1、430-2、

……

、430-n可以是层间电介质(ild)。通过举例而非限制,第一介电材料430-1、430-2、

……

、430-n可以包括氧化物材料,例如sio2。在另一个实例中,第一介电材料430-1、430-2、

……

、430-n可以包括氮化硅(si3n4)材料(本文中也称为“sin”)。在另一个实例中,第一介电材料430-1、430-2、

……

、 430-n可以包括氧-碳化硅(sio

xcy

)材料。在另一个实例中,第一介电材料430-1、430-2、

……

、430-n可以包含氧-氮化硅(sio

x

ny)材料(本文中也称为“sion”)和/或其组合。实施

例并不限于这些实例。

44.在一些实施例中,半导体材料432-1、432-2、

……

、432-n可以包括处于多晶态和/ 或非晶态的硅(si)材料。半导体材料432-1、432-2、

……

、432-n可以是低掺杂的p型(p-) 硅材料。半导体材料432-1、432-2、

……

、432-n可以由作为低浓度的杂质掺杂剂的气相掺杂硼原子(b)形成,以形成低掺杂的p型(p-)硅材料。在一些实施例中,半导体材料 432-1、432-2、

……

、432-n可以通过气相掺杂硼原子(b)原位形成。低掺杂的p型(p-) 硅材料可以是非晶硅材料。然而,实施例并不限于这些实例。

45.在一些实施例中,第二介电材料433-1、433-2、

……

、433-n可以是层间电介质(ild)。通过举例而非限制,第二介电材料433-1、433-2、

……

、433-n可以包括氮化物材料。所述氮化物材料可以是氮化硅(si3n4)材料(本文中也称为“sin”)。在另一个实例中,第二介电材料433-1、433-2、

……

、433-n可以包括氧-碳化硅(sioc)材料。在另一个实例中,第二介电材料433-1、433-2、

……

、433-n可以包含氧-氮化硅(sion)和/或其组合。实施例并不限于这些实例。然而,根据实施例,第二介电材料433-1、433-2、

……

、433-n 被有目的地选择成在材料或组成上不同于第一介电材料430-1、430-2、

……

、430-n,使得可以对第一介电层和第二介电层中的一个介电层执行选择性蚀刻工艺,选择所述选择性蚀刻工艺用于第一介电层和第二介电层中的另一个介电层,例如,可以相对于半导体材料432-1、432-2、

……

、432-n和第一氧化物介电材料430-1、430-2、

……

、430-n 选择性地蚀刻第二sin介电材料433-1、433-2、

……

、433-n。

46.再次,可以根据如化学气相沉积(cvd)等半导体制造工艺在半导体制造设备中沉积交替的第一介电材料430-1、430-2、

……

、430-n层、半导体材料432-1、432-2、

……

、 432-n层和第二介电材料433-1、433-2、

……

、433-n层的重复迭代。然而,实施例并不限于此实例,并且其它合适的半导体制造技术可以用于在重复迭代中沉积第一介电材料、半导体材料和第二介电材料的交替层,以形成竖直堆叠401。

47.所述层可以竖直地出现在重复迭代中。在图4a的实例中,示出了重复迭代的编号为1、2和3的三个层级。例如,所述堆叠可以包含:第一介电材料430-1、半导体材料 432-1、第二介电材料433-1、第三节点材料430-2、第二半导体材料432-2、第四介电材料433-2、第五介电材料430-3、第三半导体材料432-3和第六介电材料433-3。如此,堆叠可以包含:在另外的重复迭代中的第一氧化物材料430-1、第一半导体材料432-1、第一氮化物材料433-1、第二氧化物材料430-2、第二半导体材料432-2、第二氮化物材料433-2、第三氧化物材料430-3、第三半导体材料432-3和第三氮化物材料433-3。然而,实施例并不限于此实例,并且可以包含更多或更少的重复迭代。

48.图4b是根据本公开的许多实施例的在半导体制造工艺的另一阶段处用于形成竖直堆叠的存储器胞元阵列以形成水平定向的存取装置(例如,晶体管)的沟道和体区域的横截面视图。

49.根据实施例,图4b-4f中所述的半导体制造工艺可以发生于如图5a-6e所示的主要在第二方向上延伸的细长柱和存取线路形成已经被执行之后。根据实施例,图4a-4f中的方法可以将半导体材料432(例如,低掺杂(p-)多晶硅材料)转变为单晶结构。

50.如图4b所示,竖直开口471可以穿过竖直堆叠的存储器胞元内的层形成,以暴露竖直堆叠401中的竖直侧壁。可以使用第一蚀刻工艺通过在重复迭代中交替形成开口 471,以

形成邻近半导体材料432(例如,多晶硅(poly-si))的第一区域(例如,图7c中的 742)的开口471。竖直开口471可以穿过氧化物材料430、半导体材料432和氮化物材料 433的重复迭代形成。如此,竖直开口471可以穿过第一氧化物材料430-1、第一半导体材料432-1、第一氮化物材料433-1,、第二氧化物材料430-2、第二半导体材料432-2、第二氮化物材料433-2、第三氧化物材料430-3、第三半导体材料432-3和第三氮化物材料433-3形成。然而,实施例并不限于图4b所示的单一竖直开口471。多个竖直开口可以穿过材料层形成。竖直开口471可以被形成为暴露竖直堆叠401中的竖直侧壁。在一个实例中,衬底400的工作面可以被掩盖并图案化,以形成范围在五十(50)纳米(nm)到五百(500)nm内的宽度以及范围在五百(500)nm到两万(20,000)nm内的深度的竖直开口 471。然而,实施例并不限于此实例。

51.图4c是根据本公开的许多实施例的在半导体制造工艺的另一阶段处用于形成具有竖直定向的存取线的竖直堆叠的存储器胞元阵列以形成水平定向的存取装置的沟道和体区域的横截面视图。

52.如图4c所示,金属(例如,晶种)材料416可以沉积在竖直堆叠401、竖直开口471 的侧壁和竖直开口471的底部之上。在一些实施例中,可以使用原子层沉积(ald)工艺沉积金属材料416。在一个实施例中,金属材料416是镍(ni)金属材料416。在此实例中,镍(ni)金属材料416可以被选择性地沉积,以形成具有硅材料432的ni硅化物(nisi)416。在一个实例中,金属材料416(例如,晶种材料)可以被沉积到范围为大约5-50埃的厚度(t1)。然而,实施例并不限于这些实例。在一些实施例中,金属材料416包括可以与硅(si)材料(例如,多晶硅材料432)形成硅化物的金属。

53.图4d是根据本公开的许多实施例的在半导体制造工艺的另一阶段处用于形成具有竖直定向的存取线的竖直堆叠的存储器胞元阵列以形成水平定向的存取装置的沟道和体区域的横截面视图。

54.在图4d的示例实施例中,根据金属诱导侧向结晶(milc)、固相结晶(spc)工艺,可以在温度、压力和时间参数下加工竖直堆叠401,使得金属材料416水平地在半导体材料432的一部分内前进并将半导体材料432的一部分的晶体结构转变为大晶粒尺寸的多晶材料417,例如单晶半导体材料。作为在高温下退火工艺的结果,随着金属材料416 前进穿过半导体材料432,金属材料416可以从半导体材料432获取硅原子并且变为金属硅化物材料415。在一些实施例中,金属硅化物材料415可以是硅化镍材料、硅化钴材料或硅化银材料。作为在金属硅化物材料415与半导体材料432之间进行化学反应的结果,金属硅化物材料415可以前进穿过半导体材料432。可以通过调节施加到竖直堆叠401和金属硅化物材料415的温度来控制金属硅化物材料415前进穿过半导体材料432 的速度。在一些实施例中,可以在400到600摄氏度(℃)范围内的温度下加工竖直堆叠 401,使得金属硅化物材料415水平地前进穿过半导体材料432(例如,多晶硅),从而将半导体材料432的一部分转变为单晶半导体材料417。

55.在一些实施例中,金属硅化物材料415在半导体材料432的一部分内水平地前进的距离(dist1)是由如厚度(h1)等许多因素决定的,例如,半导体材料432层的竖直高度、金属材料(例如,沉积在竖直堆叠401的竖直开口471中的半导体材料432的竖直侧壁和第一区域上的晶种材料)的厚度以及温度。在一些实施例中,可以通过调节在工艺中施加到竖直堆叠401和金属硅化物材料415的温度以及调节施加所述温度的时间量来控制金属硅化物材料

415在半导体材料432的一部分内水平地前进从而将半导体材料432的一部分转变为单晶半导体材料417的距离(dist1)。

56.在一些实施例中,在低于600摄氏度(℃)的施加温度下,半导体材料432层的在二十(20)nm到一百(100)nm范围内的厚度(h1)(例如,竖直高度)以及沉积到在大约5-50 埃范围内的厚度(t1)的金属材料416(例如,晶种材料)的厚度、时间和工艺参数被控制成使得金属硅化物材料415水平地前进穿过硅材料432在100纳米(nm)到300nm范围内的第一距离(dist1),从而将半导体材料432的一部分转变为单晶硅半导体材料417。在一个实施例中,金属硅化物材料415水平地前进穿过硅材料432至少200纳米(nm)的第一距离(dist1),从而将半导体材料432的一部分转变为大晶粒多晶硅和/或单晶硅结构417。在一些实施例中,根据本文所述的设计规则,可以在低至400摄氏度(℃)的温度下进行工艺。

57.在一些实施例中,在以上所述的工艺参数下,金属硅化物材料415以对角线-水平进展前进穿过硅材料432,从而将半导体材料432的一部分转变为大晶粒多晶硅和/或单晶硅结构417。然而,此类对角线-水平前进由第一介电材料430(例如,作为竖直方向(第三方向(d3)上的底板)界定,并且由第二介电材料433(例如,作为竖直方向上的顶板)界定,使得金属硅化物材料415的前进在远离竖直开口471移动的方向上继续在第二方向 (d2)在半导体材料432内水平地进展距离(dist1)和高度(h1),从而将半导体材料432的一部分转变为大晶粒多晶硅和/或单晶硅结构417。

58.在一些实施例中,金属416(例如,晶种材料)可以被沉积在穿过竖直堆叠400的在第二区域(例如,图7c中的744)中敞开的第二竖直开口(例如,图7c中的751)中,以最终形成存储节点。对以上所述那些使用类似工艺和加工参数控制技术,所得金属硅化物材料415可以在远离第二竖直开口(例如,图7c中的751)移动的方向上水平地进展穿过半导体材料432,所述半导体材料是将包含邻近第二竖直开口和第二区域(例如,744)并且在第二竖直开口和第二区域中形成的存储节点的竖直堆叠401的侧面。在这些实施例中,金属硅化物材料415可以在朝着第一开口471的方向上移动穿过半导体材料432。然而,实施例并不限于这些实例。

59.在一个实施例中,金属硅化物材料415继续在第二方向(d2)上在半导体材料432内沿《100》结晶平面朝向或靠近《100》结晶平面朝向的结晶平面朝向水平地进展距离 (dist1)和高度(h1),从而将半导体材料432的一部分转变为大晶粒多晶硅和/或单晶硅结构417。然而,实施例并不限于此实例。在一些实施例中,金属硅化物材料415从初始金属416(例如,沉积位置上的晶种材料)进展更远的距离可以实现更好的单晶均匀性。

60.根据一些实施例,所得的经转变的硅晶体材料417的一部分是基本上单晶硅结构,使得晶体结构的晶界(gb)大部分为子晶界(sub-gb),并且使得经转变的硅晶体材料417 的一部分具有大约小于(《)一度(1

°

)的晶体取向差异。在一个实施例中,大晶粒多晶硅和/ 或基本上单晶硅晶体材料417的晶界缺陷浓度小于在1

×

10

18

立方厘米(cubiccentimeters)(也称为centimeters cubed(cm3))内的一个缺陷。例如,根据实施例,可以在温度、沉积厚度和时间参数下加工竖直堆叠401,以使金属硅化物材料415水平地前进,从而将多晶硅和/或非晶硅半导体材料432再结晶为大部分具有子晶界(sub-gb)的基本上单晶硅结构417。另外规定,根据本文中所述的实施例,多晶硅半导体材料和/或非晶硅半导体材料432被再结晶为基本上单晶硅结构417,使得单晶硅结构417内的晶界的晶体取向差异小于一度(1

°

)。

再次,在一些实施例中,单晶硅结构417的缺陷密度可以小于在1

×

10

18

立方厘米(cm3)的单晶硅结构417内的一个缺陷。

61.因此,由于大晶粒尺寸和低晶界(gb)密度,用于水平定向的存取装置的沟道和体区域的更佳晶体结构设置有更佳的电子迁移率。例如,可以实现较低的gb陷阱密度,并且出现较少的电子空穴对可能发生,从而根据所述的设计规则和规模得到用于水平定向的存取装置的较低的“截止”电流(“ioff”)。而且,与形成(例如,沉积)半导体材料432 的非晶硅:氢(a-si:h)膜沉积工艺的其它低温化学气相沉积(cvd)相比,可以达到更佳的具有经改进的尾位生长曲线的均匀性。

62.如所指出的,在一些实施例中,使用金属诱导侧向结晶(milc),金属材料415可以将半导体材料432转变为晶体材料417。与将milc应用于多晶硅相比,当应用于非晶硅时,milc可能是更有效的再结晶工艺。当应用于多晶硅时,milc可能不太有效,因为多晶硅中的晶界可能妨碍金属硅化物(例如,金属硅化物材料415)在再结晶过程期间穿过多晶硅移动。由于多晶硅材料中的晶界妨碍金属硅化物穿过多晶硅材料移动,因此milc期间多晶硅材料中的晶体生长速度可能比milc期间非晶硅材料中的晶体生长速度更慢。进一步地,多晶硅比非晶硅更加稳定,因此使多晶硅再结晶所需的能量的量大于使非晶硅再结晶所需的能量的量。

63.在一些实施例中,milc可以在低于450摄氏度的温度下发生。在一些实施例中,使用固相结晶(spc),金属硅化物材料415可以将半导体材料432转变为晶体材料417。可以在温度和时间参数下加工竖直堆叠401,使得当金属硅化物材料415在半导体材料 432内前进时,所述金属硅化物材料根据半导体材料432的一部分中的单独晶体的尺寸增加转变半导体材料432的所述部分的晶体结构。

64.在前进穿过半导体材料432之后,可以加工竖直堆叠401,以形成其它半导体组件,例如存储节点、数位线、竖直存取线等和/或如源极/漏极区域等分立区域。在一些实施例中并且通过举例而非限制,剩余的金属硅化物材料415具有非常低的缺陷浓度和/或杂质。进一步地,随着金属硅化物材料415前进穿过硅材料432第一距离(例如,dist1),可以在单晶硅417与剩余的未转变的和/或再结晶的半导体材料432(例如,非晶硅)之间提供分隔界面,其中界面的单晶侧的晶体大于非晶硅结构432中的晶体,并且使得在结晶之后,来自金属材料416(例如,晶种材料)的非常低的金属杂质保留在半导体材料 432(例如,多晶硅)中。

65.如以下将更详细描述的,可以在第一区域中使用再结晶的单晶硅结构417以在竖直堆叠401中形成水平定向的存取装置。在一些实施例中,现在距竖直开口471第一距离 (d1)的剩余的金属硅化物材料415可以用作蚀刻停止,同时选择性地从竖直堆叠401的第二区域中去除半导体材料432以形成存储节点。例如,可以使用ald工艺在第二区域中的选择性地去除的半导体材料432中形成水平电容器胞元。

66.如所指出的,加工竖直堆叠401,使得金属硅化物材料415水平地前进穿过硅材料第一距离(dist1)并且在剩余半导体材料432的经转变的单晶硅417与晶体结构之间提供分隔界面。界面的单晶侧417上的晶体大于剩余半导体材料432结构中的晶体。由于与用于剩余非晶硅和/或多晶硅半导体材料432的非金属硅化物形成工艺(例如, milc/spc工艺)相比,经转变的材料417中的晶体较大,经转变的晶体材料417可以提供经改进的沟道和体区域(例如,图3中的325),相比于使用所沉积的半导体材料432 形成的沟道和体区域,具有更

佳电子迁移率和更低的“截止电流”(“ioff”)泄露。再次,在一些实施例中,由经转变的晶体材料417形成的沟道和体区域(图3中的325)的厚度 (h1)(例如,竖直高度)可以在大约二十(20)nm到一百(100)nm的范围内。在一些实施例中,在远离竖直开口471的水平方向上的界面一侧上的剩余的、未经转变的半导体材料432可以被牺牲地去除以形成水平开口,以便形成具有竖直定向的存取线的竖直堆叠的存储器胞元的水平定向的存储节点。例如,在一些实施例中,任何剩余金属硅化物材料415可以被用作蚀刻停止以牺牲去除半导体材料432和/或用作在竖直堆叠401的第二区域中形成的作为存储节点的电容器的第一电极的欧姆触点。

67.图4e是根据本公开的许多实施例的在半导体制造工艺的另一阶段处用于形成竖直堆叠的存储器胞元阵列以形成水平定向的存取装置的沟道和体区域的横截面视图。

68.如图4e的实例所示,如从图4d中可以看出,没有在半导体材料432内前进的金属材料416可以保留在竖直开口471的第一介电材料430和第二介电材料433的竖直侧壁上以及竖直堆叠401的竖直开口471的底表面上。因此,在一个实施例中,如图4e所示,各向同性蚀刻工艺清洁可以在竖直堆叠401上的竖直开口471中执行,例如在竖直开口471的侧壁和底部上执行,以从那些表面上去除残留的、剩余的金属材料416。从竖直堆叠401的竖直开口471中的此类表面(例如,竖直开口471的侧壁和底部)中去除金属材料416可以保留竖直开口471的原始纵横比(a/r)、竖直高宽比,以便在本文描述的后续半导体制造过程中在其中进行后续材料沉积。在一些实施例中,a/r可以在十(10) 到四十(40)范围内。在一些实施例中,a/r可以在40nm到150nm范围内。

69.图4f是根据本公开的许多实施例的在半导体制造工艺的另一阶段处用于形成竖直堆叠的存储器胞元阵列以形成水平定向的存取装置的沟道和体区域的横截面视图。

70.如图4f的示例实施例所示,可以执行后续半导体制造工艺,以选择性地去除第二介电材料433的牺牲部分,使用气相掺杂在经转变的、晶体材料417的顶表面中沉积第一源极/漏极区域,沉积与第一源极/漏极区域电接触的导电数位线材料,提供隔离势垒并且在竖直开口中沉积体触点495材料,以形成如图3所示的装置结构。

71.在图4f的实例中,数位线477可以是如图2所示的在第一方向(d1)上延伸、行进到图4f中的图纸平面中并从所述图纸平面行进出来的水平定向的数位线477、207。在标题为“半导体装置的数位线和体触点(digit line and body contact for semiconductordevices)”、具有至少一位共同发明人并且于__________提交的共同未决的美国专利申请第_____________号(代理人案号:1013.0460001)中描述了在经转变的晶体材料417、与第一源极/漏极区域电接触的导电数位线材料、隔离势垒和体触点495材料的顶表面中形成第一源极/漏极区域的一个实例。在标题为“用于竖直三维(3d)存储器的水平存取装置的底部接触(underbody contact to horizontal access devices for verticalthree-dimensional(3d)memory)”、具有至少一位共同发明人并且于__________提交的共同未决的美国专利申请第_____________号(代理人案号:1013.0490001)中提供了另一个实例。在标题为“用于水平定向的存取装置的数位线形成(digit line formation forhorizontally oriented access devices)”、具有至少一位共同发明人并且于__________提交的共同未决的美国专利申请第______________号(代理人案号:1013.0510001)中提供了另一个实例。所有这些专利均通过引用全部并入本文中。

72.图5a展示了根据本公开的许多实施例的在半导体制造工艺的另一个阶段处用于形成具有半导体装置和竖直定向的存取线路的沟道和体区域的竖直堆叠的存储器胞元阵列的示例方法。图5a展示了根据一或多个实施例的在半导体制造工艺中,在特定时间点的半导体结构的俯视图。在图5a的实例所示的示例实施例中,所述方法包括使用蚀刻工艺来形成穿过竖直堆叠到达衬底的具有第一水平方向(d1)509和第二水平方向(d2) 505的多个第一竖直开口500。在一个实例中,如图5a所示,所述多个第一竖直开口 500主要在第二水平方向(d2)505上延伸并且可以在竖直堆叠中形成具有侧壁514的细长竖直柱列513。所述多个第一竖直开口500可以通过以下形成:使用光刻技术图案化光刻掩模535,例如以在蚀刻所述多个第一竖直开口500之前在竖直堆叠上形成硬掩模 (hm)。

73.图5b是沿图5a中的切割线a-a'截取的横截面视图,其示出了在半导体制造工艺中在特定时间的半导体结构的另一视图。图5b所示的横截面视图示出了半导体衬底500 上的第一介电材料530-1、530-2、

……

、530-n、半导体材料532-1、532-2、

……

、532-n 和第二介电材料533-1、533-2、

……

、533-n的交替层的重复迭代,以形成竖直堆叠,例如如图4a所示的401。图5b展示了可以在多个第一竖直开口500中、在栅极介电材料538上形成导电材料540-1、540-2、

……

、540-4。通过举例而非限制,栅极介电材料 538可以使用化学气相沉积(cvd)、等离子体增强cvd(pecvd)、原子层沉积(ald)或其它合适的沉积工艺保形地沉积在所述多个第一竖直开口500中,以覆盖多个第一竖直开口的底表面和竖直侧壁。栅极介电材料538可以沉积为适合于特定设计规则的特定厚度(t1),例如,大约10纳米(nm)的栅极电介质厚度。然而,实施例并不限于此实例。通过举例而非限制,栅极介电材料538可以包括图3中所描述的二氧化硅(sio2)材料、氧化铝(al2o3)材料、高介电常数(k)(例如,高k)、介电材料和/或其组合。

74.进一步地,如图5b所示,导电材料540-1、540-2、

……

、540-4可以保形地沉积在所述多个第一竖直开口500中、在栅极介电材料538的表面上。通过举例而非限制,导电材料540-1、540-2、

……

、540-4可以使用化学气相沉积工艺(cvd)、等离子体增强 cvd(pecvd)、原子层沉积(ald)或其它合适的沉积工艺保形地沉积在所述多个第一竖直开口500中、在栅极介电材料538的表面上,以在栅极介电材料538之上覆盖多个第一竖直开口的底表面和竖直侧壁。导电材料540-1、540-2、

……

、540-4可以保形地沉积为特定厚度(t2),以形成如图1及以下等等所示的存取线103-1、103-2、

……

、103-q(也可被称为字线)所示和如适合于特定设计规则的竖直定向的存取线。例如,导电材料 540-1、540-2、

……

、540-4可以保形地沉积为大约20纳米(nm)的厚度。然而,实施例并不限于此实例。通过举例而非限制,导电材料540-1、540-2、

……

、540-4可以包括如钨(w)等金属、金属复合物、氮化钛(tin)、掺杂非晶硅和/或图3中也描述的其一些其它组合。

75.如图5b所示,导电材料540-1、540-2、

……

、540-4可以向后凹入,以在图5b的横截面视图中保持仅沿着现在示出为542-1、542-2和542-3的细长竖直柱列的竖直侧壁。由导电材料540-1、540-2、

……

、540-4形成的多个单独的竖直存取线可以通过使用合适的选择性的各向异性蚀刻工艺向后凹入,以从第一竖直开口(例如,图5a中的500) 的底表面中去除导电材料540-1、540-2、

……

、540-4,从而暴露底表面上的栅极介电材料538以形成单独的竖直存取线540-1、540-2、

……

、540-4。如图5b所示,介电材料 539(如氧化物或其它合适的旋涂介质(sod))然后可以使用如cvd等工艺沉积在第一竖直开口500中,以填充第一竖直开

口500。电介质可以使用化学机械抛光(cmp)或其它合适的半导体制造技术被平面化为竖直半导体堆叠的硬掩模535的顶表面。后续光刻材料536(例如,硬掩模)可以使用cvd沉积,并且使用cmp平面化,以覆盖并封闭在单独的竖直存取线540-1、540-2、

……

、540-4之上的第一竖直开口500。类似的半导体工艺技术可以在本文描述的半导体制造工艺的其它点处使用。

76.图6a展示了根据本公开的许多实施例的在半导体制造工艺的另一个阶段处用于形成具有半导体装置的沟道和体区域的竖直堆叠的存储器胞元阵列的示例方法。图6a展示了根据一或多个实施例的在半导体制造工艺中,在特定时间点的俯视图。在图6a的示例实施例中,所述方法包括使用光刻工艺图案化图5b中的光刻硬掩模636、536。图 6a中的方法进一步展示了使用选择性的各向同性蚀刻工艺去除暴露的导电材料640-1、640-2、

……

、640-n、640-(n 1)、

……

、640-(z-1)和640-z的部分,以分离并独立地形成多个单独的竖直存取线640-1、640-2、

……

、640-n、640-(n 1)、

……

、640-(z-1)和 640-z,例如图1及下文等等中的存取线103-1、103-2、

……

、103-q。因此,所述多个单独的竖直存取线640-1、640-2、

……

、640-n、640-(n 1)、

……

、640-(z-1)和640-z 在图5b的横截面视图中沿细长的竖直柱列的侧壁(例如,沿细长的竖直柱列542-1、542-2 和542-3的侧壁)示出。

77.如图6a的实例所示,暴露的导电材料640-1、640-2、

……

640-n、640-(n 1)、

……

、 640-(z-1)和640-z可以使用合适的选择性的各向同性蚀刻工艺向后去除到第一竖直开口 (例如,图5a中的500)中的栅极介电材料638。如图6a所示,如氧化物或其它合适的旋涂电介质(sod)等后续介电材料641可以被沉积,以填充使用如cvd或其它合适技术等工艺去除的暴露的导电材料640-1、640-2、

……

640-n、640-(n 1)、

……

、640-(z-1) 和640-z的剩余开口。介电材料641可以使用如cmp等工艺或其它合适的技术被平面化为竖直半导体堆叠(例如,图4a中所示的401)的先前硬掩模635的顶表面。在一些实施例中,后续光刻材料637(例如,硬掩模)可以使用cvd沉积,并且使用cmp平面化,以覆盖并封闭在图4a中的竖直半导体堆叠401的工作表面之上的多个单独的竖直存取线640-1、640-2、

……

、640-n、640-(n 1)、

……

、640-(z-1)和640-z,从而沿细长的竖直柱列的侧壁保护多个单独的竖直存取线640-1、640-2、

……

、640-n、640-(n 1)、

……

、 640-(z-1)和640-z。然而,实施例并不限于这些工艺实例。

78.图6b展示了沿图6a中的切割线a-a'截取的横截面视图,其示出了在本公开的实施例的一个示例半导体制造工艺中,在此特定点处的半导体结构的另一视图。图6b所示的横截面视图远离多个单独的竖直存取线640-1、640-2、

……

、640-n、640-(n 1)、

……

、 640-(z-1),并且示出了半导体衬底600上的第一介电材料630-1、630-2、

……

、630-n、半导体材料632-1、632-2、

……

、632-n和第二介电材料633-1、633-2、

……

、633-n 的交替层的重复迭代以形成竖直堆叠,例如如图4a所示的401。如图6b所示,竖直方向611展示为与图1-3中所示的在第一方向、第二方向和第三方向中的第三方向(d3)111 类似的第三方向(d3),例如,x-y-z坐标系中的z方向。在左边和右边延伸的图纸平面是在第一方向(d1)609上。在图6b的示例实施例中,介电材料641示出为填充残留栅极介电材料638沉积上的竖直开口。以上所述的硬掩模637覆盖所展示的结构。

79.图6c展示了沿图6a中的切割线b-b'截取的横截面视图,其示出了在本公开的实施例的一个示例半导体制造工艺中,在此特定点处的半导体结构的另一视图。图6c所示的横

截面视图展示为沿第一介电材料630-1、630-2、

……

、630-n、半导体材料632-1、 632-2、

……

、632-n和第二介电材料633-1、633-2、

……

、633-n的交替层的重复迭代的轴线在第二方向(d2)605上延伸,沿所述交替层并且在所述交替层中,水平定向的存取装置和水平定向的存储节点(例如,电容器胞元)可以在半导体材料632-1、632-2、

……

、 632-n的层内形成。在图6c中,邻近的相对竖直存取线640-3由表示从图纸的平面和朝向设定的位置的虚线展示。

80.图6d展示了沿图6a中的切割线c-c'截取的横截面视图,其示出了在本公开的实施例的一个示例半导体制造工艺中,在此特定点处的半导体结构的另一视图。图6d所示的横截面视图展示为沿第一介电材料630-1、630-2、

……

、630-n、半导体材料632-1、 632-2、

……

、632-n和第二介电材料633-1、633-2、

……

、633-n的交替层的重复迭代的轴线在一定区域的外部在第二方向(d2)605上延伸,在所述区域中,水平定向的存取装置和水平定向的存储节点(例如,电容器胞元)将在半导体材料632-1、632-2、

……

、 632-n的层内形成。在图6c中,介电材料641示出为填充水平定向的存取装置与水平定向的存储节点之间的空间,所述水平定向的存取装置与水平定向的存储节点可以沿第一方向(d1)611间隔,延伸到竖直定向的存储器胞元的三维阵列的图纸平面中并从其中延伸出去。图纸的左端处示出为第一介电材料630-1、630-2、

……

、630-n、半导体材料632-1、632-2、

……

、632-n和第二介电材料633-1、633-2、

……

、633-n的交替层的重复迭代,在所述位置处,水平定向的数位线(例如,图1及以下等等所示的数位线 107-1、107-2、

……

、107-p)可以被整合以形成以下详细描述的与第二源极/漏极区域或数位线导电接触材料的电接触。

81.图6e展示了沿图6a中的切割线d-d'截取的横截面视图,其示出了在本公开的实施例的一个示例半导体制造工艺中,在此特定点处的半导体结构的另一视图。在图纸的平面中从右向左展示了图6e所示的横截面视图,所述平面在第一方向(d1)609上沿第一介电材料630-1、630-2、

……

、630-n、半导体材料632-1、632-2、

……

、632-n和第二介电材料633-1、633-2、

……

、633-n的交替层的重复迭代的轴线延伸,跨所述多个单独的竖直存取线640-1、640-2、

……

、640-n、640-(n 1)、

……

、640-(z-1)相交,并且使半导体材料632-1、632-2、

……

、632-n的区域相交,在所述区域中可以形成通过栅极介电材料638与所述多个单独的竖直存取线640-1、640-2、

……

、640-n、 640-(n 1)、

……

、640-(z-1)分开的沟道和体区域。在图6e中,第一介电填充材料639 示出为使相邻的水平定向的存取装置与水平定向的存储节点之间的空间分开,如下文更详细描述的,所述水平定向的存取装置与水平定向的存储节点可以延伸到图纸平面中并从其中延伸出去,并且可以沿第一方向(d1)609隔开并且在三维(3d)存储器中竖直堆叠于在第三方向(d3)611方向上延伸的阵列中。

82.图7a展示了根据本公开的许多实施例的在半导体制造工艺的另一个阶段处用于形成具有半导体装置的沟道和体区域的竖直堆叠的存储器胞元阵列的示例方法。图7a展示了根据一或多个实施例的在半导体制造工艺中,在特定时间点的半导体结构的俯视图。在图7a的示例实施例中,所述方法包括使用光刻工艺图案化光刻掩模735、736和 /或737,例如,图6a-6e中的635、636和/或637。图7a中的方法进一步展示了使用一或多种蚀刻工艺在存储节点区域750(和图7a和7c中的744)中形成穿过竖直堆叠并且主要在第一水平方向(d1)709上延伸的竖直开口751-1、751-n、751-(n 1)和751-z(分别或统称为竖直开口751)。所述一或多种蚀刻工艺形成竖直开口751以在图7b-7e所示的邻近半导体材料的第二区域

的竖直堆叠中暴露第一介电材料730-1、730-2、

……

、 730-n、半导体材料732-1、732-2、

……

、732-n和第二介电材料733-1、733-2、

……

、 733-n的交替层的重复迭代中的第三侧壁。其它编号的组件可以类似于结合图6a-6e所示和讨论的那些组件。

83.在一些实施例中,在选择性地去除半导体材料的存取装置区域(例如,晶体管区域) 之后执行此工艺,在所述存取装置区域中形成水平定向的存取装置的第一源极/漏极区域、沟道区域和第二源极/漏极区域。在其它实施例中,在选择性地去除半导体材料的存取装置区域之后执行此工艺,在所述存取装置区域中形成水平定向的存取装置的第一源极/漏极区域、沟道区域和第二源极/漏极区域。

84.根据图7b-7e所示的示例实施例,所述方法包括在竖直堆叠(图4a中的401)中形成第二竖直开口751以及选择性地蚀刻半导体材料732-1、732-2、

……

、732-n的第二区域744,以在与竖直堆叠(图4a中的401)中的竖直开口751相距第二水平距离处向后形成第二水平开口734(d2开口)。根据实施例,选择性地蚀刻半导体材料732-1、 732-2、

……

、732-n的第二区域744包括使用原子层蚀刻(ale)工艺。如结合图7c更详细地解释的,可以在距离竖直开口的第二水平开口734的远端处的半导体材料732-1、 732-2、

……

、732-n中形成第二源极/漏极区域778。

85.图7b展示了沿图7a中的切割线a-a'截取的横截面视图,其示出了在本公开的实施例的一个示例半导体制造工艺中,在此特定点处的半导体结构的另一视图。图7b所示的横截面视图远离多个单独的竖直存取线740-1、740-2、

……

、740-n、740-(n 1)、

……

、 740-(z-1),并且示出了半导体衬底700上的通过开口751分开的介电材料730-1、730-2、

……

、730-(n 1)、半导体材料732-1、732-2、

……

、732-n和第二介电材料733-1、 733-2、

……

、733-n的交替层的重复迭代以形成竖直堆叠。如图7b所示,竖直方向711 展示为与图1-3中所示的在第一方向、第二方向和第三方向中的第三方向(d3)111类似的第三方向(d3),例如,x-y-z坐标系中的z方向。在左边和右边延伸的图纸平面是在第一方向(d1)709上。在图7b的示例实施例中,竖直堆叠内的材料是在第二方向(d2)上延伸到图纸的平面中并从其中延伸出去并且沿三维(3d)存储器的竖直堆叠的存储器胞元阵列的水平存取装置和水平存储节点的朝向的轴线延伸的介电材料730-1、 730-2、

……

、730-(n 1)、半导体材料732-1、732-2、

……

、732-n和第二介电材料733-1、 733-2、

……

、733-n。

86.图7c展示了沿图7a中的切割线b-b'截取的横截面视图,其示出了在本公开的实施例的一个示例半导体制造工艺中,在此特定点处的半导体结构的另一视图。图7c所示的横截面视图展示为沿第一介电材料730-1、730-2、

……

、730-n、半导体材料732-1、 732-2、

……

、732-n和第二介电材料733-1、733-2、

……

、733-n的交替层的重复迭代的轴线,沿图纸平面在第二方向(d2)705上在左边和右边延伸,并且在所述交替层中,水平定向的存取装置和水平定向的存储节点(例如,电容器胞元)可以在半导体材料 732-1、732-2、

……

、732-n层内形成。在图7c的示例实施例中,开口756在水平定向的存储节点(例如,电容器胞元)可以在这种半导体制造工艺中稍后形成的区域展示。

87.在图7c中的示例实施例中,竖直开口751和水平开口734示出为通过结合图7a 所述的掩模、图案化和蚀刻工艺形成。如图7c所示,第二区域744中的半导体材料732-1、 732-2、

……

、732-n已经被选择性地去除,以形成水平开口734。在一个实例中,使用原子层蚀刻(ale)工艺选择性地蚀刻半导体材料732-1、732-2、

……

、732-n,并且从竖直开口751中向后

去除第二距离(d2开口)。如图8a-8e所示,可以在第二水平开口734 中相对于图4a-4f所示的制造工艺稍后或首先形成水平定向的存储节点(例如,电容器胞元)。

88.根据一个示例实施例,如图7c所示,可以通过使用于n型晶体管的如磷(p)等高能气相掺杂剂流动到第二水平开口734中来形成第二源极/漏极区域778,以在第二水平开口734的远端处将掺杂剂从竖直开口751注入半导体材料732-1、732-2、

……

、732-n 中。在一个实例中,可以使用气相掺杂实现高度各向同性(例如,非定向掺杂),以在区域742中形成水平定向的存取装置的第二源极/漏极区域778。在另一个实例中,可以与高能等离子体辅助一起使用具有如磷等掺杂气体的热退火。然而,实施例并不限于此,并且可以利用其它合适的半导体制造技术。

89.如图8c进一步所示,用于水平定向的存储节点的第一电极(例如,861)被耦接到水平存取装置的第二源极/漏极区域778。如图8c稍后所示,示出了在第二水平开口734 中形成的此类水平定向的存储节点,所述第二水平开口在图纸平面中在左边和右边在第二方向(d2)上延伸与竖直开口751相距第二距离(d2开口),所述竖直开口在竖直堆叠(例如,图4a中的401)中并且沿三维(3d)存储器的竖直堆叠的存储器胞元阵列中的水平存取装置和水平存储节点的朝向轴线形成。在图7c中,相邻的相对竖直存取线740-3由指示从图纸的平面和朝向向内设定的位置的虚线展示。

90.图7d展示了沿图7a中的切割线c-c'截取的横截面视图,其示出了在本公开的实施例的一个示例半导体制造工艺中,在此特定点处的半导体结构的另一视图。图7d所示的横截面视图展示为沿第一介电材料730-1、730-2、

……

、730-n、半导体材料732-1、 732-2、

……

、732-n和第二介电材料733-1、733-2、

……

、733-n的交替层的重复迭代的轴线在一定区域的外部,在图纸的平面中在左边和右边在第二方向(d2)705上延伸,在所述区域中,水平定向的存取装置和水平定向的存储节点(例如,电容器胞元)将在半导体材料732-1、732-2、

……

、732-n的层内形成。在图纸的左端处示出第一介电材料 730-1、730-2、

……

、730-n、半导体材料732-1、732-2、

……

、732-n和第二介电材料 733-1、733-2、

……

、733-n的交替层的重复迭代,在所述位置处,水平定向的数位线(例如,图1及以下等等所示的数位线107-1、107-2、

……

、107-p)可以被整合,以形成结合上文图4a-4f所述的具有第一源极/漏极区域的电接触或数位线导电接触材料。

91.再次,虽然第一源极/漏极区域和第二源极/漏极区域的引用在本文中用于表示两个单独且不同的源极/漏极区域,但被称为“第一”和/或“第二”源极/漏极区域的源极/ 漏极区域并不旨在具有某些独特的含义。源极/漏极区域中的一个源极/漏极区域仅旨在连接到数位线(例如,107-2),并且另一个源极/漏极区域可以连接到存储节点。

92.图7e展示了沿图7a中的切割线d-d'截取的横截面视图,其示出了在本公开的实施例的一个示例半导体制造工艺中,在此特定点处的半导体结构的另一视图。在图纸的平面中从右向左展示了图7e所示的横截面视图,所述平面在第一方向(d1)709上沿第一介电材料730-1、730-2、

……

、730-n、半导体材料732-1、732-2、

……

、732-n和第二介电材料733-1、733-2、

……

、733-n的交替层的重复迭代的轴线延伸,跨所述多个单独的竖直存取线740-1、740-2、

……

、740-4相交,并且使半导体材料732-1、732-2、

……

、 732-n的区域相交,在所述区域中可以形成通过栅极电介质738与所述多个单独的竖直存取线740-1、740-2、

……

、740-4分开的沟道和体区域。在图7e中,第一介电填充材料739示出为使相邻的水平定向的

2、

……

、832-n和第二介电材料833-1、833-2、

……

、833-n的交替层的重复迭代的轴线,沿图纸平面在左边和在右边在第二方向(d2)805延伸,沿所述交替层并在所述交替层内,水平定向的存取装置和水平定向的存储节点(例如,电容器胞元)在半导体材料832-1、832-2、

……

、832-n层内形成。在图8c的示例实施例中,水平定向的存储节点(例如,电容器胞元)展示为已经在此半导体制造工艺中形成,并且示出了通过胞元电介质863分开的耦接到水平存取装置的源极/漏极区域的第一电极861(例如,底部电极) 和耦接到如接地平面等公共电极平面的第二电极856(例如,顶部电极)。然而,实施例不限于此实例。在其它实施例中,形成通过胞元电介质863分开的要耦接到水平存取装置的源极/漏极区域的第一电极861(例如,底部电极)和要耦接到如接地平面等公共电极平面的第二电极856(例如,顶部电极)是在形成接下来描述的水平定向的存取装置的旨在定位(例如,布置形成)的半导体材料832-1、832-2、

……

、832-n的区域中的第一源极/漏极区域、沟道和体区域以及第二源极/漏极区域之后形成的。

97.在图8c的示例实施例中,示出了在第二水平开口(例如,图7c所示的734)中形成具有要耦接到水平存取装置的源极/漏极区域的第一电极861(例如,底部电极)和要耦接到如接地平面等公共电极平面的第二电极856(例如,顶部电极)的水平定向的存储节点,所述第二水平开口在图纸的平面中在左边和右边在第二方向(d2)上延伸与竖直开口(例如,图7c中的751)相距第二距离(d2开口),所述竖直开口在竖直堆叠中并且沿三维(3d) 存储器的竖直堆叠(例如,图4a中的401)的存储器胞元的阵列中的水平存取装置和水平存储节点的朝向轴线形成。在图8c中,相邻的相对竖直存取线840-3由指示从图纸的平面和朝向向内设定的位置的虚线展示。

98.图8d展示了沿图8a中的切割线c-c'截取的横截面视图,其示出了在本公开的实施例的一个示例半导体制造工艺中,在此特定点处的半导体结构的另一视图。图8d所示的横截面视图展示为沿第一介电材料830-1、830-2、

……

、830-n、半导体材料832-1、832-2、

……

、832-n和第二介电材料833-1、833-2、

……

、833-n交替层的重复迭代的轴线在一定区域的外部,在图纸平面在左边和在右边的在第二方向(d2)805上延伸,在所述区域中,水平定向的存取装置和水平定向的存储节点(例如,电容器胞元)将在半导体材料832-1、832-2、

……

、832-n的层内形成。在图8c中,介电材料841示出为填充水平定向的存取装置之间的空间,所述水平定向的存取装置可以沿第一方向(d1)间隔,延伸到竖直定向的存储器胞元的三维阵列的图纸的平面中并从其中延伸出去。然而,在图8d的横截面视图中,电容器胞元结构的第二电极856(例如,顶部公共电极)另外示出为存在于水平相邻的装置之间的空间中。图纸的左端处示出为第一介电材料830-1、 830-2、

……

、830-n、半导体材料832-1、832-2、

……

、832-n和第二介电材料833-1、 833-2、

……

、833-n的交替层的重复迭代,在所述位置处,水平定向的数位线(例如,图1及以下等等所示的数位线107-1、107-2、

……

、107-p)可以被整合以形成以下详细描述的与第二源极/漏极区域或数位线导电接触材料的电接触。

99.图8e展示了沿图8a中的切割线d-d'截取的横截面视图,其示出了在本公开的实施例的一个示例半导体制造工艺中,在此特定点处的半导体结构的另一视图。在图纸的平面中从右向左展示了图8e所示的横截面视图,所述平面在第一方向(d1)809上沿第一介电材料830-1、830-2、

……

、830-n、半导体材料832-1、832-2、

……

、832-n和第二介电材料833-1、833-2、

……

、833-n的交替层的重复迭代的轴线延伸,跨所述多个单独的竖直存取线840-1、

840-2、

……

、840-4相交,并且使半导体材料832-1、832-2、

……

、 832-n的区域相交,在所述区域中可以形成通过栅极介电材料838与所述多个单独的竖直存取线840-1、840-2、

……

、840-4分开的沟道和体区域。在图8e中,第一介电填充材料839示出为使相邻的水平定向的存取装置与水平定向的存储节点之间的空间分开,如下文更详细描述的,所述水平定向的存取装置与水平定向的存储节点可以延伸到图纸平面中并从其中延伸出去,并且可以沿第一方向(d1)809隔开并且在三维(3d)存储器中竖直堆叠于在第三方向(d3)811方向上延伸的阵列中。图8展示了根据本公开的许多实施例的耦接到水平定向的存储节点并且耦接到如可以形成竖直堆叠的存储器胞元阵列的一部分的竖直定向的存取线和水平定向的数位线的示例水平定向的存取装置的一部分的横截面视图。水平定向的存取装置801可以具有由沟道和体区域分开的第一源极/ 漏极区域和第二源极/漏极区域,并且具有与沟道区域相对并且通过栅极电介质与其分开的栅极。

100.图9是根据本公开的多个实施例的呈包含存储器装置903的计算系统900的形式的设备的框图。如本文所使用的,例如,存储器装置903、存储器阵列910和/或主机902 也可以分别被认为是“设备”。根据实施例,存储器装置903可以包括根据本文所述的实施例的具有形成具有数位线和体触点的存储器胞元的至少一个存储器阵列910。

101.在此实例中,系统900包含主机902,所述主机通过接口904耦接到存储器装置903。在各种其它类型的系统中,计算系统900可以是个人膝上型计算机、台式计算机、数码相机、移动电话、存储卡读取器或物联网(iot)启用的装置。主机902可以包含能够访问存储器903的多个处理资源(例如,一或多个处理器、微处理器或某种其它类型的控制电路系统)。系统900可以包含单独的集成电路,或者主机902和存储器装置903两者均可以位于同一集成电路上。例如,主机902可以是包括多个存储器装置903的存储器系统的系统控制器,其中系统控制器905通过如中央处理单元(cpu)等另一个处理资源来提供对相应存储器装置903的访问。

102.在图1所示出的实例中,主机902负责执行操作系统(os)和/或可以(例如,通过控制器905从存储器装置903)加载到所述操作系统的各种应用(例如,进程)。可以通过从主机902向存储器装置903提供访问命令以访问包括os和/或各种应用的数据来从存储器装置903加载os和/或各种应用。主机902还可以通过向存储器装置903提供访问命令以检索在os和/或各种应用的执行中所利用的所述数据来访问由os和/或各种应用所利用的数据。

103.为了清楚起见,已经将系统900简化为集中于与本公开特别相关的特征。存储器阵列910可以是dram阵列,所述dram陈列包括根据本文所述的技术形成的具有数位线和体触点的至少一个存储器胞元。例如,存储器阵列910可以是如3d-dram存储器阵列等非屏蔽dl 4f2阵列。阵列910可以包括存储器胞元,所述存储器胞元以由字线(其在本文中可以称为存取线或选择线)耦接的行和由数位线(其在本文中可以称为读出线或数据线)耦接的列布置。尽管在图1中示出了单个阵列910,但实施例不限于此。例如,存储器装置903可以包含许多阵列910(例如,许多dram胞元库)。

104.存储器装置903包含用于锁存接口904上提供的地址信号的地址电路系统906。所述接口可以包含例如采用适合协议的物理接口(例如,数据总线、地址总线和命令总线或组合的数据/地址/命令总线)。此类协议可以是定制的或专有的,或接口904可以采用如外围组件互连快速(pcie)、gen-z、ccix等标准化协议。通过行解码器908和列解码器 912接收并

解码地址信号以访问存储器阵列910。可以通过使用读出电路系统911读出读出线上的电压和/或电流变化来从存储器阵列910读取数据。读出电路系统911可以包括例如读出放大器,所述读出放大器可以读取并锁存来自存储器阵列910的一页(例如,一行)数据。i/o电路系统907可以用于通过接口904与主机902进行双向数据通信。读取/写入电路系统913用于将数据写入存储器阵列910或从存储器阵列910读取数据。作为实例,电路系统913可以包括各种驱动器、锁存器电路系统等。

105.控制电路系统905包含寄存器918并解码主机902提供的信号。信号可以是由主机 902提供的命令。这些信号可以包含芯片启用信号、写入启用信号和地址锁存信号,所述信号用于控制在存储器阵列910上执行的操作,包含数据读取操作、数据写入操作和数据擦除操作。在各个实施例中,控制电路系统905负责执行来自主机902的指令。控制电路系统905可以包括状态机、定序器和/或某种其它类型的控制电路系统,所述控制电路系统可以以硬件、固件或软件或这三种的任何组合的形式实施。在一些实例中,主机902可以是存储器装置103外部的控制器。例如,主机902可以是耦接到计算装置的处理资源的存储器控制器。

106.术语半导体可以指例如材料、晶圆或衬底,并且包含任何基底半导体结构。“半导体”应被理解为包含蓝宝石上硅(sos)技术、绝缘体上的硅(soi)技术、薄膜晶体管(tft) 技术、掺杂和未掺杂的半导体、由基底半导体结构支撑的外延硅以及其它半导体结构。此外,当在先前描述中引用半导体时,可能已经利用先前的工艺步骤在基底半导体结构中形成了区域/结,并且术语半导体可以包含含有此类区域/结的底层材料。

107.本文的附图遵循编号惯例,其中一或多个第一数字与附图编号相对应,并且剩余数字标识附图中的元件或组件。可以通过使用类似的数字来标识不同附图之间的类似(例如,相同)元件或组件。如将理解的,可以添加、交换和/或消除在本文的各个实施例中示出的元件,以提供本公开的多个另外的实施例。另外,如应理解的,在图中提供的元件的比例和/或相对尺度旨在展示本公开的实施例并且不应以限制性的意义而采用。

108.如本文所使用的,“许多”或“一定量的”事物可以是指此类事物中的一或多个。例如,许多或一定量的存储器胞元可以是指一或多个存储器胞元。多个某物意为两个或两个以上。如本文所使用的,共同执行的多个行为是指在特定时间段内重叠、至少部分地重叠的行为。本文中使用的术语“耦接”可以包含与无中间元件电耦接、直接耦接和 /或直接连接(例如,通过直接的物理接触)、与中间元件间接耦接和/或与连接,或无线耦接。术语耦接可以进一步包含彼此协作或交互(例如,像在因果关系中一样)的两个或两个以上的元件。耦接在两个元件之间的元件可以在两个元件之间并且耦接到所述两个元件中的每个元件。

109.应当认识到,术语竖直的解释了由于常规制造、测量和/或组装变化导致的与“确切的”竖直的变化,并且本领域的普通技术人员应了解术语“垂直”的含义。例如,竖直的可以对应于z方向。如本文所使用的,当特定元件“邻近”另一元件时,所述特定元件可以覆盖所述另一元件,可以位于所述另一元件之上或位于所述另一元件的侧面和/ 或可以与所述另一元件直接物理接触。位于侧面可以指例如可以垂直于z方向的水平方向(例如,y方向或x方向)。

110.尽管本文已经展示并描述了具体实施例,但是本领域的普通技术人员将理解,旨在实现相同结果的布置可以替换所示出的具体实施例。本公开旨在覆盖本公开的各个实施例的改编形式或变化形式。应理解的是,上面的描述以说明性方式而非限制性方式进行。在

阅读以上描述后,上述实施例的组合以及本文未具体描述的其它实施例对于本领域的技术人员而言将是显而易见的。本公开的各个实施例的范围包含以上结构和方法被使用的其它应用。因此,本公开的各个实施例的范围应当参考所附权利要求连同与此类权利要求被赋予的等效物的全部范围确定。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。