1.本技术案主张2020年8月4日申请的美国正式申请案第16/984,911号的优先权及益处,该美国正式申请案的内容以全文引用的方式并入本文中。

2.本公开是关于一种半导体元件以及该半导体元件的制备方法。特别是有关于一种具有可编程特征的半导体元件,以及具有该可编程构件的该半导体元件的制备方法。

背景技术:

3.半导体元件是使用在不同的电子应用,例如个人电脑、手机、数码相机,或其他电子设备。半导体元件的尺寸是逐渐地变小,以符合计算能力所逐渐增加的需求。然而,在尺寸变小的制程期间,是增加不同的问题,且如此的问题在数量与复杂度上持续增加。因此,仍然持续着在达到改善品质、良率、效能与可靠度以及降低复杂度方面的挑战。

4.上文的“先前技术”说明仅是提供背景技术,并未承认上文的“先前技术”说明揭示本公开的标的,不构成本公开的先前技术,且上文的“先前技术”的任何说明均不应作为本案的任一部分。

技术实现要素:

5.本公开的一实施例提供一种半导体元件,具有一基底;一通道区,位在该基底中;多个第一杂质区,位在该基底中,且分别位在该通道区的两端上;一栅极介电层,位在该通道区上;一栅极下导电层,位在该栅极介电层上;多个第一接触点,分别位在所述第一杂质区上;所述可编程隔离层,分别位在所述第一接触点上;以及一上导电层,位在所述可编程隔离层上,且电性连接到该栅极下导电层。

6.在本公开的一些实施例中,所述可编程隔离层的厚度是不同于该栅极介电层的一厚度。

7.在本公开的一些实施例中,该栅极介电层具有与所述可编程隔离层相同的一厚度。

8.在本公开的一些实施例中,该半导体元件还包括一栅极上导电层,位在该栅极下导电层上,并电性连接到该上导电层,其中该栅极上导电层是由下列材料所制:硅化钛(titanium silicide)、硅化镍(nickel silicide)、硅化镍铂(nickel platinum silicide)、硅化钽(tantalum silicide)或硅化钴(cobalt silicide)。

9.在本公开的一些实施例中,该栅极上导电层的一厚度是介于大约2nm与大约20nm之间。

10.在本公开的一些实施例中,该半导体元件还包括多个第一栅极间隙子,位在该栅极介电层的各侧壁上以及在该栅极下导电层的各侧壁上。

11.在本公开的一些实施例中,该半导体元件还包括多个第二栅极间隙子,位在所述第一栅极间隙子的各侧壁上。

12.在本公开的一些实施例中,该半导体元件还包括一高峰部,具有一三角形剖面轮

廓,并位在该通道区与该栅极介电层之间,其中该栅极介电层包括一罩盖部以及多个平坦部,该罩盖部位在该高峰部上,所述平坦部分别连接到该罩盖部的两端,并位在该通道区上。

13.在本公开的一些实施例中,该罩盖部的一厚度是等于或小于所述平坦部的厚度。

14.在本公开的一些实施例中,该高峰部包括一第一刻面(first faceted plane)以及一第二刻面,是均接触该罩盖部,且在该第一刻面与该第二刻面之间的一角度,是介于大约50度到大约60度之间。

15.在本公开的一些实施例中,该半导体元件还包括一栅极通孔(gate via),位在该上导电层与该栅极上导电层之间,其中该上导电层与该栅极上导电层是经由该栅极通孔而电性连接。

16.在本公开的一些实施例中,该半导体元件还包括一覆盖层,是覆盖所述第一杂质区、所述第一栅极间隙子以及该栅极上导电层,其中所述第一接触点分别沿着该覆盖层设置,且位在所述第一杂质区上,而该栅极通孔是沿着该覆盖层设置,并位在该栅极上导电层上。

17.在本公开的一些实施例中,该半导体元件还包括一第二杂质区,位在该基底中,并远离所述第一杂质区设置,其中该第二杂质区具有与所述第一杂质区不同的一电子型态,且其中一第一接触点是电性连接到该第二杂质区。

18.本公开的另一实施例提供一种半导体元件,具有一基底;一通道区,位在该基底中;多个第一杂质区,位在该基底中,且分别位在该通道区的两端上;一栅极介电层,位在该通道区上;一栅极下导电层,位在该栅极介电层上;一栅极通孔,位在该栅极下导电层上;多个第一接触点,分别位在所述第一杂质区上;多个可编程隔离层,分别位在所述第一接触点上;以及多个上导电层,分别位在所述可编程隔离层与该栅极通孔上。

19.本公开的另一实施例提供一种半导体元件的制备方法。该制备方法包括:提供一基底;形成一通道区在该基底中;形成一栅极介电层在该通道区上;形成一栅极下导电层在该栅极介电层上;形成多个第一杂质区在该通道区的两端上;形成多个第一接触点在所述第一杂质区上;形成多个可编程隔离层在所述接触点上;形成一栅极通孔在该栅极下导电层上;以及形成一上导电层在该栅极通孔与所述可编程隔离层上。

20.在本公开的一些实施例中,该半导体元件的制备方法还包括一步骤:形成多个第一栅极间隙子在该栅极下导电层的各侧壁上以及在该栅极介电层的各侧壁上。

21.在本公开的一些实施例中,该半导体元件的制备方法还包括一步骤:形成一栅极上导电层在该栅极通孔与该栅极下导电层之间。

22.在本公开的一些实施例中,该栅极上导电层是由下列材料所制:硅化钛、硅化镍、硅化镍铂、硅化钽或硅化钴。

23.在本公开的一些实施例中,该通道区的一掺杂浓度(dopant concentration)是小于所述第一杂质区的一掺杂浓度。

24.在本公开的一些实施例中,该通道区与该基底具有不同的电子型态(electrical types)。

25.由于本公开该半导体元件的设计,当施加一编程电压(programming voltage)时,该栅极介电层及/或所述可编程隔离层可能会破裂。因此,该半导体元件可当成一可编程元

件使用,并可使用在一芯片的一修复系统(repair system),以改善该芯片的良率。此外,由于高峰部(peak portion)的存在,所以可改善编程该半导体元件的可靠度(reliability)。

26.上文已相当广泛地概述本公开的技术特征及优点,而使下文的本公开详细描述得以获得较佳了解。构成本公开的权利要求标的的其它技术特征及优点将描述于下文。本公开所属技术领域中具有通常知识者应了解,可相当容易地利用下文揭示的概念与特定实施例可作为修改或设计其它结构或制程而实现与本公开相同的目的。本公开所属技术领域中具有通常知识者亦应了解,这类等效建构无法脱离后附的权利要求所界定的本公开的精神和范围。

附图说明

27.参阅实施方式与权利要求合并考量图式时,可得以更全面了解本技术案的揭示内容,图式中相同的元件符号是指相同的元件。

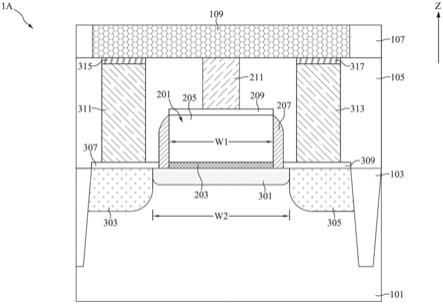

28.图1为依据本公开一实施例一种半导体元件的剖视示意图。

29.图2为依据本公开一实施例具有该半导体元件的电路架构图。

30.图3到图7为依据本公开一实施例各半导体元件的剖视示意图。

31.图8为依据本公开一实施例一种半导体元件的制备方法的流程示意图。

32.图9到图19为依据本公开一实施例该半导体元件的制备方法的一流程的剖视示意图。

33.其中,附图标记说明如下:

34.1a:半导体元件

35.1b:半导体元件

36.1c:半导体元件

37.1d:半导体元件

38.1e:半导体元件

39.1f:半导体元件

40.101:基底

41.103:绝缘层

42.105:第一隔离层

43.107:第二隔离层

44.109:上导电层

45.109-1:上导电层

46.109-3:上导电层

47.109-5:上导电层

48.111:高峰部

49.113:覆盖层

50.201:栅极结构

51.203:栅极介电层

52.203-1:罩盖部

53.203-3:平坦部

54.205:栅极下导电层

55.207:第一栅极间隙子

56.209:栅极上导电层

57.211:栅极通孔

58.213:第二栅极间隙子

59.301:通道区

60.303:第一杂质区

61.305:第一杂质区

62.307:第一导电层

63.309:第一导电层

64.311:第一接触点

65.313:第一接触点

66.315:可编程隔离层

67.317:可编程隔离层

68.401:第二杂质区

69.403:第二导电层

70.405:第三导电层

71.501:第一主动区

72.503:第二主动区

73.601:凹陷

74.inib:脉冲信号

75.na:第一节点

76.nw1:高电压阻断开关

77.nw2:电流限制开关

78.pp:编程部

79.sens:感测晶体管

80.sp:感测部

81.vbias:偏压

82.vprog:编程电压

83.vsel:选择电压

84.w1:宽度

85.w2:宽度

86.α:角度

87.z:方向

88.10:制备方法

89.s11:步骤

90.s13:步骤

91.s15:步骤

92.s17:步骤

characteristics)运行的一元件,而一光电元件(electro-optic device)、一发光显示元件(light-emitting display device)、一半导体线路(semiconductor circuit)以及一电子元件(electronic device),是均包括在半导体元件的范畴中。

104.应当理解,在本公开的描述中,上方(above)(或之上(up))是对应z方向箭头的该方向,而下方(below)(或之下(down))是对应z方向箭头的相对方向。

105.应当理解,在本公开的描述中,一“深度(depth)”表示一元件(例如一层、沟槽、孔、开口等等)在一剖视图中的一垂直尺寸(vertical size),其是从该元件的一上表面测量到一下表面;一“宽度(width)”表示一元件(例如一层、沟槽、孔、开口等等)在剖视图中的一尺寸(size),其是从该元件的一侧表面测量到一相对表面。可在指出的地方,术语“厚度”可以代替“宽度”及/或“深度”。

106.应当理解,在本公开的描述中,一元件(或一特征)沿着方向z位在最高垂直高度(level)的一表面,是表示成该元件(或该特征)的一上表面。一元件(或一特征)沿着方向z位在最低垂直高度(level)的一表面,是表示成该元件(或该特征)的一下表面。

107.图1为依据本公开一实施例中一种半导体元件1a的剖视示意图。

108.请参考图1,半导体元件1a可具有一基底101、一绝缘层103、一第一隔离层105、一第二隔离层107、一上导电层109、一栅极结构201、多个第一栅极间隙子207、一栅极上导电层209、一栅极通孔211、一通道区301、多个第一杂质区303与305、多个第一导电层307与309、多个第一接触点311与313以及多个可编程隔离层315与317。

109.请参考图1,在一些实施例中,基底101可为块状(bulk)半导体,其是由整体由至少一种半导体材料组成。提供给块状半导体的半导体材料可包含任何材料,或是多个材料的堆叠,所述材料是具有半导体特性,包括硅、锗、硅锗合金、iii-v族化合物半导体或ii-vi族化合物半导体,但并不以此为限。iii-v族化合物半导体是为材料,其是包括元素周期表中iii族的至少一元素以及元素周期表中v族的至少一元素。ii-vi族化合物半导体为材料,其是包括元素周期表中ii族的至少一元件以及元素周期表中vi族的至少一元素。在一些实施例中,基底101可掺杂有一掺杂物,例如磷(phosphorus)、砷(arsenic)、锑(antimony)或硼(boron)。在所述的实施例中,基底101是掺杂有硼,并具有一第一电子类型。在一些实施例中,基底101可具有一有机半导体或一层式(layered)半导体,而层式半导体是例如硅/硅锗(silicon/silicon germanium)、绝缘体上覆硅(silicon-on-insulator)或绝缘体上覆硅锗(silicon germanium-on-insulator)。

110.请参考图1,绝缘层103可设置在基底101中。绝缘层103的上表面可大致与基底101的上表面为共面。绝缘层103可具有一深宽比(aspect ratio),是介于大约1:4到大约1:10之间。在一些实施例中,绝缘层103的各侧壁可呈锥形(tapered)。在一些实施例中,绝缘层103的各侧壁可大致呈垂直。举例来说,绝缘层103可由下列材料所制:氧化硅、氮化硅、氮氧化硅、氧化氮化硅或氟化物掺杂硅酸盐(fluoride-doped silicate)。

111.应当理解,若是存在一个垂直平面,则一表面(或侧壁)是呈“垂直(vertical)”的话,则该表面与该垂直平面的偏离不会超过该表面的均方根粗糙度的三倍。

112.应当理解,在本公开的描述中,氮氧化硅表示一物质(substance),其是包含硅、氮以及氧,且在其中的氧的一比率是大于氮的一比率。氧化氮化硅是表示一物质,其是包含硅、氧以及氮,且在其中的氮的一比率是大于氧的一比率。

113.请参考图1,第一隔离层105可设置在基底101上。第二隔离层107可设置在第一隔离层105上。第一隔离层105与第二隔离层107可具有厚度,是介于大约0.5微米(micrometers)到大约3.0微米之间。第一隔离层105与第二隔离层107可由下列材料所制:氧化硅、硼磷硅酸盐玻璃(borophosphosilicate glass)、未掺杂硅酸盐玻璃(undoped silicate glass)、氟硅酸盐玻璃(fluorinated silicate glass)、低介电常数(low-k)介电材料、类似物或其组合。第一隔离层105与第二隔离层107可由不同材料所制,但并不以此为限。所述低介电常数介电材料可具有一介电常数,是小于3.0或甚至小于2.5。在一些实施例中,所述低介电常数介电材料可具有一介电常数,是小于2.0。

114.请参考图1,通道区301可设置在基底101中。通道区301的上表面可大致与基底101的上表面为共面。通道区301可掺杂有一掺杂物,例如磷、砷、锑或硼。在所述的实施例中,通道区301掺杂有磷,并具有一第二电子类型。通道区301的掺杂浓度较大于基底101的掺杂浓度。

115.请参考图1,所述第一杂质区303、305可设置在基底101中。所述第一杂质区303、305可分别对应设置在通道区301的两端上。所述第一杂质区303、305的各上表面可大致与基底101的上表面为共面。所述第一杂质区303、305的各下表面可位在一垂直位面,是较低于通道区301的一垂直位面。

116.所述第一杂质区303、305可掺杂有一掺杂物,例如磷、砷、锑或硼。在所述的实施例中,所述第一杂质区303、305掺杂有磷,并具有第二电子类型。所述第一杂质区303、305的掺杂浓度可较大于通道区301的掺杂浓度。所述第一杂质区303、305与通道区301可电性连接。所述第一杂质区303、305在文中亦可表示成源极/漏极区。

117.请参考图1,栅极结构201可设置在通道区301上,并位在第一隔离层105中。栅极结构201可包括一栅极介电层203以及一栅极下导电层205。

118.请参考图1,栅极介电层203可设置在通道区301上。栅极介电层203的一宽度w1可较小于通道区301的一宽度w2。在一些实施例中,举例来说,栅极介电层203可由氧化硅所制。在一些实施例中,举例来说,栅极介电层203可由高介电常数(high-k)介电材料所制,例如金属氧化物、金属氮化物、金属硅酸盐(metal silicate)、过渡金属氧化物(transition metal-oxide)、过渡金属氮化物、过渡金属硅酸盐、金属的氮氧化物、金属铝酸盐(metal aluminate)、硅酸锆(zirconium silicate)、铝酸锆(zirconium aluminate)或其组合。尤其是,栅极介电层203可由下列材料所制:氧化铪(hafnium oxide)、氧化铪硅(hafnium silicon oxide)、氮氧化铪硅(hafnium silicon oxynitride)、氧化铪钽(hafnium tantalum oxide)、氧化铪钛(hafnium titanium oxide)、氧化铪锆(hafnium zirconium oxide)、氧化镧铪(hafnium lanthanum oxide)、氧化镧(lanthanum oxide)、氧化锆(zirconium oxide)、氧化钛(titanium oxide)、氧化钽(tantalum oxide)、氧化钇(yttrium oxide)、钛酸锶(strontium titanium oxide)、钛酸钡(barium titanium oxide)、氧化钡锆(barium zirconium oxide)、氧化硅镧(lanthanum silicon oxide)、氧化硅铝(aluminum silicon oxide)、氧化铝(aluminum oxide)、氮化硅(silicon nitride)、氮氧化硅(silicon oxynitride)、氧化氮化硅(silicon nitride oxide)或其组合。在一些实施例中,栅极介电层203可为一多层结构,举例来说,其是为一层氧化硅以及另一层高介电常数介电材料。

119.在一些实施例中,一界面层(interfacial layer)(图1中未示)可设置在栅极介电层203与基底101之间。界面层可具有一厚度,介于大约到大约之间。在一些实施例中,界面层可具有一厚度,是介于大约到大约之间。在半导体元件1a的制造期间,界面层可帮助栅极介电层203的形成。

120.请参考图1,栅极下导电层205可设置在栅极介电层203上。在一些实施例中,举例来说,栅极下导电层205可由一导电材料所制,例如多晶硅、多晶硅锗或其组合。在一些实施例中,栅极下导电层205可掺杂有一掺杂物,例如磷、砷、锑或硼。在一些实施例中,举例来说,栅极下导电层205可由下列材料所制:钨、铝、钛、铜、类似物或其组合。栅极结构201、通道区301以及所述第一杂质区303可表示为一空乏模式晶体管(depletion mode transistor)。

121.在一些实施例中,栅极介电层203与栅极下导电层205可具有一u形剖面轮廓,并可适合于整合在一后栅极(gate last)或先栅极(gate first)处理流程(process flow)。

122.请参考图1,所述第一栅极间隙子207可设置在栅极下导电层205的各侧壁上以及在栅极介电层203的各侧壁上。所述第一栅极间隙子207亦可设置在通道区301上。举例来说,所述第一栅极间隙子207可由氧化硅、氮化硅或类似物所制。

123.请参考图1,栅极上导电层209可设置在栅极下导电层205上,并在第一隔离层105中。栅极上导电层209可具有一厚度,是介于大约2nm到大约20nm之间。举例来说,栅极上导电层209可由下列材料所制:硅化钛、硅化镍、硅化镍铂、硅化钽或硅化钴。

124.请参考图1,所述第一导电层307、309可分别对应设置在所述第一杂质区303、305上。所述第一导电层307、309可具有与栅极上导电层209相同的厚度。所述第一导电层307、309可由与栅极上导电层209相同的材料所制。栅极上导电层209与第一导电层307、309可使用成欧姆接触(ohmic contacts)。

125.请参考图1,栅极通孔211可设置在栅极上导电层209上以及在第一隔离层105中。栅极通孔211的上表面可大致与第一隔离层105的上表面为共面。举例来说,栅极通孔211可由下列材料所制:钨、钴、锆、钽、钛、铝、钌、铜、金属碳化物(例如碳化钽、碳化钛、碳化钽镁(tantalum magnesium carbide))、金属氮化物(例如氮化钛)、过渡金属铝化物(transition metal aluminides)或其组合。栅极通孔211可电性连接到栅极上导电层209。

126.请参考图1,所述第一接触点311、313可分别对应设置在所述第一导电层307、309上。所述第一接触点311、313可设置在第一隔离层105中。所述第一接触点311、313的厚度可较小于第一隔离层105的厚度。举例来说,所述第一接触点311、313可由下列材料所制:钨、钴、锆、钽、钛、铝、钌、铜、金属碳化物(例如碳化钽、碳化钛、碳化钽镁(tantalum magnesium carbide))、金属氮化物(例如氮化钛)、过渡金属铝化物(transition metal aluminides)或其组合。所述第一接触点311、313可分别电性连接到所述第一杂质区313、305。

127.请参考图1,所述可编程隔离层315、317可分别对应设置在所述第一接触点311、313上。所述可编程隔离层315、317可设置在第一隔离层105中。所述可编程隔离层315、317的各上表面可大致与栅极通孔211的上表面为共面。在一些实施例中,所述可编程隔离层315、317可具有相同的厚度。在一些实施例中,所述可编程隔离层315、317可具有不同厚度。在一些实施例中,栅极介电层203与所述可编程隔离层315、317可具有相同的厚度。在一些

实施例中,栅极介电层203与所述可编程隔离层315、317可具有不同厚度。在一编程程序期间,栅极通孔211与所述可编程隔离层315、317的各厚度是可决定其编程电流或编程电压。

128.在一些实施例中,所述可编程隔离层315、317可由与栅极介电层203相同的材料所制。在一些实施例中,所述可编程隔离层315、317可与栅极介电层203不相同的材料所制。举例来说,所述可编程隔离层315、317可由下列材料所制:氧化硅、氮化硅、氮氧化硅、氧化氮化硅、氧化铪(hafnium oxide)、氧化铪硅(hafnium silicon oxide)、氮氧化铪硅(hafnium silicon oxynitride)、氧化镧(lanthanum oxide)、氧化镧铝(lanthanum aluminum oxide)、氧化锆(zirconium oxide)、氧化硅锆(zirconium silicon oxide)、氮氧化硅锆(zirconium silicon oxynitride)、氧化铝或其组合。所述可编程隔离层315、317可由相同材料所制,但并不以此为限。

129.如图1所示,上导电层109可设置在第二隔离层107中。上导电层109可设置在栅极通孔211与所述可编程隔离层315、317上。上导电层109可电性连接到栅极通孔211。在一些实施例中,上导电层109可由与所述第一接触点311、313相同的材料所制。在一些实施例中,上导电层109可由与所述第一接触点311、313不相同的材料所制。举例来说,上导电层109可由下列材料所制:钨、钴、锆、钽、钛、铝、钌、铜、金属碳化物(例如碳化钽、碳化钛、碳化钽镁(tantalum magnesium carbide))、金属氮化物(例如氮化钛)、过渡金属铝化物(transition metal aluminides)或其组合。

130.上导电层109、可编程隔离层315以及第一接触点311的构成是可表示成一源极电容器。上导电层109、可编程隔离层317以及第一接触点313的构成是可表示成一漏极电容器。应当理解,在本公开的描述中,源极与漏极可互换使用。上导电层109、栅极通孔211、栅极结构201以及通道区301的构成是可表示成一栅极电容器。源极电容器、漏极电容器以及栅极电容器可当作可编程构件使用,例如反熔丝(anti-fuses)。

131.在半导体元件1a的一编程程序期间,可提供一编程电压,举例来说,编程电压是经由上导电层109与基底101而施加到半导体元件1a。在一给定编程时间之后,来自于编程电压的高电压应力(high voltage stress)可能导致栅极介电层203及/或所述可编程隔离层315、317的破裂(rupture)或损坏(breakdown)。在编程程序之后,源极电容器、漏极电容器以及栅极电容器的各导电状态,是可从一关闭(off)状态转换至一开启(on)状态。在一些实施例中,在编程程序之后,可能使所有的栅极介电层203与所述可编程隔离层315、317破裂。在一些实施例中,在编程程序之后,可能仅栅极介电层203与所述可编程隔离层315、317的其中两个破裂。

132.图2为依据本公开一实施例具有该半导体元件1a的电路架构图。

133.在一些实施例中,半导体元件1a整体上可当作一可编程元件使用,并可与其他半导体元件整合在一起。请参考图2,例示的电路可包括一编程部pp以及一感测部sp。编程部pp可由半导体元件1a与一高电压阻断开关(high voltage block switch)nw1以及一电流限制开关(current limit switch)nw2串接所构成。半导体元件1a、高电压阻断开关nw1以及电流限制开关nw2的串接,可避免由编程过应力(programming overstress)所造成的接触点烧坏问题(contact burnt problem)。

134.当对编程部pp进行编程时,一编程电压vprog可施加到半导体元件1a的上导电层109(为了清楚起见,图2中未示),且一选择电压vsel可施加到电流限制开关nw2的栅极节点

(gate node)。在一给定的编程时间之后,源自编程电压vprog的高电压应力可导致半导体元件1a的栅极介电层203(为了清楚起见,图2中未示)及/或所述可编程隔离层315、317(为了清楚起见,图2中未示)的破裂(rupture)或损坏(breakdown)。选择电压vsel是可在编程期间限制最大电流,是可施加选择电流vsel以避免接触点被过度编程电流所烧坏。当编程时,高电压阻断开关nw1可插入在半导体元件1a与感测部sp之间,以去耦合(decouple)感测部sp与高电场。偏压vbias是施加到高电压阻断开关nw1的栅极节点,并设定到编程电压vprog的一半数值。

135.在电源启动期间,可开启感测部sp,并可检测半导体元件1a的状态是否在破裂状态。若是半导体元件1a是未受损伤(例如无破裂)的话,在电源开启(power up)期间,一脉冲信号inib是用于在电源开启期间初始化闩锁(latch),并可启动(activated)到low,且第一节点na可初始化到high。因为选择电压vsel与编程电压vprog是均为接地,所以当一感测晶体管sens启动到high时,半导体元件1a的状态可感测到第一节点na。若是半导体元件1a在破裂状态时,可形成从第一节点na到接地(vprog)的一电流路径。因此,第一节点na的状态可转换至low。否则,第一节点na可停留在high的预充电状态(precharged state)。

136.应当理解,用于遍及所有图式的相同或类似元件编号,是用于表示相同或类似的特征、元件或结构,因此对于每一个图式将不会重复相同或类似特征、元件或结构的详细解释。

137.图3到图7为依据本公开一实施例各半导体元件1b、1c、1d、1e、1f的剖视示意图。

138.请参考图3,在半导体元件1b中,上导电层109-1、109-3、109-5可分别对应设置在栅极通孔211与所述编程隔离层315、317上。上导电层109-1、109-3、109-5可电性耦接到不同的外部电压源。在上导电层109-1、109-3、109-5的辅助下,源极电容器、漏极电容器以及栅极电容器的编程程序是可分别执行。在每一编程程序之后,取决于所使用的上导电层109-1、109-3、109-5,是仅栅极介电层203与所述编程隔离层315、317其中之一可能破裂。

139.请参考图4,在半导体元件1c中,多个第二栅极间隙子213可设置在所述第一栅极间隙子207的各侧壁上。举例来说,所述第一栅极间隙子207可由氧化硅、氮化硅或多晶硅所制。举例来说,所述第二栅极间隙子213可由氧化硅所制。由于所述第二栅极间隙子213的存在,是可最小化所述第一栅极间隙子207的一厚度,借此降低形成在栅极下导电层205与所述第一杂质区303、305之间的重叠电容(overlap capacitance)。

140.请参考图5,在半导体元件1d中,一高峰部(peak portion)111可设置在通道区301与栅极介电层203之间。高峰部111可具有一剖面轮廓,该剖面轮廓是为一三角形形状,并可具有彼此相交的一第一刻面111-1以及一第二刻面111-3。第一刻面111-1与第二刻面111-3之间的一角度α是可介于大约50度到大约60度之间。第一刻面111-1与第二刻面111-3可具有一结晶方向(crystal orientation)《111》。在一些实施例中,高峰部111可具有剖面轮廓,其是为一钻石形状、一五边形形状或具有多于五个侧边的一形状。举例来说,高峰部111可由下列材料所制:硅、锗、硅锗、硅碳、硅锗碳、镓、砷化镓、砷化铟、磷化铟或其他iv-iv族、iii-v族或ii-vi族半导体材料。

141.请参考图5,栅极介电层203可设置在高峰部111与通道区301上。栅极介电层203可包括一罩盖部(capping portion)203-1以及二平坦部203-3。罩盖部203-1可设置在第一刻面111-1与第二刻面111-3上。二平坦部203-3可分别对应连接到罩盖部203-1的两端。二平

坦部203-3可设置在通道区301上。二平坦部203-3的一厚度可大于或等于罩盖部203-1的一厚度。在一些实施例中,二平坦部203-3的厚度可大于罩盖层203-1的厚度。

142.在半导体元件1d的编程期间,因为电场集中在尖锐轮廓处,所以高峰部111的顶部(vertex)可为最脆弱部(most vulnerable part)。由于高峰部111的顶部可包含最高电场,所以罩盖部203-1可崩溃,以形成罩盖部203-1邻近高峰部111处的一破裂点(rupture point),且据此可造成一电阻的降低。因此,半导体元件1d是熔断(blown)及编程(programmed)。在编程期间,罩盖部203-1的破裂点的位置可轻易地限制在邻近高峰部111具有最高电场的顶部的位置处。因此,可提升半导体元件1d的可靠度。

143.请参考图6,在半导体元件1e中,一覆盖层(covering layer)113可设置在覆盖基底101、所述第一导电层307、309、所述第一栅极间隙子207以及栅极上导电层209。举例来说,覆盖层113可由氮化硅所制。所述第一接触点311、313可沿着覆盖层113设置,且分别设置在所述第一导电层307、309上。在接下来的所述半导体制程期间,覆盖层113可提供额外的保护给前述所述元件。

144.请参考图7,在半导体元件1f中,绝缘层103可界定一第一主动区501以及一第二主动区503在基底101中。通道区301与所述第一杂质区303、305可设置在第一主动区501中。一第二杂质区401可设置在第二主动区503中。第二杂质区401可掺杂有一掺杂物,例如磷、砷、锑或硼。在所述的实施例中,第二杂质区401掺杂有硼,并具有第一电子型态,其是与所述第一杂质区303、305相反。一第二导电层403可设置在第二杂质区401上。第二导电层403可具有与栅极上导电层209相同的厚度。第二导电层403可由与栅极上导电层209相同的材料所制。一第三导电层405可设置在第二导电层403上,并可电性耦接到第一接触点311。第三导电层405可由与所述第一接触点311、313相同的材料所制。

145.应当理解,文中所提到的功能或步骤是可发生不同于各图式中的顺序。举例来说,连续显示的两个图式实际上可以大致同时执行,或者是有时可以相反顺序执行,其是取决于所包含的功能或步骤。

146.应当理解,“正在形成(forming)”、“已经形成(formed)”以及“形成(form)”的术语,可表示并包括任何产生(creating)、构建(building)、图案化(patterning)、植入(implanting)或沉积(depositing)一元件(element)、一掺杂物(dopant)或一材料的方法。形成方法的例子可包括原子层沉积(atomic layer deposition)、化学气相沉积(chemical vapor deposition)、物理气相沉积(physical vapor deposition)、喷溅(sputtering)、旋转涂布(spin coating)、扩散(diffusing)、沉积(depositing)、生长(growing)、植入(implantation)、微影(photolithography)、干蚀刻以及湿蚀刻,但并不以此为限。

147.图8为依据本公开一实施例一种半导体元件1a的制备方法10的流程示意图。图9到图19为依据本公开一实施例该半导体元件1a的制备方法的一流程的剖视示意图。

148.请参考图8及图9,在步骤s11,可提供一基底101,且一绝缘层103与一通道区301可形成在基底101中。

149.请参考图9,可执行一系列的沉积制程,以沉积一垫氧化物层(在图9中未示)以及一垫氮化物层(在图9中未示)在基底101上。可执行一微影制程,以界定绝缘层103的位置。在微影制程之后,可执行一蚀刻制程,例如一非等向性干蚀刻制程,以沿着垫氧化物层、垫氮化物层以及基底101而形成多个沟槽。一隔离材料可沉积进入所述沟槽中。可执行一平坦

化制程,例如化学机械研磨,以移除多余填充材料,直到基底101的上表面暴露为止。接下来,可执行另一个微影-蚀刻制程,以界定通道区301的位置。可执行一植入(implantation)制程,以形成通道区301在基底101中。

150.请参考图8及图10,在步骤s13,一栅极结构201可形成在通道区301上。

151.请参考图10,栅极结构201可包括一栅极介电层203以及一栅极下导电层205。栅极介电层203可形成在通道区301上。栅极下导电层205可形成在栅极介电层203上。栅极介电层203以及栅极下导电层205可借由多个沉积制程以及接续的微影-蚀刻制程所形成。举例来说,所述沉积制程可为化学气相沉积或原子层沉积。

152.请参考图8及图11,在步骤s15,多个第一栅极间隙子207可形成在栅极结构201的各侧壁上。

153.请参考图11,一层隔离材料可共形沉积,以覆盖基底101与栅极结构201。接下来,可执行一蚀刻制程,例如一非等向性干蚀刻制程,以移除该层隔离材料的一部份,且同时形成多个第一栅极间隙子207在栅极下导电层205的各侧壁上以及在栅极介电层203的各侧壁上。举例来说,该层隔离材料可为氧化硅、氮化硅或类似物。应当理解,在所述第一栅极间隙子207形成之后,仍有通道区301的一些部分暴露。

154.请参考图8及图12,在步骤s17,第一杂质区303、305可形成在基底101中。

155.请参考图12,可执行一植入制程,以形成多个第一杂质区303、305在基底101中。可形成所述第一杂质区303、305以重叠通道区301的两端。所述第一杂质区303、305与通道区301可电性连接。

156.请参考图8及图13,在步骤s19,一栅极上导电层209可形成在栅极结构201与所述第一导电层307、309上,而栅极结构201与所述第一导电层307、309是可分别对应形成在所述第一杂质区303、305上。

157.请参考图13,一层导电材料可形成在基底101、所述第一栅极间隙子207与栅极下导电层205上。举例来说,该层导电材料可包含钛、镍、铂、钽或钴。接下来,可执行一热处理。在热处理期间,金属层的金属原子可与栅极下导电层205的硅原子进行化学反应,以形成栅极上导电层209以及所述第一导电层307、309。栅极上导电层209与所述第一导电层307、309可包含硅化钛、硅化镍、硅化镍铂、硅化钽或硅化钴。热处理可为一动态表面退火(dynamic surface annealing)制程。在热处理之后,可执行一清洗(cleaning)制程,以移除未反应的导电材料。清洗制程可使用蚀刻剂(etchant),例如过氧化氢(hydrogen peroxide)以及标准清洁1(standard clean 1,sc1)溶液。

158.请参考图8、图14及图15,在步骤s21,一第一隔离层105可形成在基底101上,且多个第一接触点311、313可形成在所述第一导电层307、309。

159.请参考图14,第一隔离层104可形成在如图13所例示的中间半导体元件上。可执行一平坦化制程,例如化学机械研磨,以提供一大致平坦表面给接下来的处理步骤。

160.请参考图15,可执行一微影制程,以界定所述第一接触点311、313的位置。可执行一蚀刻制程,例如一非等向性干蚀刻制程,以形成多个接触点开口在第一隔离层105中。所述第一导电层307、309的各上表面可经由所述接触点开口而暴露。一导电材料可借由一沉积制程而沉积进入所述接触点开口中,而导电材料是例如钨、钴、锆、钽、钛、铝、钌、铜、金属碳化物、金属氮化物或过渡金属铝化物。在沉积制程之后,可执行一平坦化制程,例如化学

机械研磨,以移除多余材料,提供一大致平坦表面给接下来的处理步骤,且同时形成所述第一接触点311、313。

161.请参考图8、图16及图17,在步骤s23,多个可编程隔离层315、317可分别对应形成在所述第一接触点311、313上。

162.请参考图16,可执行一回蚀制程,以凹陷所述第一接触点311、313,且同时形成多个凹陷601。在回蚀制程期间,所述第一接触点311、313对第一隔离层105的一蚀刻率,是可介于大约100:1到大约20:1之间。

163.请参考图17,可沉积一隔离材料以充填所述凹陷601。可执行一平坦化制程,例如化学机械研磨,直到第一隔离层105的上表面暴露为止,以提供大致平坦表面给接下来的处理步骤。举例来说,隔离材料可为氧化硅、氮化硅、氮氧化硅、氧化氮化硅、氧化铪(hafnium oxide)、氧化铪硅(hafnium silicon oxide)、氮氧化铪硅(hafnium silicon oxynitride)、氧化镧(lanthanum oxide)、氧化镧铝(lanthanum aluminum oxide)、氧化锆(zirconium oxide)、氧化硅锆(zirconium silicon oxide)、氮氧化硅锆(zirconium silicon oxynitride)、氧化铝或其组合。

164.请参考图8及图18,在步骤s25,一栅极通孔211可形成在栅极上导电层209上。

165.请参考图18,可执行一微影制程,以界定栅极通孔211的位置。可执行一蚀刻制程,例如一非等向性干蚀刻制程,以形成一通孔开口(via opening)在第一隔离层105中。栅极上导电层209的上表面可经由通孔开口而暴露。一导电材料可借由一沉积制程而沉积进入通孔开口中,而导电材料是例如钨、钴、锆、钽、钛、铝、钌、铜、金属碳化物(例如碳化钽、碳化钛、碳化钽镁(tantalum magnesium carbide))、金属氮化物(例如氮化钛)、过渡金属铝化物(transition metal aluminides)或其组合。在沉积制程之后,可执行一平坦化制程,例如化学机械研磨,以移除多余材料,提供一大致平坦表面给接下来的处理步骤,且同时形成栅极通孔211。

166.请参考图8及图19,在步骤s27,一第二隔离层107可形成在第一隔离层105,且一上导电层109可形成在第二隔离层107中。

167.请参考图19,第二隔离层107可形成在图18中所例示的中间半导体元件上。可执行一第一平坦化制程,例如化学机械研磨,以提供一大致平坦表面给接下来的处理步骤。可执行一微影制程,以界定上导电层109的位置。可执行一蚀刻制程,例如一非等向性干蚀刻制程,以形成一沟槽在第二隔离层107中。栅极通孔211与所述可编程隔离层315、317的各上表面可经由该沟槽而暴露。一导电材料是借由一沉积制程而可沉积进入该沟槽中,而导电材料是例如钨、钴、锆、钽、钛、铝、钌、铜、金属碳化物(例如碳化钽、碳化钛、碳化钽镁(tantalum magnesium carbide))、金属氮化物(例如氮化钛)、过渡金属铝化物(transition metal aluminides)。在沉积制程之后,可执行一第二平坦化制程,例如化学机械研磨,以移除多余材料,提供一大致平坦表面给接下来的处理步骤,且同时形成上导电层109。

168.本公开的一实施例提供一种半导体元件,具有一基底;一通道区,位在该基底中;多个第一杂质区,位在该基底中,且分别位在该通道区的两端上;一栅极介电层,位在该通道区上;一栅极下导电层,位在该栅极介电层上;多个第一接触点,分别位在所述第一杂质区上;所述可编程隔离层,分别位在所述第一接触点上;以及一上导电层,位在所述可编程

隔离层上,且电性连接到该栅极下导电层。

169.本公开的另一实施例提供一种半导体元件,具有一基底;一通道区,位在该基底中;多个第一杂质区,位在该基底中,且分别位在该通道区的两端上;一栅极介电层,位在该通道区上;一栅极下导电层,位在该栅极介电层上;一栅极通孔,位在该栅极下导电层上;多个第一接触点,分别位在所述第一杂质区上;多个可编程隔离层,分别位在所述第一接触点上;以及多个上导电层,分别位在所述可编程隔离层与该栅极通孔上。

170.本公开的另一实施例提供一种半导体元件的制备方法。该制备方法包括:提供一基底;形成一通道区在该基底中;形成一栅极介电层在该通道区上;形成一栅极下导电层在该栅极介电层上;形成多个第一杂质区在该通道区的两端上;形成多个第一接触点在所述第一杂质区上;形成多个可编程隔离层在所述接触点上;形成一栅极通孔在该栅极下导电层上;以及形成一上导电层在该栅极通孔与所述可编程隔离层上。

171.由于本公开该半导体元件的设计,当施加一编程电压(programming voltage)时,栅极介电层203及/或所述可编程隔离层315、317可能会破裂。因此,半导体元件1a可当成一可编程元件使用,并可使用在一芯片的一修复系统(repair system),以改善该芯片的良率。此外,由于高峰部111的存在,所以可改善编程该半导体元件1d的可靠度。

172.应当理解,术语“大约(about)”修饰成分(ingredient)、部件的一数量(quantity),或是本公开的反应物(reactant),其是表示可发生的数值数量上的变异(variation),举例来说,其是经由典型的测量以及液体处理程序(liquid handling procedures),而该液体处理程序用于制造浓缩(concentrates)或溶液(solutions)。再者,变异的发生可源自于应用在制造组成成分(compositions)或实施所述方法或其类似方式在测量程序中的非故意错误(inadvertent error)、在制造中的差异(differences)、来源(source)、或成分的纯度(purity)。在一方面,术语“大约(about)”意指报告数值的10%以内。在另一方面,术语“大约(about)”意指报告数值的5%以内。在再另一方面,术语“大约(about)”意指报告数值的10、9、8、7、6、5、4、3、2或1%以内。

173.虽然已详述本公开及其优点,然而应理解可进行各种变化、取代与替代而不脱离权利要求所定义的本公开的精神与范围。例如,可用不同的方法实施上述的许多制程,并且以其他制程或其组合替代上述的许多制程。

174.再者,本技术案的范围并不受限于说明书中所述的制程、机械、制造、物质组成物、手段、方法与步骤的特定实施例。该技艺的技术人士可自本公开的揭示内容理解可根据本公开而使用与本文所述的对应实施例具有相同功能或是达到实质上相同结果的现存或是未来发展的制程、机械、制造、物质组成物、手段、方法、或步骤。据此,此等制程、机械、制造、物质组成物、手段、方法、或步骤是包含于本技术案的权利要求内。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。