1.本发明属于半导体集成电路封装测试领域,涉及一种提高引线框架与塑封料结合力的方法。

背景技术:

2.在半导体集成电路引线框架类产品封装过程中,为了满足引线键合要求,一般会在铜引线框架表面镀银,芯片粘接在引线框架上后,用键合丝在芯片焊盘和引线框架镀银层上键合实现电气通路,最后塑封、电镀、激光打标及成型。

3.但是,由于银与塑封料的结合力较弱,在后续产品加工过程和使用过程中的应力以及塑封体本身应力的作用下,引线框架类塑封产品镀银层与塑封料之间易发生分层现象,并且,分层一旦发生会成为潮气入侵的通路或分层扩展的源头,最终导致塑封器件失效。

技术实现要素:

4.为了克服上述现有技术的缺点,本发明的目的在于提供一种提高引线框架与塑封料结合力的方法,解决了现有加工和使用过程中,容易出现分层进而导致器件失效的问题。

5.为了达到上述目的,本发明采用以下技术方案予以实现:

6.本发明公开了一种提高引线框架与塑封料结合力的方法,包括:

7.步骤一、在保护气体氛围中,通过电火花将陶瓷劈刀中的键合丝末端熔融成球体;步骤二、通过键合压力,将所得球体于引线框架载体表面镀银层或内引脚镀银层上压扁,使焊点成型,同时,通过超声电流处理,在焊点上产生促进键合的超声功率,使焊点与引线框架载体表面镀银层或内引脚镀银层发生界面物理化学反应,形成键合界面;步骤三、将球体与键合丝的连接处切断,在引线框架载体表面镀银层或内引脚镀银层上形成焊点。

8.优选地,重复步骤一至步骤三,在引线框架载体表面镀银层或内引脚镀银层上形成焊点阵列。

9.进一步优选地,焊点阵列的阵列方式可选正方形阵列或平行四边形阵列;在塑封产品固定分层位置局部地阵列焊点或不固定分层位置全部阵列焊点。

10.进一步优选地,完成焊点阵列之后,对引线框架载体进行去氧化处理。

11.优选地,步骤一中,通过电火花将陶瓷劈刀中的键合丝末端熔融成球体的电流时间参数包括:烧球电流为60~65ma、烧球时间为350~380μs。

12.优选地,步骤二中,键合压力为18~22g。

13.优选地,步骤二中,超声电流为75~85ma,时间为10~15ms。

14.优选地,键合丝为铜线。

15.优选地,所述引线框架载体或内引脚与塑封料结合力的方法通过k&s压焊机进行。

16.与现有技术相比,本发明具有以下有益效果:

17.本发明公开了一种提高引线框架与塑封料结合力的方法,在原先的塑封料与引线

框架载体表面镀银层的界面增加焊点阵列,进而有利于提高引线框架表面镀银层与塑封料结合力。其中,通过在引线框架表面镀银层增加焊点阵列,改变与塑封料之间的结合界面结构,提高结合界面的强度,能有效的改善铜引线框架与塑封料之间的分层问题,提高塑封可靠性。在阵列焊点过程中,可灵活选择阵列焊点的位置,针对性的在固定分层位置阵列焊点,焊点可避开芯片粘接区域和引线键合区域,使用灵活度高,适应性强。所述方法通过在引线框架载体或内引脚镀银层植上焊点来改善引线框架或内引脚与塑封料之间的结合界面。因此,本发明所述方法,解决了现有加工和使用过程中,容易出现分层进而导致器件失效的问题。

18.进一步地,键合丝为铜线,利用铜与塑封料的结合力要高于银与塑封料的结合力,且植球可以增大结合面积,最终减少分层的发生,提高产品的可靠性。

附图说明

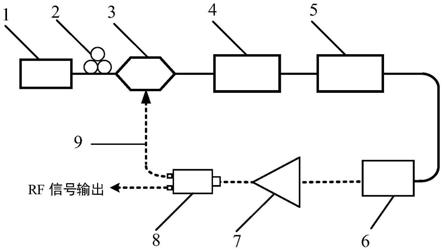

19.图1为本发明的烧球环节示意图;

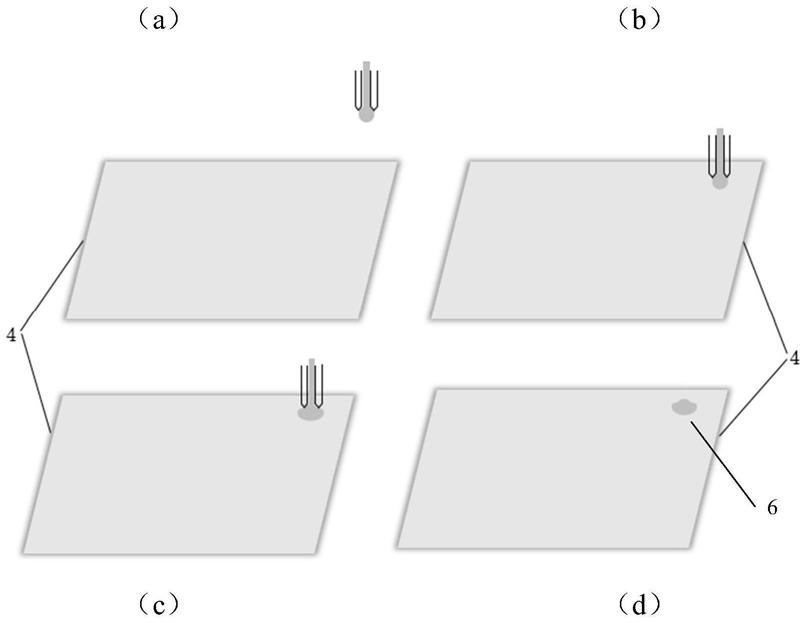

20.图2为本发明中完成铜焊球界面键合形成铜焊点的过程示意图;其中,(a)为烧球,(b)为定位,(c)为成型,(d)为切断;

21.图3为实施例1铜焊点阵列(引线框架载体局部正方形阵列)示意图;

22.图4为实施例1铜焊点阵列(引线框架载体局部平行四边形阵列)示意图;

23.图5为实施例2铜焊点阵列(引线框架载体全部)示意图;

24.图6为本发明的阵列铜焊球塑封体剖面示意图。

25.其中:1

‑

铜焊球,2

‑

劈刀,3

‑

键合丝,4

‑

铜引线框架载体,5

‑

芯片,6

‑

铜焊点。

具体实施方式

26.为了使本技术领域的人员更好地理解本发明方案,下面将结合本发明实施例中的附图,对本发明实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例仅仅是本发明一部分的实施例,而不是全部的实施例。基于本发明中的实施例,本领域普通技术人员在没有做出创造性劳动前提下所获得的所有其他实施例,都应当属于本发明保护的范围。

27.需要说明的是,本发明的说明书和权利要求书及上述附图中的术语“第一”、“第二”等是用于区别类似的对象,而不必用于描述特定的顺序或先后次序。应该理解这样使用的数据在适当情况下可以互换,以便这里描述的本发明的实施例能够以除了在这里图示或描述的那些以外的顺序实施。此外,术语“包括”和“具有”以及他们的任何变形,意图在于覆盖不排他的包含,例如,包含了一系列步骤或单元的过程、方法、系统、产品或设备不必限于清楚地列出的那些步骤或单元,而是可包括没有清楚地列出的或对于这些过程、方法、产品或设备固有的其它步骤或单元。

28.下面结合附图对本发明做进一步详细描述:

29.参见图1~图2可知,本发明公开的一种提高引线框架表面镀银层与塑封料结合力的方法,包括如下步骤:

30.步骤1,通过电火花,在保护气体氛围中一定电流时间下将陶瓷劈刀2的预留铜线(键合丝3)熔融成一个铜焊球1;

31.步骤2,采用陶瓷劈刀2,在一定的键合压力下在铜引线框架载体4表面镀银层上或内引脚镀银层将铜焊球1压扁,使铜焊点6成型;同时,施加一定的超声电流,在铜焊点6上产生促进键合的超声功率,使铜焊点6与铜引线框架载体4表面镀银层或内引脚镀银层发生界面物理化学反应,生成金属间化合物,形成键合界面;

32.步骤3,采用陶瓷劈刀2,将铜线(键合丝3)沿铜焊球1尾部切断,在铜引线框架载体4表面镀银层或内引脚镀银层上形成铜焊点6;

33.步骤4,重复步骤1、步骤2、步骤3、形成铜焊点6阵列,阵列的铜焊点6需预留芯片粘接和引线键合位置;其中,铜焊点6阵列可以增加塑封料与引线框架界面结合面积,并且用与塑封料结合力更强的铜来部分替代银与塑封料形成结合界面,最终可提高引线框架与塑封料的结合力。

34.步骤5,如铜引线框架载体4在形成铜焊点6过程中发生过度氧化,则可对铜引线框架载体4进行去氧化处理;

35.步骤6,进行芯片粘接、等离子清洗、引线键合、等离子清洗、塑封、电镀、激光打标及成型;

36.优选的,步骤1中,通过烧球得到铜焊球,烧球电流为60~65ma、烧球时间为350~380μs。

37.优选的,步骤2中,键合压力位18~22g。

38.优选的,步骤2中,进行界面键合的超声电流为65~75ma,键合时间为10~15ms。

39.优选的,步骤3中,铜焊点6阵列的阵列方式可选正方形阵列或平行四边形阵列。其中,可形成的60

°

角的菱形阵列圆的面积占比是最大的,作为最密平行四边形阵列。

40.优选的,步骤3中,可在塑封产品固定分层位置局部地或不固定分层位置阵列铜焊点6。

41.优选的,步骤1~步骤4所述的过程在k&s压焊机上进行。

42.参见图3,可知本发明应用时,可在引线框架载体表面镀银层局部阵列正方形阵列焊点以解决塑封产品固定分层。

43.参见图4,可知本发明应用时,可在引线框架载体表面镀银层局部阵列平行四边形阵列焊点以解决塑封产品固定分层。

44.参见图5,可知本发明应用时,可在引线框架载体表面镀银层预留芯片位置后全部阵列焊点以解决塑封产品引线框架载体表面非固定位置分层。

45.参见图6,可知本发明中,由于焊点的存在,塑封料与引线框架界面结合面积增加,可有效提升塑封料与引线框架界面结合力。

46.下面结合具体实施例对本发明做进一步详细描述:

47.实施例1:

48.针对某型号lqfp48l(其中芯片粘接载体尺寸5.2*5.2mm2,芯片尺寸3.2*4.2mm2,芯片左上角载体易分层)产品,利用本发明,具体实施情况如下:

49.步骤1:在铜引线框架载体4左上角阵列上铜焊点6,铜焊点6间距80μs;本实施例制得的为正方形阵列。

50.具体地,通过电火花将陶瓷劈刀中的键合丝末端熔融成球体的电流时间参数为烧球电流60ma,烧球时间350μs;键合过程中的键合压力的参数为18g;超声电流处理的操作参

数为超声电流65ma,超声时间10ms。

51.步骤2:将待封装的芯片粘接至铜引线框架载体4芯片粘接载体指定位置;

52.步骤3:对待键合的电路进行等离子清洗,之后根据键合图进行引线键合;

53.步骤4:对键合后的电路进行等离子清洗,使用塑封机用塑封料进行塑封,形成塑封体。

54.步骤5:将塑封体在烘箱中175℃固化8

‑

9小时,并对塑封体依次进行切筋、电镀锡、激光打标、成型,得到成品塑封件。

55.实施例2:

56.针对某型号lqfp44l(其中芯片粘接载体尺寸5.2*5.2mm2,芯片尺寸5.2*5.2mm2,芯片左上角载体易分层产品),利用本发明,具体实施情况如下:

57.步骤1:在载体预留出芯片粘接位置后全部阵列上铜焊点6,铜焊点6间距100μs;本实施例通过在塑封产品固定分层位置局部地阵列铜焊点6,制得的为平行四边形阵列。

58.具体地,通过电火花将陶瓷劈刀中的键合丝末端熔融成球体的电流时间参数为烧球电流62ma,烧球时间360μs;键合过程中的键合压力的参数为19g;超声电流处理的操作参数为超声电流68ma,超声时间12ms。

59.步骤2:将待封装的芯片粘接至铜引线框架载体4芯片粘接载体指定位置;

60.步骤3:对待键合的电路进行等离子清洗,之后根据键合图进行引线键合;

61.步骤4:对键合后的电路进行等离子清洗,使用塑封机用塑封料进行塑封,形成塑封体。

62.步骤5:将塑封体在烘箱中175℃固化8

‑

9小时,并对塑封体依次进行电镀锡、激光打标、切筋成型,得到成品塑封件。

63.实施例3:

64.针对某型号sop8l(其中芯片粘接载体尺寸2.4*3.3mm2,芯片尺寸1.76*1.46mm2)产品,利用本发明,具体实施情况如下:

65.步骤1:在载体预留出芯片粘接位置后全部阵列上铜焊点6,铜焊点6间距100μs;本实施例制得的为正方形阵列。

66.具体地,通过电火花将陶瓷劈刀中的键合丝末端熔融成球体的电流时间参数为烧球电流65ma,烧球时间380μs;键合过程中的键合压力的参数为22g;超声电流处理的操作参数为超声电流75ma,超声时间15ms。

67.步骤2:将待封装的芯片粘接至铜引线框架载体4芯片粘接载体指定位置;

68.步骤3:对待键合的电路进行等离子清洗,之后根据键合图进行引线键合;

69.步骤4:对键合后的电路进行等离子清洗,使用塑封机用塑封料进行塑封,形成塑封体。

70.步骤5:将塑封体在烘箱中175℃固化8

‑

9小时,并对塑封体依次进行电镀锡、激光打标、切筋成型,得到成品塑封件。

71.以上内容仅为说明本发明的技术思想,不能以此限定本发明的保护范围,凡是按照本发明提出的技术思想,在技术方案基础上所做的任何改动,均落入本发明权利要求书的保护范围之内。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。