1.本发明是有关于一种蚀刻方法,且特别关于一种制作半导体装置的沟槽结构的干式蚀刻方法。

背景技术:

2.半导体工业正不断的蓬勃发展当中。半导体设计和材料的技术进步让半导体装置具有更小、更复杂的电路。半导体装置的功能密度通常增加而尺寸缩小,可以提高生产效率及降低成本。

3.半导体装置的功能受到半导体芯片面积的限制,而随着半导体技术的发展,越来越多装置采用三维堆栈技术来增加组件的密度。然而,三维堆栈技术增加了半导体装置制程的复杂度,并更难维持半导体装置的制程质量及稳定度,且会影响产量。对于三维集成电路的半导体芯片来说,系要求较高的沟槽宽高比(aspect ratio),传统技术中,通常采用bosch公司开发的深反应性离子蚀刻(deep reactive-ion etching,drie)制程来制作沟槽。然而,现有的drie制程,仍有沟槽侧壁粗糙度偏高的问题,从而影响半导体芯片的电性和机械性质。因此,在半导体装置的制程中进行对应的发展,以提升制程质量及稳定度是亟需解决的问题。

[0004]“先前技术”段落只是用来帮助了解本

技术实现要素:

,因此在“先前技术”段落所揭露的内容可能包含一些没有构成所属技术领域中具有通常知识者所知道的习知技术。在“先前技术”段落所揭露的内容,不代表该内容或者本发明一个或多个实施例所要解决的问题,在本发明申请前已被所属技术领域中具有通常知识者所知晓或认知

发明内容

[0005]

本发明提供一种制作半导体装置的沟槽结构的干式蚀刻方法,可以提高半导体装置的质量及稳定度,并提高产量。

[0006]

本发明的其他目的和优点可以从本发明所揭露的技术特征中得到进一步的了解。

[0007]

本发明的制作半导体装置的沟槽结构的干式蚀刻方法包括以下步骤:步骤1:提供一半导体基材,该半导体基材上设置有图案化的一光阻层且放置于一反应腔室,该半导体基材具有被该光阻层遮蔽的一保留区域以及露出的一待蚀刻区域,该反应腔室包括一上电极以及一下电极。步骤2:引入一第一蚀刻气体至该反应腔室以进行一第一蚀刻方法,而移除部分的该待蚀刻区域而形成一沟槽,该沟槽具有一第一深度,该第一蚀刻气体包括六氟化硫、氧气、氦、三氟化氮以及一第一有机硅化物。步骤3:引入一第二蚀刻气体至该反应腔室以进行一第二蚀刻方法,而将该沟槽从该第一深度往下蚀刻至一第二深度,该第二蚀刻气体包括六氟化硫、氧气、氦以及一第二有机硅化物,其中,该第二蚀刻方法中的该反应腔室的压力大于该第一蚀刻方法中的该反应腔室的压力。步骤4:引入一第三蚀刻气体至该反应腔室以进行一第三蚀刻方法,该第三蚀刻气体包括氢溴酸、氧气以及氦。其中该反应腔室内的每秒温度变化不超过 /-1%,该反应腔室的每秒压力变化不超过 /-5%,该上电极或

该下电极的每秒功率变化不超过 /-1%。

[0008]

在本发明的一实施例中,在上述该第一蚀刻方法中,六氟化硫的流速介于10sccm至2000sccm之间,氧气的流速介于10sccm至500sccm之间,氦的流速介于10sccm至500sccm之间,三氟化氮的流速介于10sccm至300sccm之间,该第一有机硅化物的流速介于50sccm至200sccm之间。

[0009]

在本发明的一实施例中,在上述该第一蚀刻方法中,六氟化硫相对该第一蚀刻气体的体积百分比为30%,氧气相对该第一蚀刻气体的体积百分比为20%,氦相对该第一蚀刻气体的体积百分比为20%,三氟化氮相对该第一蚀刻气体的体积百分比为10%,该第一有机硅化物相对该第一蚀刻气体的体积百分比为20%。

[0010]

在本发明的一实施例中,在上述该第一蚀刻方法中,该上电极的功率为3000w,该下电极的功率为500w。

[0011]

在本发明的一实施例中,在上述该第二蚀刻方法中,六氟化硫的流速介于10sccm至2000sccm之间,氧气的流速介于10sccm至500sccm之间,氦的流速介于10sccm至500sccm之间,该第二有机硅化物的流速介于50sccm至200sccm之间。

[0012]

在本发明的一实施例中,在上述该第二蚀刻方法中,六氟化硫相对该第二蚀刻气体的体积百分比为20%,氧气相对该第二蚀刻气体的体积百分比为20%,氦相对该第二蚀刻气体的体积百分比为40%,该第二有机硅化物相对该第二蚀刻气体的体积百分比为20%。

[0013]

在本发明的一实施例中,在上述该第二蚀刻方法中,该上电极的功率为7000w,该下电极的功率为2000w。

[0014]

在本发明的一实施例中,在上述该第三蚀刻方法中,氢溴酸的流速介于10sccm至2000sccm之间,氧气的流速介于10sccm至500sccm之间,氦的流速介于10sccm至500sccm之间。

[0015]

在本发明的一实施例中,在上述该第三蚀刻方法中,氢溴酸相对该第三蚀刻气体的体积百分比为60%,氧气相对该第三蚀刻气体的体积百分比为10%,氦相对该第三蚀刻气体的体积百分比为30%。

[0016]

在本发明的一实施例中,在上述该第三蚀刻方法中,该上电极的功率为1000w,该下电极的功率为100w。

[0017]

基于上述,本发明提供的制作半导体装置的沟槽结构的干式蚀刻方法,透过第一蚀刻气体、第二蚀刻气体、第三蚀刻气体分别进行第一蚀刻方法、第二蚀刻方法、第三蚀刻方法来制造具有深沟槽的半导体结构,可以提升制程质量及稳定度,更可以提高产量。

[0018]

为让本发明的上述特征和优点能更明显易懂,下文特举实施例,并配合所附图式作详细说明如下。

附图说明

[0019]

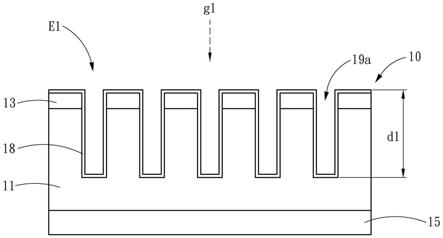

图1是本发明一实施例的制作半导体装置的沟槽结构的干式蚀刻装置的示意图。

[0020]

图2a、图2b、图2c、图2d是根据一些实施例所绘示出制作半导体装置的沟槽结构的干式蚀刻方法的中间阶段的剖面图。

具体实施方式

[0021]

有关本发明之前述及其他技术内容、特点与功效,在以下配合参考图式之一较佳实施例的详细说明中,将可清楚的呈现。以下实施例中所提到的方向用语,例如:上、下、左、右、前或后等,仅是参考附加图式的方向。因此,使用的方向用语是用来说明并非用来限制本发明。本文中,「约」及「大约」之用语通常表示在一给定值或范围的10%内、或5%之内、或3%之内、或2%之内、或1%之内、或0.5%之内。在此给定的数量为大约的数量,亦即在没有特定说明「约」或「大约」的情况下,仍可隐含「约」或「大约」之含义。

[0022]

请参照图1,图1是本发明一实施例的制作半导体装置10的沟槽结构的干式蚀刻装置17的示意图。

[0023]

请同时参照图2a、图2b、图2c、图2d,图2a、图2b、图2c、图2d是根据一些实施例所绘示出制作半导体装置10的沟槽结构的干式蚀刻方法的中间阶段的剖面图。请先参照图2a,本实施例的制作半导体装置10的沟槽结构的干式蚀刻方法包括以下步骤:

[0024]

步骤1:提供一半导体基材11。该半导体基材11上设置有图案化的一光阻层13且放置于一反应腔室171(如图1所示)。该半导体基材11具有被该光阻层13遮蔽的一保留区域111以及露出的一待蚀刻区域113。该反应腔室171包括一上电极173以及一下电极175。该半导体基材11的材料例如包括硅。该反应腔室171设置于该干式蚀刻装置17的内部(如图1所示)。

[0025]

此外,该半导体装置10可以包括一氧化物层15。该氧化物层15设置于该半导体基材11的下方。

[0026]

为了方便说明,图2a、图2b、图2c、图2d并不绘制该干式蚀刻装置17。接着,请参照图2b。

[0027]

步骤2:引入一第一蚀刻气体g1至该反应腔室171以进行一第一蚀刻方法e1,而移除部分的该待蚀刻区域113而形成一沟槽19a。该沟槽19a具有一第一深度d1。在本实施例中,该第一蚀刻气体g1包括六氟化硫(sf6)、氧气(o2)、氦(he)、三氟化氮(nf3)及一第一有机硅化物。

[0028]

步骤3:如图2c所示,引入一第二蚀刻气体g2至该反应腔室171以进行一第二蚀刻方法e2,而将该沟槽19a从该第一深度d1往下蚀刻至一第二深度d2。该第二蚀刻方法e2还蚀刻除去该沟槽19a底部的氧化物,而形成沟槽19b。该沟槽19b部分披覆保护层18a。在本实施例中,该第二蚀刻气体g2包括六氟化硫(sf6)、氧气(o2)、氦(he)以及一第二有机硅化物。

[0029]

步骤4:如图2d所示,引入一第三蚀刻气体g3至该反应腔室171以进行一第三蚀刻方法e3。该第三蚀刻气体包括氢溴酸(hbr)、氧气(o2)以及氦(he)。在该第三蚀刻方法e3中,将该沟槽19b从该第二深度d2往下蚀刻至该氧化物层15,以形成沟槽19c。该第三蚀刻气体g3不会蚀刻该氧化物层15。

[0030]

在本实施例中,该反应腔室171内的每秒温度变化不超过 /-1%。

[0031]

在本实施例中,该反应腔室171的每秒压力变化不超过 /-5%。

[0032]

在本实施例中,该上电极173或该下电极175的每秒功率变化不超过 /-1%。

[0033]

如图1所示,具体而言,该干式蚀刻装置17可以包括多个槽体t1、t2、t3、t4及管线p。该些槽体t1、t2、t3、t4用于储存各蚀刻方法所需的气体,而该管线p用于将各蚀刻方法所需的气体传输至该反应腔室171。本发明并不限制槽体的数量与蚀刻气体的储存位置及储

存方式。该上电极173及该下电极175用于与各蚀刻气体作用以进行蚀刻,其细节并不赘述。该第一有机硅化物及/该第二有机硅化物例如可以二氯硅烷(h2sicl2)气体来实现。

[0034]

详细来说,在步骤1中。该半导体基材11暴露的该待蚀刻区域113会产生氧化物(native oxide)(未图示)。在步骤2的该第一蚀刻方法e1中,必须使用该第一蚀刻气体g1进行蚀刻才能将此氧化物分解,以继续进行蚀刻。六氟化硫离子和自由基可以蚀刻该半导体基材11的硅。如图2b所示的保护层18,该第一有机硅化物与氧生成氧化硅(sio2)以保护该光阻层13的顶部和侧壁。氧与硅及氟反应生成氟氧化硅(sioxfy)聚合物,以保护该沟槽19a的侧壁,避免受到六氟化硫离子和自由基的侵蚀。三氟化氮用于蚀刻该光阻层13上的氧化聚合物及该沟槽19a的侧壁上的氟氧化硅聚合物,以控制该沟槽19a的轮廓。

[0035]

在图2a中,该半导体基材11的厚度例如是大约600μm,该光阻层13的厚度例如是大约20μm。在图2b中,该沟槽19a的宽度例如是大约5μm,该保护层18的厚度例如是大约30nm。

[0036]

在本实施例中,上述的该第二蚀刻方法e2(步骤3)中的该反应腔室171的压力大于该第一蚀刻方法e1(步骤2)中的该反应腔室171的压力。

[0037]

在本实施例中,该第一蚀刻方法e1(步骤2)中,六氟化硫的流速介于10sccm至2000sccm之间,氧气的流速介于10sccm至500sccm之间,氦的流速介于10sccm至500sccm之间,三氟化氮的流速介于10sccm至300sccm之间,该第一有机硅化物的流速介于50sccm至200sccm之间。

[0038]

在本实施例中,在该第一蚀刻方法e1(步骤2)中,六氟化硫相对该第一蚀刻气体g1的体积百分比为30%,氧气相对该第一蚀刻气体g1的体积百分比为20%,氦相对该第一蚀刻气体g1的体积百分比为20%,三氟化氮相对该第一蚀刻气体g1的体积百分比为10%,该第一有机硅化物相对该第一蚀刻气体g1的体积百分比为20%。

[0039]

在本实施例中,在该第一蚀刻方法e1(步骤2)中,该上电极173的功率大约为3000w,该下电极175的功率大约为500w。

[0040]

此外,在该第一蚀刻方法e1中,为了增加蚀刻的深度,该反应腔室171的压力必须低至小于100mt(milli-torr)。在该第一蚀刻方法e1中,该第一蚀刻方法e1的蚀刻时间必须大于30秒,以降低bosch深反应性离子蚀刻中气体流动的不稳定性,并降低蚀刻方法中意外的蚀刻停止现象。

[0041]

在本实施例中,在该第一蚀刻方法e1之后,该光阻层13的厚度仍然可以保留蚀刻前的厚度的2/3~1/2。如前所述,可以沉积聚合物以保护该光阻层13和该沟槽19a的侧壁。该反应腔室171的压力必须大于150mt。该上电极173的功率在7000w以下,该下电极175的功率在50w以下。此时气体的比例约包括40vol.%的氧及60vol.%的si有机化合物。

[0042]

详细来说,在步骤3的该第二蚀刻方法e2中,氦可以降低六氟化硫的浓稠度,可以降低蚀刻速率,并降低沟槽底部的聚合物生长。

[0043]

在本实施例中,在该第二蚀刻方法e2(步骤3)中,六氟化硫的流速介于10sccm至2000sccm之间,氧气的流速介于10sccm至500sccm之间,氦的流速介于10sccm至500sccm之间,该第二有机硅化物的流速介于50sccm至200sccm之间。

[0044]

在本实施例中,在该第二蚀刻方法e2(步骤3)中,六氟化硫相对该第二蚀刻气体g2的体积百分比为20%,氧气相对该第二蚀刻气体g2的体积百分比为20%,氦相对该第二蚀刻气体g2的体积百分比为40%,该第二有机硅化物相对该第二蚀刻气体g2的体积百分比为

20%。

[0045]

在本实施例中,在该第二蚀刻方法e2(步骤3)中,该上电极173的功率大约为7000w,该下电极175的功率大约为2000w。

[0046]

在本实施例中,由于该第二蚀刻气体g2会对该氧化物层15的材料进行蚀刻,因此必须进行该第三蚀刻方法e3。该第三蚀刻气体g3不会对该氧化物层15的材料进行蚀刻。

[0047]

详细来说,步骤4的该第三蚀刻方法e3是一过蚀刻(over-etch)方法。该第三蚀刻方法e3使用氢溴酸、氧气及氦来沉积聚合物(未图示),以保护该光阻层13及该沟槽19c。氢溴酸用于蚀刻硅,还可以制造氢(h2)及溴化硅(sioxbry)。溴化硅可以沉积以保护下方的该氧化物层15及该光阻层13。氧、硅及氢可以形成sioh聚合物(未图示)以保护该沟槽19c的侧壁。

[0048]

在本实施例中,在该第三蚀刻方法e3(步骤4)中,氢溴酸的流速介于10sccm至2000sccm之间,氧气的流速介于10sccm至500sccm之间,氦的流速介于10sccm至500sccm之间。

[0049]

在本实施例中,在该第三蚀刻方法e3(步骤4)中,氢溴酸相对该第三蚀刻气体g3的体积百分比为60%,氧气相对该第三蚀刻气体g3的体积百分比为10%,氦相对该第三蚀刻气体g3的体积百分比为30%。

[0050]

在本实施例中,在该第三蚀刻方法e3(步骤4)中,该上电极173的功率大约为1000w,该下电极175的功率大约为100w。

[0051]

本实施例的制作半导体装置10的沟槽结构的干式蚀刻方法,透过调整温度及/或功率参数、应用特定蚀刻气体、调整蚀刻参数来制造具有深沟槽(沟槽19c)的半导体结构。从而底部的该氧化物层15上不易产生微沟槽,在该沟槽19c上不会产生弯曲(necking/bowing)。可以改善该沟槽19c的侧壁的粗糙度、避免该氧化物层15产生微沟槽,更可以提高该半导体装置10的产量。

[0052]

本实施例的制作半导体装置10的沟槽结构的干式蚀刻方法中,该第一蚀刻方法e1、该第二蚀刻方法e2、该第三蚀刻方法e3具有足够的反应时间,透过严格的温度、压力、功率控制,可以大幅改善该沟槽19c的侧壁的粗糙度及该沟槽19c的轮廓。本实施例的该沟槽19c的侧壁粗糙度(roughness)可以小于10nm,宽高比(aspect ratio)可以大于100,且该沟槽19c的底部轮廓角可以是89.7度~90.3度间。而目前现有技术产生的沟槽(未图示)的侧壁粗糙度通常大于100nm,宽高比通常在30-60间,且沟槽的底部轮廓角通常是在88度~92度间。

[0053]

本实施例具有高宽高比的该沟槽19c的该半导体装置10例如可以应用于微机电系统(microelectromechanical systems,mems)。

[0054]

综上所述,本发明实施例的制作半导体装置的沟槽结构的干式蚀刻方法,透过第一蚀刻气体、第二蚀刻气体、第三蚀刻气体分别进行第一蚀刻方法、第二蚀刻方法、第三蚀刻方法来制造具有深沟槽的半导体结构,可以提升制程质量及稳定度,更可以提高产量。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。