技术特征:

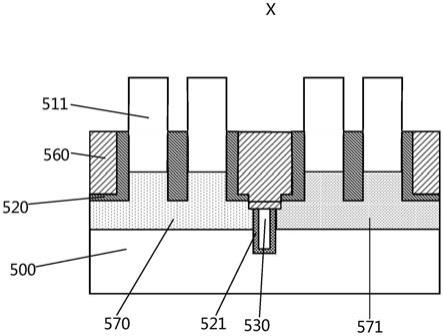

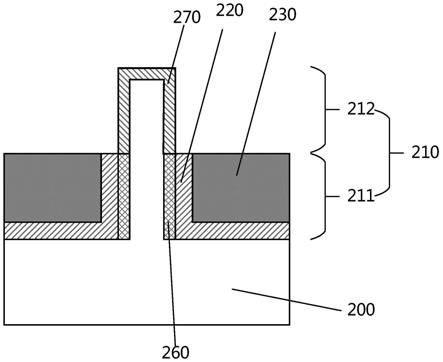

1.一种半导体结构的形成方法,其特征在于,包括:提供半导体衬底,所述半导体衬底上形成有若干鳍结构,在所述半导体衬底中形成有沟槽,所述沟槽分隔相邻的有源区;在所述沟槽顶部的表面生长封闭层,所述封闭层封闭所述沟槽顶部。2.如权利要求1所述半导体结构的形成方法,其特征在于,所述半导体衬底和所述鳍结构上形成有第一介质层,所述第一介质层暴露所述鳍结构的部分底部表面,所述半导体结构的形成方法还包括:形成第二介质层,所述第二介质层覆盖所述沟槽侧壁和所述第一介质层暴露的鳍结构表面;去除所述沟槽顶部侧壁的部分第二介质层、与所述沟槽顶部邻接的半导体衬底表面的部分第一介质层,以及所述第一介质层暴露的鳍结构表面覆盖的第二介质层。3.如权利要求2所述半导体结构的形成方法,其特征在于,去除所述沟槽顶部侧壁的部分第二介质层、与所述沟槽顶部邻接的半导体衬底表面的部分第一介质层,以及所述第一介质层暴露的鳍结构表面覆盖的第二介质层的方法包括:在所述第一介质层上和所述沟槽中形成硬掩膜层,所述硬掩膜层填满所述沟槽;回刻蚀所述硬掩膜层使所述硬掩膜层顶面低于所述沟槽顶面;刻蚀去除高于所述硬掩膜层顶面的部分所述第二介质层以及与所述沟槽邻接的半导体衬底表面的部分第一介质层;去除所述硬掩膜层。4.如权利要求3所述半导体结构的形成方法,其特征在于,回刻蚀所述硬掩膜层使所述硬掩膜层顶面低于所述沟槽顶面后,所述硬掩膜层低于所述沟槽的部分的深度占所述沟槽深度的10%至20%。5.如权利要求3所述半导体结构的形成方法,其特征在于,刻蚀去除高于所述硬掩膜层顶面的部分所述第二介质层以及与所述沟槽邻接的半导体衬底表面的部分第一介质层的方法为各向同性刻蚀。6.如权利要求2所述半导体结构的形成方法,其特征在于,在所述沟槽顶部侧壁、与所述沟槽顶部邻接的半导体衬底表面以及所述第一介质层暴露的鳍结构表面形成封闭层,所述封闭层封闭所述沟槽顶部的方法包括:在所述沟槽顶部侧壁、与所述沟槽顶部邻接的半导体衬底表面以及所述第一介质层暴露的鳍结构表面外延生长外延层,至所述外延层封闭所述沟槽顶部;减薄所述外延层形成所述封闭层。7.如权利要求6所述半导体结构的形成方法,其特征在于,减薄所述外延层形成所述封闭层的方法包括:采用各向异性的干法刻蚀工艺减薄所述外延层;采用灰化以及湿法刻蚀工艺进一步减薄所述外延层。8.如权利要求1所述半导体结构的形成方法,其特征在于,所述封闭层的厚度为1纳米至5纳米。9.如权利要求2所述半导体结构的形成方法,其特征在于,还包括:采用fcvd工艺在所述第一介质层上以及封闭层上形成隔离材料层,所述隔离材料层填满所述若干鳍结构之间的空间并且顶部表面高于所述第一介质层的顶部表面;

固化所述隔离材料层并氧化所述封闭层。10.如权利要求9所述半导体结构的形成方法,其特征在于,固化所述隔离材料层并氧化所述外延层的方法包括:采用蒸汽退火工艺处理所述隔离材料层并氧化所述外延层;采用干法退火工艺处理所述隔离材料层。11.如权利要求9所述半导体结构的形成方法,其特征在于,所述方法还包括:平坦化所述隔离材料层以及第一介质层至暴露所述鳍结构的顶部,其中,所述鳍结构包括位于半导体衬底上的鳍以及位于所述鳍上的掩膜层;分别在不同有源区进行掺杂离子注入;去除所述掩膜层;刻蚀所述隔离材料层和第一介质层的一部分,形成环绕所述鳍底部的隔离结构。12.如权利要求2所述半导体结构的形成方法,其特征在于,所述半导体衬底中形成所述沟槽的方法包括:在所述第一介质层表面依次形成牺牲层、抗反射层和图案化的光阻层,所述图案化的光阻层定义所述沟槽的位置;以所述图案化的光阻层为掩膜刻蚀所述抗反射层、所述牺牲层和所述第一介质层,在所述第一介质层中形成开口;以所述第一介质层为掩膜刻蚀所述半导体衬底形成所述沟槽;去除所述牺牲层、抗反射层和图案化的光阻层。13.如权利要求2所述半导体结构的形成方法,其特征在于,采用原位蒸汽生成工艺形成所述第二介质层。14.一种半导体结构,其特征在于,包括:半导体衬底,所述半导体衬底上形成有若干鳍;沟槽,位于所述半导体衬底中,分隔相邻的有源区;隔离结构,位于所述半导体衬底上并环绕所述鳍底部,其中,所述隔离结构不填充所述沟槽并且封闭所述沟槽的顶部。

技术总结

本申请提供半导体结构及其形成方法,所述半导体的结构包括:半导体衬底,所述半导体衬底上形成有若干鳍;沟槽,位于所述半导体衬底中,分隔相邻的有源区;隔离结构,位于所述半导体衬底上并环绕所述鳍底部,其中,所述隔离结构不填充所述沟槽并且封闭所述沟槽的顶部。本申请所述的半导体结构及其形成方法,在相邻的有源区之间形成被空气填充的沟槽,利用所述沟槽隔离相邻的有源区,可以减少相邻有源区之间的漏电。的漏电。的漏电。

技术研发人员:任飞 徐娟

受保护的技术使用者:中芯国际集成电路制造(北京)有限公司

技术研发日:2020.06.03

技术公布日:2021/12/6

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。