具有极窄带通数字滤波的模数转换电路

1.关于联邦资助的研究或开发的声明

2.不适用。

3.在光盘上提交的材料的通过引用并入

4.不适用。

技术领域

5.本发明总体上涉及数据通信系统,并且更具体地涉及感测数据收集和/或通信。

背景技术:

6.传感器用于范围广泛的各种应用中,从家庭自动化到工业系统、到医疗保健、到运输等等。例如,传感器被放置在车身、汽车、飞机、船、轮船、卡车、摩托车、手机、电视、触摸屏、工厂、电器、电机、收银台等中以用于各种应用。

7.通常,传感器将物理量转换成电或光信号。例如,传感器将物理现象,如生物条件、化学条件、电条件、电磁条件、温度、磁条件、机械运动(位置、速度、加速度、力、压力)、光学条件和/或放射性条件,转换为电信号。

8.传感器包括换能器,其用于将一种形式的能量(例如,力)转换为另一种形式的能量(例如,电信号)。有多种传感器可以支持传感器的各种应用。例如,换能器是电容器、压电换能器、压阻换能器、热换能器、热电偶、光电导换能器,例如光敏电阻、光电二极管和/或光电晶体管。

9.传感器电路耦合到传感器以向传感器提供电力并从传感器接收代表物理现象的信号。传感器电路包括至少三个与传感器的电连接:一个用于电源;另一个用于公共电压参考(例如,接地);第三个用于接收代表物理现象的信号。随着物理现象从一个极端变化到另一个极端(对于感测物理现象的范围),代表物理现象的信号将随电源电压变化到地。

10.传感器电路将接收到的传感器信号提供给一个或多个计算装置以进行处理。已知计算装置用于传送数据、处理数据和/或存储数据。计算装置可以是支持数百万网络搜索、股票交易、或每小时在线购买的蜂窝电话、膝上型电脑、平板电脑、个人计算机(pc)、工作站、视频游戏装置、服务器和/或数据中心。

11.计算装置为各种应用处理传感器信号。例如,计算装置处理传感器信号以确定运输期间冷藏卡车中各种物品的温度。作为另一实施例,计算装置处理传感器信号以确定触摸屏上的触摸。作为又一实施例,计算装置处理传感器信号以确定产品生产线中的各种数据点。

附图说明

12.图1是根据本发明的通信系统的实施方案的示意框图;

13.图2是根据本发明的计算装置的实施方案的示意框图;

14.图3是根据本发明的计算装置的另一个实施方案的示意框图;

15.图4是根据本发明的计算装置的另一个实施方案的示意框图;

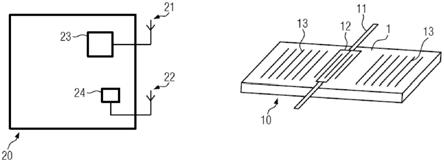

16.图5a是根据本发明的计算子系统的示意性绘图;

17.图5b是根据本发明的计算子系统的另一个实施方案的示意框图;

18.图5c是根据本发明的计算子系统的另一个实施方案的示意框图;

19.图5d是根据本发明的计算子系统的另一个实施方案的示意框图;

20.图5e是根据本发明的计算子系统的另一个实施方案的示意框图;

21.图6是根据本发明的驱动感测电路的实施方案的示意框图;

22.图6a是根据本发明的驱动感测电路的另一个实施方案的示意框图;

23.图7是根据本发明的功率信号图的实施例;

24.图8是根据本发明的传感器图的实施例;

25.图9是根据本发明的功率信号图的另一个实施例的示意框图;

26.图10是根据本发明的功率信号图的另一个实施例的示意框图;

27.图11是根据本发明的功率信号图的另一个实施例的示意框图;

28.图11a是根据本发明的功率信号图的另一个实施例的示意框图;

29.图12是根据本发明的功率信号变化检测电路的实施方案的示意框图;

30.图13是根据本发明的驱动感测电路的另一个实施方案的示意框图;

31.图14是根据本发明的具有编程参考信号发生器的驱动感测电路的实施例的示意框图;

32.图15是根据本发明的数据感测电路的实施方案的示意框图;

33.图16是根据本发明的数据感测电路的另一个实施方案的示意框图;

34.图17是根据本发明的数据电路的实施方案的示意框图;

35.图18是根据本发明的模数转换电路的实施方案的示意框图;

36.图19是根据本发明的模数转换电路的另一个实施方案的示意框图;

37.图20a

‑

20b是根据本发明绘制条件对电容的示例图;

38.图21是根据本发明绘制输入的阻抗对频率的示例图;

39.图22是根据本发明的影响值的实施例;

40.图23是根据本发明的西格玛

‑

德尔塔模数(adc)电路的实施方案的示意框图;

41.图24是根据本发明的西格玛

‑

德尔塔过采样调制器的量化噪声的实施例;

42.图25是根据本发明的模数转换电路的不同级的示例输出的示意框图;

43.图26是根据本发明对模拟信号进行采样以产生数字化信号的实施例;

44.图27是根据本发明实现乘法累加函数的数字滤波器的示意框图;

45.图28是根据本发明实现乘法累加函数的数字滤波器的示意框图;

46.图29是根据本发明的数字化信号的实施例;

47.图30是根据本发明产生数字滤波输出的实施例;

48.图31是根据本发明的数字抽取滤波电路的实施方案的示意框图;

49.图32是根据本发明的抗混叠滤波器的示例频率响应h(z);

50.图33是根据本发明的抗混叠滤波器的实施方案的示意框图;

51.图34是根据本发明的抽取器的实施方案的示意框图;

52.图35是根据本发明的具有频道的频带的实施例;

53.图36是根据本发明的数字抽取滤波电路的另一个实施方案的示意框图;

54.图37是根据本发明的数字抽取滤波电路的另一个实施方案的示意框图;

55.图38是根据本发明的数字抽取滤波电路的多相滤波器的实施例的示意框图;

56.图39是根据本发明的数字抽取滤波电路的另一个实施方案的示意框图;

57.图40是根据本发明的移位寄存器存储器的实施例的示意框图;

58.图41是根据本发明的数字抽取滤波电路的另一个实施方案的示意框图;

59.图42是根据本发明的具有n个频道的频带的实施例;

60.图43是根据本发明的数字带通滤波器(bpf)电路的实施方案的示意框图;

61.图44是根据本发明的数字带通滤波器(bpf)电路的示例频率响应h(z);

62.图45是根据本发明的数字带通滤波器(bpf)电路的示例频率响应h(z);

63.图46a

‑

46d是根据本发明通过数字带通滤波器(bpf)电路处理信号的实施例;

64.图47a

‑

47d是根据本发明通过数字带通滤波器(bpf)电路处理信号的实施例;

65.图48是根据本发明的数字带通滤波器(bpf)电路的实施方案的示意框图;

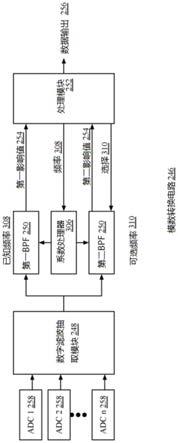

66.图49是根据本发明的模数转换电路的另一个实施方案的示意框图;

67.图50是根据本发明的第一带通滤波器(bpf)电路的实施方案的示意框图;

68.图51是根据本发明的第二带通滤波器(bpf)电路的实施方案的示意框图;

69.图52是根据本发明的系数处理器的实施方案的示意框图;

70.图53是根据本发明的模数转换电路的另一个实施方案的示意框图;以及

71.图54是模数转换电路内的处理模块控制的实施方案的示意框图。

72.发明详述

73.图1是包括多个计算装置12

‑

10、一个或多个服务器22、一个或多个数据库24、一个或多个网络26、多个驱动感测电路28、多个传感器30和多个致动器32的通信系统10的实施方案的示意框图。计算装置14包括具有传感器和驱动传感器电路的触摸屏16,计算装置18包括触摸和触觉屏幕20,其包括传感器、致动器和驱动感测电路。

74.传感器30用于将物理输入转换成电输出和/或光输出。传感器的物理输入可以是多种物理输入条件之一。例如,物理条件包括但不限于以下中的一种或多种:声波(例如,幅度、相位、极化、频谱和/或波速);生物和/或化学条件(例如,流体浓度、液位、成分等);电气条件(例如,电荷、电压、电流、电导率、介电常数、电场,包括幅度、相位和/或极化);磁性条件(例如,通量、磁导率、磁场,包括幅度、相位和/或极化);光学条件(例如,折射率、反射率、吸收率等);热条件(例如,温度、通量、比热、热导率等);以及机械条件(例如位置、速度、加速度、力、应变、应力、压力、扭矩等)。例如,压电传感器将力或压力转换为电信号。作为另一个实施例,麦克风将可听声波转换为电信号。

75.有多种类型的传感器来感测各种类型的物理条件。传感器类型包括但不限于电容传感器、电感传感器、加速度计、压电传感器、光传感器、磁场传感器、超声波传感器、温度传感器、红外(ir)传感器、触摸传感器、接近传感器、压力传感器、液位传感器、烟雾传感器和气体传感器。在许多方面,传感器作为物理世界和数字世界之间的接口,方法是通过将现实世界的条件转换为数字信号,然后由计算装置处理,用于大量应用,包括但不限于医疗应用、生产自动化应用、家庭环境控制、公共安全等。

76.各种类型的传感器具有多种传感器特性,这些特性是向传感器提供电力、接收来

自传感器的信号和/或解释来自传感器的信号的因素。传感器特性包括电阻、电抗、功率要求、灵敏度、范围、稳定性、可重复性、线性度、误差、响应时间和/或频率响应。例如,电阻、电抗和/或功率要求是确定驱动电路要求的因素。作为另一个实施例,灵敏度、稳定性和/或线性度是用于解释基于接收到的电和/或光信号的物理条件的量度(例如,温度、压力等的量度)的因素。

77.致动器32将电输入转换成物理输出。致动器的物理输出可以是多种物理输出条件之一。例如,物理输出条件包括但不限于以下中的一种或多种声波(例如,幅度、相位、极化、频谱和/或波速);磁性条件(例如,通量、磁导率、磁场,包括幅度、相位和/或极化);热条件(例如,温度、通量、比热、热导率等);以及机械条件(例如位置、速度、加速度、力、应变、应力、压力、扭矩等)。作为示例,压电致动器将电压转换为力或压力。作为另一个实施例,扬声器将电信号转换成可听的声波。

78.致动器32可以是多种致动器中的一种。例如,致动器32是梳状驱动器、数字微镜装置、电动机、电活性聚合物、液压缸、压电致动器、气动致动器、螺旋千斤顶、伺服机构、螺线管、步进电机、形状记忆合金、热双压电晶片和液压致动器。

79.各种类型的致动器具有多种致动器特性,这些特性是向致动器提供动力和向致动器发送信号以获得期望性能的因素。致动器特性包括电阻、电抗、功率要求、灵敏度、范围、稳定性、可重复性、线性度、误差、响应时间和/或频率响应。例如,电阻、电抗和功率要求是决定驱动电路要求的因素。作为另一个实施例,灵敏度、稳定性和/或线性是用于生成发送到致动器以获得期望物理输出条件的信号的因素。

80.计算装置12、14和18可以各自是便携式计算装置和/或固定计算装置。便携式计算装置可以是社交网络装置、游戏装置、手机、智能电话、数字助理、数字音乐播放器、数字视频播放器、膝上型计算机、手持计算机、平板电脑、视频游戏控制器和/或任何其他包含计算核心的便携式装置。固定计算装置可以是计算机(pc)、计算机服务器、有线机顶盒、卫星接收器、电视机、打印机、传真机、家庭娱乐设备、视频游戏控制台和/或任何类型的家庭或办公室计算设备。将参考图2

‑

4中的一个或多个更详细地讨论计算装置12、14和18。

81.服务器22是被优化用于并行处理大量数据请求的特殊类型的计算装置。服务器22包括与计算装置12、14和/或18的组件类似的组件,具有更健壮的处理模块、更多的主存储器和/或更多的硬盘驱动器存储器(例如,固态、硬盘驱动器等)。此外,服务器22通常被远程访问;因此,它通常不包括用户输入装置和/或用户输出装置。此外,服务器可以是独立的单独计算装置和/或可以是云计算装置。

82.数据库24是一种特殊类型的计算装置,其针对大规模数据存储和检索进行了优化。数据库24包括与计算装置12、14和/或18的组件类似的组件,具有更多的硬盘驱动器存储器(例如,固态、硬盘驱动器等)并且可能具有更多的处理模块和/或主存储器。此外,通常远程访问数据库24;因此,它通常不包括用户输入装置和/或用户输出装置。此外,数据库24可以是独立的单独计算装置和/或可以是云计算装置。

83.网络26包括一个或多个局域网(lan)和/或一个或多个广域网(wan),其可以是公共网络和/或专用网络。lan可以是无线lan(例如,wi

‑

fi接入点、蓝牙、zigbee等)和/或有线网络(例如,火线(firewire)、以太网等)。wan可以是有线和/或无线wan。例如,lan可能是个人家庭或企业的无线网络,而wan是因特网、蜂窝电话基础设施和/或卫星通信基础设施。

84.在操作的实施例中,计算装置12

‑

1与多个驱动感测电路28通信,所述多个驱动感测电路28进而与多个传感器30通信。传感器30和/或驱动感测电路28位于计算装置12

‑

1内和/或其外部。例如,传感器30可以在计算装置12

‑

1的外部并且驱动感测电路在计算装置12

‑

1内。作为另一个实施例,传感器30和驱动感测电路28都在计算装置12

‑

1的外部。当驱动感测电路28在计算装置外部时,它们经由有线和/或无线通信链路耦合到计算装置12

‑

1,如将参考图5a

‑

5c中的一个或多个更详细地讨论的。

85.计算装置12

‑

1与驱动感测电路28通信以:(a)开启它们,(b)从传感器(单独和/或集体)获取数据,(c)指示驱动传感电路如何将传感数据传送到计算装置12

‑

1,(d)提供与传感器一起使用的信号属性(例如,直流电平、交流电平、频率、功率电平、调节电流信号、调节电压信号、阻抗调节、各种传感器的频率模式、不同传感应用的不同频率等),和/或(e)提供其他命令和/或指令。

86.作为特定实施例,传感器30沿管道分布以测量管道的区段内的流速和/或压力。驱动感测电路28具有它们自己的电源(例如,电池、供电装置等)并且位于它们各自的传感器30的近侧。以期望的时间间隔(毫秒、秒、分钟、小时等),驱动感测电路28向传感器30提供经调节的源信号或功率信号。传感器30的电特性影响经调节的源信号或功率信号,其反映传感器正在感测的条件(例如,流速和/或压力)。

87.作为传感器的电特性的结果,驱动感测电路28检测对经调节的源信号或功率信号的影响。驱动感测电路28然后基于检测到的对功率信号的影响来生成表示对经调节的源信号或功率信号的改变的信号。经调节的源信号或功率信号的变化代表传感器30感测的条件。

88.驱动感测电路28向计算装置12

‑

1提供条件的代表信号。代表信号可以是模拟信号或数字信号。在任一情况下,计算装置12

‑

1解释代表信号以确定沿管道的每个传感器位置处的压力和/或流速。计算装置然后可以将该信息提供给服务器22、数据库24和/或另一个计算装置用于存储和/或进一步处理。

89.作为操作的另一实施例,计算装置12

‑

2耦合到驱动感测电路28,驱动感测电路28又耦合到传感器30。传感器30和/或驱动感测电路28可以在计算装置12

‑

2内部和/或外部。在该实施例中,传感器30正在感测特定于计算装置12

‑

2的条件。例如,传感器30可以是温度传感器、环境光传感器、环境噪声传感器等。如上所述,当被计算装置12

‑

2指示时(这可以是连续感测的默认设置或定期间隔),驱动感测电路28向传感器30提供经调节的源信号或功率信号,并基于传感器的电特性检测对经调节的源信号或功率信号的影响。驱动感测电路生成该影响的代表信号并将其发送到计算装置12

‑

2。

90.在操作的另一实施例中,计算装置12

‑

3耦合到多个驱动感测电路28,所述多个驱动感测电路28耦合到多个传感器30并且耦合到多个驱动感测电路28,所述多个驱动感测电路28耦合到多个致动器32。根据以上描述,耦合到传感器30的驱动感测电路28的一般功能。

91.由于致动器32本质上是传感器的反相,因为致动器将电信号转换为物理条件,而传感器将物理条件转换为电信号,因此驱动感测电路28可用于为致动器32供给动力。因此,在该实施例中,计算装置12

‑

3向致动器32的驱动感测电路28提供致动信号。驱动感测电路将致动信号调制为功率信号或经调节的控制信号,功率信号或经调节的控制信号提供给致动器32。致动器32由功率信号或经调节的控制信号供给动力并且从调制的致动信号产生期

望的物理条件。

92.作为操作的另一实施例,计算装置12

‑

x耦合到与传感器30耦合的驱动感测电路28并且耦合到与致动器32耦合的驱动感测电路28。在该实施例中,传感器30和致动器32供计算装置12

‑

x使用。例如,传感器30可以是压电麦克风并且致动器32可以是压电扬声器。

93.图2是计算装置12(例如,12

‑

1到12

‑

x中的任何一个)的实施方案的示意框图。计算装置12包括核心控制模块40、一个或多个处理模块42、一个或多个主存储器44、高速缓冲存储器46、视频图形处理模块48、显示器50、输入

‑

输出(i/o)外围装置控制模块52、一个或多个输入接口模块56、一个或多个输出接口模块58、一个或多个网络接口模块60和一个或多个存储器接口模块62。在本发明部分的详细描述的最后对处理模块42进行了更详细地描述,并且在替代实施方案中,处理模块42具有到主存储器44的定向连接。在替代实施方案中,核心控制模块40和i/o和/或外围控制模块52是一个模块,例如芯片组、快速路径互连(qpi)和/或超路径互连(upi)。

94.每个主存储器44包括一个或多个随机存取存储器(ram)集成电路或芯片。例如,主存储器44包括四个ddr4(第四代双倍数据速率)ram芯片,每个都以2,400mhz的速率运行。通常,主存储器44存储与处理模块42最相关的数据和操作指令。例如,核心控制模块40协调来自主存储器44和存储器64

‑

66的数据和/或操作指令的传输。从存储器64

‑

66检索的数据和/或操作指令是处理模块请求的或处理模块最可能需要的数据和/或操作指令。当处理模块完成主存储器中的数据和/或操作指令时,核心控制模块40协调将更新的数据发送到存储器64

‑

66用于存储。

95.存储器64

‑

66包括一个或多个硬盘驱动器、一个或多个固态存储芯片和/或一个或多个其他大容量存储装置,与高速缓冲存储器和主存储装置相比,它们相对相对于存储的数据量而言,成本低廉。存储器64

‑

66经由i/o和/或外围控制模块52以及经由一个或多个存储器接口模块62耦合到核心控制模块40。在一个实施方案中,i/o和/或外围控制模块52包括一个或多个外围组件接口(pci)总线,外围组件经由它们连接到核心控制模块40。存储器接口模块62包括用于将存储器装置耦合到i/o和/或外围控制模块52的软件驱动器和硬件连接器。例如,存储器接口62符合串行高级技术附件(sata)端口。

96.核心控制模块40通过i/o和/或外围控制模块52、网络接口模块60和网卡68或70协调处理模块42和网络26之间的数据通信。网卡68或70包括无线通信单元或有线通信单元。无线通信单元包括无线局域网(wlan)通信装置、蜂窝通信装置、蓝牙装置和/或zigbee通信装置。有线通信单元包括千兆lan连接、火线连接和/或专有计算机有线连接。网络接口模块60包括用于将网卡耦合到i/o和/或外围控制模块52的软件驱动器和硬件连接器。例如,网络接口模块60符合ieee 802.11的一个或多个版本、蜂窝电话协议、10/100/1000千兆lan协议等。

97.核心控制模块40通过输入接口模块56和i/o和/或外围控制模块52协调处理模块42和输入装置72之间的数据通信。输入装置72包括小键盘、键盘、控制开关、触摸板、麦克风、照相机等。输入接口模块56包括用于将输入装置耦合到i/o和/或外围控制模块52的软件驱动器和硬件连接器。在一个实施方案中,输入接口模块56符合一个或多个通用串行总线(usb)协议。

98.核心控制模块40通过输出接口模块58和i/o和/或外围控制模块52协调处理模块

42和输出装置74之间的数据通信。输出装置74包括扬声器等。输出接口模块58包括用于将输出装置耦合到i/o和/或外围控制模块52的软件驱动器和硬件连接器。在一个实施方案中,输出接口模块56符合一种或多种音频编解码器协议。

99.处理模块42直接与视频图形处理模块48通信以在显示器50上显示数据。显示器50包括led(发光二极管)显示器、lcd(液晶显示器)和/或其他类型的显示技术。显示器具有分辨率、纵横比和其他影响显示器质量的特性。视频图形处理模块48从处理模块42接收数据,根据显示器的特性处理数据以产生渲染数据,并将渲染数据提供给显示器50。

100.图2进一步图示了耦合到驱动感测电路28的传感器30和致动器32,驱动感测电路28耦合到输入接口模块56(例如,usb端口)。或者,驱动感测电路28中的一个或多个经由无线网卡(例如,wlan)或有线网卡(例如,千兆位lan)耦合到计算装置。虽然未示出,但计算装置12还包括耦合到核心控制模块40的bios(基本输入输出系统)存储器。

101.图3是计算装置14的另一实施方案的示意框图,其包括核心控制模块40、一个或多个处理模块42、一个或多个主存储器44、高速缓冲存储器46、视频图形处理模块48、触摸屏16、输入

‑

输出(i/o)外围控制模块52、一个或多个输入接口模块56、一个或多个输出接口模块58、一个或多个网络接口模块60和一个或多个存储器接口模块62。触摸屏16包括触摸屏显示器80、多个传感器30、多个驱动感测电路(dsc)和触摸屏处理模块82。

102.计算装置14与图2的计算装置12类似地操作,增加了触摸屏作为输入装置。触摸屏包括多个传感器(例如,电极、电容器感测单元、电容器传感器、电感传感器等)以检测屏幕的近侧触摸。例如,当一根或多根手指触摸屏幕时,触摸处(一个或多个)近侧的传感器的电容会受到影响(例如,阻抗变化)。耦合到受影响的传感器的驱动感测电路(dsc)检测变化并将变化的表示提供给触摸屏处理模块82,触摸屏处理模块82可以是单独的处理模块或集成到处理模块42中。

103.触摸屏处理模块82处理来自驱动感测电路(dsc)的代表信号以确定触摸处的位置。该信息被输入到处理模块42以作为输入进行处理。例如,触摸表示选择屏幕上的按钮、滚动功能、放大缩小功能等。

104.图4是计算装置18的另一实施方案的示意框图,其包括核心控制模块40、一个或多个处理模块42、一个或多个主存储器44、高速缓冲存储器46、视频图形处理模块48、触摸和触觉屏20、输入

‑

输出(i/o)外围控制模块52、一个或多个输入接口模块56、一个或多个输出接口模块58、一个或多个网络接口模块60和一个或多个存储器接口模块62。触摸和触觉屏20包括触摸和触觉屏显示器90、多个传感器30、多个致动器32、多个驱动感测电路(dsc)、触摸屏处理模块82、触屏处理模块92。

105.计算装置18与图3的计算装置14类似地操作,其中将触觉方面添加到屏幕20作为输出装置。屏幕20的触觉部分包括多个致动器(例如,产生振动的压电换能器,产生运动的螺线管等)以向屏幕20提供触感。为此,处理模块产生触觉数据,其通过触屏处理模块92提供给适当的驱动感测电路(dsc),触屏处理模块92可以是独立的处理模块或集成到处理模块42中。驱动感测电路(dsc)将触觉数据转换成驱动信号并将它们提供给适当的致动器以在屏幕20上产生所需的触感。

106.图5a是计算子系统25的示意性绘图,该计算子系统25包括感测数据处理模块65、多个通信模块61a

‑

x、多个处理模块42a

‑

x、多个驱动感测电路28以及多个传感器1

‑

x,传感

器1

‑

x可以是图1的传感器30。感测数据处理模块65是一个或多个服务器22内的一个或多个处理模块和/或与处理模块42a

‑

x所在的计算装置不同的一个或多个计算装置中的一个或多个处理模块。

107.驱动感测电路28(或多个驱动感测电路)、处理模块(例如,41a)和通信模块(例如,61a)在公共计算装置内。驱动感测电路、处理模块和通信模块的每一组都在单独的计算装置中。通信模块61a

‑

x是根据一种或多种有线通信协议和/或一种或多种无线通信协议构建的,所述协议符合开放系统互连(osi)模型、传输控制协议/网际协议(tcp/ip)模型以及其他通信协议模块中的一种或多种。

108.在操作的实施例中,处理模块(例如,42a)向其对应的驱动感测电路28提供控制信号。处理模块42a可以生成控制信号,从感测数据处理模块65接收它,或从感测数据处理模块65接收生成控制信号的指示。控制信号使驱动感测电路28能够向其对应的传感器提供驱动信号。控制信号还可以包括具有一个或多个频率分量的参考信号以促进驱动信号的创建和/或解释从传感器接收的感测信号。

109.基于控制信号,驱动感测电路28在驱动&感测线上向其对应的传感器(例如,1)提供驱动信号。在接收驱动信号(例如,电源信号、经调节的源信号等)的同时,传感器感测物理条件1

‑

x(例如,声波、生物条件、化学条件、电条件、磁条件、光学条件、热条件和/或机械条件)。作为物理条件的结果,传感器的电特性(例如,阻抗、电压、电流、电容、电感、电阻、电抗等)发生变化,从而影响驱动信号。请注意,如果传感器是光学传感器,它会将感测到的光学条件转换为电特性。

110.驱动感测电路28经由驱动&感测线检测对驱动信号的影响并且处理该影响以产生代表功率变化的信号,该信号可以是模拟或数字信号。处理模块42a接收代表功率变化的信号,对其进行解释,并产生代表所感测的物理条件的值。例如,如果传感器感应压力,则表示感应到的物理条件的值是压力的度量(例如,x psi(磅每平方英寸))。

111.根据感测数据处理功能(例如,算法、应用等),感测数据处理模块65从处理模块收集表示感测的物理条件的值。由于传感器1

‑

x可以是相同类型的传感器(例如,压力传感器),每个传感器可以是不同的传感器,或者它们的组合;感测到的物理条件可以相同,可以各自不同,或者它们的组合。感测数据处理模块65处理收集的值以产生一个或多个期望结果。例如,如果计算子系统25正在监控沿管道的压力,则对收集到的值的处理表明压力都在正常限值内或者一个或多个感测到的压力不在正常限值内。

112.作为另一实施例,如果计算子系统25用于制造设施中,则传感器感测各种物理条件,例如声波(例如,用于隔音、声音生成、超声监测等),生物条件(例如,细菌污染等),化学条件(例如,成分、气体浓度等)、电气条件(例如,电流水平、电压水平、电磁干扰等)、磁条件(例如,感应电流、磁场强度、磁场取向等)、光学条件(例如,环境光、红外线等)、热条件(例如,温度等),和/或机械条件(例如,物理位置、力、压力、加速度等)。

113.计算子系统25还可以包括一个或多个致动器来代替一个或多个传感器和/或作为传感器之外的补充。当计算子系统25包括致动器时,相应的处理模块向相应的驱动传感电路28提供致动控制信号。致动控制信号使驱动传感电路28能够通过驱动和致动线向致动器提供驱动信号(例如,类似于驱动和感测线,但用于致动器)。驱动信号包括一个或多个频率分量和/或幅度分量以促进致动器的期望致动。

114.此外,计算子系统25可以包括协同工作的致动器和传感器。例如,传感器正在感测致动器的物理条件。在该实施例中,驱动感应电路向致动器提供驱动信号,而另一个驱动感应信号向传感器提供相同的驱动信号或其缩放版本。这允许传感器提供对致动器物理状况的近乎即时和连续的感测。这进一步允许传感器以第一频率运行并且致动器以第二频率运行。

115.在一个实施方案中,计算子系统是用于多种应用(例如,制造、管道、测试、监控、安全等)的独立系统。在另一实施方案中,计算子系统25是形成更大系统的多个子系统中的一个子系统。例如,基于地理位置采用不同的子系统。作为一个具体的实施例,计算子系统25部署在工厂的一个部分,另一个计算子系统部署在工厂的另一部分。作为另一个实施例,基于子系统的功能采用不同的子系统。作为一个具体的实施例,一个子系统监控城市的交通灯运行,另一个子系统监控城市的污水处理厂。

116.不管计算系统的使用和/或部署、它感测的物理条件和/或它正在致动的物理条件如何,每个传感器和每个致动器(如果包括)都由单线驱动和感测,与单独的驱动线和感应线相反。这提供了许多优点,包括但不限于更低的功率要求、更好的驱动高阻抗传感器的能力、更低的线对线干扰,和/或并发感测功能。

117.图5b是计算子系统25的另一个实施方案的示意框图,其包括感测数据处理模块65、通信模块61、多个处理模块42a

‑

x、多个驱动感测电路28和多个传感器1

‑

x,传感器1

‑

x可以是图1的传感器30。感测数据处理模块65是一个或多个服务器22中的一个或多个处理模块和/或与处理模块42a

‑

x所在的计算装置不同的一个或多个计算装置中的一个或多个处理模块。

118.在一个实施方案中,驱动感测电路28、处理模块和通信模块在公共计算装置内。例如,计算装置包括中央处理单元,该中央处理单元包括多个处理模块。感测数据处理模块65、通信模块61、处理模块42a

‑

x、驱动感测电路28和传感器1

‑

x的功能和操作如参考图5a所讨论的。

119.图5c是计算子系统25的另一个实施方案的示意框图,计算子系统25包括感测数据处理模块65、通信模块61、处理模块42、多个驱动感测电路28和多个传感器1

‑

x,传感器1

‑

x可以是图1的传感器30。感测数据处理模块65是一个或多个服务器22内的一个或多个处理模块和/或与处理模块42所在的计算装置不同的一个或多个计算装置中的一个或多个处理模块。

120.在一个实施方案中,驱动感测电路28、处理模块和通信模块在公共计算装置内。感测数据处理模块65、通信模块61、处理模块42、驱动感测电路28和传感器1

‑

x的功能和操作如参考图5a所讨论的。

121.图5d是计算子系统25的另一个实施方案的示意框图,其包括处理模块42、参考信号电路100、多个驱动感测电路28和多个传感器30。处理模块42包括驱动感测处理块104、驱动感测控制块102和参考控制块106。处理模块42的每个块102

‑

106可以通过处理模块的单独模块来实现,可以是处理模块内的软件和硬件的组合,和/或可以是处理模块42内的现场可编程模块。

122.在操作的实施例中,驱动感测控制块104生成一个或多个控制信号以激活一个或多个驱动感测电路28。例如,驱动感测控制块102生成控制信号,在给定的时间段(例如,1

秒、1分钟等)内启用驱动感测电路28。作为另一实施例,驱动感测控制块102生成控制信号以顺序地启用驱动感测电路28。作为又一实施例,驱动感测控制块102生成一系列控制信号以周期性地启用驱动感测电路28(例如,每秒、每分钟、每小时等启用一次)。

123.继续操作的实施例,参考控制块106生成参考控制信号,其将参考控制信号提供给参考信号电路100。参考信号电路100根据控制信号生成用于驱动感测电路28的一个或多个参考信号。例如,控制信号是使能信号,作为响应,参考信号电路100生成预编程的参考信号,其将预编程的参考信号提供给驱动感测电路28。在另一个实施例中,参考信号电路100为驱动感测电路28中的每一个生成唯一参考信号。在又一实施例中,参考信号电路100为第一组中的驱动感测电路28中的每一个生成第一唯一参考信号并且为第二组中的驱动感测电路28中的每一个生成第二唯一参考信号。

124.参考信号电路100可以以多种方式实现。例如,参考信号电路100包括dc(直流)电压发生器、ac电压发生器和电压组合电路。dc电压发生器产生第一电平的dc电压,而ac电压发生器产生第二电平的ac电压,第二电平小于或等于第一电平。电压组合电路组合直流电压和交流电压以产生参考信号。作为实施例,参考信号电路100生成类似于图7中所示的信号的参考信号,这将在随后讨论。

125.作为另一实施例,参考信号电路100包括dc电流发生器、ac电流发生器和电流组合电路。dc电流发生器产生第一电流水平的dc电流,ac电流发生器产生第二电流水平的ac电流,第二电流水平小于或等于第一电流水平。电流组合电路组合dc和ac电流以产生参考信号。

126.回到操作实施例,参考信号电路100向驱动感测电路28提供一个或多个参考信号。当驱动感测电路28经由来自驱动感测控制块102的控制信号被启用时,它向其对应的传感器30提供驱动信号。作为物理条件的结果,传感器的电特性改变,这影响驱动信号。基于检测到的对驱动信号和参考信号的影响,驱动感测电路28产生代表对驱动信号的影响的信号。

127.驱动感测电路向驱动感测处理块104提供代表对驱动信号的影响的信号。驱动感测处理块104处理代表信号以产生物理条件的感测值97(例如,代表特定温度、特定压力水平等的数字值)。处理模块42将感测值97提供给在计算装置上运行的另一个应用程序、另一个计算装置和/或服务器22。

128.图5e是包括处理模块42、多个驱动感测电路28和多个传感器30的计算子系统25的另一个实施方案的示意框图。该实施方案类似于图5d的实施方案,更详细地示出了驱动感测处理块104、驱动感测控制块102和参考控制块106的功能。例如,驱动感测控制块102包括单独的启用/禁用块102

‑

1到102

‑

y。启用/禁用块用于以如上文参考图5d所讨论的方式启用或禁用对应的驱动感测电路。

129.驱动感测处理块104包括方差确定模块104

‑

1a到y和方差解释模块104

‑

2a到y。例如,方差确定模块104

‑

1a从对应的驱动感测电路28接收代表由传感器感测的物理条件的信号。方差确定模块104

‑

1a用于确定代表所感测的物理条件的信号与代表已知的或参考的物理条件的信号的差异。方差解释模块104

‑

1b解释该差异以确定感测到的物理条件的特定值。

130.作为一个具体实施例,方差确定模块104

‑

1a从相应的驱动感测电路28接收代表由

传感器感测到的感测物理条件(例如,温度)的数字信号10010110(十进制为150)。对于8位,有28(256)个可能的信号代表所感测的物理条件。假设温度单位是摄氏度,数字值0100 0000(十进制的64)表示25摄氏度的已知值。方差确定模块104

‑

b1确定代表感测值的数字信号(例如,1001 0110,十进制的150)与已知信号值(例如,0100 0000,十进制的64)之间的差值,即0011 0000(十进制的86)。方差确定模块104

‑

b1然后基于该差值和已知值确定感测值。在此实施例中,感测值等于25 86*(100/256)=25 33.6=58.6摄氏度。

131.图6是耦合到传感器30的驱动中心电路28

‑

a的示意框图。驱动感测电路28包括电源电路110和电源信号变化检测电路112。传感器30包括基于变化的物理条件114(例如,压力、温度、生物、化学等)具有变化的电特性(例如,电容、电感、阻抗、电流、电压等)的一个或多个换能器,反之亦然(例如,致动器)。

132.电源电路110可操作地耦合到传感器30,并且当被启用时(例如,根据来自处理模块42的控制信号,施加电力,闭合开关,接收参考信号等)向传感器30提供功率信号116。电源电路110可以是产生基于电压的功率信号的电压供应电路(例如,电池、线性调节器、未调节的dc

‑

dc转换器等),产生基于电流的功率信号的电流源电路(例如,电流源电路、电流镜电路等),或为传感器提供所需功率电平并基本匹配传感器阻抗的电路。电源电路110产生包括dc(直流)分量和/或振荡分量的功率信号116。

133.当接收功率信号116并且当暴露于条件114时,传感器的电特性影响118功率信号。当功率信号变化检测电路112被启用时,它检测作为传感器的电特性的结果对功率信号的影响118。例如,功率信号是1.5电压信号,并且在第一条件下,传感器消耗1毫安电流,这对应于1.5k欧姆的阻抗。在第二条件下,电源信号保持在1.5伏,电流增加到1.5毫安。因此,从条件1到条件2,传感器的阻抗从1.5k欧姆变为1k欧姆。功率信号变化检测电路112确定该变化并产生对功率信号的变化的代表信号120。

134.作为另一实施例,功率信号是1.5电压信号,并且在第一条件下,传感器消耗1毫安的电流,其对应于1.5k欧姆的阻抗。在第二条件下,电源信号下降到1.3伏,电流增加到1.3毫安。因此,从条件1到条件2,传感器的阻抗从1.5k欧姆变为1k欧姆。功率信号变化检测电路112确定该变化并产生对功率信号的变化的代表信号120。

135.如图7所示,功率信号116包括dc分量122和/或振荡分量124。振荡分量124包括正弦信号、方波信号、三角波信号、多电平信号(例如,具有相对于dc分量随时间变化的幅度),和/或多边形信号(例如,相对于dc分量具有对称或不对称的多边形形状)。请注意,作为条件或条件变化的结果,功率信号不会受到传感器的影响。

136.在一个实施方案中,功率产生电路110改变功率信号116的振荡分量124的频率,使得它可以被调谐到传感器的阻抗和/或在频率上从系统中的其他功率信号偏移。例如,电容传感器的阻抗随频率降低。因此,如果振荡分量的频率相对于电容而言太高,则电容器看起来像短路,并且电容的变化将被忽略。类似地,如果振荡分量的频率相对于电容来说太低,则电容器看起来像是开路,电容的变化将被忽略。

137.在一个实施方案中,功率产生电路110改变dc分量122和/或振荡分量124的幅度以提高感测的分辨率和/或调整感测的功耗。此外,功率产生电路110产生驱动信号110,使得振荡分量124的幅度小于dc分量122的幅度。

138.图6a是耦合到传感器30的驱动中心电路28

‑

a1的示意框图。驱动感测电路28

‑

a1包

括信号源电路111、信号变化检测电路113和电源115。电源115(例如,电池、供电装置、电流源等)产生与信号117组合的电压和/或电流,信号117由信号源电路111产生。组合信号被提供给传感器30。

139.信号源电路111可以是产生基于电压的信号117的电压供应电路(例如,电池、线性调节器、未调节的dc

‑

dc转换器等)、产生基于电流的信号117的电流供应电路(例如,电流源电路、电流镜电路等),或者向传感器提供期望功率水平并且基本上匹配传感器阻抗的电路。信号源电路111产生包括dc(直流)分量和/或振荡分量的信号117。

140.当接收组合信号(例如,信号117和来自电源的功率)并且当暴露于条件114时,传感器的电特性影响119信号。当信号变化检测电路113被启用时,它检测作为传感器的电特性的结果对信号的影响119。

141.图8是绘制电特性对条件的传感器图的实施例。传感器具有基本线性的区域,其中条件的增量变化产生电特性的相应增量变化。该图显示了两种类型的电特性:一种随着条件增加而增加,另一种随着条件增加而减少。作为第一种类型的实施例,温度传感器的阻抗增加并且温度增加。作为第二种类型的实施例,电容触摸传感器的电容随着触摸被感测而减小。

142.图9是功率信号图的另一实施例的示意框图,其中传感器的电特性或电特性的变化正在影响功率信号。在这个实施例中,传感器的电特性或电特性变化的影响减少了直流分量,但对振荡分量几乎没有影响。例如,电特性是电阻。在这个实施例中,传感器的电阻或电阻变化降低了功率信号,推断出相对恒定电流的电阻增加。

143.图10是功率信号图的另一实施例的示意框图,其中传感器的电特性或电特性的变化正在影响功率信号。在这个实施例中,传感器的电特性或电特性变化的影响降低了振荡分量的幅度,但对直流分量几乎没有影响。例如,电特性是电容器和/或电感器的阻抗。在此实施例中,传感器的阻抗或阻抗变化降低了振荡信号分量的幅度,从而推断出相对恒定电流的阻抗增加。

144.图11是功率信号图的另一实施例的示意框图,其中传感器的电特性或电特性的变化正在影响功率信号。在这个实施例中,传感器的电特性或电特性变化的影响改变了振荡分量的频率,但对dc分量几乎没有影响。例如,电特性是电容器和/或电感器的电抗。在该实施例中,传感器的电抗或电抗的变化改变了振荡信号分量的频率,从而推断出电抗的增加(例如,传感器用作积分器或相移电路)。

145.图11a是功率信号图的另一实施例的示意框图,其中传感器的电特性或电特性的变化正在影响功率信号。在这个实施例中,传感器的电特性或电特性变化的影响改变了振荡分量的频率,但对dc分量几乎没有影响。例如,传感器包括以不同频率振荡的两个换能器。第一换能器接收频率为f1的功率信号并将其转换为第一物理条件。第二换能器被第一物理条件激励以产生不同频率f2的电信号。在该实施例中,传感器的第一和第二换能器改变振荡信号分量的频率,这允许更细粒度的感测和/或更宽的感测范围。

146.图12是功率信号变化检测电路112的一个实施方案的示意框图,该电路接收受影响的功率信号118和产生的功率信号116,以由此产生表示功率信号变化的信号120。对功率信号的影响118是传感器的电特性和/或电特性变化的结果;图8

‑

11a显示了影响的一些实施例。

147.在一个实施方案中,功率信号变化检测电路112检测功率信号116的dc分量122和/或振荡分量124的变化。功率信号变化检测电路112然后根据电源信号的变化来产生代表功率信号的变化的信号120。例如,功率信号的变化起因于传感器的阻抗和/或传感器阻抗的变化。代表信号120反映了功率信号的变化和/或传感器阻抗的变化。

148.在一个实施方案中,功率信号变化检测电路112可操作以检测振荡分量在某一频率处的变化,该变化可以是振荡分量的相移、频率变化和/或幅度变化。功率信号变化检测电路112还可操作以基于该频率处的振荡分量的变化来生成表示功率信号的变化的信号。功率信号变化检测电路112还用于向电源电路110提供关于振荡分量的反馈。反馈允许电源电路110以期望的频率、相位和/或幅度调节振荡分量。

149.图13是驱动感测电路28

‑

b的另一实施方案的示意框图,驱动感测电路28

‑

b包括变化检测电路150、调节电路152和电源电路154。驱动感测电路28

‑

b耦合到传感器30,其包括基于变化的物理条件114(例如,压力、温度、生物、化学等)而具有变化的电特性(例如,电容、电感、阻抗、电流、电压等)的换能器。.

150.电源电路154可操作地耦合到传感器30,并且当被启用时(例如,根据来自处理模块42的控制信号,施加电力,关闭开关,接收参考信号,等等)向传感器30提供功率信号158。电源电路154可以是产生基于电压的功率信号的电压供应电路(例如,电池、线性调节器、未调节的dc

‑

dc转换器等)或产生基于电流的功率信号的电流供应电路(例如,电流源电路、电流镜电路等)。电源电路154产生包括dc(直流)分量和振荡分量的功率信号158。

151.当接收功率信号158并且当暴露于条件114时,传感器的电特性影响160功率信号。当启用变化检测电路150时,它检测作为传感器30的电特性的结果对功率信号的影响160。变化检测电路150进一步可操作以基于检测到的对功率信号的影响生成代表对功率信号的变化的信号120。

152.调节电路152在其被启用时生成调节信号156以将dc分量调节到期望的dc电平和/或基于代表功率信号变化的信号120将振荡分量调节到期望的振荡电平(例如,幅度、相位和/或频率)。无论传感器的电特性如何,电源电路154利用调节信号156来将功率信号保持在期望的设置158。以此方式,调节量表示电特性对功率信号的影响。

153.在一个实施例中,电源电路158是dc

‑

dc转换器,其可操作以提供具有dc分量和ac分量的经调节的功率信号。变化检测电路150是比较器,而调节电路152是产生调节信号156的脉宽调制器。比较器将受传感器影响的功率信号158与包括dc和ac分量的参考信号进行比较。当电特性处于第一水平(例如,第一阻抗)时,调节功率信号以提供电压和电流,使得功率信号基本上类似于参考信号。

154.当电特性改变到第二水平(例如,第二阻抗)时,变化检测电路150检测功率信号158的dc和/或ac分量的变化并且产生代表信号120,代表信号120指示变化。调节电路152检测代表信号120的变化并产生调节信号以基本上消除对功率信号的影响。功率信号158的调节可以通过调节dc和/或ac分量的幅度、通过调节ac分量的频率和/或通过调节ac分量的相位来完成。

155.应注意,本文中可能使用的术语,例如比特流、流、信号序列等(或它们的等价物)已被可互换地使用来描述其内容对应于多种期望类型中的任何一种的数字信息(例如,数据、视频、语音、文本、图形、音频等,其中任何一个通常可以被称为“数据”)。

156.图14是用于为驱动感测电路提供参考信号波形的实施方案的示意框图。在一个实施例中,正弦波形,例如振荡分量124,由参考信号发生器149生成,参考信号发生器149耦合到变化检测电路150。参考信号发生器149可以是锁相环(pll)、晶体振荡器、数字频率合成器和/或任何其他可以提供所需频率、相移和/或幅度的正弦信号的信号源。

157.通常,电源电路154产生源信号158,该源信号被调节以基本上匹配正弦参考信号157。例如,当传感器30是感测触摸屏显示器电容变化的多个传感器之一时,参考信号发生器149产生的正弦信号是有用的。在这样的环境中,正弦参考信号的使用很容易产生并且也不会引入可能对驱动感测电路的操作、显示器的触摸屏操作和/或显示器的显示操作产生不利影响的谐波。

158.电源电路154的输出(源信号158)和参考信号发生器输出(例如参考信号157)耦合到运算放大器151的输入,其输出耦合到模数转换器(adc)212。表示源信号变化的信号120由adc 212输出,该输出也输入到调节电路152并由数模转换器(dac)214转换;调节电路152的输出耦合到电源电路154以向电源电路154提供调节信号156。由参考信号发生器149产生的正弦信号是非线性信号,因此具有非线性分辨率。

159.图15是包括模拟时域电路202、模数电路204和数字频域电路206的数据感测电路200的实施方案的示意框图。数据感测电路200根据频域中信息在时域中工作。一般而言,数据感测电路200基于模拟频域信号210(例如,具有频域中的数据的模拟信号)和参考信号208来生成数字数据216。所得数字数据216可以是期望的输出数据或者可能需要进一步处理以获得所需的数据输出。

160.在操作的实施例中,模拟时域电路202将模拟频域信号210的信号分量输出到装置218。模拟时域电路202包括调节源电路以生成信号分量。在一个实施方案中,调节源电路是基于参考信号208调节到特定电流值的相关电流源。在另一个实施方案中,调节源电路是电压电路(例如,线性调节器、dc

‑

dc转换器、电池等),其基于参考信号208生成调节电压。

161.装置218改变信号分量以产生模拟频域信号210,其中以特定速率改变信号分量以表示输入数据。数据速率的倒数对应于模拟频域信号210的频率;因此,信号在模拟域中,数据在频域中。作为实施例,模拟时域电路202产生的信号分量是对应于参考信号208的dc电压(例如,0.25伏至5伏或更高)。装置218通过改变信号分量上的负载来改变信号分量以影响信号分量的电压和/或电流,从而创建模拟频域信号210(例如,信号分量加上改变的效果)。

162.作为特定实施例,装置218以特定速率(例如,10hz至100mhz或更高)改变其电阻以表示输入数据。电阻的增加降低了恒定电流的电压,降低了恒定电压的电流,或降低了信号分量的电压和电流。电阻的减小增加了恒定电流的电压,增加了恒定电压的电流,或增加了信号分量的电压和电流。装置电阻以特定速率的增加和减少代表输入数据。不同电阻级别的数量对应于数据级别,其中n等于数据速率每个周期的唯一数据值的数量,其中n是2或更大的整数。例如,当n=2时,有两个数据级别(例如,第一电阻的逻辑“0”和第二电阻的逻辑“1”),当n=10时,有十个数据级别(例如,0到9)。

163.作为产生模拟频域信号210的另一实施例,由模拟时域电路202产生的信号分量包括振荡分量(例如,正弦波、三角波、方波、锯齿波等,具有几毫伏到5伏或更高的峰峰电压,具有100hz到1mhz或更高的频率),其对应于参考信号208。在该实施例中,装置以特定速率

(例如,10hz到100mhz或更高的fx)改变其阻抗(例如,电容、电感和/或电阻)来表示输入数据。阻抗的增加降低了恒定电流的电压,降低了恒定电压的电流,或降低了信号分量的电压和电流。阻抗的降低会增加恒定电流的电压,增加恒定电压的电流,或增加信号分量的电压和电流。装置阻抗以特定速率的增加和减少代表了输入数据。

164.继续操作的实施例,模拟时域电路202使用参考信号208与模拟频域信号210相比较来创建模拟频域误差校正信号212。模拟频域误差校正信号212是表示保持信号分量并因此保持模拟频域信号210基本匹配参考信号所需的误差校正。误差校正代表嵌入在信号分量的改变中的频域数据。

165.模数电路204(例如,“n”位模数转换器,其中n是等于或大于1的整数)将模拟频域误差校正信号212转换为数字频域误差校正信号214。表示频域数据的误差校正基本上保留在数字域中。

166.数字频域电路206在频域中操作以恢复数字数据216。例如,数字频域电路206包括一个或多个有限脉冲响应(fir)滤波器、一个或多个级联集成梳状(cic)滤波器、一个或多个无限脉冲响应(fir)滤波器、一个或多个抽取级、一个或多个快速傅立叶变换(fft)滤波器和/或一个或多个离散傅立叶变换(dft)滤波器。

167.图16是数据感测电路200的另一个实施方案的示意框图,其包括模拟时域电路202

‑

1、模数电路204、数字频域电路206;以及数模反馈电路220。该数据感测电路200与图10的数据感测电路200类似地操作,但具有以下区别。用于经由模拟时域电路201

‑

1内的调节源电路调节信号分量的反馈来自数模反馈电路220(例如,“n”位数模转换器,当n是等于或大于1的整数时)。

168.图17是数据电路230的另一实施方案的示意框图,数据电路230包括驱动感测电路28、多个数字带通滤波器(bpf)电路232

‑

236和多个数据源(1至n)。如前所述,驱动感测电路28基于参考信号208产生驱动和感测信号238的驱动信号分量(例如,信号238的驱动部分)。数据源以不同频率操作以将频域数据嵌入驱动和感测信号238(例如,信号238的感测部分)。每个数据源的操作类似于图10的装置218,以通过改变信号238的驱动分量上的负载将数据嵌入到信号238中。

169.在操作的实施例中,数据源1以第一频率fl改变驱动和感测信号238的驱动信号分量;数据源2以第二频率f2改变驱动和感测信号238的驱动信号分量;并且数据源n以“第n”频率fn改变驱动和感测信号238的驱动信号分量。驱动感测电路28调节驱动和感测信号238以基本匹配参考信号208,其可类似于图14的参考信号157。

170.驱动感测电路28基于驱动和感测信号238的调节来输出代表对驱动和感测信号238的改变的信号120。数字bpf电路232中的每一个接收信号120并且被调谐从中提取与数据源之一相对应的数据。例如,数字bpf电路232被调谐以提取数据源1的处于频率f1的数据以产生代表第一数据240的一个或多个数字值。第二数字bpf电路234被调谐以提取数据源2的处于频率f2的数据以产生一个或多个代表第二数据242的数字值。调谐第n个数字bpf电路236以提取数据源n的处于频率fn的数据以产生一个或多个代表第n数据244的数字值。数字bpf电路232

‑

236中的每个包括一个或多个有限脉冲响应(fir)滤波器、一个或多个级联集成梳状(cic)滤波器、一个或多个无限脉冲响应(iir)滤波器、一个或多个抽取级、一个或多个快速傅立叶变换(fft)滤波器,和/或一个或多个离散傅立叶变换(dft)滤波器。

171.图18是模数转换电路246的实施方案的示意框图,模数转换电路246包括模数转换器(adc)258、数字抽取滤波电路248、数字带通滤波器(bpf)电路250、以及处理模块252。adc 258可以以多种方式实现。例如,adc258是先前附图的驱动感测电路28的adc转换器212。作为另一个实施例,adc 258被实现为快速adc、逐次逼近adc、斜坡比较adc、wilkinson adc、积分adc和/或增量编码adc。作为又一实施例,adc 258被实现为西格玛

‑

德尔塔adc。

172.数字抽取滤波电路248包括一个或多个有限脉冲响应(fir)滤波器、一个或多个级联集成梳状(cic)滤波器、一个或多个无限脉冲响应(fir)滤波器、一个或多个抽取级、一个或多个快速傅立叶变换(fft)滤波器,和/或一个或多个离散傅立叶变换(dft)滤波器,一个或多个多相滤波器,以及一个或多个抽取级。数字带通滤波器(bpf)电路250包括一个或多个有限脉冲响应(fir)滤波器、一个或多个级联集成梳状(cic)滤波器、一个或多个无限脉冲响应(fir)滤波器、一个或多个抽取级、一个或多个快速傅立叶变换(fft)滤波器,和/或一个或多个离散傅立叶变换(dft)滤波器,以及一个或多个多相滤波器。bpf 250包括多个抽头,这些抽头的系数被设置为产生近似以模拟输入信号的振荡频率为中心的带通区域,并且具有为对纯音(例如,s1)进行滤波而调谐的带宽。

173.模数转换电路246的级的采样频率被设置为数据输出速率的倍数。例如,数据输出256的速率是300hz,因此采样频率是300hz的倍数。例如,adc电路258以2

17

*300hz(大约39.32mhz)的采样频率(fs)对模拟输入信号进行过采样。当采样频率大于奈奎斯特采样频率(例如,当振荡频率为20khz

‑

200khz时为40khz

‑

400khz)时,模拟输入信号被称为过采样。将采样频率设置为远高于奈奎斯特采样频率的频率会导致模拟信号明显过采样。模拟信号的过采样允许更窄的带通滤波并提高信噪比(snr)。

174.在操作的实施例中,adc 258将包括一组纯音分量(例如,一个或多个纯音分量,每个都具有振荡频率)的模拟信号转换成该一个或多个纯音分量的数字信号。例如,输入模拟信号具有纯音(例如,正弦信号、dc信号、重复信号和/或它们的组合),其在f1处具有直流分量和/或振荡频率(例如,音频范围内的频率,在20khz

‑

200khz范围内,或更多)。作为一个具体的实施例,adc是西格玛

‑

德尔塔adc,它以大约39.32mhz(例如,300*2

17

)的时钟速率对模拟输入信号进行过采样,因此,将低频噪声推高到感兴趣频带外的更高频率。将参考图23更详细地讨论西格玛

‑

德尔塔adc的实施例。

175.继续具体实施例,adc 258产生代表模拟信号的大约39.32mhz的1位数字输出。在一个实施方案中,模拟信号包括频率f1的误差校正信号s1,其表示嵌入在模拟输入信号中的频域数据并且基本上保留在数字域中(例如,如图14

‑

15中所讨论的)。

176.数字抽取滤波电路248获取来自adc电路258的输出(例如,大约39.32mhz的1位数字输出)并将其转换为具有另一数据速率频率的另一数字信号,该另一数据速率频率是数据输出速率的倍数(例如,300hz)。在该实施例中,数字抽取滤波电路248具有2

12

*300hz(大约1.23mhz)的输出速率(fd)。

177.作为更具体的实施例,数字抽取滤波电路248将大约39.32mhz的1位数字输出转换成代表频率fl的误差校正信号sl的2

12

*300hz(大约1.23mhz)的18位输出。采样率(fs)和数字抽取滤波电路248的输出率(fd)之间的比率(例如,fs/fd)等于数字抽取滤波电路248的每个输出的adc 258样本的数量。例如,39.32mhz/1.23mhz=32。因此,数字抽取滤波电路248具有32的抽取率。在adc 258输出32个1位样本所需的时间内,数字抽取滤波电路248产

生1个18位输出。将将参考图31

‑

41更详细地讨论数字抽取滤波电路248。

178.数字bpf电路250取得数字抽取滤波电路248的输出(例如,大约1.23mhz的18位输出)并且对其进行带通滤波。数字bpf电路250应用以f1为中心的窄带通滤波器,并输出具有实分量和虚分量的影响值254。因为数据(例如,误差校正信号)嵌入在正弦曲线(例如,纯音)中,所需的信息位于频率f1并且基于幅度和/或相位。因此,带通滤波器可以非常窄(例如,信道间隔的1%到20%,作为具体实施例,信道间隔255的大约5%(例如,对于300hz的信道间隔,可以使用10hz带通滤波器))来捕获所需的信号。在一个实施方案中,数字bpf电路250具有4096的抽头长度(例如,在数字抽取滤波电路248以大约1.23mhz输出4096个18位输出所花费的时间内,数字bpf电路在300hz输出速率下输出1个48位影响值)。将参考图42

‑

53更详细地讨论数字bpf电路250。

179.处理模块252解释影响值254的虚分量和实分量以产生数据输出256。影响值254是具有代表具有峰值量值(即幅度)和方向(即相位)的正弦函数的实分量和虚分量的向量(即,相量复数)。例如,影响值254是一个具有24位实分量和24位虚分量的48位值。在复数域中,电压和电流是相量,而电阻、电容和电感被复数阻抗代替(例如,zr=r、zl=jfl且zc=1/(jfc)=

‑

j/(fc))。由于电压(v)=电流(i)*阻抗(z),处理模块252根据影响值254的电压和电流向量确定电容或其他阻抗值(例如,阻抗的降低使电压增加恒定电流,使电流增加恒定电压,或增加信号分量的电压和电流)。以特定速率增加和减少阻抗代表输入数据。所确定的阻抗值或阻抗值的变化以300hz的示例输出速率作为数据输出256输出。

180.图19是模数转换电路246的另一个实施方案的示意框图,其包括模数转换器(adc)258、数字抽取滤波电路248、多个数字带通滤波器(bpf)电路250和处理模块252。图19的模数转换电路246的操作与图18的实施例类似,不同之处在于包括多个数字bpf电路用于对多个纯音进行滤波。

181.在操作的实施例中,adc 258将具有一组纯音分量(例如,信号sl

‑

sn)的模拟信号转换成处于振荡频率(例如,fl

‑

fn)的一组数字信号sl

‑

sn。例如,输入模拟信号的第一个音调的振荡频率为f1(例如100khz),例如用于触摸屏显示器上的第一次自电容测量,输入模拟信号的第二个音调的振荡频率为f2(例如100.3khz),例如用于触摸屏显示器上的第一次互电容测量,并且输入模拟信号的第n个音调的振荡频率为fn(例如,100khz 300nhz),例如,用于触摸屏显示器上的第n个互电容测量。频率f1

‑

fn跨越n个信道并且由信道间隔255等距分开。例如,信道间隔255等于300hz的输出数据速率。

182.数字抽取滤波电路248获取来自adc 258的输出(例如,经由n线并行总线)并且将信号转换为具有作为数据输出速率的倍数的另一数据速率频率的其他数字信号(例如,300hz)。在该实施例中,数字抽取滤波电路248具有2

12

*300hz(大约1.23mhz)的输出速率(fd)。例如,数字抽取滤波电路248将代表频率f1

‑

fn的数字信号s1

‑

sn的大约39.32mhz的1位adc输出转换为代表频率为f1

‑

fn的信号s1

‑

sn的2

12*

300hz(大约1.23mhz)的18位输出。

183.数字bpf电路1

‑

n 250中的每一个包括多个抽头,这些抽头的系数被设置为产生近似以模拟输入信号的振荡频率为中心的带通区域,并且带通区域具有调谐用于对纯音进行滤波的带宽。例如,数字bpf电路1 250具有为滤波f1调谐的带宽,数字bpf电路2 250具有为滤波f2调谐的带宽,并且数字bpf电路n 250具有为滤波fn调谐的带宽。数字bpf电路1

‑

n250获取数字抽取滤波电路248的输出(例如,经由总线的在大约1.23mhz的n个18位输出以及频

率为f1

‑

fn的误差校正信号s1

‑

sn)并且将每个信号移位到频率f1

‑

fn的带通。

184.数字bpf电路1

‑

n 250各自应用极窄带通滤波器并输出具有实分量和虚分量的对应影响值1

‑

n 254。因为数据嵌入在每个正弦信号(s1

‑

sn)(例如,纯音)中,所需的信息位于频率f1

‑

fn并基于幅度和/或相位。因此,带通滤波器可以非常窄(例如,小于0.05倍的信道间隔(例如10hz))以捕获所需信号。

185.处理模块252解释影响值1

‑

n 254的虚分量和实分量以产生数据输出1

‑

n 256。影响值1

‑

n 254是向量(即,相量复数),每个都具表示具有峰值量值(即幅度)和方向(即相位)的正弦函数的有实分量和虚分量。例如,影响值是一个具有24位实分量和24位虚分量的48位值。在复数域中,电压和电流是相量,而电阻、电容和电感被复数阻抗代替(例如,zr=r、zl=jfl和zc=1/(jfc)=

‑

j/(fc))。由于电压(v)=电流(i)*阻抗(z),处理模块252根据由影响值1

‑

n 254表示的电压和/或电流向量确定电容或其他阻抗值。确定的阻抗值或阻抗值的变化被输出为数据输出1

‑

n 256。数据输出256以输出数据速率(例如,300hz)单独或并行输出。

186.图20a

‑

20b是描绘条件对电容(例如,触摸屏显示器的电极)的示例图。在触摸屏显示实施例中,电极具有自电容和互电容。手指电容或笔电容(例如,触摸)会提高电极的自电容,从而降低给定频率的阻抗。如图20a所示,互电容随触摸而减小,而自电容和笔电容随触摸而增加。如图20b所示,无触摸条件下的互电容、笔电容和自电容显示为大约相同的量值,但与在触摸条件下时不同。例如,互电容因触摸而减小,而自电容和笔电容因触摸而增加。

187.图21是示例图,其绘制了具有主要电容性负载的输入的阻抗与频率的关系。基于电容(自电容、笔电容和/或互电容),随着固定电容的频率增加,阻抗基于1/2πfc降低,其中f是频率,c是电容。

188.图22是影响值254

‑

1和254

‑

2的示例。当嵌入在模拟输入信号中的dc分量代表恒流电压时,影响值代表具有虚分量和实分量的电压向量。处理模块252根据电压向量(例如,阻抗(z)=电压(v)/电流(i)和zc=1/(jfc)=

‑

j/(fc))确定电容变化(例如,自电容、笔电容和/或互电容等)并解释变化是代表触摸还是无触摸条件。

189.图23是西格玛

‑

德尔塔模数(adc)电路的实施方案的示意框图。西格玛

‑

德尔塔(adc)电路258是图18和图19的adc 258的实施例并且包括过采样调制器260和数字抽取滤波电路248。在操作的实施例中,adc电路258将具有振荡频率和一组纯音分量的模拟输入信号262转换大约1.23mhz的速率的18位输出。例如,输入模拟信号262具有f1(例如20khz

‑

200khz)的振荡频率和纯音分量s1。

190.在该实施例中,过采样调制器260是1位adc西格玛

‑

德尔塔调制器。在该实施例中,过采样调制器260以2

17

*300hz(大约39.32mhz)的采样频率(fs)对模拟输入信号262进行过采样。过采样调制器260产生39.32mhz的1位adc输出,表示嵌入在频率f1的正弦信号中的误差校正信号s1。误差校正信号s1代表嵌入在模拟输入信号中的频域数据,并且基本上保留在数字域中。

191.数字抽取滤波电路248包括一个或多个有限脉冲响应(fir)滤波器、一个或多个级联集成梳状(cic)滤波器、一个或多个无限脉冲响应(fir)滤波器、一个或多个抽取级、一个或多个多个快速傅立叶变换(fft)滤波器和/或一个或多个离散傅立叶变换(dft)滤波器、一个或多个多相滤波器和一个或多个抽取级。数字抽取滤波电路248获取来自过采样调制

器260的输出(例如,代表频率f1的误差校正信号s1的大约39.32mhz的1位adc输出)并且对其进行滤波并将其下变频为具有另一数据速率频率的另一数字信号。在该实施例中,数字抽取滤波电路248具有2

12

*300hz(大约1.23mhz)的输出速率(fd)。

192.例如,数字抽取滤波电路248将表示频率fl的误差校正信号sl的大约39.32mhz的1位adc输出转换为代表频率为f1的误差校正信号s1的2

12

*300hz(大约1.23mhz)的18位输出。采样率(fs)与数字抽取滤波电路248的输出率(fd)之间的比率(例如,fs/fd)等于过采样调制器260对数字抽取滤波电路248的每个输出所取的样本数。例如,39.32mhz/1.23mhz=32。因此,数字抽取滤波电路248的抽取率为32。

193.图24是图23的西格玛

‑

德尔塔过采样调制器260的量化噪声的示例。西格玛

‑

德尔塔adc实现噪声整形(即,有效地将低频噪声推高至感兴趣频带外的较高频率的功能)使其适用于高精度、高分辨率的应用。图23的过采样调制器260将量化噪声264移动到更高的频率。西格玛

‑

德尔塔过采样调制器的阶数会改变噪声整形。

194.如图所示,量化噪声264在零hz处开始较低,在过采样调制器的采样频率(fs)处上升然后趋于平稳。多阶西格玛

‑

德尔塔调制器将量化噪声264整形为比低阶西格玛

‑

德尔塔调制器更高的频率。例如,与一阶西格玛

‑

德尔塔调制器相比,三阶西格玛

‑

德尔塔调制器实施例显示频率fs附近的噪声要多得多,但低频附近的噪声要少得多。图23的数字抽取滤波电路248的输出包括从0到频率fd的频率,因此量化噪声264的很大一部分存在于所有三个实施例的输出中。然而,极窄带通滤波(例如,通过前面图中所讨论的数字bpf电路250)在较低频率处隔离感兴趣的信号,使得fd附近的噪声也被去除。

195.图25是图18和图19的模数转换电路246的不同级的示例输出的示意框图。在该实施例中,模数(adc)电路258产生2

17

*300hz(约39.32mhz)的1位adc输出。因此,每个数据输出时钟周期(例如,本实施例中为300hz)有2

17

(或131,072)个1位模拟输入信号样本。数字抽取滤波电路248以2

12

*300hz(大约1.23mhz)产生18位输出。2

17

/2

12

等于25或32;因此,在时间内,adc电路258输出32个1位样本并且数字抽取滤波电路248能够输出一个18位值,如图所示。

196.bpf电路250以300hz的数据输出时钟速率输出一个具有24位实分量和24位虚分量的48位影响值。因此,每个数据输出时钟周期有2

12

个(或4096个)18位值(例如,在本实施例中为300hz)。换言之,在数字抽取滤波电路248输出4096个18位值的时间内,一个或多个数字bpf电路250输出数据输出时钟率为300hz的具有24位实分量和24位虚分量的一个48位影响值。

197.图26是对模拟信号262进行采样以产生数字化信号270的实施例。在该实施例中,模拟信号262以每个周期8个点(s0

‑

s7)采样以创建代表模拟信号262的8个离散点的数字化信号。

198.图27是实现乘法累加函数的数字滤波器的示意框图。所示数字滤波器设计有8个级(例如抽头),以捕获图26的数字化信号的8个离散点。当8个级捕获图26所示模式中的点时,数字滤波器产生一个滤波输出272(例如,代表n位数字逻辑值的脉冲)。输入信号(例如,数字化信号270)在第0级进入数字滤波器,在那里它与系数h0相乘并且还输入到第1级。第1

‑

7级每个都包括z变换符号中的单位延迟z

‑1,以提供延迟输入(抽头)到每一级的乘法运算(即,输入信号在延迟z

‑1之后乘以下一个系数(例如,h1

‑

h6))。每个级的乘法运算结果相加

(即累加)以创建滤波输出。一系列乘法累加函数也称为移动平均线。滤波器的抽头越多,输出的计算量就越大。

199.图28是实现乘法累加函数的数字滤波器的示意框图。数字滤波器的工作方式与图27中的数字滤波器类似,为方便起见,此处显示。

200.图29是数字化信号270的示例。在某个时间点,数字化信号270具有特定模式。例如,所示模式是一个正弦信号周期。可以设置图28的数字滤波器的系数h0

‑

h7,以便只有接近所需模式的东西才能产生可行的输出。

201.图30是产生数字滤波输出272的实施例。随着图29的数字化信号270移动通过数字滤波器的级(例如,图27和28的级),级0

‑

7处的系数h0

‑

h7设置以查找图29中所示的模式(即,系数设置带通滤波器的中心频率、带通滤波器的带宽和带通滤波器的滚降)。当识别出图29中所示的模式(或与该模式相当接近的模式)时,带通滤波器会产生指示信号存在的输出(例如,正弦信号的幅度和/或相位)。如图所示,在第7级和时间t7,滤波器识别出图29所示的模式已经移动通过级0

‑

7,因此在时间t7产生滤波输出272。

202.滤波输出272可以是表示n位数字逻辑值的脉冲。例如,第一幅度的数字化正弦信号可以产生代表0的1位数字逻辑的脉冲,而第二幅度的数字化正弦信号可以产生代表1的1位数字逻辑的脉冲。因此,数字数据(例如,图18

‑

19中的信号s1)可以嵌入到模拟信号中并通过数字滤波提取。

203.图31是数字抽取滤波电路248的一个实施方案的示意框图。数字抽取滤波电路248包括抗混叠滤波器274和抽取器276。一般而言,数字抽取滤波电路248对输入信号的高频分量进行滤波并降低采样率,使得下一级模数转换电路246可以更有效地操作。

204.当adc 258是图23的西格玛

‑

德尔塔adc 258时,数字抽取滤波电路248以大约39.32mhz从adc 258或过采样调制器260接收1位adc输出流。通过过采样模拟输入信号,量化噪声264分布在更宽的带宽上。当adc 258是一阶西格玛

‑

德尔塔adc时,来自过采样调制器260的输出包括量化噪声264,该量化噪声被整形为在过采样调制器260的采样频率(fs)(例如,39.32mhz)处最大,如图所示。

205.抗混叠滤波器274是低通滤波平均滤波器(例如,一个或多个有限脉冲响应(fir)滤波器、一个或多个梳状滤波器、一个或多个升余弦滤波器、一个或多个级联集成梳状(cic)滤波器、一个或多个无限脉冲响应(iir)滤波器、一个或多个抽取级、一个或多个快速傅立叶变换(fft)滤波器和/或一个或多个离散傅立叶变换(dft)滤波器等),其对1位adc输出进行采样并提供截止频率以去除或衰减较高频率的信号(例如,量化噪声264)。抗混叠滤波器274具有频率响应h(z)。

206.抽取器276通过丢弃抗混叠滤波器274的输出数据的部分来降低抗混叠滤波器274的输出速率。在该实施例中,抽取器276将抗混叠滤波器274的输出速率(例如,39.32mhz)降低32以产生大约1.23mhz(例如,39.32mhz/32=1.23mhz)的18位的数字抽取滤波电路248的输出速率。如图所示,应用截止频率为fd的低通抗混叠滤波器274并将信号抽取32去除了fd和fs之间的量化噪声的部分。

207.图32是抗混叠滤波器274的示例频率响应h(z)。例如,抗混叠滤波器274是截断高于1.23mhz的频率(即,数字抽取滤波电路248的输出速率)的有限脉冲响应(fir)。如图所示,fir滤波器具有sinx/x(例如,或“sinc”)频率响应。sinc频率响应具有“陷波”响应(例

如,当设置为该频率时,它可以拒绝线路频率)。陷波位置也与输出数据速率直接相关。如图所示,图32中的第一陷波位置位于数字抽取滤波电路248的输出速率,约为1.23mhz(例如,截止频率)的输出速率。sinc频率响应在数据速率的整数倍处为零(例如,2.46mhz、3.69mhz等)。根据奈奎斯特采样定理,采样率为39.32mhz时,信号可以包含高达39.32mhz/2=19.66mhz的频率成分。

208.图33是抗混叠滤波器274的实施方案的示意框图。在该实施例中,抗混叠滤波器274实施如图27中讨论的乘法累加函数。例如,抗混叠滤波器274是具有n个抽头的低通有限脉冲响应(fir)滤波器。在抗混叠滤波器274中选择的抽头数量与采样频率(例如,39.32mhz)、期望的截止频率或阻带频率(例如,1.23mhz)以及若干其他期望的滤波器特性有关。例如,增加fir滤波器中的抽头数量会降低噪声,减少阻带频率和通带频率之间的过渡带宽,并增加阻带中的衰减。然而,fir滤波器的抽头越多,它的计算量就越大(例如,需要更多的乘法累加)。

209.在一个具体的实施例中,抗混叠滤波器274是一个128抽头的fir滤波器(例如,fir滤波器具有128个频率系数h0

‑

h127),它截断高于1.23mhz的频率(即数字抽取滤波电路248的输出速率)并以39.32mhz的1位adc输出频率运行。39.32mhz的1位adc输出是时域中的1位代码流,此处显示为输入信号x[n],其中x[n]包括n个离散点。在1位代码流上显示为虚线的模拟信号显示了1位输入流如何表示模拟信号的简化示例。如前面的图中所讨论的,数字抽取滤波电路248一次对输入的32个样本进行滤波。为了适应128抽头,可以用零填充32位输入。

[0210]

输入信号在第0级进入抗混叠滤波器274,在那里它与系数h0相乘,并输入到第1级。第1

‑

127级每个都包括z变换符号中的单位延迟z

‑1以提供延迟输入(抽头)到每一级的乘法运算(即,输入信号在延迟z

‑1之后乘以下一个系数(例如,h1

‑

h127))。每个级的乘法运算结果相加(即累加)以创建滤波输出。一系列乘法累加函数也称为移动平均线。抽头越多,输出的计算量就越大。

[0211]

抗混叠滤波器274的输出信号等于其中在本实施例中n为128。输出方程是输入信号与滤波器系数卷积的总和。在时域中,128位代码序列类似于原始模拟信号(为方便起见,此处仅显示20位)并负责高分辨率。然而,在频域中,抗混叠滤波器274仅对信号应用低通滤波器以衰减量化噪声。因此,输出信号现在是模拟输入信号的高分辨率数字版本。

[0212]

图34是抽取器276的一个实施方案的示意框图。抽取器276从这里表示为y[n]=y[0] y[1]

…

y[127]的128抽头抗混叠滤波器274获取输出(注意,为方便起见,插图仅显示了20个样本)并丢弃了每个m计算(例如,其中m是抽取因子)。例如,在抽取因子为32和来自128抽头抗混叠滤波器274的128个样本的输入的情况下,抽取器276输出4个输出y[0] y[1](原为y[31]), y[2](原为y[63]) y[3](原为y[95])。从四个输出的总和中,以大约1.23mhz的输出速率产生一个18位输出。

[0213]

图35是具有频道的频带的实施例。感兴趣的频带280开始于f1并结束于fn。感兴趣的频带280包括以期望的信道间隔255(例如,300hz或另一频率的数据输出速率)隔开的信道282f1

‑

fn。作为特定实施例,感兴趣的频带280包括128个信道,其中每个信道包含具有频率f1

‑

f128的纯音分量s1

‑

s128。信道间隔为300hz(例如,数据输出速率)时,感兴趣的频带

宽度为128x 300hz=38.4khz(即n x信道间隔200hz)。如果f1为100khz,则感兴趣的频带280跨越从100khz到138.4khz。

[0214]

图36是数字抽取滤波电路248的另一个实施方案的示意框图。数字抽取滤波电路248包括抗混叠滤波器274

‑

1到274

‑

n和抽取器276

‑

1到276

‑

n,其中n对应于1位adc输出的n个信道。作为实施例,抗混叠滤波器274

‑

1到274

‑

n是128抽头有限脉冲响应(fir)滤波器。adc输出的n个信道经由n线并行总线284被传送到数字抽取滤波电路248。来自adc的1位数据的每个信道用对应的抗混叠滤波器274

‑

1至274

‑

n进行滤波,并且由相应的抽取器276

‑

1至276

‑

n抽取32的因子,以数字抽取滤波电路248的输出速率产生n个输出。

[0215]

例如,数字抽取滤波电路248从adc取得39.32mhz的1位输出的128个信道,并用抽取因子为32的抗混叠滤波器对每个信道进行滤波,从而以约1.23mhz的采样率产生128个18位输出。例如,128个18位输出被多路复用到以大约157.29mhz运行的单个总线上(即128(27)个信道x输出速率1.23mhz(2

12

x 300hz)或2

19

x 300hz=大约157.29mhz)。作为一个具体的实施例,输出总线是16位总线,有8个空闲时隙(例如,复用8位二进制数的128个信道需要8位)。输出总线以输出速率的128倍运行,以允许每个信道通过每个抗混叠滤波器274

‑

1到274

‑

n并输出到单个总线上。或者,可以并行输出128个18位输出。

[0216]

图37是数字抽取滤波电路248的另一个实施方案的示意框图。与图31

‑

36的128抽头有限脉冲响应(fir)抗混叠滤波器274和抽取器276相比,此处所示的数字抽取滤波电路248包括32个4抽头多相滤波器e0(z)

‑

e

31

(z),系数为e(n)=h(32n l)、n=0

…

3和l=0

…

31。每个多相滤波器包括延迟(z

‑1)和抽取器(

↓

32),产生的结果由求和网络278添加以计算最终输出。

[0217]

在图31

‑

36的实施例中,滤波器响应与完整信号卷积并且刚刚计算的许多点被丢弃(例如,信号被滤波然后被抽取)。多相滤波器是数字抽取滤波电路248的更有效的实现方式,因为可以在滤波之前抽取信号并且不会浪费计算。此外,数字抽取滤波电路中的每个多相滤波器以1.23mhz的较慢数字抽取滤波电路248输出速率运行(与以39.32mhz运行的128fir滤波器相比)。

[0218]

在该实施例中,因为抽取率为32,所以需要32个多相滤波器。数字抽取滤波电路248的输入上的每个样本仅被传送到多相滤波器中的一个。32个1位输入样本(例如,来自39.32mhz的1位adc输出流)被加载到32个多相滤波器,从底部(在第0级)开始并向上工作。加载32个1位样本后,多相滤波器运行以生成单个输出点(例如,1.23mhz下的18位输出)。对接下来的32个样本重复该过程。

[0219]

图38是图37中所示的数字抽取滤波电路248的多相滤波器的实施例的示意框图。每个多相滤波器e0(z)

‑

e

31

(z)包括4个系数(例如,4个抽头)。前面图中讨论的128抽头fir滤波器的频率响应可以重写为每个滤波器e0(z)

‑

e

31

(z)的频率响应的总和。基于抽取因子,产生输出的抽头可以包含在一个滤波器中(例如,e0(z)包括抽头h[0]、h[32]z

‑1、h[64]z

‑2和h[96]z

‑3,每32个点从输入信号中提取数据。然后可以分解输入信号x[n],以便在输入到滤波器e0(z)

‑

e

31

(z)之前抽取信号。例如,x[n]值x[0]、x[32]、x[64]和x[96]被输入到滤波器e0(z)中,它产生抽取所需的值。为了不浪费滤波器完成的计算,其他输入乘以零。求和网络278将滤波器e0(z)

‑

e

31

(z)的结果(例如,y[0]、y[1]、y[2]和y[3])相加,从而以1.23mhz的输出速率产生18位输出。

[0220]

图39是数字抽取滤波电路248的另一个实施方案的示意性框图。在该实施例中,数字抽取滤波电路248通过所示的结构以39.32mhz对1位adc输出的128个信道进行滤波和抽取(以32倍的因子)。与图36中所示的实施例相反,其中每个输入信道需要n个(例如128个)单独的抗混叠滤波器和抽取器,这里每个信道都由相同的滤波器结构处理。为了通过一种结构对128个信道进行滤波和抽取,数字抽取滤波电路248包括32个移位寄存器存储器286、32位移位288、32个4抽头多相滤波器e0‑

e

31

(例如,图37)实现为32个查找表(lut)290和求和树292。

[0221]

每个移位寄存器存储器286包含用于128个信道中的每个信道的5位寄存器。在每个5位寄存器中,其中一位保留用于新输入,而其他4位包含之前的4个二进制输入。存储器以与输出采样率(例如,1.23mz)相同的频率一次一列地写入每个移位存储器注册表286,然而,存储器以输出采样率的128倍的速率(例如,128x1.23mz=157.29mhz)一次一行地读出到滤波器结构中。如图所示,到以输出速率将128位输入到每个移位存储器注册表286时,每个周期有4位输入到每个lut 290中。在此实施例中,抽取因子为32时,每128位输出4位。将参考图40更详细地讨论移位存储器注册表286的结构。

[0222]

位移位288移除输入位并将其他4位重新排列为查找表(lut)290的正确地址线。多相滤波器e0

‑

e31被实现为一组查找表(lut)290。lut 290存储对应于可能输入值的预先计算的乘积值。预先计算的乘积值存储在其地址位置与乘积值对应的输入值的二进制值相同的存储器位置。例如,对于每个多相滤波器e0

‑

e31,4个二进制输入抽头的16种可能组合的输出被预先计算并存储在表中。每个lut从位移位288中获取4位输入,并根据地址确定预先计算的值。每个lut的输出是代表4位输入数据的16位(例如,每抽头(4抽头)每个输入(4)1位)。代表4位输入数据的16位通过求和树292来计算18位最终结果。

[0223]

数字抽取滤波电路248以输出速率的128倍(例如,128

×

1.23mhz=157.29mhz)的速率运行,使得所有128个信道都可以通过相同的结构进行处理,并且所有输出数据都可以在相同的输出总线上进行处理。数字抽取滤波电路248一次处理代表每128个信道的128位的4位。在图36

‑

37的多相滤波器中,32个1位输入样本(例如,来自39.32mhz的1位adc输出流)从底部开始加载到32个多相滤波器中并向上工作。加载32个样本后,多相滤波器运行以生成单个输出点。在这里,来自128个信道中每个信道的1位样本被加载到32个多相滤波器中。因此,图39的滤波器结构以数字抽取滤波电路248数据输出速率的128倍运行。

[0224]

求和树292将多相滤波器(lut 290)的结果相加(例如,来自e0的16位与来自e1的16位相加以产生17位值,等等)以获得在157.29mhz总线上复用的1.23mhz的128个18位输出的最终结果。

[0225]

图40是移位寄存器存储器286的实施例的示意框图。例如,移位寄存器存储器286是双端口5位x 128位装置(例如,静态存取随机存储器(sram)装置),一次写入一列(128位),一次读取一行(5位)。端口a是一个只写端口,具有数据a(128位)的输入和寻址行的地址a(3位)。端口b是只读端口,具有数据b(5位)的输出和用于寻址列的地址b(7位)的输入。移位寄存器存储器286具有锁存输出。

[0226]

每行移位寄存器存储器286是128个1位adc输出信道之一的移位寄存器。在每行的5个抽头中,4个抽头是读出到滤波器结构中的活动数据,第五个抽头保留用于下一个输出样本的输入数据。当图39的滤波器结构的数据到达输入总线时,所有128个信道都在该周期

内被采样。

[0227]

存储器以与输出采样率(例如,1.23mz)相同的频率被写入每个移位存储器注册286,然而,存储器以输出采样率的128倍(例如,128x1.23mz=157.29mhz)读出到滤波器结构中。这允许所有128个信道都由相同的滤波器结构处理,并且所有输出数据都可以多路复用到相同的输出总线上。

[0228]

图41是数字抽取滤波电路248的另一个实施方案的示意框图。图41示出了图39的数字抽取滤波电路248的详细实施例。每128个信道的输入信号按顺序分解以32的抽取率抽取每个信道(例如,如参考图38所讨论的)。例如,移位寄存器存储器1 286写入每个信道的第一位(x[0]),然后写入每个信道的第32位(x[32]),然后写入每个信道的第64位(x[64]),然后写入每个信道的第96位(x[96])。移位寄存器存储器1 286以128倍写入速率(1.23mhz)的速率从每个信道中依次读出一行包含x[0]、x[32]、x[64]和x[96]的数据,从而通过一个滤波器结构对128个信道进行滤波。

[0229]

来自移位寄存器存储器1 286的每个信道的四位数据通过滤波器e0(查找表(lut)290)滤波以产生128个16位输出。例如,e0滤波器包括抽头h[0]、h[32]z

‑1、h[64]z

‑2和h[96]z

‑3。x[0]、x[32]、x[64]和x[96]的输入产生代表这些输入的16位滤波器输出y[0]。移位寄存器存储器2到128的操作与移位寄存器存储器1 286类似。来自每个滤波器e0

‑

e31的每个16位输出通过求和树292以产生一个18位输出。因此,在数字抽取滤波电路128的输出端,128个18位值以在157.29mhz总线上复用的1.23mhz的速率输出(例如,128

×

1.23mhz)。

[0230]

图42是具有n个频道282的频带的实施例。图42类似于图35的实施例,不同之处在于现在感兴趣的频带280通过数字抽取滤波电路248之后与抽取频率fd=1.23mhz进行比较(例如,数字抽取滤波电路248截断在高于1.23mhz的频率处的噪声并将采样率降低到1.23mhz)。感兴趣的频带280开始于f1并结束于fn。感兴趣的频带280包括以期望的信道间隔255(例如,300hz或另一频率的数据输出速率)隔开的信道282f1

‑

fn。信道间隔为300hz(例如,数据输出速率)时,感兴趣的频带宽度为128x300hz=38.4khz(即n x信道间隔300hz)。如果f1为100khz,则感兴趣的频带280跨越从100khz到138.4khz。

[0231]

图43是数字带通滤波器(bpf)电路250的实施方案的示意框图。数字带通滤波器(bpf)电路250包括一个或多个有限脉冲响应(fir)滤波器、一个或多个级联集成梳状(cic)滤波器、一个或多个无限脉冲响应(fir)滤波器、一个或多个抽取级、一个或多个快速傅立叶变换(fft)滤波器、一个或多个离散傅立叶变换(dft)滤波器和/或一个或多个多相滤波器。bpf 250包括多个抽头,其系数被设置为产生近似以模拟参考信号的振荡频率(例如,100khz)为中心的带通区域,并且具有调谐用于对纯音(例如,f1)进行滤波的带宽。bpf 250具有频率响应h(z)。

[0232]

数字bpf电路250取数字抽取滤波电路248的输出(例如,代表频率fl的信号sl的大约1.23mhz的18位输出)并且移至频率fl的带通(例如,100khz)。当数字抽取滤波电路248的输出包括来自不同信道的n个18位输出时(例如,模拟输入信号包括图42的纯音分量f1

‑

fn),每个输出都需要一个数字bpf电路来隔离每个纯音分量。

[0233]

数字bpf电路250应用极窄带通滤波器并输出在300hz的输出频率下具有实分量和虚分量的影响值254(si)。因为嵌入的数据是正弦曲线(例如,纯音),所需的信息位于频率f1并基于幅度和/或相位。因此,带通滤波器可以非常窄(例如,小于0.05倍的信道间隔(例

如,10hz))以捕获所需信号。

[0234]

图44是数字带通滤波器(bpf)电路250的示例频率响应h(z)。作为实施例,数字bpf电路250是具有长度n的离散傅立叶变换(dft)滤波器。例如,数字bpf电路250具有长度4096,以便对4096个18位输入进行滤波以产生1个48位输出。显示了sinx/x(例如,或“sinc”)频率响应。sinc频率响应具有“陷波”响应(例如,当设置为该频率时,它可以拒绝线路频率)。采样频率为1.23mhz,长度为4096,频率区间(即频域中的样本之间的间隔)分辨率为1.23mhz/4096=300hz。陷波位置也与输出数据速率直接相关。如图所示,sinc频率响应在300hz输出数据速率(例如,600hz、900hz、1200hz等)的整数倍处等于零。

[0235]

图45是数字带通滤波器(bpf)电路250的示例频率响应h(z)。有限脉冲响应(fir)滤波器具有如图所示的sinx/x(例如,或“sinc”)频率响应。sinc频率响应具有“陷波”响应(例如,当设置为该频率时,它可以拒绝线路频率)。随着信号s1移至带通,可以应用极窄带通滤波器。例如,使用中心频率为5hz的10hz带通滤波器来隔离纯音。如图所示,图45中的第一陷波位置位于10hz,中心频率为5hz。

[0236]

图46a

‑

46d是由数字带通滤波器(bpf)电路1 250处理信号的实施例。bpf电路1 250包括多个抽头,其系数被设置为产生近似以模拟参考信号s1的振荡频率(例如,100khz)为中心的带通区域,并且带通区域具有调谐的带宽以对具有在f1、f2和f3处的频率分量的数字信号进行滤波。在图46a中,数字bpf电路1250接收数字抽取滤波电路248的输出(例如,代表频率f1的信号s1、频率f2的信号s2和频率f3的信号s3的大约1.23mhz的18位输出)。

[0237]

在图46b中,数字bpf电路1 250将代表频率fl的信号sl、频率f2的信号s2和频率f3的信号s3的大约1.23mhz的18位输出移位到频率fl(例如,100khz)的带通。例如,s1现在处于0hz,而s2和s3与s1均匀间隔(例如,在300hz和600hz)。

[0238]

在图46c中,数字bpf电路1 250应用极窄带通滤波器来隔离sl。因为嵌入的数据是正弦波(例如纯音),所需信息位于频率f1(例如0hz)并基于幅度和/或相位。因此,带通滤波器可以非常窄(例如,小于0.05倍的信道间隔(例如,10hz))以捕获所需信号。

[0239]

在图46d中,数字bpf电路1 250输出在300hz的输出频率下具有实分量和虚分量的影响值254(sl)。影响值254(s1)是48位,具有24位实部和24位虚部。

[0240]

图47a

‑

47d是由数字带通滤波器(bpf)电路2 250处理信号的实施例。bpf电路2 250包括多个抽头,其系数设置为产生近似以模拟参考信号s2的振荡频率(例如,100.3khz)为中心的带通区域,并且带通区域具有调谐的带宽以对纯音(例如,f2)进行滤波。在图47a中,数字bpf电路2250接收数字抽取滤波电路248的输出(例如,代表频率f1的信号s1、频率f2的信号s2和频率f3的信号s3的大约1.23mhz的18位输出).

[0241]

在图47b中,数字bpf电路2 250将代表频率fl的信号s1、频率f2的信号s2和频率f3的信号s3的大约1.23mhz的18位输出移位到频率f2的带通(例如,100.3khz)。例如,s2现在为0hz,s3为300hz。s1可以折叠并与s3或其他频率对齐。

[0242]

在图47c中,数字bpf电路2 250应用极窄带通滤波器来隔离s2。因为嵌入的数据是正弦曲线(例如纯音),所需的信息位于频率f2(例如0hz)并基于幅度和/或相位。因此,带通滤波器可以非常窄(例如,小于0.05倍的信道间隔(例如,10hz))以捕获所需信号。

[0243]

在图47d中,数字bpf电路2 250输出在300hz的输出频率下具有实分量和虚分量的影响值254(s2)。影响值254(s2)是48位,具有24位实部和24位虚部。

[0244]

图48是数字带通滤波器(bpf)电路250的实施方案的示意框图。数字bpf电路250包括一个或多个有限脉冲响应(fir)滤波器、一个或多个级联集成梳状(cic)滤波器、一个或多个无限脉冲响应(fir)滤波器、一个或多个抽取级、一个或多个快速傅立叶变换(fft)滤波器、一个或多个离散傅立叶变换(dft)滤波器和/或一个或多个多相滤波器。

[0245]

使用dft滤波器实施例,bpf电路250从数字抽取滤波电路248接收n个信道的输出(例如,在以大约157.29mhz运行的16位总线上以大约1.23mhz的128个18位输出)并且在每个信道上一次以两个频率(例如,自电容频率和笔频率)进行长度为n的离散傅立叶变换计算(例如,具有同步输出的频率响应)。数字bpf电路250以两倍于输入总线的速度(例如,2

20

×

300hz=314.57mhz)运行以计算每个输入的两个频率。

[0246]

离散傅立叶变换(dft)将复数序列变换成另一个复数序列。接收到的每个18位输入代表一个频率的复数。一个18位输入被馈送到两个单独的乘法器,在乘法器中输入与dft的实数或虚数系数相乘。系数处理器对于每个频率预先计算dft的实部和虚部。将参考图52更详细地讨论系数处理器。

[0247]

对于输入的每个实部和虚部,bpf电路250应用乘法累加函数。例如,实部系数294乘以输入并由累加器302累加。当为所有输出(例如,128个信道x 2个频率=256个输出)计算最终结果时,最终结果被移位到输出缓冲器304和实分量值298(例如,24位)以300hz输出。同样,虚部系数296乘以输入并由累加器302累加。当对于所有输出(128个信道x 2个频率=256个输出)计算最终结果时,最终结果被移位到输出缓冲器304和虚分量值300(例如,24位)以300hz输出。因此,bpf电路对来自数字抽取滤波电路248的n个输出进行滤波以产生具有实分量值298和虚分量值300的1个输出,并以两倍于输入的速度运行,以便对于每个信道输出两个频率的结果。

[0248]

图49是模数转换电路246的另一个实施方案的示意框图,其包括模数转换器(adc)电路1

‑

n 258、数字滤波抽取电路248、第一带通滤波器(bpf)电路250、第二bpf电路250、系数处理器306和处理模块252。

[0249]

adc电路1

‑

n 258可以是先前附图的驱动感测电路28的adc转换器212和/或任何常规adc(例如,快速adc、逐次逼近adc、斜坡比较adc、wilkinson adc、积分adc和/或增量编码adc)。adc电路258可以通过1位adc西格玛

‑

德尔塔调制器和数字抽取滤波电路248(例如,西格玛

‑

德尔塔adc)的组合来实现。图49根据前面的实施例操作,除了第一bpf电路250可操作以处理来自数字滤波抽取电路248的输出,其中频率是已知的,并且第二bpf电路250可操作以处理来自数字滤波抽取电路248的输出,其中频率可根据感兴趣区域(roi)通过处理模块252来选择。

[0250]

例如,在每n个信道的两个点处测量互电容(例如,256个频率,其中n等于128)。处理模块252基于给定的交叉点或基于始终开启的自身频率和笔频率的结果在特定点处选择对哪些交叉点进行采样。处理模块252将所选择的频率310输入到第二bpf 250中并且系数处理器306基于所选择的频率预先计算用于第二bpf 250的系数。将参考图51更详细地讨论第二bpf 250。

[0251]

在触摸屏的每n个电极(例如,128个电极,其中n等于128)的一个点(例如,一个频率)处测量自电容并且在一个点(例如,一个频率)处测量笔电容(在相同的n个电极上一个频率)。这些频率是系统已知的,因此处理模块252将已知频率308输入系数处理器306以预

先计算第一bpf250的系数。将参考图50更详细地讨论第一bpf 250。

[0252]

第一bpf 250输出代表自电容和笔电容值的第一影响值254(例如,第一bpf 250以两倍于输入总线的速度运行以对每个信道的两个频率进行滤波,如图48中所讨论的)。第二bpf 250输出代表互电容值的第二影响值254。处理模块252解释影响值254的虚分量和实分量以产生数据输出256。影响值254是向量(即,相量复数),其具有代表具有峰值量值(即幅度)和方向(即相位)的正弦函数。例如,影响值254是48位值,每个值具有24位实分量和24位虚分量。在复数域中,电压和电流是相量,所有电阻、电容和电感都用复数阻抗代替(例如,z

r

=r、z

l

=jfl,和zc=1/(jfc)=

‑

j/(fc))。

[0253]

由于信道的阻抗主要基于其电容(自电容、笔电容和/或互电容),随着固定电容的频率增加,阻抗会根据1/2πfc降低,其中f是频率,c是电容。由于电压(v)=电流(i)*阻抗(z),处理模块252根据影响值254的电压和电流向量确定电容或其他阻抗值(例如,阻抗的降低使恒定电流的电压增加,增加恒定电压的电流,或增加信号分量的电压和电流)。阻抗的增加和/或减少代表输入数据。所确定的阻抗值或阻抗值的变化以300hz的示例输出速率作为数据输出256输出。

[0254]

图50是第一带通滤波器(bpf)电路250的实施方案的示意框图。第一bpf电路250是一个或多个离散傅立叶变换(dft)或快速傅立叶变换(fft)滤波器,其接收来自数字抽取滤波电路248的n个(例如,128个)输出信道(例如,在以大约157.29mhz运行的16位总线上大约1.23mhz的128个18位输出),并且一次两个频率地在每个信道上计算长度n=4096的离散傅立叶变换(例如,自电容频率和笔频率)。数字bpf电路250以两倍于输入总线的速度(例如,2

20

×

300hz=314.57mhz)运行以计算每个输入的两个频率。

[0255]

离散傅立叶变换将n个复数序列(例如,{x

n

}=x0,x1,

…

,x

n

‑1)转换为另一个复数序列(例如,{x

k

}=x0,x1,

…

,x

n

‑1),其中),其中根据欧拉公式,也可以表示为为

[0256]

对于每个18位输入,由系数处理器306为每个频率预先计算的实部和虚部。将参照图52更详细地讨论系数处理器306。

[0257]

例如,实部系数w

n

cos(2πω

s

n)(对于自频(fs)输入ω

s

,其中)和w

n

cos(2πω

p

n)(对于笔频率(fp)输入ω

p

,其中)由系数处理器306预先计算并被多路复用以与来自左侧所示的数字抽取滤波电路248的正确的18位输出相乘。虚部系数

‑

w

n

sin(2πω

s

n)(对于自频(fs)输入ω

s

,其中)和

‑

w

n

sin(2πω

p

n)(对于笔频(fp))输入ω

p

,其中)由系数处理器306预先计算并且被多路复用以与来自右侧所示的数字抽取滤波电路248的正确的18位输出相乘。

[0258]

第一bpf电路250包括4个18

×

18乘法器(例如,每个频率每边2个),用于将来自数字抽取滤波电路248的18位与来自系数处理器的18位相乘。第一bpf电路250包括4个30位有符号累加器302(例如,每个频率每边2个),具有256个输出寄存器,用于将相乘的值相加。第

一bpf电路250还包括4个256

×

24位输出缓冲器304(例如,每频率每边2个)。例如,输出缓冲器304是具有只写端口和只读端口的两端口静态存取随机存储器(sram)。

[0259]

第一bpf电路250计算接收到的所有256个18位值(例如,128个信道x 2个频率)的最终乘积并将最终结果移位到输出缓冲器304。输出缓冲器304输出24位实分量值298以及24位虚分量值300以300hz输出到处理模块252。

[0260]

图51是第二带通滤波器(bpf)电路250的实施方案的示意框图。第二bpf电路250是一个或多个离散傅立叶变换(dft)或快速傅立叶变换(fft)滤波器,其接收来自数字抽取滤波电路248的n个(例如,128)个输出信道(例如,在以约157.29mhz运行的16位总线上以约1.23mhz的128个18位输出)并且一次两个频率地在每个信道上计算长度为n=4096的离散傅立叶变换(例如,每个信道有两个互频率)。数字bpf电路250以两倍于输入总线的速度(例如,2

20

×

300hz=314.57mhz)运行以计算每个输入的两个频率。

[0261]

第二bpf电路250可操作以处理来自数字滤波抽取电路248的输出,其中频率可根据感兴趣区域(roi)来选择。例如,在每n个信道的两个点测量互电容(例如,256个频率,其中n等于128)。处理模块252基于给定的交叉点或基于始终开启的自身频率和笔频率的结果在特定点处选择对哪些交叉点进行采样。处理模块252将选择的频率输入到第二bpf 250的输出映射316中。

[0262]

例如,输出映射316是256

×

12位的二端口静态存取随机存储器(sram),其具有与处理模块接口的只写端口以及只读端口。处理模块用每个频率的12位地址(例如,信道号的7位地址326和频率索引的5位地址328)填充256个条目的输出映射316。输入缓冲器312是双缓冲的(与第一bpf电路250相比),因此信道可以顺序加载和随机时钟输出。例如,输入缓冲器312是具有只写端口和只读端口的256

×

18位二端口sram。因为输入是双缓冲的,所以第二bpf电路250将比第一bpf电路250多一个周期的延迟(例如,在300hz)。

[0263]

在每个求和步骤,计数器314时钟通过256个交叉点。每个交叉点选择与系数处理器306计算的频率之一对应的线和系数。系数处理器306基于所选频率预先计算第二bpf 250的系数。例如,互频率有34个可能的频率值。因此,系数处理器306为34种可能性中的每一种计算实数和虚数系数并将这些值存储在查找表中。

[0264]

系数处理器306将实系数输入系数查找表(lut)318并将虚系数输入系数lut 320。每个系数lut 318和320是具有只读端口和只写端口的34x 18位两端口sram。对应于所选频率的5位地址328被输入到每个系数lut 318和320,并用于为输入选择正确的系数。系数lut 318向乘法器输入18位实系数,以乘以来自数字滤波抽取电路248的18位输入值。系数lut 320将18位虚系数输入到示意图右侧的第二乘法器乘以来自数字滤波抽取电路248的18位输入值。

[0265]

第二bpf 250的其余部分与第一bpf电路250类似地操作。第二bpf电路250包括4个18

×

18个乘法器(例如,每个频率每边2个),用于将来自数字抽取滤波电路248的18位与来自系数lut 318和320的18位相乘。第二bpf电路250包括4个30位有符号累加器302(例如,每频率每边2个),具有256个输出寄存器,用于将相乘的值相加。第二bpf电路250还包括4个256

×

24位输出缓冲器304(例如,每频率每边2个)。例如,输出缓冲器304是具有只写端口和只读端口的两端口sram。第二bpf电路250计算接收到的所有256个18位值(例如,128个信道x 2个频率)的最终乘积并将最终结果移位到输出缓冲器304。输出缓冲器304输出24位实分

量值322和24位虚分量值324以300hz输出到处理模块。

[0266]

图52是系数处理器306的实施方案的示意框图。系数处理器306包括“nk”锁存器、 1024、函数多路复用器、余弦查找表330、频率查找表332、0.5

‑

0.5x、“w

n”锁存器、计数器334、两个多路复用器和系数处理器乘法器336。频率查找表332是34x 12位的两端口静态存取随机存储器(sram),其由处理模块填充有34个可能的频率选项。余弦查找表330是1.17定点4096

×

16位查找表(例如,只读存储器(rom))。系数处理器乘法器336是一个18

×

18位有符号乘法器。

[0267]

如前所述,离散傅立叶变换(dft)将n个复数序列(例如,{x

n

}=x0,x1,

…

,x

n

‑1)转换为另一个复数序列(例如,{x

k

}=x0,x1,

…

,x

n

‑1),其中根据欧拉公式,也可以表示为拉公式,也可以表示为

[0268]

对于每个18位输入,系数处理器306为每个频率预先计算的实部和虚部。

[0269]

例如,bpf电路250的每个输入可能有34种可能的频率选项。对于34个频率选项中的每一个,预先计算每个实部系数w

n

cos(2πωn)(对于频率输入ω,其中)和每个虚部系数

‑

w

n

sin(2πωn)(对于频率输入ω,其中)由系数处理器306。

[0270]

系数处理器306以比bpf电路250大1的n的速率运行,使得它总是比bpf电路250提前一个周期。对于n的每个值,(其以1.23mhz的输入采样速率运行),系数处理器306进行以下计算:1)w

n

=0.5

‑

0.5cos(2πn/n),并且对于34个频率可能性(k)中的每一个:1)kn mod 4096,2)w

n

cos(2πkn/n),和3)

‑

w

n

sin(2πkn/n)。为了完成这个,系数处理器乘法器336以输入采样率的n倍运行(例如,当n为128时,128

×

1.23mhz=157.29mhz)。

[0271]

计数器334从0到4095,将“n”的值输入到功能多路复用器和与w

n

锁存器相连的多路复用器中。kn锁存器将kn值输入到cos(2πkn/n)和

‑

sin(2πkn/n)函数的函数多路复用器。kn加1024值也被输入到功能多路复用器。根据时钟周期,选择一个函数(例如,cos(2πkn/n)、

‑

sin(2πkn/n)或cos(2πn/n))。所选择的函数被输入到余弦查找表330中以查找该函数的特定值。

[0272]

如果选择的函数不包括k,则余弦查找表330的特定值被馈送到0.5

‑

0.5x,其中w

n

=0.5

‑

0.5cos(2πn/n)的值被计算并输出到w

n

锁存器。w

n

锁存器输出一个值并与计数器334输出复用。当函数确实包括k时,所选函数被输入到余弦查找表330中以查找该函数的特定值。然后将特定值与来自频率查找表332的输出(k)一起输入到多路复用器中。在一个时钟周期上,cos(2πkn/n)或

‑

sin(2πkn/n)的特定值被输入到系数处理器乘法器336与w

n

值相乘。计算出的系数被转换为18位,然后输出到bpf电路250。

[0273]

在不同的时钟周期,来自频率查找表332的k值被输入到系数处理器乘法器336以与来自计数器334的值n相乘。kn值被输入到kn锁存器中用于下一组计算。

[0274]

图53是模数转换电路246的另一实施方案的示意框图,其包括模数转换器(adc)电路1

‑

n 258、数字滤波抽取电路248、笔带通滤波器(bpf)电路338、自bpf电路340、系数处理

器306、互bpf电路342和处理模块252。

[0275]

除了以输入总线的速度运行的两个bpf滤波器(例如,笔bpf电路338和自bpf电路340)代替一个bpf电路250(例如,第一bpf电路250)以两倍于输入总线的速度运行以便一次计算两个频率之外,图53的操作类似于图49的实施例。笔bpf电路338和自bpf电路340处理来自数字滤波抽取电路248的输出,其中频率是已知的(例如,自测量和笔测量始终开启),并且互bpf电路342可操作以处理来自数字滤波抽取电路248的输出,其中频率可根据感兴趣区域(roi)进行选择。

[0276]

例如,在每n个电极的两个点处测量互电容(例如,256个频率,其中n等于128)。处理模块252基于给定的交叉点或基于始终开启的自频率和笔频率的结果在特定点处选择对哪些交叉点进行采样。处理模块252将频率310的选择输入到相互bpf电路342中,并且系数处理器306基于所选择的频率预先计算互bpf电路342的系数。

[0277]

自电容是在每n个电极的一个点(例如,频率)处测量的,并且笔电容是在每n个电极(例如,一个频率)的一个点处测量的。这些频率是系统已知的,因此处理模块252将已知频率308输入系数处理器306以预先计算笔bpf电路338和自bpf电路340的系数。

[0278]

笔bpf电路338输出代表笔电容值的笔影响值。自bpf电路340输出代表自电容值的自影响值。互bpf电路342输出代表互电容值的互影响值。处理模块252解释影响值的虚分量和实分量以产生300hz的数据输出256。影响值254是具有实分量和虚分量的向量(即,相量复数),表示具有峰值量值(即,幅度)和方向(即,相位)的正弦函数。例如,影响值254是48位值,每个值具有24位实分量和24位虚分量。在复数域中,电压和电流是相量,所有电阻、电容和电感都用复数阻抗代替(例如,z

r

=r、z

l

=jfl和z

c

=1/(jfc)=

‑

j/(fc))。

[0279]

由于信道的阻抗主要基于其电容(自电容、笔电容和/或互电容),随着固定电容的频率增加,阻抗基于1/2πfc降低,其中f是频率和c是电容。由于电压(v)=电流(i)*阻抗(z),处理模块252根据影响值的电压和电流向量确定电容或其他阻抗值(例如,阻抗的降低增加了恒定电流的电压,增加恒定电压的电流,或增加信号分量的电压和电流)。阻抗的增加和/或减少代表输入数据。所确定的阻抗值或阻抗值的变化以300hz的示例输出速率作为数据输出256输出。

[0280]

图54是处理模块252控制模数转换电路246内的一个实施方案的示意框图。模数转换电路246是一个受限数据通信系统,其中所有变量都由处理模块252设定,并且被控制进行所需的数据处理。处理模块252可操作以控制模数转换电路246的每一级以产生期望的输出256。

[0281]

例如,处理模块252通过参考生成电路344(例如,参考信号发生器149)为每个振荡参考信号设置频率和波形以产生模拟参考信号346。dc分量输入数据348嵌入在每个模拟参考中信号346中。处理模块252还设置adc 258的采样率。adc 258处理包含模拟参考信号和dc分量的模拟信号,并将代表信号350输出到数字滤波级352(例如,数字抽取滤波电路248和数字bpf电路250)。

[0282]

处理模块252确定每个滤波器的级(例如,抽头)、采样频率、滤波器带宽和任何其他期望的滤波器参数。处理模块252基于期望的输出速率、期望的线性度和其他因素来确定数字滤波参数。处理模块252将已知频率和互频率选择输入到用于数字bpf滤波器的系数处理器中。

[0283]

数字滤波级352产生将在数据处理354级由处理模块252解释的影响值254。处理模块252基于数据输出速率和输入数据348的性质设置数据解释参数。

[0284]

例如,输入数据348可以传达电流(i)、电压(v)或阻抗(z)变化中的一个或多个。例如,如果输入是具有恒定电流的电压测量值,则处理模块252可以分析电压变化以确定阻抗变化值。基于数据解释参数,处理模块252解释影响值254并产生经处理的输出数据256。

[0285]

如可在本文中使用的,术语“基本上”和“大约”为其对应的术语和/或项目之间的相关性提供了行业接受的容差。对于某些行业,行业接受的容差小于1%,而对于其他行业,行业接受的容差为10%或更高。行业接受的容差的其他示例范围从小于1%到50%。行业接受的容差对应于但不限于组件值、集成电路工艺变化、温度变化、上升和下降时间、热噪声、尺寸、信号误差、丢包、温度、压力、材料成分和/或性能指标。在行业内,可接受容差的容差差异可能大于或小于一个百分比水平(例如,小于 /

‑

1%的尺寸公差)。项目之间的某些相关性的范围可能从小于一个百分比水平到几个百分比的差异。项目之间的其他相关性可能从几个百分点的差异到差异的量值不等。

[0286]

如本文还可以使用的,术语“配置为”、“可操作地耦合到”、“耦合到”和/或“耦合”包括项目之间的直接耦合和/或项目之间经由中间项目(例如,项目包括但不限于组件、元件、电路和/或模块)的间接耦合,其中,例如间接耦合,中间项目不修改信号的信息,但可以调整其电流电平、电压电平和/或功率电平。如这里可以进一步使用的,推断耦合(即,其中一个元素通过推断耦合到另一元素)包括以与“耦合到”相同的方式在两个项目之间的直接和间接耦合。

[0287]

如本文还可以进一步使用的,术语“被配置为”、“可操作以”、“耦合到”或“可操作地耦合到”指示项目包括电源连接、输入(多个)、输出(多个)等中的一个或多个,以在被激活时执行其对应的一个或多个功能,并且还可以包括对一个或多个其他项目的推断耦合。如本文还可以进一步使用的,术语“关联于”包括单独项目的直接和/或间接耦合和/或一个项目嵌入另一项目中。

[0288]

如可在本文中使用的,术语“有利地比较”表示两个或更多个项目、信号等之间的比较提供了期望的关系。例如,当期望的关系是信号1的量值大于信号2的幅度时,当信号1的量值大于信号2的量值或信号2的量值小于信号1的量值时,可以实现有利的比较。如本文所用,术语“不利地比较”表示两个或更多个项目、信号等之间的比较未能提供所需的关系。

[0289]

如可在本文中使用的,一项或多项权利要求可以在该通用形式的特定形式中包括短语“a、b和c中的至少一个”或该通用形式中的“a、b和c中的至少一个”,具有比“a”、“b”和“c”更多或更少的元素。在任何一种措辞中,短语的解释都相同。特别地,“a、b和c中的至少一个”等同于“a、b或c中的至少一个”并且应表示a、b和/或c。例如,它的意思是:仅“a”,仅“b”,仅“c”,“a”和“b”,“a”和“c”,“b”和“c”,和/或“a”、“b”和“c”。

[0290]

如本文还可以使用的,术语“处理模块”、“处理电路”、“处理器”、“处理电路系统”和/或“处理单元”可以是单个处理装置或多个处理装置。这种处理装置可以是微处理器、微控制器、数字信号处理器、微型计算机、中央处理单元、现场可编程门阵列、可编程逻辑装置、状态机、逻辑电路、模拟电路、数字电路和/或任何基于电路和/或操作指令的硬编码来操纵信号(模拟和/或数字)的装置。处理模块、模块、处理电路、处理电路系统和/或处理单元可以是或进一步包括存储器和/或集成存储器元件,其可以是单个存储器装置、多个存储

器装置,和/或另一个处理模块、模块、处理电路、处理电路系统和/或处理单元的嵌入式电路。这种存储器装置可以是只读存储器、随机存取存储器、易失性存储器、非易失性存储器、静态存储器、动态存储器、闪存、高速缓冲存储器和/或任何存储数字信息的装置。注意,如果处理模块、模块、处理电路、处理电路系统和/或处理单元包括一个以上的处理装置,则处理装置可以位于中央(例如,通过有线和/或无线总线结构直接耦合在一起)或者可以分布式地定位(例如,通过经由局域网和/或广域网的间接耦合的云计算)。进一步注意,如果处理模块、模块、处理电路、处理电路系统和/或处理单元通过状态机、模拟电路、数字电路和/或逻辑电路实现其一个或多个功能,则存储相应操作指令的存储器和/或存储器元件可以嵌入在包括状态机、模拟电路、数字电路和/或逻辑电路的电路系统内部或外部。还要注意的是,存储器元件可以存储对应于一个或多个图中所示的步骤和/或功能中的至少一些的硬编码和/或操作指令,并且处理模块、模块、处理电路、处理电路系统和/或处理单元执行对应于一个或多个图中所示的步骤和/或功能中的至少一些的硬编码和/或操作指令。这样的存储装置或存储器元件可以包括在制品中。

[0291]

一个或多个实施方案已经在上面借助于示出指定功能的性能及其关系的方法步骤进行了描述。为便于描述,本文已任意定义了这些功能构建块和方法步骤的边界和序列。只要适当地执行指定的功能和关系,就可以定义替代边界和序列。因此,任何此类替代边界或序列都在权利要求的范围和精神内。此外,为了便于描述,已经任意定义了这些功能构建块的边界。只要适当地执行某些重要功能,就可以定义替代边界。类似地,此处也可以任意定义流程图块以说明某些重要功能。

[0292]

就所使用的程度而言,流程图块边界和序列可以以其他方式定义并且仍然执行某些重要功能。功能构建块和流程图块和序列的这种替代定义因此在权利要求的范围和精神内。本领域普通技术人员还将认识到,功能构建块以及本文中的其他说明性块、模块和组件可以如所示出的或通过分立组件、专用集成电路、执行适当软件的处理器等或任何其组合来实现。

[0293]

此外,流程图可以包括“开始”和/或“继续”指示。“开始”和“继续”指示反映了所呈现的步骤可以任选地并入一个或多个其他例程或以其他方式与一个或多个其他例程结合使用。此外,流程图可以包括“结束”和/或“继续”指示。“结束”和/或“继续”指示反映了所呈现的步骤可以如所描述和所示那样结束或者任选地并入一个或多个其他例程或以其他方式与一个或多个其他例程结合使用。在此上下文中,“开始”表示所呈现的第一步骤的开始,并且可以在未具体显示的其他活动之前。此外,“继续”指示反映了所呈现的步骤可以被多次执行和/或可以被未具体示出的其他活动接续。此外,虽然流程图指示步骤的特定顺序,但只要保持因果关系的原则,其他顺序同样是可能的。

[0294]

这里使用一个或多个实施方案来说明一个或多个方面、一个或多个特征、一个或多个概念和/或一个或多个实施例。设备、制品、机器和/或过程的物理实施方案可以包括参考本文讨论的一个或多个实施方案描述的一个或多个方面、特征、概念、实施例等。此外,在各个图中,实施方案可以包含相同或相似命名的功能、步骤、模块等,这些功能、步骤、模块等可以使用相同或不同的附图标记,因此,功能、步骤、模块等可以是相同或相似的功能、步骤、模块等或是不同的功能、步骤、模块。

[0295]

虽然上述图中的晶体管被示为场效应晶体管(fet),但如本领域普通技术人员将

理解的,可以使用任何类型的晶体管结构来实现晶体管,包括,但不限于,双极型金属氧化物半导体场效应晶体管(mosfet)、n阱晶体管、p阱晶体管、增强型、耗尽型和零电压阈值(vt)晶体管。

[0296]

除非相反地特别说明,到达、来自和/或在本文呈现的任何图的图中的元件之间的信号可以是模拟或数字、连续时间或离散时间、以及单端或差分。例如,如果信号路径显示为单端路径,则它也代表差分信号路径。同样,如果信号路径显示为差分路径,则它也代表单端信号路径。虽然本文描述了一种或多种特定架构,但同样可以实现使用一种或多种未明确示出的数据总线、元件之间的直接连接和/或本领域普通技术人员所认识到的其他元件之间的间接耦合的其它架构。

[0297]

在一个或多个实施方案的描述中使用术语“模块”。模块通过诸如处理器或其他处理装置或其他硬件的装置来实现一个或多个功能,这些装置可以包括存储操作指令的存储器或与其相关联地操作。模块可以独立运行和/或与软件和/或固件结合运行。还如本文所使用的,模块可以包含一个或多个子模块,每个子模块可以是一个或多个模块。

[0298]

如本文中可进一步使用的,计算机可读存储器包括一个或多个存储元件。存储器元件可以是单独的存储器装置、多个存储器装置或存储器装置内的一组存储器位置。这种存储器装置可以是只读存储器、随机存取存储器、易失性存储器、非易失性存储器、静态存储器、动态存储器、闪存、高速缓冲存储器和/或任何存储数字信息的装置。存储器装置可以是固态存储器、硬盘驱动器存储器、云存储器、拇指驱动器、服务器存储器、计算装置存储器和/或用于存储数字信息的其他物理介质的形式。

[0299]

虽然一个或多个实施方案的各种功能和特征的特定组合已经在本文中进行了明确描述,但是这些特征和功能的其他组合同样是可能的。本公开不受本文公开的特定实施例的限制并且明确地结合了这些其他组合。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。