1.本公开涉及电力线通信领域,具体地,涉及一种频率调整电路、方法及通信设备。

背景技术:

2.晶体谐振器因具有高精度和高稳定度的性能,被广泛应用于通信传输等技术领域。其中,电力线通信过程中,因为发射机和接收机之间晶体谐振器的频率不完全同步,使得接收机接收到的信号与发射机发送的信号之间存在采样频率偏差,而采样频率偏差随着时间的积累使得接收机接收的数据包错误。

3.相关技术中,申请公布号为(cn113037219a)和(cn113037215a)的发明专利申请均提供了一种晶振控制电路,发明专利申请(cn113037219a)提供的晶振控制电路的信号处理模块对接收到的第一时钟信号进行预设处理得到第二时钟信号,并将第二时钟信号输出至电容阵列控制模块;电容阵列控制模在第二时钟信号控制下生成第一控制信号,并将第一控制信号输出至电容阵列模块;电容阵列模块在第一控制信号的控制下,设定晶振起振的初始电容值,晶振波形达到预设幅度时,通过每次增加设定电容值来控制负载电容达到目标电容值,从而调节晶振的起振波形和振荡频率。发明专利申请(cn113037215a)提供的晶振控制电路的晶振驱动模块为晶振提供驱动能量并将晶振产生的第一时钟信号输出至频率输出模块和电容阵列控制模块;电容阵列控制模块在第一时钟信号的控制下生成控制信号,该控制信号用于调节电容阵列模块的电容值,从而平滑控制晶振的输出频率和功耗。授权公告号为(cn101924534b)的发明专利提供的晶体振荡器的数字控制电容开关阵列单调调谐方法,数字译码电路直接将输入数字控制位转变为开关阵列的实际控制信号,开关阵列中每个开关对应控制多层金属叉指电容阵列的一个电容单元,通过开关阵列中各开关的打开与关断调节多层金属叉指电容阵列中接入晶体振荡器的电容单元的数量,即调节晶体振荡器中总电容大小,从而实现晶体振荡器的单调调谐。可见相关技术中大部分是通过调节电容阵列模块的电容实现对晶振频率的控制,但随着晶振的负载电容的不断增大,使得晶振频率的步长不一致,导致晶振的可调节范围受限,无法保证发射机与接收机的频率一致,而负载电容的减小会导致频率的增加,反之负载电容的增加会导致频率的减小。

4.相关技术中还可以通过芯片io输入一个标准频率的方波,利用数字算法计算晶振频率和标准频率的偏差,调整晶体谐振器的负载电容大小来微调晶振的负载谐振频率。但标准频率的方波存在(

‑

2ppm

‑

2ppm)的频率偏差,难以根据标准频率进行调频,实现精准的频率校准,从而导致发射机与接收机之间仍存在采样频率偏差,从而导致数据传输错误。

技术实现要素:

5.本公开的目的是提供一种频率调整电路、方法及通信设备,解决了相关技术中因发射机与接收机之间的采样频率偏差导致的数据包接收错误的技术问题。

6.为了实现上述目的,第一方面,本公开提供一种频率调整电路,所述电路包括晶体谐振器、起振电路以及可编程电容阵列,所述晶体谐振器与所述起振电路并联,所述可编程

电容阵列与所述晶体谐振器连接,所述可编程电容阵列包括多个依次并联的电容阵列,每一所述电容阵列能够独立工作,所述可编程电容阵列中每一次用于编码的目标电容阵列是根据待输出编码中的部分比特位的取值确定的。

7.可选地,所述电路包括两个可编程电容阵列的情况下,第一所述可编程电容阵列的一端与所述晶体谐振器的晶振输入引脚连接,第一所述可编程电容阵列的另一端接地;第二所述可编程电容阵列的一端与所述晶体谐振器的晶振输出引脚连接,第二所述可编程电容阵列的另一端接地。

8.可选地,所述电路包括两个以上所述可编程电容阵列的情况下,各所述可编程电容阵列依次串联后接入所述晶体谐振器的晶振输入引脚与晶振输出引脚之间。

9.可选地,所述可编程电容阵列包括粗调子电路以及与所述粗调子电路并联的细调子电路;所述细调子电路包括分段温度计码译码器以及与所述分段温度计码译码器连接的分段温度计码细调电容阵列,所述粗调子电路包括分段二进制码译码器以及与所述分段二进制码译码器连接的分段二进制码粗调电容阵列;所述细调子电路以及所述粗调子电路均能输出独立编码,所述分段温度计码细调电容阵列以及所述分段二进制码粗调电容阵列中每一次用于编码的目标电容阵列是根据待输出编码中的部分比特位的取值确定的。

10.可选地,所述分段温度计码细调电容阵列包括多个依次并联的第一电容子电路,各所述第一电容子电路包括依次串联的电容以及控制开关。

11.可选地,所述分段二进制码粗调电容阵列包括多个依次并联的电容阵列,且各所述电容阵列的单位电容依次增大。

12.可选地,所述分段二进制码粗调电容阵列中的所述电容阵列包括多个依次并联的第二电容子电路,各所述第二电容子电路包括依次串联的电容以及控制开关。

13.可选地,所述控制开关的断开以及闭合根据待输出编码中的部分比特位的取值确定。

14.第二方面,本公开提供一种频率调整方法,由第一方面所述的频率调整电路执行,所述方法包括:获取接收机与发送端各待调整的晶体谐振器的频率与预设标准频率的频率偏差,根据所述频率偏差对各所述晶体谐振器的频率进行出厂校准;获取出厂校准后所述接收机与发送端的晶体谐振器之间的采样频率偏差,根据所述采样频率偏差对各所述晶体谐振器的频率进行通信校准。

15.第三方面,本公开提供一种通信设备,包括第一方面所述的频率调整电路。

16.通过上述技术方案,本公开中通过编码控制可编程电容阵列进行分段拟合直线,线性化晶体谐振器的牵引灵敏度,保证晶体谐振器的频率随控制编码控制单调性,实现对频率步长的精确校准,保证了发射机与接收机之间数据的正确传输。

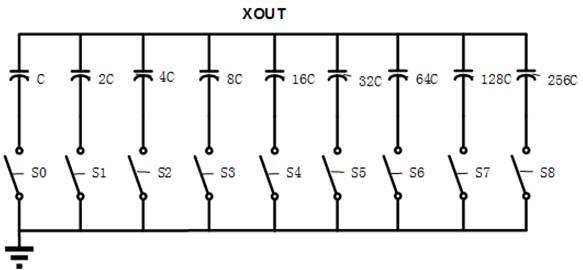

17.本公开的其他特征和优点将在随后的具体实施方式部分予以详细说明。

附图说明

18.附图是用来提供对本公开的进一步理解,并且构成说明书的一部分,与下面的具

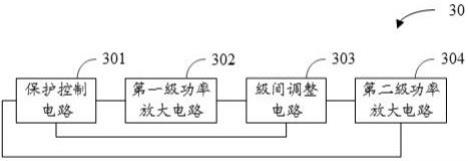

体实施方式一起用于解释本公开,但并不构成对本公开的限制。在附图中:图1是根据一示例性实施例示出的一种频率调整电路的示意图;图2是根据一示例性实施例示出的相关技术中频率调整电路的示意图;图3是根据一示例性实施例示出的一种频率调整电路中可编程电容阵列的示意图;图4是根据一示例性实施例示出的一种频率调整电路中分段温度计码细调电容阵列的示意图;图5是根据一示例性实施例示出的一种频率调整电路中分段二进制码粗调电容阵列的示意图;图6是根据一示例性实施例示出的根据频率调整电路得到的仿真效果图;图7是根据一示例性实施例示出的一种频率调整方法的流程图;图8是根据一示例性实施例示出的一种通信设备的框图。

具体实施方式

19.这里将详细地对示例性实施例进行说明,其示例表示在附图中。下面的描述涉及附图时,除非另有表示,不同附图中的相同数字表示相同或相似的要素。以下示例性实施例中所描述的实施方式并不代表与本公开相一致的所有实施方式。

20.需要说明的是,在本公开中,说明书和权利要求书以及附图中的术语“s101”、“s102”等用于区别步骤,而不必理解为按照特定的顺序或先后次序执行方法步骤。

21.以下结合附图对本公开的具体实施方式进行详细说明。应当理解的是,此处所描述的具体实施方式仅用于说明和解释本公开,并不用于限制本公开。

22.正如背景技术所言,相关技术中,通过二进制编码调整晶体谐振器(以下简称晶振)的负载电容大小,来微调发射机和接收机中晶振的负载谐振频率,使得发射机和接收机的频率一致从而进行数据传输,或通过io输入一个标准频率的方波,利用数字算法计算晶振频率和标准频率的偏差,调整晶体谐振器的负载电容大小来微调晶振的负载谐振频率。

23.其中,通过二进制编码调整晶振的负载电容大小时,微调负载电容c

l

导致负载谐振频率f

l

的频率变化可以用牵引灵敏度表示,具体计算式如下:但二进制编码最小时,晶振频率牵引灵敏度最大,但随着二进制编码增大,电容阵列中被选中的电容越多,晶振频率牵引灵敏度越小,参照图2,电容阵列包括:开关s0一端接地,一端接电容c的下端,电容c的上端接晶振输出引脚xout(以下简称xout);开关s1一端接地,一端接电容2c的下端,电容2c的上端接xout;开关s2一端接地,一端接电容4c的下端,电容4c的上端接xout;开关s3一端接地,一端接电容8c的下端,电容8c的上端接xout;开关s4一端接地,一端接电容16c的下端,电容16c的上端接xout;开关s5一端接地,一端接电容32c的下端,电容32c的上端接xout;开关s6一端接地,一端接电容64c的下端,电容64c的上端接xout;开关s7一端接地,一端接电容128c的下端,电容128c的上端接xout;开关s8一端接地,一端接电容256c的下端,电容256c的上端接xout。

24.二进制编码最小的情况下,电容阵列中的开关s0闭合,电容c被选中,随着与晶振

输出引脚xout连接的电容阵列中多个开关的闭合,电容这列中被选中的电容越多,如随着二进制编码增大,开关s0、s1、s2闭合,电容c、2c、4c被选中,开关s0、

···

、s5闭合,电容c、

···

、32c被选中,开关s0、

···

、s7闭合,电容c、

···

、128c被选中,而每增加一个二进制编码会使得可调节的晶振频率步长不一致,将导致需要精细控制频率时只能使用较小的单元电容,从而会使频率可调节范围受限,而在发射机与接收机的晶振的频率不同,导致发射机与接收机之间的数据传输错误。

25.其中,通过标准频率的方波调整晶振的负载电容大小来微调晶振的负载谐振频率时,负载电容的减小会导致频率的增加,反之负载电容的增加会导致频率的减小,且标准频率的方波存在(

‑

2ppm

‑

2ppm)的频率偏差,难以根据标准频率进行调频,实现精准的频率校准,从而导致发射机与接收机之间仍存在采样频率偏差,导致发射机与接收机之间的数据传输错误。

26.有鉴于此,本公开提供一种频率调整电路、方法及通信设备,通过编码控制可编程电容阵列进行分段拟合直线,线性化晶体谐振器的牵引灵敏度,对晶体谐振器的频率进行多次调节,保证晶体谐振器的频率随控制编码控制单调性,实现对频率步长的精确校准,保证了整发射机与接收机之间数据的正确传输。

27.图1是根据一示例性实施例示出的一种频率调整电路的示意图,参照图1,该电路包括晶体谐振器100、起振电路200以及可编程电容阵列,晶体谐振器100与起振电路200并联,可编程电容阵列与晶体谐振器100连接;可编程电容阵列包括多个依次并联的电容阵列,每一电容阵列能够独立工作,该可编程电容阵列中每一次用于编码的目标电容阵列是根据待输出编码中的部分比特位的取值确定的。

28.其中,待输出编码可以根据调频需求确定,本公开对此不作具体限定。

29.本公开中通过编码控制可编程电容阵列中需接入频率调整电路中的电容阵列,通过可编程电容阵列中的多个电容阵列进行分段拟合直线,线性化晶体谐振器的牵引灵敏度,从而扩大晶体谐振器的频率可调范围,进而调整发射机与接收机的晶体谐振器的频率一致,保证了整发射机与接收机之间数据的正确传输。

30.其中,参照图1,晶体谐振器xtal100包括动态等效子电路以及静态等效电容c0,动态等效子电路与静态等效电容c0并联后接入晶体谐振器的晶振输入引脚xin与晶振输出引脚xout之间。

31.动态等效子电路包括动态等效电感l1、动态等效电容c1以及动态等效电阻r1,动态等效电感l1、动态等效电容c1以及动态等效电阻r1依次串联后,与静态等效电容c0并联,再接入晶振输入引脚xin与晶振输出引脚xout之间,构成晶体谐振器。

32.本公开提供的晶体谐振器为现有的晶体谐振器,其工作原理在此不再阐述。

33.其中,参照图1,起振电路包括反馈电阻rf以及反相器a0,反馈电阻rf以及反相器a0并联后,接入晶振输入引脚xin与晶振输出引脚xout之间。

34.本公开提供的起振电路为现有技术,其具体工作原理在此不再阐述。

35.为了使本领域技术人员更加理解本公开提供的频率调整电路,下面对上述电路中各部分进行详细举例说明。

36.该频率调整电路中可存在不同数量的可编程电容阵列的情况,如仅存在两个可编

程电容阵列的频率调整电路,或者存在两个以上的可编程电容阵列的频率调整电路,而不同数量的可编程电容阵列对应的频率调整电路中各部分的具体连接方式不同。

37.在一可实施例中,该电路包括两个可编程电容阵列的情况下,第一可编程电容阵列的一端与晶体谐振器100的晶振输入引脚连接,第一可编程电容阵列的另一端接地;第二可编程电容阵列的一端与晶体谐振器100的晶振输出引脚连接,第二可编程电容阵列的另一端接地。

38.如图1所示,在电路中包括两个可编程电容阵列的情况下,第一可编程电容阵列300的一端与晶振输入引脚xin连接,第一可编程电容阵列300的另一端接地;第二可编程电容阵列400的一端与晶振输出引脚xout连接,第二可编程电容阵列400的另一端接地,其中第一可编程电容阵列300与第二可编程电容阵列400的具体构成完全一致。

39.在一可实施例中,该电路包括两个以上可编程电容阵列的情况下,各可编程电容阵列依次串联后接入晶体谐振器100的晶振输入引脚与晶振输出引脚之间。

40.在一可实施例中,该可编程电容阵列包括,可编程电容阵列包括粗调子电路以及与粗调子电路并联的细调子电路;细调子电路包括分段温度计码译码器401以及与分段温度计码译码器401连接的分段温度计码细调电容阵列402,粗调子电路包括分段二进制码译码器403以及与分段二进制码译码器403连接的分段二进制码粗调电容阵列404;细调子电路以及粗调子电路均能输出独立编码,分段温度计码细调电容阵列402以及分段二进制码粗调电容阵列404中每一次用于编码的目标电容阵列是根据待输出编码中的部分比特位的取值确定的。

41.进一步的,参照图3,细调子电路以及粗调子电路通过第一接口和第二接口连接。

42.本公开通过编码控制可编程电路中的粗调子电路(包括分段二进制码译码器和分段二进制码粗调电容阵列)对晶体谐振器的频率进行粗调,通过编码控制可编程电路中的细调子电路(包括分段温度计码译码器和分段温度计码细调电容阵列)对晶体谐振器的频率进行细调,保证晶体谐振器的频率随控制编码控制单调性,实现对频率步长的精确校准,保证了整发射机与接收机之间数据的正确传输。

43.在一可实施例中,该分段温度计码细调电容阵列402包括多个依次并联的第一电容子电路,各第一电容子电路包括依次串联的电容以及控制开关。

44.参照图4,分段温度计码细调电容阵列402包括四个依次并联的第一电容子电路a、第一电容子电路b、第一电容子电路c以及第一电容子电路d,第一电容子电路a包括依次串联的电容cta<30:0>以及控制开关sta<30:0>;第一电容子电路b包括依次串联的电容ctb<30:0>以及控制开关stb<30:0>;第一电容子电路c包括依次串联的电容ctc<30:0>以及控制开关stc<30:0>;第一电容子电路d包括依次串联的电容ctd<30:0>以及控制开关std<30:0>。

45.以31bit分段温度计码可编程电容阵列为例,其具体连接形式为:控制开关sta<30:0>一端接地,一端接电容cta<30:0>的下端,电容cta<30:0>的上端接xout;控制开关stb<30:0>一端接地,一端接电容ctb<30:0>的下端,电容ctb <30:0>的上端接xout;控制开关stc<30:0>一端接地,一端接电容ctc<30:0>的下端,电容ctc <30:0>的上端接xout;控制开关std<30:0>一端接地,一端接电容ctd<30:0>的下端,电容ctd <30:0>的上端接xout。

46.参照图3和图4,分段温度计码译码器的具体运行过程如下:分段二进制码译码器(粗调二进制码)d_coarse<8:0>的高2bit为00时,控制开关sta <30:0>由5bit分段温度计码译码器(细调二进码)d_fine<4:0>转化的31bit温度计码控制,控制开关stb<30:0>,stc<30:0>,std<30:0>均为0;粗调二进制码d_coarse<8:0>的高2bit为01时,控制开关stb <30:0>由5bit细调二进码d_fine<4:0>转化的31bit温度计码控制,控制开关sta<30:0>,stc<30:0>,std<30:0>均为0;粗调二进制码d_coarse<8:0>的高2bit为10时,控制开关stc<30:0>由5bit细调二进码d_fine<4:0>转化的31bit温度计码控制,控制开关sta<30:0>,stb<30:0>,std<30:0>均为0;粗调二进制码d_coarse<8:0>的高2bit为11时,控制开关std <30:0>由5bit细调二进码d_fine<4:0>转化的31bit温度计码控制,控制开关sta<30:0>,stb<30:0>,stc<30:0>均为0;其中,控制开关为1代表该控制开关所串联的电容接入xout和地之间,控制开关为0代表该控制开关所串联的电容不接入xout和地之间。

47.以5bit二进制转成的分段温度计码细调为例:分段二进制码译码器d_coarse<8:0>为高2bit时的四个状态00、01、10、11将5bit分段温度计码分为4段;00时,分段温度计码细调电容阵列402中,控制开关sta<30:0>由5bit细调二进码d_fine<4:0>转化的31bit温度计码控制,接入xout和地之间,控制开关stb<30:0>,控制开关stc<30:0>,控制开关std<30:0>均为0,所串联的细调电容阵列不接入;01时,控制开关stb<30:0>由5bit细调二进码d_fine<4:0>转化的31bit温度计码控制,接入xout和地之间,控制开关sta<30:0>,控制开关stc<30:0>,控制开关std<30:0>均为0,所串联的细调电容阵列不接入;10时,控制开关stc <30:0>由5bit细调二进码d_fine<4:0>转化的31bit温度计码控制,接入xout和地之间,控制开关sta<30:0>,控制开关stb<30:0>,控制开关std<30:0>均为0,所串联的细调电容阵列不接入;11时,控制开关std <30:0>由5bit细调二进码d_fine<4:0>转化的31bit温度计码控制,接入xout和地之间,控制开关sta<30:0>,控制开关stb<30:0>,控制开关stc<30:0>均为0,所串联的细调电容阵列不接入。

48.其中,第一电容子电路a中的单位电容大小为cta,第一电容子电路b中的单位电容大小为ctb,第一电容子电路c中的单位电容大小为ctc,第一电容子电路d中的单位电容大小为ctd,cta<ctb<ctc<ctd,单位电容为电容阵列中所有电容均接入频率调整电路后,该电容阵列的电容量。

49.在一可实施例中,该分段二进制码粗调电容阵列404包括多个依次并联的电容阵列,且各电容阵列的单位电容依次增大。

50.其中,单位电容为电容阵列中所有电容均接入频率调整电路后,该电容阵列的电容量。

51.参照图5,分段二进制码粗调电容阵列404包括四个依次并联的电容阵列a、电容阵列b、电容阵列c以及电容阵列d,其中,电容阵列a的单位电容为ca、电容阵列b的单位电容为cb、电容阵列c的单位电容为cb、电容阵列d的单位电容为cd,且ca<cb<cc<cd。

52.通过设置依次增大的单位电容,通过各电容阵列进行分段拟合直线,从而线性化晶振的牵引灵敏度,扩大了晶振频率的可调节范围。

53.在一可实施例中,分段二进制码粗调电容阵列中的电容阵列包括多个依次并联的第二电容子电路,各第二电容子电路包括依次串联的电容以及控制开关。

54.参见图5,分段二进制码粗调电容阵列404包括四个依次并联的电容阵列a、电容阵列b、电容阵列c以及电容阵列d列,其中,电容阵列a包括:开关sa一端接地,一端接电容ca的下端,电容ca的上端接xout;开关sa0一端接地,一端接电容1ca的下端,电容1ca的上端接xout;开关sa1一端接地,一端接电容2ca的下端,电容2ca的上端接xout;开关sa2一端接地,一端接电容4ca的下端,电容4ca的上端接xout;开关sa3一端接地,一端接电容8ca的下端,电容8ca的上端接xout;开关sa4一端接地,一端接电容16ca的下端,电容16ca的上端接xout;开关sa5一端接地,一端接电容32ca的下端,电容32ca的上端接xout;开关sa6一端接地,一端接电容64ca的下端,电容64ca的上端接xout;其中,开关sa和电容ca为伪开关电容单元,用于保证分段前后的单调性;电容阵列b包括:开关sb一端接地,一端接电容cb的下端,电容cb的上端接xout;开关sb0一端接地,一端接电容1cb的下端,电容1cb的上端接xout;开关sb1一端接地,一端接电容2cb的下端,电容2cb的上端接xout;开关sb2一端接地,一端接电容4cb的下端,电容4cb的上端接xout;开关sb3一端接地,一端接电容8cb的下端,电容8cb的上端接xout;开关sb4一端接地,一端接电容16cb的下端,电容16cb的上端接xout;开关sb5一端接地,一端接电容32cb的下端,电容32cb的上端接xout;开关sb6一端接地,一端接电容64cb的下端,电容64cb的上端接xout;电容阵列c包括:开关sc一端接地,一端接电容cc的下端,电容cc的上端接xout;开关sc0一端接地,一端接电容1cc的下端,电容1cc的上端接xout;开关sc1一端接地,一端接电容2cc的下端,电容2cc的上端接xout;开关sc2一端接地,一端接电容4cc的下端,电容4cc的上端接xout;开关sc3一端接地,一端接电容8cc的下端,电容8cc的上端接xout;开关sc4一端接地,一端接电容16cc的下端,电容16cc的上端接xout;开关sc5一端接地,一端接电容32cc的下端,电容32cc的上端接xout;开关sc6一端接地,一端接电容64cc的下端,电容64cc的上端接xout;电容阵列d包括:开关sd一端接地,一端接电容cd的下端,电容cd的上端接xout;开关sd0一端接地,一端接电容1cd的下端,电容1cd的上端接xout;开关sd1一端接地,一端接电容2cd的下端,电容2cd的上端接xout;开关sd2一端接地,一端接电容4cd的下端,电容4cd的上端接xout;开关sd3一端接地,一端接电容8cd的下端,电容8cd的上端接xout;开关sd4一端接地,一端接电容16cd的下端,电容16cd的上端接xout;开关sd5一端接地,一端接电容32cd的下端,电容32cd的上端接xout;开关sd6一端接地,一端接电容64cd的下端,电容64cd的上端接xout。

55.在一可实施例中,该控制开关的断开以及闭合根据待输出编码中的部分比特位的取值确定。

56.其中,待输出编码包括二进制码和温度计码,通过二进制码和温度计码中部分比特位的取值对控制开关的断开以及闭合进行控制,控制开关为1,代表与该控制开关串联的电容接入频率调整电路;控制开关为0,代表与该控制开关串联的电容不接入频率调整电路中,以控制电容阵列的实现分段拟合直线,从而线性化晶振的牵引灵敏度。

57.参照图3以及图5,分段二进制码译码器的具体运行过程如下:以9bit二进制码粗调为例:高2bit的00、01、10、11四个状态将9bit二进制码分为4段,00时电容阵列a受低7bit二进制控制,接入xout和地之间;01时电容阵列a和电容阵列b

接入xout和地之间,其中电容阵列b受低7bit二进制控制,电容阵列a中所有电容全接入xout和地之间;10时电容阵列a、电容阵列b和电容阵列c接入xout和地之间,其中电容阵列c受低7bit二进制控制,电容阵列a、电容阵列b中所有电容全接入xout和地之间;11时电容阵列a、电容阵列b、电容阵列c和电容阵列d接入xout和地之间,其中电容阵列d受低7bit二进制控制,电容阵列a、电容阵列b和电容阵列c中所有电容全接入xout和地之间。如,分段二进制码译码器(粗调二进制码)d_coarse<8:0>的高2bit为00时,电容阵列a中,控制开关sa=1,控制开关sa6,sa5,sa4,sa3,sa2,sa1,sa0分别受低7bit二进制码控制,控制开关sa6为msb(most significant bit,最高有效位),控制开关sa0为lsb(least significant bit,最低有效位);电容阵列b中,控制开关sb=0,控制开关sb6,sb5,sb4,sb3,sb2,sb1,sb0均为0;电容阵列c中,控制开关sc=0,控制开关sc6,sc5,sc4,sc3,sc2,sc1,sc0均为0;电容阵列d中,控制开关sd=0,控制开关sd6,sd5,sd4,sd3,sd2,sd1,sd0均为0。

58.粗调二进制码d_coarse<8:0>的高2bit为01时,电容阵列b中,控制开关sb=1,控制开关sb6,sb5,sb4,sb3,sb2,sb1,sb0分别受低7bit二进制码控制,sb6为msb,sb0为lsb;电容阵列a中,控制开关sa=1,控制开关sa6,sa5,sa4,sa3,sa2,sa1,sa0均为1;电容阵列c中,控制开关sc=0,控制开关sc6,sc5,sc4,sc3,sc2,sc1,sc0均为0;电容阵列d中,控制开关sd=0,开关sd6,sd5,sd4,sd3,sd2,sd1,sd0均为0。

59.粗调二进制码d_coarse<8:0>的高2bit为10时,电容阵列c中,控制开关sc=1,控制开关sc6,sc5,sc4,sc3,sc2,sc1,sc0分别受低7bit二进制码控制,sc6为msb,sc0为lsb;电容阵列a中,控制开关sa=1,控制开关sa6,sa5,sa4,sa3,sa2,sa1,sa0均为1;电容阵列b中,控制开关sb=1,控制开关sb6,sb5,sb4,sb3,sb2,sb1,sb0均为1;电容阵列d中,控制开关sd=0,控制开关sd6,sd5,sd4,sd3,sd2,sd1,sd0均为0。

60.粗调二进制码d_coarse<8:0>的高2bit为11时,电容阵列d中,控制开关sd=1,控制开关sd6,sd5,sd4,sd3,sd2,sd1,sd0分别受低7bit二进制码控制,sd6为msb,sd0为lsb;电容阵列a中,控制开关sa=1,控制开关sa6,sa5,sa4,sa3,sa2,sa1,sa0均为1;电容阵列b中,控制开关sb=1,控制开关sb6,sb5,sb4,sb3,sb2,sb1,sb0均为1;电容阵列c中,控制开关sc=1,控制开关sc6,sc5,sc4,sc3,sc2,sc1,sc0均为1。

61.其中,控制开关为1代表该控制开关所串联的电容接入xout和地之间,控制开关为0代表该控制开关所串联的电容不接入xout和地之间。

62.以上逻辑关系可参见以下真值表:

参照图6,虚线为采用二进制编码调整晶体谐振器的负载电容大小得到的仿真结果,可确定出在二进制编码最小时,晶振频率牵引灵敏度最大,但随着二进制编码增大,可编程电容阵列中被选中的电容越多,晶振频率牵引灵敏度越小,每增加一个二进制编码可调节的晶振频率步长不一致;实线为采用本公开提供的频率调整电路得到的仿真结果,可确定本公开通过分段拟合直线的方式,线性化晶振的牵引灵敏度。

63.且本公开通过分段二进制码粗调电容阵列和分段温度计码细调电容阵列的编码方式,既保证晶振频率随二进制编码控制的单调性,又达到了精细控制可调频率步长的目的。且通过本公开的晶振频率调整电路,可以实现0.1ppm的调整精度。

64.基于同一发明构思,本公开还提供一种频率调整方法,由上述的频率调整电路执行,参见图7,该方法包括:在步骤s101中,获取接收机与发送端各待调整的晶体谐振器的频率与预设标准频率的频率偏差,根据频率偏差对各晶体谐振器的频率进行出厂校准。

65.在步骤s102中,获取出厂校准后接收机与发送端的晶体谐振器之间的采样频率偏差,根据采样频率偏差对各晶体谐振器的频率进行通信校准。

66.其中,预设标准频率可根据发射机和接收机之间具体通信过程中的频率进行预设,本公开对此不作具体限定。

67.本公开提供的频率调整方法,包括出厂校准和通信校准两步频率校准,第一步,在包括频率调整电路的产品(如芯片等)在出厂时,比较产品中晶体谐振器与预设标准频率之间的频率偏差,先调节频率调整电路中的分段二进制码粗调电容阵列,再调节频率调整电

路中的分段温度计码细调电容阵列,将晶体谐振器的频率调节到预设标准频率附近;第二步,利用采样频率偏差估计算法,获取电力线通信的接收机与发送端之间的采样频率偏差,根据采样频率偏差先调节频率调整电路中的分段二进制码粗调电容阵列,再调节频率调整电路中的分段温度计码细调电容阵列,以解决现有电力线通信中因发射机与接收机之间的采样频率偏差造成的数据包接收错误的技术问题。

68.关于上述实施例中的频率调整电路,其中各个元器件的连接关系以及具体运行原理已经在有关该频率调整电路的实施例中进行了详细描述,此处将不做详细阐述说明。

69.基于同一发明构思,本公开还提供一种通信设备,包括上述的频率调整电路。

70.图8是根据一示例性实施例示出的一种电子设备700的框图。如图8所示,该电子设备700可以包括:处理器701,存储器702。该电子设备700还可以包括多媒体组件703,输入/输出(i/o)接口704,以及通信组件705中的一者或多者。

71.其中,处理器701用于控制该电子设备700的整体操作,以控制频率调整电路进行调频。存储器702用于存储各种类型的数据以支持在该电子设备700的操作,这些数据例如可以包括用于在该电子设备700上操作的任何应用程序或方法的指令,以及应用程序相关的数据,例如联系人数据、收发的消息、图片、音频、视频等等。该存储器702可以由任何类型的易失性或非易失性存储设备或者它们的组合实现,例如静态随机存取存储器(static random access memory,简称sram),电可擦除可编程只读存储器(electrically erasable programmable read

‑

only memory,简称eeprom),可擦除可编程只读存储器(erasable programmable read

‑

only memory,简称eprom),可编程只读存储器(programmable read

‑

only memory,简称prom),只读存储器(read

‑

only memory,简称rom),磁存储器,快闪存储器,磁盘或光盘。多媒体组件703可以包括屏幕和音频组件。其中屏幕例如可以是触摸屏,音频组件用于输出和/或输入音频信号。例如,音频组件可以包括一个麦克风,麦克风用于接收外部音频信号。所接收的音频信号可以被进一步存储在存储器702或通过通信组件705发送。音频组件还包括至少一个扬声器,用于输出音频信号。i/o接口704为处理器701和其他接口模块之间提供接口,上述其他接口模块可以是键盘,鼠标,按钮等。这些按钮可以是虚拟按钮或者实体按钮。通信组件705用于该电子设备700与其他设备之间进行有线或无线通信。无线通信,例如wi

‑

fi,蓝牙,近场通信(near field communication,简称nfc),2g、3g、4g、nb

‑

iot、emtc、或其他5g等等,或它们中的一种或几种的组合,在此不做限定。因此相应的该通信组件705可以包括:wi

‑

fi模块,蓝牙模块,nfc模块等等。

72.在一示例性实施例中,电子设备700可以被一个或多个应用专用集成电路(application specific integrated circuit,简称asic)、数字信号处理器(digital signal processor,简称dsp)、数字信号处理设备(digital signal processing device,简称dspd)、可编程逻辑器件(programmable logic device,简称pld)、现场可编程门阵列(field programmable gate array,简称fpga)、控制器、微控制器、微处理器或其他电子元件实现,用于控制上述频率调整电路进行调频。

73.在另一示例性实施例中,还提供了一种包括程序指令的计算机可读存储介质,该程序指令被处理器执行时控制上述频率调整电路进行调频。例如,该计算机可读存储介质可以为上述包括程序指令的存储器702,上述程序指令可由电子设备700的处理器701执行控制上述频率调整电路进行调频。

74.以上结合附图详细描述了本公开的优选实施方式,但是,本公开并不限于上述实施方式中的具体细节,在本公开的技术构思范围内,可以对本公开的技术方案进行多种简单变型,这些简单变型均属于本公开的保护范围。

75.另外需要说明的是,在上述具体实施方式中所描述的各个具体技术特征,在不矛盾的情况下,可以通过任何合适的方式进行组合。为了避免不必要的重复,本公开对各种可能的组合方式不再另行说明。

76.此外,本公开的各种不同的实施方式之间也可以进行任意组合,只要其不违背本公开的思想,其同样应当视为本公开所公开的内容。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。