1.本披露一般地涉及电路领域。更具体地,本披露涉及一种运算电路、芯片和板卡。

背景技术:

2.目前,深度学习(deep learning)已经成为机器学习中的重要分支,也大力助推着人工智能(ai)的发展。深度学习的核心技术——深度神经网络(dnn)已在诸多行业有着广泛的应用。

3.神经网络模型中存在大量的乘法、加法以及乘法与加法的混合运算,这些运算可通过相应的运算电路来实现。然而,目前的运算电路中各运算器件(例如乘法器)的输入数据来源往往是固定的,该种方式使得一个运算电路只能执行一种既定的运算模式,从而导致运算器件的灵活性较差。

技术实现要素:

4.为了至少解决如上所提到的一个或多个技术问题,本披露提出了一种运算电路,其通过引入多个选择器,对乘法器和加法器的运算数据进行选择控制,可以实现多种模式的乘法和/或加法运算。

5.在第一方面中,本披露实施例提供了一种运算电路,包括:乘法器,其配置用于执行乘法运算;加法器,其配置用于执行加法运算;以及多个选择器,其配置用于根据相应的使能信号控制选择通路以连通输入数据与所述乘法器和/或加法器来执行指定的运算模式并输出对应结果;其中所述运算模式具有包括乘法运算和/或加法运算的运算规则。

6.在第二方面中,本披露实施例提供了一种芯片,其包括前述第一方面的运算电路。

7.在第三方面中,本披露实施例提供了一种板卡,其包括前述第二方面的芯片。

8.通过如上所提供的运算电路、芯片和板卡,本披露实施例的方案可以通过使能信号的配置控制各个选择器连通不同的通路,从而控制向乘法器和加法器输入不同的运算数据,进而实现多种模式的乘法和/或加法运算。由此可见,本披露实施例对运算电路进行了优化,优化后的运算电路可实现多种模式的乘加运算,从而增加了运算器件的灵活性。

附图说明

9.通过参考附图阅读下文的详细描述,本公开示例性实施方式的上述以及其他目的、特征和优点将变得易于理解。在附图中,以示例性而非限制性的方式示出了本公开的若干实施方式,并且相同或对应的标号表示相同或对应的部分,其中:

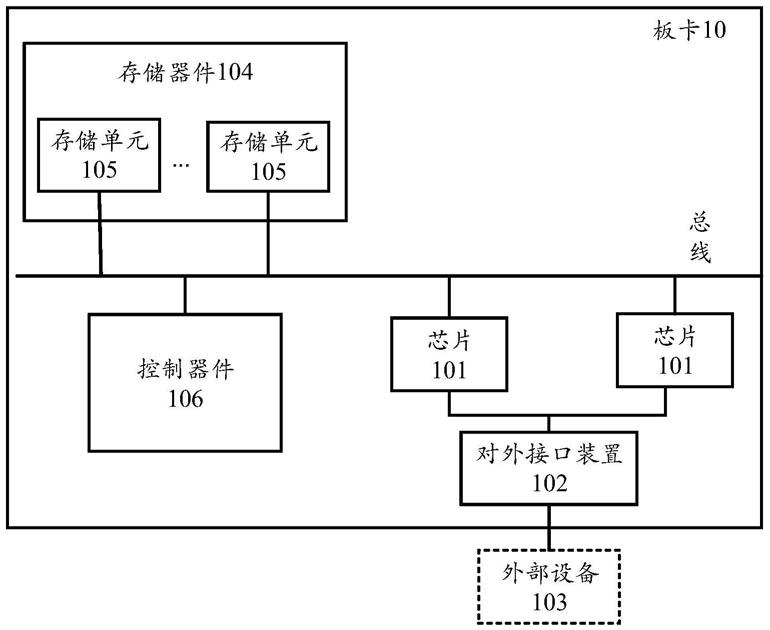

10.图1示出本披露实施例的板卡的结构图;

11.图2示出本披露实施例的组合处理装置的结构图;

12.图3示出本披露实施例的单核或多核计算装置的处理器核的内部结构示意图;

13.图4示出本披露一个实施例的运算电路的示意性结构图;

14.图5示出本披露另一实施例的运算电路的示意性结构图;

15.图6示出本披露一个实施例的逻辑电路的示意性结构图;以及

16.图7a

‑

图7d分别示出四种运算模式的简化电路图。

具体实施方式

17.下面将结合本披露实施例中的附图,对本披露实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例是本披露一部分实施例,而不是全部的实施例。基于本披露中的实施例,本领域技术人员在没有做出创造性劳动前提下所获得的所有其他实施例,都属于本披露保护的范围。

18.应当理解,本披露的权利要求、说明书及附图中可能出现的术语“第一”、“第二”、“第三”和“第四”等是用于区别不同对象,而不是用于描述特定顺序。本披露的说明书和权利要求书中使用的术语“包括”和“包含”指示所描述特征、整体、步骤、操作、元素和/或组件的存在,但并不排除一个或多个其它特征、整体、步骤、操作、元素、组件和/或其集合的存在或添加。

19.还应当理解,在本披露说明书中所使用的术语仅仅是出于描述特定实施例的目的,而并不意在限定本披露。如在本披露说明书和权利要求书中所使用的那样,除非上下文清楚地指明其它情况,否则单数形式的“一”、“一个”及“该”意在包括复数形式。还应当进一步理解,在本披露说明书和权利要求书中使用的术语“和/或”是指相关联列出的项中的一个或多个的任何组合以及所有可能组合,并且包括这些组合。

20.如在本说明书和权利要求书中所使用的那样,术语“如果”可以依据上下文被解释为“当...时”或“一旦”或“响应于确定”或“响应于检测到”。

21.下面结合附图来详细描述本披露的具体实施方式。

22.图1示出本披露实施例的一种板卡10的结构示意图。如图1所示,板卡10包括芯片101,其是一种系统级芯片(system on chip,soc),或称片上系统,集成有一个或多个组合处理装置,组合处理装置是一种人工智能运算单元,用以支持各类深度学习和机器学习算法,满足计算机视觉、语音、自然语言处理、数据挖掘等领域复杂场景下的智能处理需求。特别是深度学习技术大量应用在云端智能领域,云端智能应用的一个显著特点是输入数据量大,对平台的存储能力和计算能力有很高的要求,此实施例的板卡10适用在云端智能应用,具有庞大的片外存储、片上存储和强大的计算能力。

23.芯片101通过对外接口装置102与外部设备103相连接。外部设备103例如是服务器、计算机、摄像头、显示器、鼠标、键盘、网卡或wifi接口等。待处理的数据可以由外部设备103通过对外接口装置102传递至芯片101。芯片101的计算结果可以经由对外接口装置102传送回外部设备103。根据不同的应用场景,对外接口装置102可以具有不同的接口形式,例如pcie接口等。

24.板卡10还包括用于存储数据的存储器件104,其包括一个或多个存储单元105。存储器件104通过总线与控制器件106和芯片101进行连接和数据传输。板卡10中的控制器件106配置用于对芯片101的状态进行调控。为此,在一个应用场景中,控制器件106可以包括单片机(micro controller unit,mcu)。

25.图2是示出此实施例的芯片101中的组合处理装置的结构图。如图2中所示,组合处理装置20包括计算装置201、接口装置202、处理装置203和存储装置204。

26.计算装置201配置成执行用户指定的操作,主要实现为单核智能处理器或者多核智能处理器,用以执行深度学习或机器学习的计算,其可以通过接口装置202与处理装置203进行交互,以共同完成用户指定的操作。

27.接口装置202用于在计算装置201与处理装置203间传输数据和控制指令。例如,计算装置201可以经由接口装置202从处理装置203中获取输入数据,写入计算装置201片上的存储装置。进一步,计算装置201可以经由接口装置202从处理装置203中获取控制指令,写入计算装置201片上的控制缓存中。替代地或可选地,接口装置202也可以读取计算装置201的存储装置中的数据并传输给处理装置203。

28.处理装置203作为通用的处理装置,执行包括但不限于数据搬运、对计算装置201的开启和/或停止等基本控制。根据实现方式的不同,处理装置203可以是中央处理器(central processing unit,cpu)、图形处理器(graphics processing unit,gpu)或其他通用和/或专用处理器中的一种或多种类型的处理器,这些处理器包括但不限于数字信号处理器(digital signal processor,dsp)、专用集成电路(application specific integrated circuit,asic)、现场可编程门阵列(field

‑

programmable gate array,fpga)或者其他可编程逻辑器件、分立门或者晶体管逻辑器件、分立硬件组件等,并且其数目可以根据实际需要来确定。如前所述,仅就本披露的计算装置201而言,其可以视为具有单核结构或者同构多核结构。然而,当将计算装置201和处理装置203整合共同考虑时,二者视为形成异构多核结构。

29.存储装置204用以存储待处理的数据,其可以是dram,为ddr内存,大小通常为16g或更大,用于保存计算装置201和/或处理装置203的数据。

30.图3示出了计算装置201为单核或多核装置时处理核的内部结构示意图。计算装置301用以处理计算机视觉、语音、自然语言、数据挖掘等输入数据,计算装置301包括三大模块:控制模块31、运算模块32及存储模块33。

31.控制模块31用以协调并控制运算模块32和存储模块33的工作,以完成深度学习的任务,其包括取指单元(instruction fetch unit,ifu)311及指令译码单元(instruction decode unit,idu)312。取指单元311用以获取来自处理装置203的指令,指令译码单元312则将获取的指令进行译码,并将译码结果作为控制信息发送给运算模块32和存储模块33。

32.运算模块32包括向量运算单元321及矩阵运算单元322。向量运算单元321用以执行向量运算,可支持向量乘、加、非线性变换等复杂运算;矩阵运算单元322负责深度学习算法的核心计算,即矩阵乘及卷积。

33.存储模块33用来存储或搬运相关数据,包括神经元存储单元(neuron ram,nram)331、权值存储单元(weight ram,wram)332、直接内存访问模块(direct memory access,dma)333。nram 331用以存储输入神经元、输出神经元和计算后的中间结果;wram 332则用以存储深度学习网络的卷积核,即权值;dma 333通过总线34连接dram 204,负责计算装置301与dram 204间的数据搬运。

34.以上结合图1

‑

图3对本公开的硬件架构及其内部结构进行了详细的描述。可以理解的是上述描述仅仅是示例性的而非限制性的。根据不同的应用场景和硬件规格,本领域技术人员也可以对本公开的板卡及其内部结构进行改变,而这些改变依然落入本公开的保护范围内。本披露的实施例基于前述硬件环境,提供一种多模式运算电路,其可以用于实现

例如图3中的运算模块32中的各种电路,包括但不限于向量运算单元321和矩阵元单元322。

35.图4示出了本披露一个实施例的运算电路400的示意性结构图。如图4中所示,运算电路400可以包括乘法器402、加法器403和多个选择器,例如选择器401和选择器404。乘法器402可以配置用于执行乘法运算,加法器403可以配置用于执行加法运算。

36.在一个实施场景中,上述乘法器402可以为模拟乘法器、硬件乘法器或谐波乘法器,加法器403可以为全加器或半加器,而选择器401和选择器404可以为数据选择器或多路选择器等。在一种实现中,数据选择器可以为2选1数据选择器、3选1数据选择器或4选1数据选择器,从而可以满足不同运算场景的需求。

37.在一个实施例中,上述选择器401和选择器404可以配置用于根据相应的使能信号控制选择通路以连通第一输入数据a、第二输入数据b、第三输入数据c与上述乘法器402和/或加法器403来执行指定的运算模式并输出对应结果。选择器的数目可以根据具体运算需求(例如要实现的运算模式)确定,例如可以为3个、4个、5个或6个等。另外,针对于不同的运算模式,还可以设置上述输入数为其他数目,例如为2个、3个或4个等。可以理解,这些运算模式具有包括乘法运算和/或加法运算的运算规则。例如,神经网络模型中常见的全连接层、卷积层、池化层等的计算可以归纳为两数相乘再与第三数相加的运算。

38.图5示出了根据本披露一个实施例的包括五个选择器、针对三个输入数据的运算电路500的示意性结构图。

39.由图5可以看出,运算电路500包含的五个选择器分别为第一选择器501、第二选择器502、第三选择器503、第四选择器504和第五选择器505。第一选择器501的第一输入端与第一数据输入端连接,其第二输入端与加法器511的输出端连接,其输出端连接到乘法器510的第一输入端。第二选择器502的第一输入端与第一数据输入端连接,其第二输入端与乘法器510的输出端连接,其输出端连接到加法器511的第一输入端。另外,第三选择器503的第一输入端与第二数据输入端连接,其第二输入端与第三数据输入端连接,其输出端连接到乘法器510的第二输入端。第四选择器504的第一输入端与第二数据输入端连接,其第二输入端与第三数据输入端连接,其输出端连接到加法器511的第二输入端。进一步,第五选择器505的第一输入端与加法器511的输出端连接,其第二输入端与乘法器510的输出端连接,其输出端为运算电路500的输出端。

40.设定第一数据输入端接收来自于外部的第一输入数据a,第二数据输入端接收来自于外部的第二输入数据b,第三数据输入端接收来自于外部的第三输入数据c。第一选择器501的使能信号为en1、第二选择器502的使能信号为en2、第三选择器503的使能信号为en3、第四选择器504的使能信号为en4和第五选择器505的使能信号为en5。

41.基于上述运算电路500的结构以及三个外部输入数据,本披露方案可通过上述各个使能信号的控制选择连通不同的通路,从而执行不同的运算,并最终实现相应的运算模式。例如,对于第一选择器501,可设定在其使能信号en1为0时,其可连通第一数据输入端和乘法器510之间的通路,从而可以将第一输入数据a输入到乘法器510。可设定在使能信号en1为1时,其可连通加法器511的输出端和乘法器510之间的通路,从而可以将加法器511的输出数据输入到乘法器510。

42.对于第二选择器502,可设定在使能信号en2为0时,其可连通第一数据输入端和加法器511之间的通路,从而可以将第一输入数据a输入到加法器511。另外,可设定在使能信

号en2为1时,其可连通乘法器510的输出端和加法器511之间的通路,从而可以将乘法器510的输出数据输入到加法器511。

43.对于第三选择器503,可设定在使能信号en3为0时,其可连通第二数据输入端和乘法器510之间的通路,从而可以将第二输入数据b输入到乘法器510。另外,还可设定在使能信号en3为1时,其可连通第三数据输入端和乘法器510之间的通路,从而可以将第三输入数据c输入到乘法器510。

44.对于第四选择器504,可设定在使能信号en4为0时,其可连通第二数据输入端和加法器511之间的通路,从而可以将第二输入数据b输入到加法器511。还可设定在使能信号en4为1时,其可连通第三数据输入端和加法器511之间的通路,从而可以将第三输入数据c输入到加法器511。

45.对于连接运算电路500的输出端的第五选择器505,可设定在使能信号en5为0时,其可以连通加法器511的输出端和运算电路500的输出端,从而可以将加法器511的输出数据作为运算电路的运算结果输出。对应地,还可设定在使能信号en5为1时,其可以连通乘法器510的输出端和运算电路500的输出端,从而可以将乘法器510的输出数据作为运算电路的运算结果输出。

46.基于运算电路500的上述结构,通过对各个选择器的使能信号的不同配置便可将上述各个选择器配置为不同的选择模式,从而使运算电路500执行相应的运算模式。例如,在设置en1=0,en2=1,en3=0,en4=1,en5=0时,第一选择器501控制连通第一数据输入端和乘法器510之间的通路,第三选择器503控制连通第二数据输入端和乘法器510之间的通路。第二选择器502控制连通乘法器510的输出端和加法器511之间的通路,第四选择器504控制连通第三数据输入端和加法器511之间的通路,并且第五选择器505控制连通加法器511的输出端和运算电路500的输出端。可见,通过该配置运算电路可实现(a*b) c的运算模式。

47.在设置en1=1,en2=0,en3=1,en4=0,en5=1时,第二选择器502控制连通第一数据输入端和加法器511之间的通路,第四选择器504控制连通第二数据输入端和加法器511之间的通路。第一选择器501控制连通加法器511的输出端和乘法器510之间的通路,第三选择器503控制连通第三数据输入端和乘法器510之间的通路,并且第五选择器505控制连通乘法器510的输出端和运算电路500的输出端。可见,通过该配置运算电路可实现(a b)*c的运算模式。

48.另外,在设置en1=0,en3=0,en5=1时,第一选择器501控制连通第一数据输入端和乘法器510之间的通路,第三选择器503控制连通第二数据输入端和乘法器510之间的通路,并且第五选择器505控制连通乘法器510的输出端和运算电路500的输出端。可见,通过该配置运算电路可实现a*b的运算模式。

49.进一步,在设置en2=0,en4=0,en5=0时,第二选择器502控制连通第一数据输入端和加法器511之间的通路,第四选择器504控制连通第二数据输入端和加法器511之间的通路,并且第五选择器505控制连通加法器511的输出端和运算电路500的输出端。可见,通过该配置运算电路可实现a b的运算模式。

50.通过上述描述可见,本方案的实施例可以通过使能信号的配置控制运算电路中各个选择器连通不同的通路,从而控制向乘法器和加法器输入不同的运算数据,进而实现多

种模式的乘法和/或加法运算。由此可见,本方案的实施例实现了对运算电路的优化,通过该优化可使运算电路可实现多种模式的乘加运算,从而增加了运算器件的灵活性。

51.在一个实施例中,可以通过硬件电路来生成上述图5中各个选择器的使能信号。在一种实现中,硬件电路可为逻辑电路,并且逻辑电路可配置用于根据运算模式指示信号,生成对应的使能信号以分别传递给上述多个选择器。

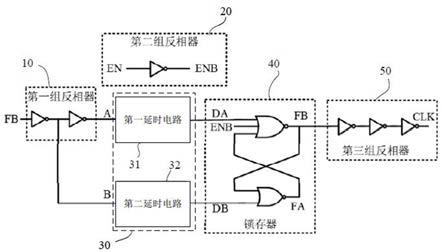

52.图6示出了本披露一个实施例的逻辑电路600的示意性结构图。在该图所示的实施例中,逻辑电路600可以根据运算模式指示信号mode1和mode2(运算模式指示信号的两比特模式指示位,稍后详述)来生成上述图5中五个选择器的使能信号en1、en2、en3、en4和en5,并将它们分别传递给对应的选择器。

53.在一个实施场景中,上述逻辑电路600可通过与门、或门、非门和异或门等多种逻辑门电路中的一种或多种的组合来实现。例如,可通过与门、非门和异或门来组成一个逻辑电路,从而可以对例如上述运算模式指示信号中的两比特模式指示位mode1和mode2执行与运算、非运算以及异或运算并生成相应的使能信号。另外,上述运算模式指示信号可以来自于用于控制运算电路的运算的控制模块,例如处理器。

54.在另一个实施场景中,上述使能信号还可通过软件算法来生成。软件算法可为与上述逻辑电路600相对应的逻辑运算方法,即与运算、或运算、非运算和异或运算等多种逻辑运算中的一种或多种的组合运算方法,此处不再详述。

55.上述仅仅列举了几种逻辑电路及逻辑运算方法,本领域技术人员还可根据不同运算场景(例如运算模式指示信号与使能信号之间不同的对应关系)来选择其他逻辑电路或逻辑运算方法,此处不再详述。

56.在图5的示例性运算电路中,其支持四种运算模式,由此运算模式指示信号可以包括两比特模式指示位(例如上述实施例中的mode1和mode2),以用于指示例如前述的四种运算模式。

57.图7a

‑

图7d中分别示出了该四种运算模式的简化电路图,其中图7a对应(a*b) c模式,图7b对应(a b)*c模式,图7c对应a*b模式,并且图7d对应a b模式。在图7a

‑

图7d中,标号701表示乘法器,标号702表示加法器。

58.通过上述运算模式指示信号来指示四种运算模式的方式有多种。例如,在一个实施例中,可以设置上述两比特模式指示位中的第一比特用于指示前述第一输入数据a和第二输入数据b之间的乘法和加法的运算顺序,设置第二比特用于指示前述第三输入数据c是否参与运算。进一步,可以设置当第一比特为0时先执行乘法运算,设置当第一比特为1时先执行加法运算,反之亦然。另外,可以设置当第二比特为0时指示第三输入数据c参与运算,并且相应地设置当第二比特为1时指示第三输入数据c不参与运算,反之亦然。

59.基于上述设定,当第一比特和第二比特均为0时,可执行图7a所示的(a*b) c模式。当第一比特为1、第二比特为0时,可执行图7b所示的(a b)*c模式。当第一比特为0而第二比特为1时,可执行图7c所示的a*b模式。进一步,当第一比特和第二比特均为1时,可执行图7d所示的a b模式。可见,通过对上述两比特模式指示位的指示功能的设置,可控制运算电路执行不同的运算模式。

60.本领域技术人员可以理解的是,上述两比特模式指示位的指示功能仅仅是示例性的而非限制性的,本领域技术人员可以根据运算场景的不同设置其分别为不同的指示功

能,以用于实现不同的运算模式。

61.为了便于根据运算模式指示信号中的两比特模式指示位生成对应的使能信号,在一个实施例中,当运算模式指示信号中的第一比特mode1指示第一输入数据a和第二输入数据b之间的乘法和加法的运算顺序时,上述逻辑电路600可配置成基于第一比特的数值,确定上述第一选择器501、第二选择器502、第三选择器503和第四选择器504各自的使能信号。进一步,逻辑电路600可配置成基于第一比特和第二比特的数值,确定上述第五选择器505的使能信号。

62.进一步地,基于图5所示的选择器与乘法器和加法器的具体连接关系,可以按如下设置各个使能信号:设置第一选择器501的使能信号与第三选择器503的使能信号相同,第二选择器502的使能信号与第四选择器504的使能信号相同,并且设置第一选择器501的使能信号与第二选择器502的使能信号相反,相应地,第三选择器503的使能信号与第四选择器504的使能信号也相反。基于上述的设定,逻辑电路600还可用于根据上述两比特模式指示位与前述四种运算模式的对应关系,将第一选择器501的使能信号设置为等于两比特模式指示位中的第一比特的值或与之相反,以及将第五选择器505的使能信号设置为等于第一比特和第二比特的异或结果或同或结果。

63.为了进一步说明上述运算模式指示信号中的两比特模式指示位以及各个使能信号之间的对应关系,下面提供了具有三种不同配置关系的真值表,如表1

‑

3。在表1

‑

3中,mode1为两比特模式指示位中的第一比特,mode2为两比特模式指示位中的第二比特,en1

‑

en5分别为前述第一选择器501

‑

第五选择器505的使能信号。表中

“‑”

表示取值任意。

64.在表1中,设定当mode1=0时,指示先计算乘法;当mode1=1时,指示先计算加法。当mode2=0时,指示第三输入数据c参与运算,并且当mode2=1时,指示第三输入数据c不参与运算。

65.表1

66.mode2mode1运算模式en1en2en3en4en500(a*b) c0101001(a b)*c1010110a*b0

‑0‑

111a b

‑0‑

00

67.由该表1可以推导出五个使能信号与模式指示位之间的逻辑关系如下:

68.en1=mode1,en2=not mode1,

69.en3=mode1,en4=not mode1,

70.en5=mode1 xor mode2,其中not表示逻辑“非”,xor表示逻辑“异或”。

71.在表2中,设定当mode1=0时,指示先计算乘法;当mode1=1时,指示先计算加法。当mode2=0时,指示第三输入数据c不参与运算,并且当mode2=1时,指示第三输入数据c参与运算。

72.表2

73.mode2mode1运算模式en1en2en3en4en500a*b0

‑0‑

101a b

‑0‑

00

10(a*b) c0101011(a b)*c10101

74.由该表2可以推导出五个使能信号与模式指示位之间的逻辑关系如下:

75.en1=mode1,en2=not mode1,

76.en3=mode1,en4=not mode1,

77.en5=mode1 xnor mode2,其中xnor表示逻辑“异或非”或“同或”。

78.在表3中,当mode1=0时,指示先计算加法;当mode1=1时,指示先计算乘法。当mode2=0时,指示第三输入数据c不参与运算,并且当mode2=1时,指示第三输入数据c参与运算。

79.表3

80.mode2mode1运算模式en1en2en3en4en500a b

‑0‑

0001a*b0

‑0‑

110(a b)*c1010111(a*b) c01010

81.由该表3可以推导出五个使能信号与模式指示位之间的逻辑关系如下:

82.en1=not mode1,en2=mode1,

83.en3=not mode1,en4=mode1,

84.en5=mode1 xor mode2。

85.通过上述三种不同的对应关系可以看出,对于同一运算电路,可以通过将运算模式指示信号与多种(例如4种)运算模式进行对应,从而根据运算模式指示信号可以为各个选择器生成相应的使能信号,以实现运算模式指示信号所指示的运算模式,因此可实现运算电路配置的灵活性。可以理解,本领域技术人员还可以构想出其他对应关系,本披露在此方面没有限制。

86.上文中结合图5所示的运算电路示例性地说明了运算电路实现多种运算模式的实现方法。可以理解的是,在上述实施例的教导下,本领域技术人员还可修改运算电路的结构并进行相应参数的配置,从而实现对应的运算模式,此处不再详述。

87.本披露实施例还提供了一种芯片,其可以包括前面结合附图描述的任一实施例的运算电路。进一步地,本披露还提供了一种板卡,该板卡可以包括前述芯片。

88.根据不同的应用场景,本披露的电子设备或装置可以包括服务器、云端服务器、服务器集群、数据处理装置、机器人、电脑、打印机、扫描仪、平板电脑、智能终端、pc设备、物联网终端、移动终端、手机、行车记录仪、导航仪、传感器、摄像头、相机、摄像机、投影仪、手表、耳机、移动存储、可穿戴设备、视觉终端、自动驾驶终端、交通工具、家用电器、和/或医疗设备。所述交通工具包括飞机、轮船和/或车辆;所述家用电器包括电视、空调、微波炉、冰箱、电饭煲、加湿器、洗衣机、电灯、燃气灶、油烟机;所述医疗设备包括核磁共振仪、b超仪和/或心电图仪。本披露的电子设备或装置还可以被应用于互联网、物联网、数据中心、能源、交通、公共管理、制造、教育、电网、电信、金融、零售、工地、医疗等领域。进一步,本披露的电子设备或装置还可以用于云端、边缘端、终端等与人工智能、大数据和/或云计算相关的应用场景中。在一个或多个实施例中,根据本披露方案的算力高的电子设备或装置可以应用于

云端设备(例如云端服务器),而功耗小的电子设备或装置可以应用于终端设备和/或边缘端设备(例如智能手机或摄像头)。在一个或多个实施例中,云端设备的硬件信息和终端设备和/或边缘端设备的硬件信息相互兼容,从而可以根据终端设备和/或边缘端设备的硬件信息,从云端设备的硬件资源中匹配出合适的硬件资源来模拟终端设备和/或边缘端设备的硬件资源,以便完成端云一体或云边端一体的统一管理、调度和协同工作。

89.需要说明的是,为了简明的目的,本披露将一些方法及其实施例表述为一系列的动作及其组合,但是本领域技术人员可以理解本披露的方案并不受所描述的动作的顺序限制。因此,依据本披露的公开或教导,本领域技术人员可以理解其中的某些步骤可以采用其他顺序来执行或者同时执行。进一步,本领域技术人员可以理解本披露所描述的实施例可以视为可选实施例,即其中所涉及的动作或模块对于本披露某个或某些方案的实现并不一定是必需的。另外,根据方案的不同,本披露对一些实施例的描述也各有侧重。鉴于此,本领域技术人员可以理解本披露某个实施例中没有详述的部分,也可以参见其他实施例的相关描述。

90.在具体实现方面,基于本披露的公开和教导,本领域技术人员可以理解本披露所公开的若干实施例也可以通过本文未公开的其他方式来实现。例如,就前文所述的电子设备或装置实施例中的各个单元来说,本文在考虑了逻辑功能的基础上对其进行拆分,而实际实现时也可以有另外的拆分方式。又例如,可以将多个单元或组件结合或者集成到另一个系统,或者对单元或组件中的一些特征或功能进行选择性地禁用。就不同单元或组件之间的连接关系而言,前文结合附图所讨论的连接可以是单元或组件之间的直接或间接耦合。在一些场景中,前述的直接或间接耦合涉及利用接口的通信连接,其中通信接口可以支持电性、光学、声学、磁性或其它形式的信号传输。

91.在本披露中,作为分离部件说明的单元可以是或者也可以不是物理上分开的,作为单元示出的部件可以是或者也可以不是物理单元。前述部件或单元可以位于同一位置或者分布到多个网络单元上。另外,根据实际的需要,可以选择其中的部分或者全部单元来实现本披露实施例所述方案的目的。另外,在一些场景中,本披露实施例中的多个单元可以集成于一个单元中或者各个单元物理上单独存在。

92.在另外一些实现场景中,上述集成的单元也可以采用硬件的形式实现,即为具体的硬件电路,其可以包括数字电路和/或模拟电路等。电路的硬件结构的物理实现可以包括但不限于物理器件,而物理器件可以包括但不限于晶体管或忆阻器等器件。鉴于此,本文所述的各类装置(例如计算装置或其他处理装置)可以通过适当的硬件处理器来实现,例如中央处理器、gpu、fpga、dsp和asic等。进一步,前述的所述存储单元或存储装置可以是任意适当的存储介质(包括磁存储介质或磁光存储介质等),其例如可以是可变电阻式存储器(resistive random access memory,rram)、动态随机存取存储器(dynamic random access memory,dram)、静态随机存取存储器(static random access memory,sram)、增强动态随机存取存储器(enhanced dynamic random access memory,edram)、高带宽存储器(high bandwidth memory,hbm)、混合存储器立方体(hybrid memory cube,hmc)、rom和ram等。

93.依据以下条款可更好地理解前述内容:

94.条款1、一种运算电路,包括:

95.乘法器,其配置用于执行乘法运算;

96.加法器,其配置用于执行加法运算;以及

97.多个选择器,其配置用于根据相应的使能信号控制选择通路以连通输入数据与所述乘法器和/或加法器来执行指定的运算模式并输出对应结果;

98.其中所述运算模式具有包括乘法运算和/或加法运算的运算规则。

99.条款2、根据条款1所述的运算电路,其中所述多个选择器包括:

100.第一选择器,其第一输入端与第一数据输入端连接,其第二输入端与所述加法器的输出端连接,其输出端连接到所述乘法器的第一输入端;

101.第二选择器,其第一输入端与第一数据输入端连接,其第二输入端与所述乘法器的输出端连接,其输出端连接到所述加法器的第一输入端;

102.第三选择器,其第一输入端与第二数据输入端连接,其第二输入端与第三数据输入端连接,其输出端连接到所述乘法器的第二输入端;

103.第四选择器,其第一输入端与第二数据输入端连接,其第二输入端与第三数据输入端连接,其输出端连接到所述加法器的第二输入端;以及

104.第五选择器,其第一输入端与所述加法器的输出端连接,其第二输入端与所述乘法器的输出端连接,其输出端为所述运算电路的输出端。

105.条款3、根据条款2所述的运算电路,还包括:

106.逻辑电路,其配置用于根据运算模式指示信号,生成对应的使能信号以分别传递给所述多个选择器。

107.条款4、根据条款3所述的运算电路,其中所述运算模式指示信号包括两比特模式指示位,用于指示以下四种运算模式:

108.(a*b) c;(a b)*c;a*b;和a b;

109.其中a、b、c分别为所述运算电路的第一输入数据、第二输入数据和第三输入数据。

110.条款5、根据条款4所述的运算电路,其中所述两比特模式指示位中的第一比特用于指示第一输入数据a和第二输入数据b之间的乘法和加法的运算顺序,第二比特用于指示第三输入数据c是否参与运算。

111.条款6、根据条款5所述的运算电路,其中所述逻辑电路进一步用于:

112.基于第一比特的数值,确定所述第一选择器、第二选择器、第三选择器和第四选择器各自的使能信号;以及

113.基于第一比特和第二比特的数值,确定所述第五选择器的使能信号。

114.条款7、根据条款6所述的运算电路,其中所述第一选择器的使能信号与第三选择器的使能信号相同,第二选择器的使能信号与第四选择器的使能信号相同,并且第一选择器的使能信号与第二选择器的使能信号相反。

115.条款8、根据条款7所述的运算电路,其中所述逻辑电路进一步用于:

116.根据所述两比特模式指示位与所述四种运算模式的对应关系,将所述第一选择器的使能信号设置为等于所述两比特模式指示位中的第一比特的值或与之相反,以及将所述第五选择器的使能信号设置为等于所述第一比特和第二比特的异或结果或同或结果。

117.条款9、一种芯片,包括根据条款1

‑

8任一所述的运算电路。

118.条款10、一种板卡,包括根据条款9所述的芯片。

119.以上对本披露实施例进行了详细介绍,本文中应用了具体个例对本披露的原理及实施方式进行了阐述,以上实施例的说明只是用于帮助理解本披露的方法及其核心思想;同时,对于本领域的一般技术人员,依据本披露的思想,在具体实施方式及应用范围上均会有改变之处,综上所述,本说明书内容不应理解为对本披露的限制。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。