1.本发明属于应用于移动通信、微波通讯、雷达领域的半导体材料,具体地说,涉及一种低电压高线性共源共栅放大器。

背景技术:

2.随着半导体工艺的进步,系统集成度不断提高,由于集成电路的功耗和供电电压成平方关系,为降低系统的整体功耗,系统的电源电压不断降低。

3.同时,对于可植入式医疗器件、无线传感器网络、无线遥测网络等需要采用电池或环境能量供电的低压系统,需要保证无线系统能够在低电源电压下正常工作。

4.然而,对于无线系统中的射频前端,射频放大器作为射频前端中的核心器件,其性能直接决定了射频前端的性能。电源电压对射频放大器线性度,最大输出功率等核心参数具有决定性作用,低电源电压将导致器件关键指标变差甚至无法正常工作。

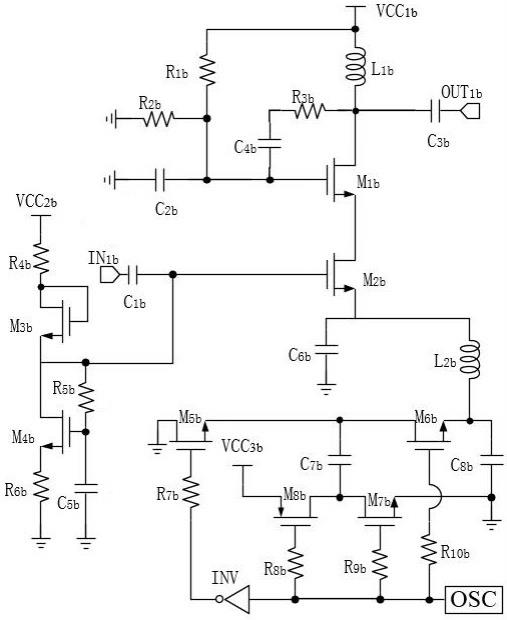

5.如图1所示,为一种现有的cascode放大器电路结构。cascode放大器指的是由共源和共栅两级放大器形成的级联结构。由于共源共栅结构中的共栅级晶体管m

1a

能够减小共源级晶体管m

2a

米勒电容的作用,使输入输出端得到良好隔离,从而提高了系统的稳定性。

6.同时cascode放大器还具有较高增益,电压摆幅大,输出功率能力强,工作频带宽等优点,在射频前端中得到了广泛应用。

7.但常规的cascode放大器存在以下缺点:由于cascode放大器的共源级晶体管和共栅极晶体管是一种堆积结构,加载在共源/共栅级晶体管上的电压只有单级放大器的一半。

8.当cascode放大器工作于较高电压时,共源级晶体管m

2a

的漏极有足够的电压空间保证系统处在稳定的状态。当电源电压降低时,随着电源电压的降低,cascode放大器的电压输出摆幅、线性度、输出功率能力也随之降低。当电源电压降低到一定程度时, m

1a

和m

2a

两个晶体管的阈值电压相互叠加,无法保证两个晶体管同时工作在饱和区,即无法保证电路能够处在良好的放大状态。

技术实现要素:

9.本发明针对现有技术的上述不足和需求,提出了一种低电压高线性共源共栅放大器,通过在常规的cascode放大器上增设电压提升电路,通过电压提升单元,提高了cascode放大器单元中nmos晶体管m

1b

漏极与nmos晶体管m

2b

源极之间的电势差,使cascode放大器单元输出电压摆幅和最大功率输出能力增强,进而有效提高了共源共栅放大器的线性度。

10.本发明具体实现内容如下:本发明提出了一种低电压高线性共源共栅放大器,包括cascode放大器和电压提升单元;所述cascode放大器包括级联的共源放大器和共栅放大器;所述共源放大器中设

置有用作共源级晶体管的nmos晶体管m

1b

,所述共栅放大器中设置有用作共栅级晶体管的nmos晶体管m

2b

;所述nmos晶体管m

2b

漏极与nmos晶体管m

1b

源极连接;所述nmos晶体管m

2b

的源极连接所述电压提升单元。

11.为了更好地实现本发明,进一步地,还包括直流偏置单元,所述直流偏置单元连接在所述nmos晶体管m

2b

的栅极上。

12.为了更好地实现本发明,进一步地,还包括直流分离单元,所述直流分离单元设置在所述cascode放大器和电压提升单元之间,所述cascode放大器中的nmos晶体管m

2b

的源极先连接所述直流分离单元,然后通过所述直流分离单元与所述电压提升单元连接。

13.为了更好地实现本发明,进一步地,所述cascode放大器还包括电阻r

1b

、电阻r

2b

、电阻r

3b

、电容c

1b

、电容c

2b

、电容c

3b

、电容c

4b

、和电感l

1b

;所述电容c

1b

的第一端与信号输入端in

1b

连接;所述nmos晶体管m

2b

的漏极与nmos晶体管m

1b

的源极连接,nmos晶体管m

1b

的栅极与电容c

4b

的第一端、电容c

2b

的第一端、电阻r

1b

的第一端、电阻r

2b

的第一端连接在一起;所述电容c

2b

的第二端与地连接,电阻r

2b

的第二端与地连接;所述电阻r

1b

的第二端与电感l

1b

的第一端、电源vcc

1b

连接;所述电容c

4b

的第二端与电阻r

3b

的第一端连接;所述电阻r

3b

的第二端与电感l

1b

的第二端、nmos晶体管m

1b

的漏极、电容c

3b

的第一端连接;所述电容c

3b

的第二端与信号输出端out

1b

连接。

14.为了更好地实现本发明,进一步地,所述电压提升单元包括nmos晶体管m

5b

、nmos晶体管m

6b

、nmos晶体管m

7b

、pmos晶体管m

8b

、电容c

7b

、电容c

8b

、反相器inv、振荡器osc、电阻r

7b

、电阻r

8b

、电阻r

9b

、电阻r

10b

;所述振荡器osc的输出端与反相器inv的输入端、电阻r

8b

的第一端、电阻r

9b

的第一端、电阻r

10b

的第一端连接在一起;所述反相器inv的输出端与电阻r

7b

的第一端连接,所述电阻r

7b

的第二端与nmos晶体管m

5b

的栅极连接;所述电阻r

8b

的第二端与pmos晶体管m

8b

的栅极连接,所述电阻r

9b

的第二端与nmos晶体管m

7b

的栅极连接,所述电阻r

10b

的第二端与nmos晶体管m

6b

的栅极连接;所述pmos晶体管m

8b

的源极与电源vcc

3b

连接,所述pmos晶体管m

8b

的漏极与nmos晶体管m

7b

的漏极、电容c

7b

的第一端连接;所述nmos晶体管m

7b

的源极与电容c

8b

的第一端、地连接;所述nmos晶体管m

5b

的漏极与地连接,nmos晶体管m

5b

的源极与电容c

7b

的第二端、nmos晶体管m

6b

的漏极连接,nmos晶体管m

6b

的源极与电容c

8b

的第二端、电感l

2b

的第二端连接;所述nmos晶体管m

6b

的源极与电容c

8b

的第二端之间搭接出端口作为所述电压提升电路与cascode放大器的nmos晶体管m

2b

的源极连接的端口。

15.为了更好地实现本发明,进一步地,所述直流偏置单元包括电阻r

4b

、电阻r

5b

、电阻r

6b

、nmos晶体管m

3b

、nmos晶体管m

4b

和电容c

5b

;所述电阻r

5b

的第一端与nmos晶体管m

3b

的源极、nmos晶体管m

4b

的漏极、电容c

1b

的第

二端、nmos晶体管m

2b

的栅极连接在一起;所述nmos晶体管m

3b

的栅极与nmos晶体管m

3b

的漏极、电阻r

4b

的第一端连接;所述电阻r

4b

的第二端与电源vcc

2b

连接;所述电阻r

5b

的第二端与电容c

5b

的第一端、nmos晶体管m

4b

的栅极连接;所述nmos晶体管m

4b

的源极与电阻r

6b

的第一端连接,所述电阻r

6b

的第二端与地连接,电容c

5b

的第二端与地连接;所述nmos晶体管m

3b

的源极与电阻r

5b

的第一端共同搭接出一个端口作为直流偏置单元与所述cascode放大器的nmos晶体管m

2b

的栅极连接的端口。

16.为了更好地实现本发明,进一步地,所述直流分离单元包括电容c

6b

和电感l

2b

;所述电容c

6b

的第一端与电感l

2b

的第一端、nmos晶体管m

2b

的源极连接,电容c

6b

第二端与地连接;所述电感l

2b

的第二端作为直流分离单元与所述电压提升单元连接的端口。

17.为了更好地实现本发明,进一步地,所述cascode放大器还包括电阻r

1b

、电阻r

2b

、电阻r

3b

、电容c

1b

、电容c

2b

、电容c

3b

、电容c

4b

、和电感l

1b

;所述电容c

1b

的第一端与信号输入端in

1b

连接;所述nmos晶体管m

2b

的漏极与nmos晶体管m

1b

的源极连接,nmos晶体管m

1b

的栅极与电容c

4b

的第一端、电容c

2b

的第一端、电阻r

1b

的第一端、电阻r

2b

的第一端连接在一起;所述电容c

2b

的第二端与地连接,电阻r

2b

的第二端与地连接;所述电阻r

1b

的第二端与电感l

1b

的第一端、电源vcc

1b

连接;所述电容c

4b

的第二端与电阻r

3b

的第一端连接;所述电阻r

3b

的第二端与电感l

1b

的第二端、nmos晶体管m

1b

的漏极、电容c

3b

的第一端连接;所述电容c

3b

的第二端与信号输出端out

1b

连接;所述电压提升单元包括nmos晶体管m

5b

、nmos晶体管m

6b

、nmos晶体管m

7b

、pmos晶体管m

8b

、电容c

7b

、电容c

8b

、反相器inv、振荡器osc、电阻r

7b

、电阻r

8b

、电阻r

9b

、电阻r

10b

;所述振荡器osc的输出端与反相器inv的输入端、电阻r

8b

的第一端、电阻r

9b

的第一端、电阻r

10b

的第一端连接在一起;所述反相器inv的输出端与电阻r

7b

的第一端连接,所述电阻r

7b

的第二端与nmos晶体管m

5b

的栅极连接;所述电阻r

8b

的第二端与pmos晶体管m

8b

的栅极连接,所述电阻r

9b

的第二端与nmos晶体管m

7b

的栅极连接,所述电阻r

10b

的第二端与nmos晶体管m

6b

的栅极连接;所述pmos晶体管m

8b

的源极与电源vcc

3b

连接,所述pmos晶体管m

8b

的漏极与nmos晶体管m

7b

的漏极、电容c

7b

的第一端连接;所述nmos晶体管m

7b

的源极与电容c

8b

的第一端、地连接;所述nmos晶体管m

5b

的漏极与地连接,nmos晶体管m

5b

的源极与电容c

7b

的第二端、nmos晶体管m

6b

的漏极连接,nmos晶体管m

6b

的源极与电容c

8b

的第二端、电感l

2b

的第二端连接;所述nmos晶体管m

6b

的源极与电容c

8b

的第二端之间搭接出端口作为所述电压提升电路与直流分离单元连接的端口;

所述直流偏置单元包括电阻r

4b

、电阻r

5b

、电阻r

6b

、nmos晶体管m

3b

、nmos晶体管m

4b

和电容c

5b

;所述电阻r

5b

的第一端与nmos晶体管m

3b

的源极、nmos晶体管m

4b

的漏极、电容c

1b

的第二端、nmos晶体管m

2b

的栅极连接在一起;所述nmos晶体管m

3b

的栅极与nmos晶体管m

3b

的漏极、电阻r

4b

的第一端连接;所述电阻r

4b

的第二端与电源vcc

2b

连接;所述电阻r

5b

的第二端与电容c

5b

的第一端、nmos晶体管m

4b

的栅极连接;所述nmos晶体管m

4b

的源极与电阻r

6b

的第一端连接,所述电阻r

6b

的第二端与地连接,电容c

5b

的第二端与地连接;所述nmos晶体管m

3b

的源极与电阻r

5b

的第一端共同搭接出一个端口作为直流偏置单元与所述cascode放大器的nmos晶体管m

2b

的栅极连接的端口;所述直流分离单元包括电容c

6b

和电感l

2b

;所述电容c

6b

的第一端与电感l

2b

的第一端、nmos晶体管m

2b

的源极连接,电容c

6b

第二端与地连接;所述电感l

2b

的第二端与所述直流分离单元的nmos晶体管m

6b

的源极与电容c

8b

的第二端之间搭接出端口连接。

18.本发明与现有技术相比具有以下优点及有益效果:(1)本发明通过电压提升单元,提高了cascode放大器单元中nmos晶体管m

1b

漏极与nmos晶体管m

2b

源极之间的电势差,使cascode放大器单元输出电压摆幅和最大功率输出能力增强,进而有效提高了共源共栅放大器的线性度;(2)本发明通过直流偏置单元为cascode放大器单元在全温(

‑

55℃至125℃)范围内提供稳定的直流工作点,避免了直流工作点漂移带来的性能损失;(3)本发明通过直流分离单元确保电压提升单元不影响cascode放大器单元的电特性,确保低电压高线性共源共栅放大器处于正常工作状态。

附图说明

19.图1为传统共源共栅放大器;图2为本发明的一种低电压高线性共源共栅放大器;图3为本发明与传统共源共栅放大器功率增益对比示意图;图4为本发明与传统共源共栅放大器输出三阶交调点对比示意图。

具体实施方式

20.为了更清楚地说明本发明实施例的技术方案,下面将结合本发明实施例中的附图,对本发明实施例中的技术方案进行清楚、完整地描述,应当理解,所描述的实施例仅仅是本发明的一部分实施例,而不是全部的实施例,因此不应被看作是对保护范围的限定。基于本发明中的实施例,本领域普通技术工作人员在没有做出创造性劳动前提下所获得的所有其他实施例,都属于本发明保护的范围。

21.在本发明的描述中,需要说明的是,除非另有明确的规定和限定,术语“设置”、“相连”、“连接”应做广义理解,例如,可以是固定连接,也可以是可拆卸连接,或一体地连接;可

以是机械连接,也可以是电连接;也可以是直接相连,也可以是通过中间媒介间接相连,可以是两个元件内部的连通。对于本领域的普通技术人员而言,可以具体情况理解上述术语在本发明中的具体含义。

22.实施例1:本实施例提出了一种低电压高线性共源共栅放大器,包括cascode放大器和电压提升单元;所述cascode放大器包括级联的共源放大器和共栅放大器;所述共源放大器中设置有用作共源级晶体管的nmos晶体管m

1b

,所述共栅放大器中设置有用作共栅级晶体管的nmos晶体管m

2b

;所述nmos晶体管m

2b

漏极与nmos晶体管m

1b

源极连接;所述nmos晶体管m

2b

的源极连接所述电压提升单元。

23.工作原理:通过电压提升单元,提高了cascode放大器单元中nmos晶体管m

1b

漏极与nmos晶体管m2b源极之间的电势差,使cascode放大器单元输出电压摆幅和最大功率输出能力增强,进而有效提高了共源共栅放大器的线性度。

24.实施例2:本实施例在上述实施例1的基础上,为了更好地实现本发明,进一步地,还包括直流偏置单元,所述直流偏置单元连接在所述nmos晶体管m2b的栅极上。

25.工作原理:直流偏置单元为cascode放大器单元在全温(

‑

55℃至125℃)范围内提供稳定的直流工作点,避免了直流工作点漂移带来的性能损失。

26.本实施例的其他部分与上述实施例1相同,故不再赘述。

27.实施例3:本实施例在上述实施例1

‑

2任一项的基础上,为了更好地实现本发明,进一步地,还包括直流分离单元,所述直流分离单元设置在所述cascode放大器和电压提升单元之间,所述cascode放大器中的nmos晶体管m2b的源极先连接所述直流分离单元,然后通过所述直流分离单元与所述电压提升单元连接。

28.工作原理:直流分离单元确保电压提升单元不影响cascode放大器单元的电特性,确保低电压高线性共源共栅放大器处于正常工作状态。

29.本实施例的其他部分与上述实施例1

‑

2任一项相同,故不再赘述。

30.实施例4:本实施例在上述实施例1

‑

3任一项的基础上,为了更好地实现本发明,进一步地,如图2所示,所述cascode放大器还包括电阻r

1b

、电阻r

2b

、电阻r

3b

、电容c

1b

、电容c

2b

、电容c

3b

、电容c

4b

、和电感l

1b

;所述电容c

1b

的第一端与信号输入端in

1b

连接;所述nmos晶体管m

2b

的漏极与nmos晶体管m

1b

的源极连接,nmos晶体管m

1b

的栅极与电容c

4b

的第一端、电容c

2b

的第一端、电阻r

1b

的第一端、电阻r

2b

的第一端连接在一起;所述电容c

2b

的第二端与地连接,电阻r

2b

的第二端与地连接;所述电阻r

1b

的第二端与电感l

1b

的第一端、电源vcc

1b

连接;所述电容c

4b

的第二端与电阻r

3b

的第一端连接;所述电阻r

3b

的第二端与电感l

1b

的第二端、nmos晶体管m

1b

的漏极、电容c

3b

的第一端连接;

所述电容c

3b

的第二端与信号输出端out

1b

连接。

31.工作原理:射频信号通过信号输入端in

1b

进入低电压高线性共源共栅放大器后,通过电容c

1b

,然后依次经过nmos晶体管m

2b

、nmos晶体管m

1b

将信号进行放大,通过电容c

3b

,由信号输出端out

1b

输出。

32.电感l

1b

为扼流电感,为cascode放大器单元供电;电阻r

1b

、电阻r

2b

对电源电压进行分压,为nmos晶体管m1b提供静态工作点,电容c2b可以补偿cascode放大器在高频时的增益损耗。电阻r3b和电容c4b形成负反馈通道,可以使cascode放大器得到更平坦的增益响应曲线、更容易实现宽带匹配和降低放大器的输入/输出驻波比。

33.本实施例的其他部分与上述实施例1

‑

3任一项相同,故不再赘述。

34.实施例5:本实施例在上述实施例1

‑

4任一项的基础上,为了更好地实现本发明,进一步地,如图2所示,所述电压提升单元包括nmos晶体管m5b、nmos晶体管m6b、nmos晶体管m7b、pmos晶体管m8b、电容c7b、电容c8b、反相器inv、振荡器osc、电阻r7b、电阻r8b、电阻r9b、电阻r10b;所述振荡器osc的输出端与反相器inv的输入端、电阻r

8b

的第一端、电阻r

9b

的第一端、电阻r

10b

的第一端连接在一起;所述反相器inv的输出端与电阻r

7b

的第一端连接,所述电阻r

7b

的第二端与nmos晶体管m

5b

的栅极连接;所述电阻r

8b

的第二端与pmos晶体管m

8b

的栅极连接,所述电阻r

9b

的第二端与nmos晶体管m

7b

的栅极连接,所述电阻r

10b

的第二端与nmos晶体管m

6b

的栅极连接;所述pmos晶体管m

8b

的源极与电源vcc

3b

连接,所述pmos晶体管m

8b

的漏极与nmos晶体管m

7b

的漏极、电容c

7b

的第一端连接;所述nmos晶体管m

7b

的源极与电容c

8b

的第一端、地连接;所述nmos晶体管m

5b

的漏极与地连接,nmos晶体管m

5b

的源极与电容c

7b

的第二端、nmos晶体管m

6b

的漏极连接,nmos晶体管m

6b

的源极与电容c

8b

的第二端、电感l

2b

的第二端连接;所述nmos晶体管m

6b

的源极与电容c

8b

的第二端之间搭接出端口作为所述电压提升电路与cascode放大器的nmos晶体管m

2b

的源极连接的端口。

35.工作原理:电压提升单元中,电阻r

7b

、电阻r

8b

、电阻r

9b

、电阻r

10b

为nmos晶体管m

5b

、pmos晶体管m

8b 、nmos晶体管m

7b 、nmos晶体管m

6b

和控制信号之间提供隔离。振荡器osc输出方波信号,直接控制pmos晶体管m

8b 、nmos晶体管m

7b 、nmos晶体管m

6b

的导通关断,方波信号通过反相器inv后,得到与振荡器osc输出方波信号相位相反的信号后,控制nmos晶体管m

5b

的导通关断。

36.在振荡器osc输出方波信号的前半周期,nmos晶体管m

6b

、nmos晶体管m

7b

关断,nmos晶体管m

5b

、pmos晶体管m

8b

导通,电容c

7b

由电源vcc

3b

充电到电源电压vcc

3b

,后半周期,nmos晶体管m

6b

、nmos晶体管m

7b

导通,nmos晶体管m

5b

、pmos晶体管m

8b

关断,由电容c

7b

给电容c

8b

充电,导通状态下, nmos晶体管m

7b

源漏极之间的内阻忽略不计,此时,电容c

8b

第一端与地相连,电压为0v,此时电容c

8b

第二端会得到一个负电压v1,电容c

8b

第二端与电感l

2b

第二端连接,所以此时的nmos晶体管m

2b

源极电压被钳位到v1。

37.v1值可由以下公式得到:;其中:;式中,为本发明的一种低电压高线性共源共栅放大器工作电流,为振荡器osc工作频率,为nmos晶体管m

6b

导通电阻,为nmos晶体管m

7b

导通电阻,为电容c7b等效串联电阻,为电容c8b等效串联电阻。

38.本实施例的其他部分与上述实施例1

‑

4任一项相同,故不再赘述。

39.实施例6:本实施例在上述实施例1

‑

5任一项的基础上,为了更好地实现本发明,进一步地,如图2所示,所述直流偏置单元包括电阻r

4b

、电阻r

5b

、电阻r

6b

、nmos晶体管m

3b

、nmos晶体管m

4b

和电容c

5b

;所述电阻r

5b

的第一端与nmos晶体管m

3b

的源极、nmos晶体管m

4b

的漏极、电容c

1b

的第二端、nmos晶体管m

2b

的栅极连接在一起;所述nmos晶体管m

3b

的栅极与nmos晶体管m

3b

的漏极、电阻r

4b

的第一端连接;所述电阻r

4b

的第二端与电源vcc

2b

连接;所述电阻r

5b

的第二端与电容c

5b

的第一端、nmos晶体管m

4b

的栅极连接;所述nmos晶体管m

4b

的源极与电阻r

6b

的第一端连接,所述电阻r

6b

的第二端与地连接,电容c

5b

的第二端与地连接;所述nmos晶体管m3b的源极与电阻r5b的第一端共同搭接出一个端口作为直流偏置单元与所述cascode放大器的nmos晶体管m2b的栅极连接的端口。

40.工作原理:电阻r4b、电阻r5b、电阻r6b、nmos晶体管m3b、nmos晶体管m4b和电容c5b所构成的直流偏置单元,可以在全温(

‑

55

°

c至125

°

c)范围内,为nmos晶体管m2b提供稳定的静态工作点。

41.本实施例的其他部分与上述实施例1

‑

5任一项相同,故不再赘述。

42.实施例7:本实施例在上述实施例1

‑

6任一项的基础上,为了更好地实现本发明,进一步地,所述直流分离单元包括电容c

6b

和电感l

2b

;所述电容c

6b

的第一端与电感l

2b

的第一端、nmos晶体管m

2b

的源极连接,电容c

6b

第二端与地连接;所述电感l2b的第二端作为直流分离单元与所述电压提升单元连接的端口。

43.工作原理:电容c6b和电感l2b构成的直流分离单元,cascode放大结构中的射频信号流过路径没有变化,即增加的电容和电感对于射频信号的传输路径没有影响,只是将直流进行了分离,并与电压提升单元连接。

44.本实施例的其他部分与上述实施例1

‑

6任一项相同,故不再赘述。

45.实施例8:本实施例在上述实施例1

‑

7任一项的基础上,如图3、图4所示:图3为本发明与传统共源共栅放大器功率增益对比示意图(am

‑

am曲线)。

△

为传统共源共栅放大器功率增益与输出功率之间的关系曲线,

○

为本发明功率增益与输出功率之间的关系曲线。从图3可以看出,本发明与传统共源共栅放大器相比较,在相同电源电压条件下,本发明提供的一种低电压高线性共源共栅放大器功率增益曲线随输出功率增加而降低1db时的输出功率(输出1db压缩点),明显高于传统共源共栅放大器。

46.图4为本发明与传统共源共栅放大器输出三阶交调点对比示意图。

△

为传统共源共栅放大器输出三阶交调点随频率变化的关系曲线,

○

为本发明输出三阶交调点随频率变化的关系曲线。从图4可以看出,本发明与传统共源共栅放大器相比较,本发明提供的一种低电压高线性共源共栅放大器输出三阶交调点更高,线性度更好。

47.以上所述,仅是本发明的较佳实施例,并非对本发明做任何形式上的限制,凡是依据本发明的技术实质对以上实施例所作的任何简单修改、等同变化,均落入本发明的保护范围之内。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。