1.本发明的实施例是涉及一种光掩模总成、其形成方法以及包括其的曝光工具。

背景技术:

2.光掩模总成(photomask assembly)是用于将图案(例如,管芯层图案、集成电路图案和/或类似图案)转移到晶片的设备。光掩模总成可包括上面形成有图案的光掩模以及保护所述图案免受损坏及灰尘影响的护膜层,否则所述损坏及灰尘可能会在图案转移到衬底时造成缺陷。

技术实现要素:

3.本发明实施例提供一种光掩模总成包括:光掩模、安装到光掩模的护膜框架以及安装到护膜框架的护膜。护膜框架包括一个或多个应力释放沟槽。

附图说明

4.结合附图阅读以下详细说明,会最好地理解本公开的各个方面。应注意,根据本行业中的标准惯例,各种特征并非按比例绘制。事实上,为使论述清晰起见,可任意增大或减小各种特征的尺寸。

5.图1是可在其中实施本文中阐述的系统和/或方法的示例性环境的图。

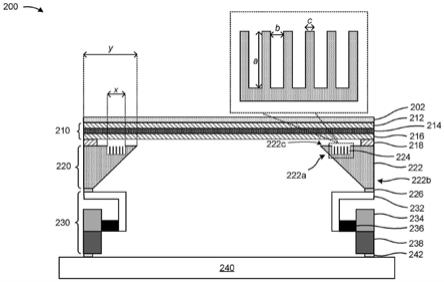

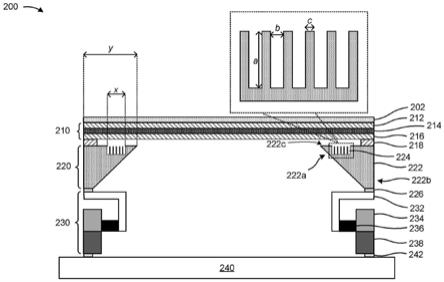

6.图2是本文中阐述的示例性光掩模总成的图。

7.图3a到图3i是本文中阐述的一个或多个示例性实施方案的图。

8.图4是示例性曝光工具的图。

9.图5是图1和/或图4所示一个或多个装置的示例性组件的图。

10.图6是与形成光掩模总成相关的示例性工艺的流程图。

具体实施方式

11.以下公开提供用于实施所提供主题的不同特征的许多不同实施例或实例。以下阐述组件及排列的具体实例以简化本公开。当然,这些仅为实例且不旨在进行限制。举例来说,以下说明中将第一特征形成在第二特征“之上”或第二特征“上”可包括其中第一特征与第二特征被形成为直接接触的实施例,且也可包括其中第一特征与第二特征之间可形成有附加特征从而使得所述第一特征与所述第二特征可不直接接触的实施例。另外,本公开可能在各种实例中重复使用参考编号和/或字母。这种重复使用是出于简洁及清晰的目的,而不是自身指示所论述的各种实施例和/或配置之间的关系。

12.此外,为易于说明,本文中可能使用例如“在

…

之下(beneath)”、“在

…

下方(below)”、“下部的(lower)”、“在

…

上方(above)”、“上部的(upper)”等空间相对性用语来阐述图中所示的一个元件或特征与另一(其他)元件或特征的关系。所述空间相对性用语旨在除图中所绘示的取向外还囊括装置在使用或操作中的不同取向。设备可具有其他取向

(旋转90度或处于其他取向),且本文中所使用的空间相对性描述语可同样相应地进行解释。

13.护膜可安装在护膜框架上,护膜框架将护膜与光掩模隔开。在对处理腔室进行抽气或将处理腔室加压到真空的光刻工艺期间,高压可能会导致护膜变形。在一些情形中,护膜发生变形可能会严重到足以导致护膜压靠护膜框架,此可能会使护膜破裂且对护膜造成其他类型的损坏。

14.本文中阐述的一些实施方案提供一种光掩模总成,所述光掩模总成被形成为使得在光掩模总成的护膜框架中形成应力释放沟槽。应力释放沟槽可减少或防止原本可因护膜发生变形所导致的护膜的损坏。应力释放沟槽可形成在护膜框架的区域中,以使得护膜框架能够与护膜一起变形,从而减少护膜框架对护膜造成的损坏量。

15.图1是可在其中实施本文中阐述的系统和/或方法的示例性环境100的图。如图1中所示,环境100可包括多个半导体处理工具102到110及传输装置112。所述多个半导体处理工具102到110可包括沉积工具102、曝光工具104、刻蚀工具106、显影工具108、光刻胶移除工具110和/或其他类似工具。示例性环境100中所包括的工具可包括在半导体清洁室、半导体铸造厂(semiconductor foundry)、半导体处理和/或制造设施和/或类似装置中。

16.沉积工具102是包括半导体处理腔室以及能够将各种类型的材料沉积到衬底上的一个或多个装置的半导体处理工具。在一些实施方案中,沉积工具102包括化学气相沉积(chemical vapor deposition,cvd)工具,例如原子层沉积(atomic layer deposition,ald)工具、外延工具、金属有机化学气相沉积(metal organic cvd,mocvd)工具、等离子体增强型化学气相沉积(plasma

‑

enhanced cvd,pecvd)工具或另一类型的cvd工具。在一些实施方案中,沉积工具102包括物理气相沉积(physical vapor deposition,pvd)工具,例如溅镀工具或另一类型的pvd工具。在一些实施方案中,示例性环境100包括多种类型的沉积工具102。

17.曝光工具104是能够将光刻胶层曝光到辐射源(例如紫外(ultraviolet,uv)光源(例如,深uv光源、极uv光源和/或类似光源)、x射线源和/或类似辐射源)的半导体处理工具。曝光工具104可将光刻胶层暴露到辐射源,以将图案从光掩模转移到光刻胶层。所述图案可包括用于形成一个或多个半导体装置的一个或多个半导体装置层图案,可包括用于形成半导体装置的一个或多个结构的图案,可包括用于对半导体装置的各个部分进行刻蚀的图案和/或可包括类似图案。在一些实施方案中,曝光工具104包括扫描仪(scanner)、步进机(stepper)或相似类型的曝光工具。

18.刻蚀工具106是能够对衬底、晶片或半导体装置的各种类型的材料进行刻蚀的半导体处理工具。举例来说,刻蚀工具106可包括湿式刻蚀工具、干式刻蚀工具和/或类似刻蚀工具。在一些实施方案中,刻蚀工具106包括填充有刻蚀剂的腔室,且将衬底在腔室中放置达特定时间周期,以移除衬底的特定大小的一个或多个部分。在一些实施方案中,刻蚀工具106可使用等离子体刻蚀或等离子体辅助刻蚀来对衬底的一个或多个部分进行刻蚀,此可涉及使用离子化气体来对所述一个或多个部分进行各向同性刻蚀或定向刻蚀。

19.显影工具108是以下半导体处理工具:所述半导体处理工具能够对已被暴露到辐射源的光刻胶层进行显影,从而对从曝光工具104转移到光刻胶层的图案进行显影。在一些实施方案中,显影工具108通过移除光刻胶层的未被暴露出的部分来对图案进行显影。在一

些实施方案中,显影工具108通过移除光刻胶层的被暴露出的部分来对图案进行显影。在一些实施方案中,显影工具108通过使用化学显影剂使光刻胶层的被暴露出的部分或未被暴露出的部分溶解来对图案进行显影。

20.光刻胶移除工具110是能够在刻蚀工具106移除衬底的一些部分之后从衬底移除光刻胶层的剩余部分的半导体装置。举例来说,光刻胶移除工具110可使用化学剥离剂和/或另一技术来从衬底移除光刻胶层。

21.传输装置112包括移动机器人、机械臂、有轨电车(tram)或轨道车(rail car)和/或以下另一类型的装置:所述另一类型的装置用于在半导体处理工具102到110之间传输光掩模总成(或其组件)、晶片和/或管芯、和/或将光掩模总成(或其组件)、晶片和/或管芯传输到其他位置(例如晶片架(wafer rack)、储藏室和/或类似位置)以及从所述其他位置传输光掩模总成(或其组件)、晶片和/或管芯。在一些实施方案中,传输装置112可为被编程为行进特定路径的装置和/或可半自主操作或自主操作。

22.提供图1中所示的装置的数目及排列作为一个或多个实例。实际上,与图1中所示的装置相比,可存在附加的装置、更少的装置、不同的装置或不同排列的装置。此外,图1中所示的两个或更多个装置可在单个装置内实施,或者图1中所示的单个装置可被实施成多个分布式装置。另外地或作为另外一种选择,环境100的一组装置(例如,一个或多个装置)可实行被阐述为由环境100的另一组装置实行的一种或多种功能。

23.图2是本文中阐述的示例性光掩模总成200的剖视图的图。光掩模总成200可为用于将图案(例如,管芯层图案、集成电路图案和/或类似图案)转移到晶片的设备。在一些实施方案中,可在曝光工具(例如,曝光工具104)中使用光掩模总成200。如图2中所示,光掩模总成200可包括各种组件和/或子系统,例如冷却层202、护膜210、护膜框架220、光掩模框架230及光掩模240或其他实例。

24.冷却层202包括耗散光刻图案化工艺期间产生的热量的材料层。冷却层202的热量耗散特性可减少翘曲、变形和/或其他热量相关的劣化。在一些实施方案中,冷却层202包含钌(ru)、碳基材料(例如,石墨、石墨烯、金刚石、碳纳米管和/或类似材料)或另一导热材料。冷却层202可具有介于从近似3纳米(nanometer,nm)到近似10nm的范围内的厚度。

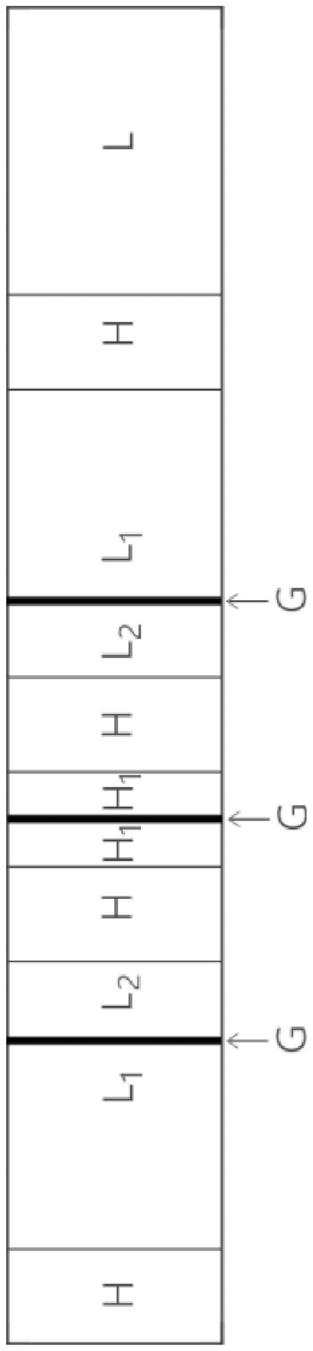

25.护膜210可包括可实行不同功能的多个层,例如位于功能层214上的顶盖层212以及上面形成有功能层214的另一顶盖层216。护膜210保护光掩模免受颗粒及其他碎片的影响且使颗粒及其他碎片在曝光工具中保持不聚焦,使得颗粒及其他碎片不会生成图案化图像,所述图案化图像可能会导致缺陷转移到晶片。

26.顶盖层212及216可保护功能层214免受化学物质和/或颗粒的影响。举例来说,功能层214可由硅形成,硅可易受环境化学物质和/或颗粒影响。在一些实施方案中,顶盖层212及216由氧化硅(sio

x

)、氮化硅(sin

x

)、碳化硅(sic

x

)或其混合物(例如氮化硅碳(sicn)、氮氧化硅(sion)和/或类似材料)形成。在一些实施方案中,顶盖层212及216包含氮化硼(bn)或碳化硼(bc)。顶盖层212及216是薄的,不会使护膜210的透明度劣化。在一些实例中,顶盖层的厚度介于从近似3nm到近似10nm的范围内。在一些实例中,顶盖层212及216中的每一者的厚度为近似5nm,此厚度具有近似10%或小于10%的变化。

27.功能层214可包含一种或多种材料,包括硅(例如多晶硅(poly

‑

si)、非晶硅(α

‑

si)、经掺杂的硅(例如经磷掺杂的硅(sip)))或硅系化合物。作为另外一种选择,功能层214

包含聚合物、石墨烯或其他合适的材料。功能层214可被形成到使得功能层214具有充足的机械强度的厚度,而不会降低功能层214的透明度。在一些实例中,功能层214可具有介于从近似30nm到近似50nm的范围内的厚度。

28.护膜210可通过缓冲层218贴合、结合、胶合或以其他方式固定到护膜框架220。缓冲层218可由粘合材料(例如热塑性弹性体(thermal plastic elastomer)或通过加热或干燥进行固化的其他大分子粘合材料)形成。在一些实施方案中,缓冲层218包含苯乙烯

‑

乙烯/丁烯

‑

苯乙烯(styrene ethylene/butylene styrene,sebs)橡胶、热塑性聚酯弹性体(thermoplastic polyester elastomer,tpe)、热塑性聚醚氨酯(thermoplastic polyether urethane,tpu)、热塑性烯烃弹性体(thermoplastic olefinic elastomer,tpo)、热塑性硫化胶(thermoplastic vulcanisate,tpv)或另一粘合材料。

29.护膜框架220可为安装结构,护膜210通过缓冲层218安装在所述安装结构上。护膜框架220可由硅、氧化硅(sio

x

)或具有足以支撑护膜210的刚性(例如,在光刻图案化工艺期间)的另一材料形成。如图2中所示,护膜框架220可具有多个表面222,例如内表面222a(例如,内表面222a可为成角度的、直的、弯曲的或者由不同的几何形状形成)、外表面222b及面对护膜210的顶表面222c。

30.护膜210可接合到护膜框架220的顶表面222c。具体来说,护膜210的顶盖层216可通过缓冲层218接合到顶表面222c的外部部分(例如,顶表面222c的朝向外表面222b或位于靠近外表面222b的部分)。如图2中进一步所示,护膜框架220可包括一个或多个应力释放沟槽224。所述一个或多个应力释放沟槽224可形成在护膜框架220的顶表面222c中。具体来说,所述一个或多个应力释放沟槽224可形成在顶表面222c的与其中护膜210贴合到护膜框架210的外部部分相邻的内部部分(例如,顶表面222c的朝向内表面222a或位于靠近内表面222a的部分)中。

31.在曝光工具的操作期间(例如,在光刻图案化工艺期间),所述一个或多个应力释放沟槽224可为护膜210提供应力释放。具体来说,在护膜210接触护膜框架220时(例如,由于护膜210发生变形),所述一个或多个应力释放沟槽224允许护膜框架220的内部部分与护膜210一起弯曲或变形。举例来说,当在曝光工具中使用光掩模总成200时(具体来说,当曝光工具被加压到真空时),由所述一个或多个应力释放沟槽224导致的护膜框架220的变形会减少施用到或施加在护膜210上的力或压力的大小。

32.如图2中所示,所述一个或多个应力释放沟槽224两端的宽度x可跨越护膜框架220的顶表面222c的宽度y的一部分。举例来说,护膜框架220的顶表面222c的宽度y可介于从近似1毫米(millimeter,mm)到近似5mm的范围内,而所述一个或多个应力释放沟槽224两端的宽度x可介于从近似5微米(micron,μm)到近似10μm的范围内。另外,如图2中的特写视图中所示,每一应力释放沟槽224可具有深度a及宽度b。在一些实施方案中,应力释放沟槽224的深度a大于应力释放沟槽224的宽度b。在一些实施方案中,应力释放沟槽224的深度a近似等于应力释放沟槽224的宽度b。在一些实施方案中,应力释放沟槽224的深度a小于应力释放沟槽224的宽度b。应力释放沟槽224的深度a的示例性范围可介于从近似1μm到近似5μm的范围内。

33.在一些实施方案中,所有应力释放沟槽224可具有近似相同的深度a和/或相同的宽度b。在一些实施方案中,两个或更多个应力释放沟槽224可具有不同的深度a和/或不同

的宽度b。另外,对于所有应力释放沟槽来说,相邻的应力释放沟槽224之间的间距c可相同,或者对于应力释放沟槽224的至少一个子集来说间距c可不同。

34.护膜框架220可通过缓冲层226贴合、接合、胶合或以其他方式固定到光掩模框架230。缓冲层226可由粘合材料(例如热塑性弹性体或通过加热或干燥进行固化的其他大分子粘合材料)形成。在一些实施方案中,缓冲层226包含苯乙烯

‑

乙烯/丁烯

‑

苯乙烯(styrene ethylene/butylene styrene,sebs)橡胶、热塑性聚酯弹性体(tpe)、热塑性聚醚氨酯(tpu)、热塑性烯烃弹性体(tpo)、热塑性硫化胶(tpv)或另一粘合材料。

35.光掩模框架230可固持和/或支撑护膜框架220及护膜210。光掩模框架230可用于将护膜框架220及护膜210安装到光掩模240。护膜框架220及光掩模框架230的高度可被配置成使得落于护膜210的表面上的颗粒和/或其他碎片在光刻曝光工艺期间不聚焦且不被转移到晶片。

36.光掩模框架230可包括用于减少护膜框架220与光掩模240之间的力传递的一个或多个组件,以使得护膜210与光掩模240之间的光掩模总成200的内部空腔能够通风和/或实现类似效果。举例来说,光掩模框架230可包括安装到侧壁234的支架232。过滤器236之间可放置在支架232与侧壁234,以使得在曝光工具的加压期间能够在内部空腔中实现通风及压力平衡。另外,光掩模框架230可包括密封垫(gasket)238,以在光掩模框架230与光掩模240之间提供结构隔离。密封垫238可减少或防止振动和/或其他机械应力从光掩模框架230转移到光掩模240。

37.光掩模框架230可通过缓冲层242贴合、接合、胶合或以其他方式固定到光掩模240。缓冲层242可由粘合材料(例如热塑性弹性体或通过加热或干燥进行固化的其他大分子粘合材料)形成。在一些实施方案中,缓冲层242包含苯乙烯

‑

乙烯/丁烯

‑

苯乙烯(sebs)橡胶、热塑性聚酯弹性体(tpe)、热塑性聚醚氨酯(tpu)、热塑性烯烃弹性体(tpo)、热塑性硫化胶(tpv)或另一粘合材料。

38.光掩模240可包括将在光刻图案化工艺期间转移到晶片上的抗蚀剂层的图案。光掩模240可通过一个或多个光掩模制作工艺(例如掩模坯件制作工艺(mask blank fabrication process)、掩模图案化工艺和/或类似工艺)形成。在掩模坯件制作工艺期间,通过在合适的衬底上沉积合适的层(例如,多个反射层、多个折射层和/或类似层)来形成掩模坯件。在一些实施方案中,掩模坯件的表面粗糙度小于近似50nm。

39.可在多层涂覆的衬底之上形成顶盖层(例如,钌),随后沉积吸收体层。接着可将掩模坯体图案化(例如,将吸收体层图案化),以在光掩模240上形成期望的图案。在一些实施方案中,在将掩模坯件图案化之前,可在吸收体层之上沉积抗反射涂布(anti

‑

reflective coating,arc)层。接着可使用图案化光掩模240将电路和/或装置图案转移到晶片上。

40.在一些实施方案中,光掩模240可被制作成包括不同的结构类型,例如(举例来说)二元强度掩模(binary intensity mask,bim)或相移掩模(phase

‑

shifting mask,psm)。示例性bim包括不透明吸收区及反射区,其中bim包括将转移到晶片的图案(例如,集成电路图案)。不透明吸收区包括被配置成吸收入射光(例如,入射极uv光)的吸收体。在反射区中,可移除吸收体(例如,在上述掩模图案化工艺期间),且由多层对入射光进行反射。另外,在一些实施方案中,光掩模240可为利用从光掩模240反射的光的相位差所生成干涉的psm。psm的实例包括交替psm(alternating psm,altpsm)、衰减psm(attenuated psm,attpsm)或无

铬psm(chromeless psm,cpsm)或其他实例。altpsm可包括设置在每一图案化掩模特征的任一侧上的移相器(相位相反)。在一些实例中,attpsm可包括具有大于零的透射率(例如,近似6%的强度透射率)的吸收体层。在一些情形中,例如由于cpsm不包含位于掩模上的移相器材料或铬,因此cpsm可被阐述为100%透射的altpsm。在一些实施方案中,psm的图案化层是具有与多层结构的材料堆叠相似的材料堆叠的反射层。

41.在一些实施方案中,依据将在其中使用光掩模总成200的曝光工具的类型而定,光掩模总成200包括其他组件、不同的组件和/或不同排列的组件。举例来说,如果光掩模总成200将在基于折射的曝光工具(例如,其中辐射能量行进穿过光掩模总成200的工具)中使用,则光掩模总成200可包括透明衬底及吸收层,所述吸收层被图案化成具有一个或多个开口,辐射能量可行进穿过所述一个或多个开口而不被吸收层吸收。作为另一实例,如果光掩模总成200将在基于反射的曝光工具(例如,其中辐射能量将从光掩模总成200反射的曝光工具)中使用,则光掩模总成200可包括涂覆有多个膜的衬底,以提供反射机制。在这些情形中,光掩模总成200可包括沉积在衬底上的硅与钼的多个交替层,以充当使辐射能量的反射最大化的布拉格反射器(bragg reflector)。

42.提供图2中所示的组件、结构和/或层的数目及排列作为一个或多个实例。实际上,与图2中所示的组件、结构和/或层相比,可存在附加的组件、结构和/或层;更少的组件、结构和/或层;不同的组件、结构和/或层;和/或不同排列的组件、结构和/或层。

43.图3a到图3i是示出本文中阐述的一个或多个示例性实施方案300的图。在一些实施方案中,示例性实施方案300可为形成光掩模总成(例如图2所示光掩模总成200和/或其中形成有应力释放沟槽的其他光掩模总成)的示例性实施方案。

44.图3a示出衬底302的俯视图及沿着线aa的剖视图。衬底302可包括由硅、晶体硅、多晶硅、非晶硅或另一材料形成的晶片(例如,200mm晶片、300mm晶片和/或类似晶片)。

45.图3b示出衬底302的另一俯视图及沿着线aa的另一剖视图。如图3b中所示,一个或多个半导体处理工具可在衬底302中形成一个或多个应力释放沟槽224。举例来说,沉积工具102可在衬底302上形成光刻胶层,曝光工具104可将光刻胶层暴露到辐射源以将光刻胶层图案化,显影工具108可对光刻胶层进行显影且移除光刻胶层的一些部分以暴露出图案,刻蚀工具106可对衬底302的一个或多个部分进行刻蚀以在衬底302中形成所述一个或多个应力释放沟槽224,且在刻蚀工具106对衬底302进行刻蚀之后,光刻胶移除工具110可移除光刻胶层的剩余部分(例如,使用化学剥离剂和/或另一技术)。

46.在一些实施方案中,所述一个或多个半导体处理工具可基于一个或多个参数形成所述一个或多个应力释放沟槽224。所述一个或多个参数可包括例如以上结合图2阐述的参数中的一者或多者,例如所述一个或多个应力释放沟槽224两端的总宽度、每一应力释放沟槽224的各别宽度、每一应力释放沟槽224的各别深度、相邻的应力释放沟槽224之间的间距和/或类似参数。另外地或作为另外一种选择,所述一个或多个参数可包括所述一个或多个应力释放沟槽224的数量、应力释放沟槽的形状或者所述一个或多个应力释放沟槽224的剖视轮廓或其他实例。另外地或作为另外一种选择,所述一个或多个参数可基于护膜总成200的护膜框架220的估测宽度、护膜框架220的估测高度、护膜框架220的材料、护膜210的厚度、其中将使用护膜总成200的光刻图案化工艺的估测压力、护膜框架的目标挠曲量、护膜总成200的内部空腔的宽度和/或类似参数。

47.图3c示出衬底302的另一俯视图及沿着线aa的另一剖视图。如图3c中所示,一个或多个半导体处理工具可形成阻挡层218。举例来说,沉积工具102可通过沉积工艺(例如旋转涂布工艺(spin

‑

coating process)、pvd工艺、cvd工艺或另一类型的沉积工艺)形成阻挡层218。在一些实施方案中,沉积工具102在衬底302的顶表面上形成阻挡层218。在一些实施方案中,沉积工具102在衬底302周围(例如,在顶表面、底表面及一个或多个侧表面上)形成阻挡层218。

48.图3d示出衬底302的另一俯视图及沿着线aa的另一剖视图。如图3d中所示,一个或多个半导体处理工具可形成用于形成护膜210的多个层。举例来说,沉积工具102可通过沉积工艺(例如旋转涂布工艺、pvd工艺、cvd工艺或另一类型的沉积工艺)形成所述多个层。在一些实施方案中,沉积工具102在阻挡层218的顶表面上及衬底302的顶表面之上形成所述多个层。在一些实施方案中,沉积工具102在阻挡层218上及衬底302周围(例如,在顶表面之上、底表面之上以及一个或多个侧表面之上)形成所述多个层。

49.在一些实施方案中,沉积工具102可通过以下方式形成护膜210的所述多个层:在阻挡层218的至少一部分上形成顶盖层216,在顶盖层216的至少一部分上形成功能层214,且在功能层214的至少一部分上(且在一些实施方案中,在顶盖层216的一部分上)形成顶盖层212。

50.图3e示出衬底302的仰视图及沿着线aa的另一剖视图。如图3e中所示,一个或多个半导体处理工具可在衬底302的底侧上向护膜210及阻挡层218中刻蚀出多个开口304,以界定护膜总成200的内周界及外周界。举例来说,刻蚀工具106可向护膜210及阻挡层218中刻蚀出开口304a,以界定护膜总成200的外周界。举例来说,刻蚀工具106可向护膜210及阻挡层218中刻蚀出开口304b,以界定护膜总成200的内周界。

51.图3f示出衬底302的另一仰视图及沿着线aa的另一剖视图。如图3f中所示,一个或多个半导体处理工具可从衬底302的底部穿过衬底302进行刻蚀,以界定护膜框架220。举例来说,刻蚀工具106可从开口304a穿过衬底302进行刻蚀以界定外表面222b,可从开口304b穿过衬底302进行刻蚀以界定内表面222a,等等。另外,刻蚀工具106可从开口304a穿过衬底302的顶侧上的阻挡层218及衬底302的顶侧上的护膜210的层进行刻蚀,以界定护膜210的周界。

52.图3g示出衬底302的另一仰视图及沿着线aa的另一剖视图。如图3g中所示,一个或多个半导体处理工具可从顶盖层216的底侧移除缓冲层218的一部分。举例来说,刻蚀工具106可实行等离子体刻蚀(例如,各向同性等离子体刻蚀),以移除位于护膜框架220的内表面222a之间的缓冲层218的部分。另外,刻蚀工具106可对位于护膜框架220的顶表面222c与缓冲层216的底表面之间的缓冲层218的一部分进行刻蚀。具体来说,刻蚀工具106可对位于护膜框架220中的顶表面222c的其中形成所述一个或多个应力释放沟槽224的部分之间的缓冲层218的部分进行刻蚀。在护膜框架220中的顶表面222c的其中形成所述一个或多个应力释放沟槽的部分上沉积缓冲层218可使缓冲层218的材料填充所述一个或多个应力释放沟槽224的至少一部分。因此,对位于护膜框架220中的顶表面222c的其中形成所述一个或多个应力释放沟槽224的部分之间的缓冲层218的部分进行刻蚀也会从所述一个或多个应力释放沟槽224移除缓冲层218的材料。

53.如图3h中所示,可将光掩模框架230贴合到光掩模总成200。将光掩模框架230贴合

到光掩模总成200可包括:使用缓冲层226将支架232贴合到护膜框架220的底部,使用设置在支架232与侧壁234之间的过滤器236将支架232贴合到侧壁234,且将侧壁贴合到密封垫238。如图3i中所示,可将光掩模240贴合到光掩模框架230。举例来说,可使用缓冲层242将光掩模240贴合到光掩模框架230。

54.如上所述,提供图3a到图3i作为一个或多个实例。其他实例可不同于针对图3a到图3i阐述的实例。

55.图4是示出示例性曝光工具400的图。在一些实施方案中,曝光工具400可为其中可使用光掩模总成(例如图2所示光掩模总成200和/或其中形成有应力释放沟槽的其他光掩模总成)的曝光工具的实例。如图4中所示,曝光工具400可包括发射辐射能量404的曝光源(或辐射源)402、多个光学组件(例如,光学组件406、光学组件408和/或类似光学组件)、被配置及设计成固定光掩模总成200的光掩模台410以及被配置成固定晶片414的晶片台412。曝光工具400可被设计成以合适的模式(例如步进扫描模式(step

‑

and

‑

scan mode)、扫描模式、步进模式和/或类似模式)实行光刻曝光工艺。

56.曝光源402可包括任何合适的光源,例如uv光源、深uv(deep uv,duv)源、极uv(euv)源、x射线源和/或类似光源。在一些实施方案中,曝光源402可包括具有近似436nm或近似365nm的波长的汞灯、具有近似248nm的波长的氟化氪(krf)准分子激光器、具有近似193nm的波长的氟化氩(arf)准分子激光器、具有近似157nm的波长的氟化物(f2)准分子激光器或具有期望波长(例如,低于近似100nm)的另一光源。在一些实施方案中,光源是具有近似13.5nm或小于13.5nm的波长的euv源。

57.光学组件406及408可接收来自曝光源402的辐射能量404,可通过光掩模总成200的图案调制辐射能量404,且可将辐射能量404导向涂覆在晶片414上的抗蚀剂层。在一些实施方案中,光学组件406及408中的每一者包括被设计成具有折射机制的一个或多个透镜或透镜系统。在一些实施方案中,例如在曝光工具400是基于euv的曝光工具的情况下,光学组件406及408中的每一者包括一个或多个具有反射机制的反射元件或反射镜。

58.光学组件406可包括照明单元,例如聚光透镜、聚光镜和/或类似照明单元。光学组件406可包括单个透镜或具有多个透镜的透镜模块和/或其他透镜组件。举例来说,光学组件406可包括微透镜阵列、遮蔽掩模(shadow mask)和/或被设计成有助于将来自曝光源402的辐射能量404导向光掩模总成200上的另一结构。

59.光学组件408可包括投影单元,例如投影透镜、投影镜和/或类似投影单元。光学组件408可具有被配置成向晶片414上的抗蚀剂层提供适当的照明的单个透镜元件或多个透镜元件。曝光工具400还可包括附加组件,例如用于在晶片414上形成光掩模总成200的图像的入射光瞳(entrance pupil)及出射光瞳(exit pupil)和/或类似组件。

60.光掩模台410被配置及设计成通过夹持机制(例如真空吸盘或静电吸盘(e

‑

chuck))来固定光掩模总成200。光掩模台410还可被设计成可操作以移动进行各种动作,例如扫描、步进和/或类似动作。在光刻曝光工艺(或曝光工艺)期间,光掩模总成200可被固定在光掩模台410上且被定位成使得在光掩模总成200上界定的集成电路图案(或图案层)可被转移到或成像在涂覆在晶片414上的抗蚀剂层上。

61.晶片台412被配置及设计成固定晶片414。晶片台412还被设计成提供各种运动,例如平移运动和/或旋转运动。在一些实施方案中,晶片414包括具有以下材料的半导体衬底:

元素半导体材料,例如晶体硅、多晶硅、非晶硅、锗或金刚石;化合物半导体材料,例如碳化硅或砷化镓;合金半导体材料,例如硅锗(sige)、砷磷化镓(gaasp)、砷化铝铟(alinas)、砷化铝镓(algaas)或镓铟磷(gainp);或其组合。晶片414可涂覆有抗蚀剂层,所述抗蚀剂层对刻蚀和/或离子植入具有抵抗性且对辐射能量404敏感。

62.晶片414可包括多个场域,所述多个场域具有针对一个或多个管芯在晶片414中界定的集成电路。在光刻曝光工艺期间,晶片414可一次曝光一个场域。举例来说,曝光工具400对在光掩模总成200中界定的集成电路图案进行扫描,且将集成电路图案转移到一个场域,接着步进到下一个场域,并重复进行扫描直到晶片414的所有场域被用尽为止。一个场域包括一个或多个电路管芯及位于边界区域处的框架区。在对涂覆在晶片414上的抗蚀剂层应用光刻曝光工艺之后,抗蚀剂层可被进行显影的化学物质进一步显影,以形成具有用于后续半导体处理(例如刻蚀或离子植入)的各种开口的图案化抗蚀剂层。

63.在一些实施方案中,曝光工具400被设计用于浸渍光刻。在光学组件408与晶片台412之间的空间中填充浸渍液体(例如水),使得光学折射率增大且光刻曝光工艺的光学分辨率得到增强。在一些实施方案中,曝光工具400包括被设计及配置成提供、容置及排出浸渍液体的各种组件。

64.如上所述,提供图4作为实例。其他实例可不同于针对图4阐述的实例。

65.图5是装置500的示例性组件的图。在一些实施方案中,沉积工具102、曝光工具104、刻蚀工具106、显影工具108、光刻胶移除工具110、传输装置112和/或曝光工具400可包括一个或多个装置500和/或装置500的一个或多个组件。如图5中所示,装置500可包括总线510、处理器520、存储器530、存储组件540、输入组件550、输出组件560及通信组件570。

66.总线510包括使得能够在装置500的组件之间进行有线通信和/或无线通信的组件。处理器520包括中央处理器(central processing unit)、图形处理单元(graphics processing unit)、微处理器、控制器、微控制器、数字信号处理器、现场可编程门阵列(field

‑

programmable gate array)、专用集成电路(application

‑

specific integrated circuit)和/或另一类型的处理组件。处理器520以硬件、固件或硬件与软件的组合来实施。在一些实施方案中,处理器520包括能够被编程以实行功能的一个或多个处理器。存储器530包括随机存取存储器(random access memory)、只读存储器(read only memory)和/或另一类型的存储器(例如,闪存(flash memory)、磁性存储器和/或光学存储器)。

67.存储组件540存储与装置500的操作相关的信息和/或软件。举例来说,存储组件540可包括硬盘驱动器(hard disk drive)、磁盘驱动器、光盘驱动器、固态盘驱动器、压缩盘、数字通用盘和/或另一类型的非暂时性计算机可读介质。输入组件550使得装置500能够接收输入,例如用户输入和/或感测的输入。举例来说,输入组件550可包括触摸屏、键盘、小键盘、鼠标、按钮、麦克风、开关、传感器、全球定位系统(global positioning system)组件、加速度计、陀螺仪、致动器和/或类似装置。输出组件560使得装置500能够例如通过显示器、扬声器和/或一个或多个发光二极管来提供输出。通信组件570使得装置500能够例如通过有线连接和/或无线连接与其他装置进行通信。举例来说,通信组件570可包括接收器、发射器、收发器、调制解调器、网络接口卡、天线和/或类似装置。

68.装置500可实行本文中阐述的一个或多个工艺。举例来说,非暂时性计算机可读介质(例如,存储器530和/或存储组件540)可存储供处理器520执行的一组指令(例如,一个或

多个指令、代码、软件代码、程序代码和/或类似指令)。处理器520可执行所述一组指令来实行本文中阐述的一个或多个工艺。在一些实施方案中,由一个或多个处理器520执行所述一组指令使得所述一个或多个处理器520和/或装置500实行本文中阐述的一个或多个工艺。在一些实施方案中,可使用硬连线电路系统代替指令或与指令结合来实行本文中阐述的一个或多个工艺。因此,本文中阐述的实施方案并不仅限于硬件电路系统与软件的任何特定组合。

69.提供图5中所示的组件的数目及排列作为实例。与图5中所示的组件相比,装置500可包括附加的组件、更少的组件、不同的组件或不同排列的组件。另外地或作为另外一种选择,装置500的一组组件(例如,一个或多个组件)可实行被阐述为由装置500的另一组组件实行的一个或多个功能。

70.图6是与形成光掩模总成相关联的示例性工艺600的流程图。在一些实施方案中,图6所示一个或多个工艺方块可由一个或多个半导体处理工具(例如,图1所示半导体处理工具102到110中的一个或多个)来实行。另外地或作为另外一种选择,图6所示一个或多个工艺方块可由装置500的一个或多个组件(例如处理器520、存储器530、存储组件540、输入组件550、输出组件560和/或通信接口570)来实行。

71.如图6中所示,工艺600可包括在衬底中形成多个应力释放沟槽(方块610)。举例来说,半导体处理工具(例如,沉积工具102、曝光工具104、刻蚀工具106、显影工具108、光刻胶移除工具110和/或类似工具)可在衬底(例如,衬底302)中形成多个应力释放沟槽(例如,应力释放沟槽224),如上所述。

72.如图6中进一步所示,工艺600可包括在形成所述多个应力释放沟槽之后在衬底上形成缓冲层(方块620)。举例来说,在形成所述多个应力释放沟槽之后,半导体处理工具(例如,沉积工具102)可在衬底上形成缓冲层(例如,缓冲层218),如上所述。

73.如图6中进一步所示,工艺600可包括在缓冲层上形成护膜(方块630)。举例来说,半导体处理工具(例如,沉积工具102)可在缓冲层上形成护膜(例如,护膜210),如上所述。

74.如图6中进一步所示,工艺600可包括对衬底进行刻蚀以形成用于在上面安装护膜的护膜框架(方块640)。举例来说,半导体处理工具(例如,刻蚀工具106)可对衬底进行刻蚀以形成用于在上面安装护膜的护膜框架(例如,护膜框架220),如上所述。

75.如图6中进一步所示,工艺600可包括移除护膜框架与护膜之间的缓冲层的一部分(方块650)。举例来说,半导体处理工具(例如,刻蚀工具106)可移除护膜框架与护膜之间的缓冲层的一部分,如上所述。

76.工艺600可包括附加的实施方案,例如任何单个实施方案或以下阐述的实施方案和/或与本文中其他地方阐述的一个或多个其他工艺结合的实施方案的任何组合。

77.在第一实施方案中,工艺600包括在护膜上形成冷却层(例如,冷却层202)。在第二实施方案(单独地或与第一实施方案结合)中,形成缓冲层包括在衬底周围形成缓冲层,在缓冲层上形成护膜包括在缓冲层周围形成护膜,且工艺600包括对缓冲层及衬底进行刻蚀以形成护膜框架。在第三实施方案(单独地或与第一实施方案及第二实施方案中的一者或多者结合)中,工艺600包括将护膜框架贴合到光掩模框架(例如,光掩模框架230)且将光掩模框架贴合到光掩模(例如,光掩模240)。

78.在第四实施方案(单独地或与第一实施方案到第三实施方案中的一者或多者结

合)中,形成护膜层包括:在缓冲层上形成第一顶盖层(例如,顶盖层216),在第一顶盖层上形成功能层(例如,功能层214),且在功能层上形成第二顶盖层(例如,顶盖层212)。在第五实施方案(单独地或与第一实施方案到第四实施方案中的一者或多者结合)中,工艺600包括移除护膜与护膜框架的其中形成所述多个应力释放沟槽的部分之间的缓冲层的另一部分。在第六实施方案(单独地或与第一实施方案到第五实施方案中的一者或多者结合)中,工艺600包括从所述多个应力释放沟槽移除缓冲层的材料。

79.在第七实施方案(单独地或与第一实施方案到第六实施方案中的一者或多者结合)中,形成所述多个应力释放沟槽包括将所述多个应力释放沟槽形成到基于以下中的至少一者的深度:护膜框架的估测宽度、护膜框架的估测高度、护膜框架的材料、护膜的厚度或护膜框架的目标挠曲量。

80.尽管图6示出工艺600的示例性方块,然而在一些实施方案中,与图6中所绘示的方块相比,工艺600可包括附加的方块、更少的方块、不同的方块或不同排列的方块。另外地或作为另外一种选择,可并行实行工艺600的方块中的两者或更多者。

81.以此种方式,光掩模总成200可被形成为使得应力释放沟槽224形成在光掩模总成200的护膜框架220中。应力释放沟槽224可减少或防止原本可因护膜210发生变形所导致的护膜210的损坏。应力释放沟槽224可形成在护膜框架220的区域中,以使得护膜框架220能够与护膜210一起变形,从而减少由护膜框架220对护膜210造成的损坏量。

82.如以上所更详细地阐述,本文中阐述的一些实施方案提供一种光掩模总成。所述光掩模总成包括:光掩模;护膜框架,安装到所述光掩模;以及护膜,安装到所述护膜框架。所述护膜框架包括一个或多个应力释放沟槽。

83.在一些实施例中,所述一个或多个应力释放沟槽形成在所述护膜框架的面对所述护膜的顶表面中。在一些实施例中,所述一个或多个应力释放沟槽将在所述护膜发生变形期间所述护膜接触所述护膜框架时允许所述护膜框架变形。在一些实施例中,所述一个或多个应力释放沟槽将在所述护膜发生变形期间减小由所述护膜框架施加在所述护膜上的力的大小。在一些实施例中,所述的光掩模总成还包括:缓冲层,位于所述护膜框架的顶表面的第一部分上,其中所述一个或多个应力释放沟槽形成在所述顶表面的第二部分中,且其中所述第一部分与所述第二部分是所述顶表面的不同部分。在一些实施例中,所述第一部分的位置靠近所述护膜框架的外表面;且其中所述第二部分的位置靠近所述护膜框架的内表面。

84.如以上所更详细地阐述,本文中阐述的一些实施方案提供一种方法。所述方法包括在衬底中形成多个应力释放沟槽。所述方法包括在形成所述多个应力释放沟槽之后,在所述衬底上形成缓冲层。所述方法包括在所述缓冲层上形成护膜。所述方法包括对所述衬底进行刻蚀,以形成用于在上面安装所述护膜的护膜框架。所述方法包括移除位于所述护膜框架与所述护膜之间的所述缓冲层的一部分。

85.在一些实施例中,所述的方法还包括:在所述护膜上形成冷却层。在一些实施例中,形成所述缓冲层包括:在所述衬底周围形成所述缓冲层;其中在所述缓冲层上形成所述护膜包括:在所述缓冲层周围形成所述护膜;且其中所述方法还包括:对所述缓冲层及所述衬底进行刻蚀,以形成所述护膜框架。在一些实施例中,所述的方法还包括:将所述护膜框架贴合到光掩模框架;以及将所述光掩模框架贴合到光掩模。在一些实施例中,形成所述护

膜包括:在所述缓冲层上形成第一顶盖层;在所述第一顶盖层上形成功能层;以及在所述功能层上形成第二顶盖层。在一些实施例中,所述的方法还包括:移除位于所述护膜与所述护膜框架的其中形成所述多个应力释放沟槽的部分之间的所述缓冲层的另一部分。在一些实施例中,所述的方法还包括:从所述多个应力释放沟槽移除所述缓冲层的材料。在一些实施例中,形成所述多个应力释放沟槽包括:将所述多个应力释放沟槽形成到一深度是基于以下中的至少一者:所述护膜框架的估测宽度,所述护膜框架的估测高度,所述护膜框架的材料,所述护膜的厚度,或所述护膜框架的目标挠曲量。

86.如以上所更详细地阐述,本文中阐述的一些实施方案提供一种曝光工具。所述曝光工具包括:辐射源;一个或多个光学组件;以及光掩模总成。所述光掩模总成包括:光掩模;护膜框架,安装到所述光掩模;以及护膜,安装到所述护膜框架。所述护膜框架包括多个应力释放沟槽,以在所述曝光工具的操作期间允许所述护膜框架与所述护膜一起变形。

87.在一些实施例中,所述多个应力释放沟槽将在所述曝光工具被加压时允许所述护膜框架与所述护膜一起变形。在一些实施例中,所述多个应力释放沟槽两端的宽度介于近似5微米到近似10微米的范围内。在一些实施例中,所述多个应力释放沟槽中的每一者的深度介于近似1微米到近似5微米的范围内。在一些实施例中,所述多个应力释放沟槽具有相同的深度或相同的宽度中的至少一者。在一些实施例中,所述多个应力释放沟槽中的两个或更多个具有不同的深度或不同的宽度中的至少一者。

88.以上概述了若干实施例的特征,以使所属领域中的技术人员可更好地理解本公开的各个方面。所属领域中的技术人员应理解,他们可容易地使用本公开作为设计或修改其他工艺及结构的基础来施行与本文中所介绍的实施例相同的目的和/或实现与本文中所介绍的实施例相同的优点。所属领域中的技术人员还应认识到,这些等效构造并不背离本公开的精神及范围,而且他们可在不背离本公开的精神及范围的条件下对本文作出各种改变、代替及变更。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。