1.本发明的实施方式涉及显示装置。

背景技术:

2.在显示装置中,各像素具有用于保持施加于显示元件的信号电位的保持电容。近年来,随着显示装置的高精细化,要求一边维持保持电容一边使像素电极小型化。为了增大保持电容,已知有具备各像素层叠而成的三层透明电极的结构。

3.现有技术文献

4.专利文献

5.专利文献1:日本特开2009

‑

58913号公报

技术实现要素:

6.发明所要解决的技术问题

7.本实施方式的目的在于,提供一种能够对随着高精细化而显示品质降低进行抑制的显示装置。

8.用于解决问题的技术方案

9.根据本实施方式,提供一种显示装置,具备第一基板;以及第二基板,与所述第一基板对置,所述第一基板具备:绝缘基板;开关元件,位于所述绝缘基板上并具有中继电极;有机绝缘膜,将所述开关元件覆盖,并具有贯通至所述中继电极的第一贯通孔;像素电极,在所述第一贯通孔内与所述中继电极相接;第一电容绝缘膜,在所述第一贯通孔内将所述像素电极覆盖;绝缘性的填充部件,至少填充在所述第一贯通孔内,并位于所述像素电极及所述第一电容绝缘膜上;以及共用电极,将所述填充部件覆盖。

附图说明

10.图1是表示本实施方式的显示装置的结构及等效电路的图。

11.图2是表示图1所示的像素的结构例的俯视图。

12.图3是沿图2所示的a

‑

b线的显示面板的剖视图。

13.图4是沿图2所示的c

‑

d线的第一基板的剖视图。

14.图5是沿图2所示的c

‑

d线的第一基板的剖视图的变形例。

15.图6是表示图5所示的中继电极re的详细的结构例的剖视图。

16.图7是表示第一基板的第一变形例的剖视图。

17.图8是表示第一基板sub1的第二变形例的剖视图。

18.图9是表示第一基板的第三变形例的剖视图。

19.图10是表示第一基板的第四变形例的剖视图。

20.图11是表示第一基板的第五变形例的剖视图。

21.图12是表示图3所示的电容电极的结构例的俯视图。

22.图13是表示图3所示的共用电极的结构例的俯视图。

具体实施方式

23.以下,参照附图对本实施方式进行说明。需要说明的是,公开仅为一个例子,本领域技术人员容易想到的保持发明主旨的适当变更当然包含在本发明的范围内。另外,为了使说明更加明确,与实际形态相比,附图中的各部分的宽度、厚度、形状等有时示意性地进行表示,说到底只是一个例子,并不限定本发明的解释。另外,在本说明书和各附图中,有时对发挥与在已出现的附图中描述过的要素相同或类似的功能的构成要素标注相同的附图标记,并适当省略重复的详细说明。

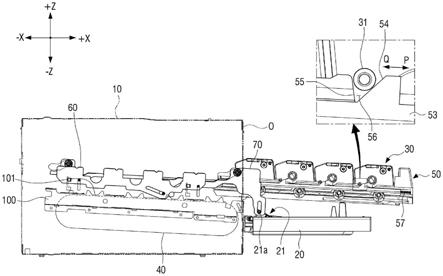

24.图1是表示本实施方式的显示装置dsp的结构及等效电路的图。

25.在一个例子中,第一方向x、第二方向y以及第三方向z相互正交,但也可以90度以外的角度交叉。第一方向x及第二方向y相当于与构成显示装置dsp的基板的主面平行的方向,第三方向z相当于显示装置dsp的厚度方向。在本说明书中,将朝向表示第三方向z的箭头的前端的方向称为上方(或者,仅称为上),将从箭头的前端朝向相反的方向称为下方(或者,仅称为下)。

26.显示装置dsp具备显示面板pnl和安装于显示面板pnl的布线基板wb。显示面板pnl是液晶显示面板,具备第一基板sub1、与第一基板sub1对置的第二基板sub2、密封材料se、液晶层lc、信号线s、扫描线g、开关元件sw、像素电极pe以及共用电极ce等。另外,显示面板pnl具备显示图像的显示区域da和包围显示区域da的非显示区域nda。此外,显示面板pnl也可以是具有电泳元件的显示面板。

27.第一基板sub1具有比第二基板sub2更向外侧露出的安装部ma。密封材料se位于非显示区域nda,将第一基板sub1与第二基板sub2粘接。在图1中,用斜线表示配置密封材料se的区域。显示区域da位于被密封材料se包围的内侧。显示面板pnl具备在显示区域da中沿第一方向x及第二方向y呈矩阵状配置的多个像素px。

28.上述的信号线s、扫描线g、开关元件sw、像素电极pe、共用电极ce、液晶层lc位于显示区域da。信号线s沿第二方向y延伸,扫描线g沿第一方向x延伸。开关元件sw例如由薄膜晶体管(tft)构成,与扫描线g及信号线s电连接。像素电极pe与开关元件sw电连接。像素电极pe分别与共用电极ce对置,通过在像素电极pe与共用电极ce之间产生的电场驱动液晶层lc。保持电容cs例如形成于与共用电极ce同电位的电极、以及与像素电极pe同电位的电极之间。

29.柔性的布线基板wb安装于安装部ma。另外,布线基板wb具备驱动显示面板pnl的驱动ic芯片2。此外,驱动ic芯片2也可以安装于安装部ma。

30.本实施方式的显示面板pnl可以是具备通过选择性地使来自第一基板sub1的背面侧的光透过而显示图像的透射显示功能的透射型、具备通过选择性地使来自第二基板sub2的前面侧的光反射而显示图像的反射显示功能的反射型、或者具备透射显示功能及反射显示功能的半透射型中的任意一种。

31.图2是表示图1所示的像素px的结构例的俯视图。在图2中,未图示电容电极和共用电极ce。电容电极的详细的平面如图10所示,共用电极ce的详细的平面如图11所示。

32.扫描线g1及g2分别沿第一方向x延伸,在第二方向y上隔开间隔地排列。信号线s1

及s2分别沿第二方向y延伸,在第一方向x上隔开间隔地排列。像素px相当于由扫描线g1及g2和信号线s1及s2划分的区域。

33.在一个例子中,开关元件sw是双栅极型的薄膜晶体管。开关元件sw具备中继电极re、半导体层sc、栅极电极ge1及ge2等。

34.中继电极re位于信号线s1与信号线s2之间。中继电极re的一部分与扫描线g1重叠。中继电极re在第一方向x上具有宽度w1。中继电极re与信号线s1之间的间隔gp1比宽度w1小。同样地,中继电极re与信号线s2之间的间隔gp2小于宽度w1。

35.半导体层sc具有第一部分sc1、第二部分sc2以及第三部分sc3。第一部分sc1位于信号线s1的正下方。第一部分sc1沿第二方向y延伸,并与扫描线g1交叉。第二部分sc2位于信号线s1与信号线s2之间。第二部分sc2沿第二方向y延伸,并与扫描线g1交叉。第三部分sc3沿第一方向x延伸,将第一部分sc1与第二部分sc2连接。

36.半导体层sc在贯通孔ch1处与信号线s1连接。信号线s1作为开关元件sw的源极电极发挥功能。另外,半导体层sc在贯通孔ch2处与中继电极re连接。中继电极re作为开关元件sw的漏极电极发挥功能。栅极电极ge1相当于扫描线g1中与第一部分sc1重叠的部分。栅极电极ge2相当于扫描线g1中与第二部分sc2重叠的部分。

37.像素电极pe位于由扫描线g1及g2和信号线s1及s2包围的区域。另外,像素电极pe与扫描线g1、中继电极re以及贯通孔ch2重叠。在图示的例子中,像素电极pe为具有沿第二方向y的长边的大致长方形状,遍及像素px的大致整体而形成。像素电极pe在贯通孔ch3处与中继电极re连接。贯通孔ch3与贯通孔ch2的一部分重叠。即,贯通孔ch2的一部分在俯视观察时位于贯通孔ch3内。需要说明的是,在图2中,贯通孔ch1至ch3图示为四边形状,但也可以为圆形状、各角倒角的形状。

38.贯通孔ch3具有端部eg1至eg4。另外,中继电极re具有端部eg11至eg14。端部eg1与端部eg11重叠。如图2所示,端部eg2与端部eg12重叠。端部eg3与贯通孔ch2重叠。端部eg4与扫描线g1重叠。

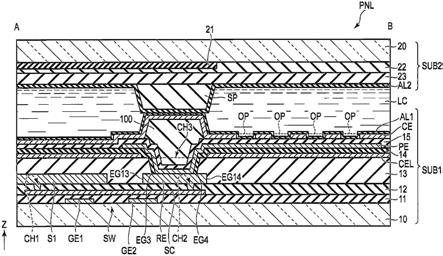

39.图3是沿图2所示的a

‑

b线的显示面板pnl的剖视图。本实施方式的显示面板pnl具备与利用沿基板主面的横向电场的显示模式对应的结构。

40.第一基板sub1具备绝缘基板10、开关元件sw、绝缘膜11至15、电容电极cel、像素电极pe、填充部件100、共用电极ce、取向膜al1等。

41.绝缘基板10是玻璃基板、树脂基板等透明的基板。开关元件sw位于绝缘基板10上。开关元件sw具备栅极电极ge1及ge2、半导体层sc以及中继电极re。栅极电极ge1及ge2设置于绝缘基板10之上,并被绝缘膜11覆盖。半导体层sc设置于绝缘膜11之上,并被绝缘膜12覆盖。图示的开关元件sw是栅极电极ge1及ge2位于比半导体层sc更靠绝缘基板10侧的位置的底栅型的薄膜晶体管。此外,开关元件sw也可以如后述那样为顶栅型的薄膜晶体管。信号线s1和中继电极re设置于绝缘膜12之上。信号线s1及中继电极re在贯通绝缘膜12的贯通孔ch1及ch2处分别与半导体层sc相接。

42.半导体层sc例如由多晶硅形成。栅极电极ge1及ge2、中继电极re以及信号线s1由铝(al)、钛(ti)、银(ag)、钼(mo)、钨(w)、铜(cu)、铬(cr)等金属材料、或者将这些金属材料组合而成的合金等形成。栅极电极ge1及ge2、中继电极re以及信号线s1既可以为单层结构,也可以为多层结构。

43.绝缘膜13将开关元件sw覆盖。绝缘膜13具有贯通至中继电极re的贯通孔ch3。贯通孔ch3的端部eg3及eg4相当于贯通孔ch3的底部的端部。端部eg3及eg4不与中继电极re的端部eg13及eg14重叠。端部eg3相对于端部eg13位于端部eg14侧。端部eg4相对于端部eg14位于端部eg13侧。电容电极cel形成于绝缘膜13之上。电容电极cel位于绝缘膜13与像素电极pe之间。电容电极cel不与贯通孔ch3重叠。绝缘膜14将电容电极cel覆盖,并且也形成于绝缘膜13之上。绝缘膜14的一部分延伸至贯通孔ch3内。像素电极pe形成于绝缘膜14之上。像素电极pe在贯通孔ch3中与中继电极re相接。由此,供给至信号线s1的信号电位经由中继电极re供给至像素电极pe。

44.绝缘膜15将像素电极pe覆盖。绝缘膜15也设置于贯通孔ch3内,在贯通孔ch3内也将像素电极pe覆盖。在图示的例子中,绝缘膜15也形成于绝缘膜14之上。填充部件100填充于贯通孔ch3内。填充部件100在贯通孔ch3内与绝缘膜15相接。填充部件100向第二基板sub2侧突出。此外,如后所述,填充部件100也可以不向第二基板sub2侧突出。填充部件100例如与形成于第一基板sub1的间隔件通过相同工序及相同材料形成。共用电极ce形成于绝缘膜15之上。另外,共用电极ce将填充部件100覆盖。另外,在一个例子中,共用电极ce具有多个开口op。开口op分别与像素电极pe对置。共用电极ce被取向膜al1覆盖。取向膜al1在开口op处也设置于绝缘膜15之上。在本实施方式中,在与贯通孔ch3重叠的位置,中继电极re、像素电极pe、绝缘膜15、填充部件100、共用电极ce、取向膜al1按此顺序重叠。

45.绝缘膜11、12、14以及15例如由氧化硅、氮化硅、氮氧化硅等无机绝缘材料形成。绝缘膜13例如由聚酰亚胺等有机绝缘材料形成。电容电极cel、像素电极pe以及共用电极ce例如由氧化铟锡(ito)、氧化铟锌(izo)等透明的导电材料形成。

46.在本实施方式中,电容电极cel与共用电极ce为相同电位。像素电极pe为与电容电极cel及共用电极ce不同的电位。在一个例子中,向电容电极cel和共用电极ce供给各像素共用的共用电位。该共同电位既可以为直流电位,也可以为交流电位。向像素电极pe供给与各像素对应的信号电位。用于驱动液晶层lc的边缘场主要由隔着绝缘膜15对置的像素电极pe和共用电极ce形成。用于保持信号电位的电容当然由隔着绝缘膜15对置的像素电极pe和共用电极ce形成,也由隔着绝缘膜14对置的电容电极cel和像素电极pe形成。

47.第二基板sub2具备绝缘基板20、遮光层21、滤色层22、外涂层23、间隔件sp以及取向膜al2。

48.绝缘基板20是玻璃基板、树脂基板等透明的基板。遮光层21及滤色层22设置于绝缘基板20的与第一基板sub1对置的一侧。遮光层21例如由着色为黑色的树脂形成,划分各像素px。在图示的例子中,遮光层21与信号线s1、开关元件sw、贯通孔ch3等对置。外涂层23将滤色层22覆盖。间隔件sp设置于外涂层23的与第一基板sub1对置的一侧。间隔件sp配置于与填充部件100重叠的位置。填充部件100隔着共用电极ce、取向膜al1及al2抵接于间隔件sp。取向膜al2将外涂层23及间隔件sp覆盖。此外,也可以不在间隔件sp的第一基板sub1侧的面上配置取向膜al2。同样地,也可以不在填充部件100的第二基板sub2侧配置取向膜al1。

49.液晶层lc位于第一基板sub1与第二基板sub2之间。第一基板sub1和第二基板sub2以取向膜al1与取向膜al2对置的方式配置。在取向膜al1与取向膜al2之间,通过未图示的间隔件形成规定的单元间隙(cell gap)。液晶层lc填充于该单元间隙内。

50.图4是沿图2所示的c

‑

d线的第一基板sub1的剖视图。此外,在图4中,省略绝缘基板10与绝缘膜11之间的半导体层sc的图示。

51.贯通孔ch3在第一方向x上具有宽度w11。中继电极re在第一方向x上具有宽度w12。在本实施方式中,宽度w12为宽度w11相等以下。需要说明的是,“相等”是指这些宽度相同,或者宽度w12比宽度w11稍大但具有可视为相同程度的微差。在本实施方式中,当这些宽度之差为

±

1μm左右时,视为它们是相等的。在图示的例子中,宽度w11及w12相互相等,端部eg1与端部eg11重叠,端部eg2与端部eg12重叠。此外,贯通孔ch3的宽度w11由贯通孔ch3的底部的宽度定义。另外,当在平面中,贯通孔ch3为圆形状时,将其直径设为贯通孔ch3的宽度。

52.图5是沿图2所示的c

‑

d线的第一基板sub1的剖视图的变形例。图5所示的结构与图4所示的结构相比较,在贯通孔ch3相对于中继电极re向信号线s1侧偏移这一点上不同。

53.在该变形例中,不仅是中继电极re,绝缘膜12也位于贯通孔ch3内。因此,绝缘膜14在贯通孔ch3内与绝缘膜12相接。贯通孔ch3的端部eg1位于比中继电极re的端部eg11更靠信号线s1侧的位置。另外,贯通孔ch3的端部eg2位于比中继电极re的端部eg12更靠信号线s1侧的位置。

54.中继电极re具有信号线s1侧的角部cn1和信号线s2侧的角部cn2。角部cn1未被绝缘膜13覆盖,且位于贯通孔ch3内。角部cn2被绝缘膜13覆盖。另外,像素电极pe将角部cn1覆盖。绝缘膜15例如在与角部cn1重叠的位置中断。像素电极pe从绝缘膜15的中断的部分露出。填充部件100将在角部cn1中露出的像素电极pe覆盖。

55.在显示装置高精细化的情况下,由于在中继电极re与信号线s1之间、以及中继电极re与信号线s2之间保持一定以上的距离以防发生短路,因此,有时中继电极re的宽度w12相对于贯通孔ch3的宽度w11相等或缩小。因此,在发生了中继电极re与贯通孔ch3的位置偏移的情况下,角部cn1、也就是中继电极re的上表面与绝缘膜12之间的台阶部位于贯通孔ch3内,通过该台阶部使绝缘膜15中断,从而有可能无法将像素电极pe完全覆盖。由此,存在像素电极pe与隔着绝缘膜15形成于像素电极pe之上的共用电极ce短路的危险。

56.根据本实施方式,在与贯通孔ch3重叠的位置,在像素电极pe与共用电极ce之间夹装填充部件100。因此,即使像素电极pe在角部cn1露出,也能够通过填充部件100保持像素电极pe与共用电极ce之间的绝缘状态。因此,能够防止像素电极pe与共用电极ce之间发生短路。

57.图6是表示图5所示的中继电极re的详细的结构例的剖视图。

58.中继电极re具有由钛形成的第一层rea、由铝形成的第二层reb、以及由钛形成的第三层rec。由于各层的蚀刻速率的不同,在对中继电极re进行蚀刻时,与由钛形成的第一层rea及第三层rec相比,由铝形成的第二层reb更被削除。因此,有时会成为第三层rec比第二层reb更突出的形状。第三层rec的突出的部分相当于角部cn1。由此,存在绝缘膜15的覆盖性恶化的情况。在这样的情况下,如上所述,也能够抑制像素电极pe与共用电极ce之间发生短路。

59.图7是表示第一基板sub1的第一变形例的剖视图。图7所示的结构与图4所示的结构相比较,在中继电极re的宽度w12比贯通孔ch3的宽度w11小这一点上不同。

60.在该变形例中,不仅是中继电极re,绝缘膜12也在贯通孔ch3内与绝缘膜14及像素

电极pe相接。贯通孔ch3的端部eg1位于比中继电极re的端部eg11更靠信号线s1侧的位置。另外,贯通孔ch3的端部eg2位于比中继电极re的端部eg12更靠信号线s2侧的位置。

61.角部cn1及cn2未被绝缘膜13覆盖,而位于贯通孔ch3内。另外,像素电极pe将角部cn1及cn2覆盖。绝缘膜15例如有时在与角部cn1及cn2(即台阶部)重叠的位置中断,但是,即使像素电极pe从绝缘膜15的中断的部分露出,也通过填充部件100将露出的像素电极pe覆盖。因此,能够防止像素电极pe与共用电极ce之间发生短路。

62.在这样的第一变形例中,也能够得到与上述实施方式同样的效果。

63.图8是表示第一基板sub1的第二变形例的剖视图。图8所示的结构与图7所示的结构相比较,在中继电极re位于信号线s2侧这一点上不同。

64.贯通孔ch3的端部eg1位于比中继电极re的端部eg11更靠信号线s1侧的位置。另外,贯通孔ch3的端部eg2与中继电极re的端部eg12重叠。角部cn1未被绝缘膜13覆盖,且位于贯通孔ch3内。另外,像素电极pe在贯通孔ch3内将角部cn1覆盖,并且将绝缘膜12的表面覆盖。其他结构与图7的结构相同,省略其说明。

65.在这样的第二变形例中,也能够得到与上述实施方式同样的效果。

66.图9是表示第一基板sub1的第三变形例的剖视图。图9所示的结构与图3所示的结构相比较,在开关元件sw为顶栅型的薄膜晶体管这一点上不同。

67.绝缘膜11将绝缘基板10覆盖。半导体层sc位于绝缘膜11之上。绝缘膜11a将半导体层sc覆盖。栅极电极ge1及ge2位于绝缘膜11a之上。绝缘膜12将栅极电极ge1及ge2覆盖。栅极电极ge1及ge2位于比半导体层sc更靠第二基板sub2侧的位置。贯通孔ch1及ch2贯通绝缘膜11a及12至半导体层sc。

68.在这样的第三变形例中,也能够得到与上述实施方式同样的效果。

69.图10是表示第一基板sub1的第四变形例的剖视图。图10所示的结构与图3所示的结构相比较,在第一基板sub1不具有电容电极cel这一点上不同。

70.像素电极pe位于绝缘膜13之上。另外,像素电极pe与贯通孔ch3的侧面ss相接。绝缘膜15将像素电极pe覆盖,也与绝缘膜13相接。

71.在这样的第四变形例中,也能够得到与上述实施方式同样的效果。

72.图11是表示第一基板sub1的第五变形例的剖视图。图11所示的结构与图3所示的结构相比,在填充部件100不向第二基板sub2侧突出这一点上不同。

73.填充部件100在第二基板sub2侧具有上表面100a。另外,将共用电极ce的上表面中位于开口op之间的部分设为上表面cea。上表面100a位于比上表面cea更靠绝缘基板10侧的位置。此时,第二基板sub2的间隔件sp既可以在与填充部件100重叠的位置抵接于第一基板sub1,也可以与第一基板sub1分离。

74.在这样的第五变形例中,也能够得到与上述实施方式同样的效果。

75.图12是表示图3所示的电容电极cel的结构例的俯视图。在图12中,省略了图2所示的像素电极pe的图示。另外,省略了图13所示的共用电极ce的图示。

76.电容电极cel与沿第一方向x排列的多个像素px重叠。更为具体而言,电容电极cel沿第一方向x延伸,并沿第二方向y隔开间隔地排列。电容电极cel形成为具有大致一定的宽度we1的带状。宽度we1小于相邻的扫描线g1至g3的间距p1。在此,宽度we1及间距p1均沿第二方向y规定。电容电极cel与扫描线g1至g3、信号线s1至s3、半导体层sc以及中继电极re分

别部分重叠,但不与贯通孔ch3重叠。即,沿第一方向x排列的贯通孔ch3位于沿第二方向y相邻的电容电极cel之间。

77.图13是表示图3所示的共用电极ce的结构例的俯视图。在图13中,省略了图2所示的像素电极pe的图示。另外,省略了图12所示的电容电极cel的图示。

78.共用电极ce与沿第一方向x及第二方向y排列的多个像素px重叠。在一个例子中,共用电极ce由单一的部件形成。共用电极ce与中继电极re、贯通孔ch3重叠。共用电极ce在各像素px中具有开口op。一个开口op与一个像素电极重叠。开口op位于相邻的信号线s1至s3之间以及相邻的扫描线g1至g3之间。开口op不与中继电极re重叠。在图示的例子中,开口op具有在第二方向y上延伸的第一部分opa、和在第一方向x上延伸的多个第二部分opb。多个第二部分opb与第一部分opa相连。由于共用电极ce具有开口op,因此,共用电极ce与像素电极pe重叠的面积比电容电极cel与像素电极pe重叠的面积小。

79.如以上所说明,根据本实施方式,能够得到可对随着高精细化而显示品质降低进行抑制的显示装置。

80.此外,虽然对本发明的几个实施方式进行了说明,但这些实施方式只是作为例子提出的,并未意图限定发明的范围。这些新的实施方式能够以其他的各种方式进行实施,在不脱离发明的主旨的范围内,能够进行各种省略、替换、变更。这些实施方式及其变形包含在发明的范围或主旨中,并且包含在权利要求书中所记载的发明和其均等的范围内。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。