1.本实用新型实施例涉及微电子技术领域,尤其涉及一种测试板。

背景技术:

2.随着微电子器件技术的发展,各种电子设备已经广泛应用于航空航天、军工、科研、通用电子等各种领域。芯片测试板是一个集成电路测试系统,用来进行芯片测试。

3.芯片测试板测试的主要目的是将合格的芯片与不合格的芯片区分开来,保证产品的质量、功能和可靠性。随着芯片测试板上集成电路的飞速发展,其规模越来越大,对电路的质量和可靠要求进一步提高,芯片测试板在测试中作为电子器件的载体,对芯片的功能测试和参数测试起到非常重要的作用。

4.但是,随着测试需求的要求越来越高,传统芯片测试板只能对单个待检测芯片进行检测。当存在大量待检测芯片时,芯片测试板的工作周期会明显增加,很大程度上降低了测试效率,增加了人工成本。

技术实现要素:

5.本实用新型实施例提供一种测试板,以实现同时对多个待测芯片的测试,提高测试效率,降低人工成本。

6.为实现上述目的,本实用新型实施例提供了一种测试板,所述测试板包括: pcb电路板;所述pcb电路板包括多个相同类型的芯片接入插座、引脚定义模块、电源模块和多个芯片外围电路;

7.所述芯片接入插座用于连接待测芯片;所述芯片接入插座包括多个测试引脚;所述引脚定义模块包括多个定义引脚;每个所述芯片接入插座外围设置一所述芯片外围电路;所述电源模块与所述引脚定义模块电连接;所述引脚定义模块通过所述芯片外围电路与所述芯片接入插座的多个测试引脚电连接。

8.可选的,所述测试板还包括开关模块;所述电源模块通过所述开关模块与所述引脚定义模块电连接。

9.可选的,所述测试板还包括多个显示模块,所述显示模块与所述芯片接入插座一一对应,所述显示模块串联在一一对应的所述芯片接入插座和所述引脚定义模块之间。

10.可选的,所述显示模块包括led指示灯。

11.可选的,至少部分数量的所述芯片接入插座的相同类型测试引脚电连接。

12.可选的,各所述芯片接入插座的测试引脚连接不同所述定义引脚。

13.可选的,所述pcb电路板还包括多个扩展测试引脚;至少部分所述测试引脚对应连接一所述扩展测试引脚。

14.实用新型本实用新型通过提供一种测试板,测试板包括:pcb电路板;pcb 电路板包括多个相同类型的芯片接入插座、引脚定义模块、多个芯片外围电路和电源模块;通过在pcb电路板设置多个芯片接入插座,对应设置引脚定义模块、多个芯片外围电路和电源模

块,实现对多个待测芯片的检测,很大程度提升检测效率,降低人工成本。

附图说明

15.为了更清楚地说明本实用新型实施例或现有技术中的技术方案,下面将对实施例或现有技术描述中所需要使用的附图做一简单地介绍,显而易见地,下面描述中的附图虽然是本实用新型的一些具体的实施例,对于本领域的技术人员来说,可以根据本实用新型的各种实施例所揭示和提示的器件结构,驱动方法和制造方法的基本概念,拓展和延伸到其它的结构和附图,毋庸置疑这些都应该是在本实用新型的权利要求范围之内。

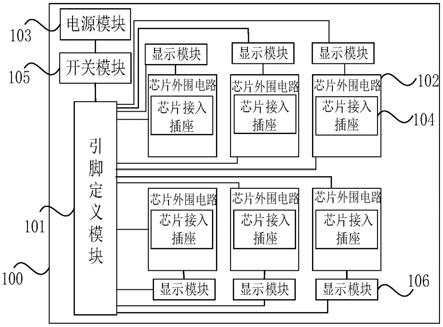

16.图1为本实用新型实施例提供的一种测试板的结构示意图;

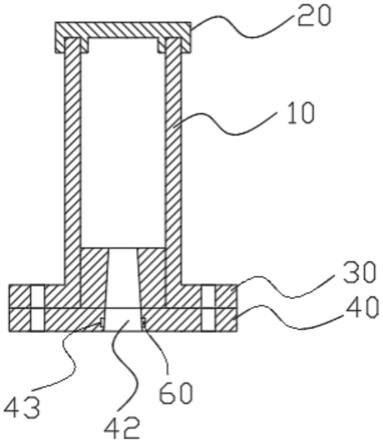

17.图2为本实用新型实施例提供的一种芯片接入插座的结构示意图;

18.图3为本实用新型实施例提供的一种引脚定义模块的结构示意图;

19.图4为本实用新型实施例提供的一种芯片外围电路的电路图;

20.图5为本实用新型实施例提供的一种电源模块的结构示意图;

21.图6为本实用新型实施例提供的另一种引脚定义模块的结构示意图;

22.图7为本实用新型实施例提供的另一种芯片接入插座的结构示意图;

23.图8为本实用新型实施例提供的另一种电源模块的结构示意图;

24.图9为本实用新型实施例提供的一种开关模块的结构示意图;

25.图10为本实用新型实施例提供的一种显示模块的结构示意图;

26.图11为本实用新型实施例提供的一种测试板的版图;

27.图12为本实用新型实施例提供的另一种测试板的版图;

28.图13为本实用新型实施例提供了一种测试板的设计方法的流程示意图。

具体实施方式

29.为使本实用新型的目的、技术方案和优点更加清楚,以下将参照本实用新型实施例中的附图,通过实施方式清楚、完整地描述本实用新型的技术方案,显然,所描述的实施例是本实用新型一部分实施例,而不是全部的实施例。基于本实用新型中的实施例所揭示和提示的基本概念,本领域的技术人员所获得的所有其他实施例,都属于本实用新型保护的范围。

30.图1为本实用新型实施例提供的一种测试板的结构示意图,如图1所示,本实用新型实施例提供了一种测试板,测试板包括:pcb电路板100;pcb电路板100包括引脚定义模块101、多个芯片外围电路102、电源模块103和多个相同类型的芯片接入插座104。

31.其中,图2为本实用新型实施例提供的一种芯片接入插座的结构示意图,如图2所示,示例性的设置有六个相同类型的芯片接入插座104,芯片接入插座104用于连接同一种待测芯片。芯片接入插座104包括多个测试引脚,用于与待测芯片的引脚电连接,实现对待测芯片的测试信号的输出或输出。芯片接入插座104的类型设置为相同类型,对同一种待测芯片的接入,实现对同一种待测芯片的测试,对于大批量的同一种待测芯片的测试需求,很大程度提高测试效率。图3为本实用新型实施例提供的一种引脚定义模块的结构示意图,如图3所示,示例性的设置有引脚定义模块1011(p1)和引脚定义模块1012(p2),引脚定义模块101包括多个定义引脚。引脚定义模块101的定义引脚根据芯片接入插座104的测试引脚进

行定义,以nor flash芯片为待测芯片,其中cs引脚、sclk引脚、si引脚均为信号输入引脚,so引脚为输出引脚,vcc引脚为电压信号引脚,vss引脚为接地端,wp引脚与hold引脚也为信号输入引脚,可应用于特殊检测需求。可根据测试系统所提供的开发手册,找到可供用户自定义引脚的引脚分配原理图,理清测试系统所提供的测试信号与引脚定义模块的各个引脚的对应关系,并给测试信号与其对应的定义引脚进行相同定义,方便后续对接收到的待测芯片输出的测试信号进行分析。如图2和图3所示,对应芯片接入插座104中cs引脚、sclk引脚、si引脚以及so引脚,在引脚定义模块101进行定义引脚的定义。多个芯片接入插座104的cs引脚、sclk 引脚、si引脚以及so引脚在引脚定义模块101均有与其对应的定义引脚,接通外部设备输出的测试信号即可实现对同一种待测芯片的同时检测,或是对单个待测芯片进行检测,很大程度提高了测试效率和灵活性。

32.继续参考图1,每个芯片接入插座104外围设置一芯片外围电路102,芯片外围电路102与待测芯片的测试需求相对应。示例性的,图4为本实用新型实施例提供的一种芯片外围电路的电路图。需要说明的是,图4仅示例性的展示一种芯片外围电路,并非对本实用新型实施例的芯片外围电路的具体结构的限定。以nor flash芯片为例,如图4所示,对应八个测试引脚设计芯片外围电路。芯片外围电路102包括去耦电容c11,主要用于消除电源中的高频噪声,如纹波或过冲等。r11、r12以及r13均为上拉电阻,主要目的是防止nor flash芯片引脚悬空引起引脚电平不确定而导致异常。r14、r15、r16、r17、r18以及 r19均为阻抗匹配电阻,主要用于防止阻抗不匹配出现信号反射现象,从而导致芯片信号异常。引脚定义模块101的定义引脚通过芯片外围电路102与对应的芯片接入插座104上的测试引脚电连接,保证待测芯片104接收或输出的测试信号正常,测试结果准确。图5为本实用新型实施例提供的一种电源模块的结构示意图,如图5所示,1端为输入端,2端和3端均为输出端。电源模块 103的输入端连接外部电源,用于给待测芯片提供电压信号。电源模块103的输出端与引脚定义模块101电连接,引脚定义模块101通过芯片外围电路102 与芯片接入插座104的多个测试引脚电连接,通过引脚定义模块101对接入的电压信号经芯片接入插座104传递至待测芯片,实现对待测芯片104的测试。

33.本实用新型实施例通过提供一种测试板,测试板包括pcb电路板。pcb电路板包括多个相同类型的芯片接入插座、引脚定义模块、多个芯片外围电路和电源模块。在pcb电路板设置多个芯片接入插座,对应设置引脚定义模块、多个芯片外围电路和电源模块,可以实现同时对多个相同待测芯片的检测,相比于现有技术只能对单个或特定待测芯片进行检测,很大程度提升检测效率,降低人工成本。

34.图6为本实用新型实施例提供的另一种引脚定义模块的结构示意图,图7 为本实用新型实施例提供的另一种芯片接入插座的结构示意图,图8为本实用新型实施例提供的另一种电源模块的结构示意图,图9为本实用新型实施例提供的一种开关模块的结构示意图,如图6、7、8和9所示,可选的,测试板还包括开关模块105;电源模块103通过开关模块105与引脚定义模块101电连接。

35.其中,开关模块105用于选择电源模块的提供的电压信号。电源模块103 提供的电压信号可以包括1.8v、3.3v或5v等。开关模块105可根据实际测试需求进行选择接入至引脚定义模块101的电压信号,实现对待测芯片104的测试,如图2、3和4所示,开关模块105选择电源模块103提供的3.3v电压信号接入引脚定义模块101的电压定义引脚vcc。如图6、7、8和

9所示,开关模块105可根据待测芯片的实际测试需求,选择电源模块103提供的3.3v电压信号或1.8v电压信号接入引脚定义模块101的电压定义引脚vcc,通过引脚定义模块101向待测芯片提供所需测试电压信号。

36.图10为本实用新型实施例提供的一种显示模块的结构示意图,图11为本实用新型实施例提供的一种测试板的版图。如图10和图11所示,可选的,测试板还包括多个显示模块106,显示模块106与芯片接入插座104一一对应,显示模块106串联在一一对应的芯片接入插座104和引脚定义模块101之间。

37.可选的,显示模块106包括led指示灯。

38.如图10和图11所示,以pcb电路板设置有引脚定义模块1011(p1)和 1012(p2)和六个芯片接入插座104为例,每一芯片接入插座104接入两个待测芯片,每一待测芯片对应设置有一led指示灯,每一led指示灯的正极电连接对应的芯片接入插座104的电压信号端vcc,每一led指示灯的负极电连接引脚定义模块101的led指示灯定义引脚(led1、led2、led3、led4、 led5、led6、led7、led8、led9、led10、led11、led12),同时每一 led指示灯与引脚定义模块101的led指示灯定义引脚之间均设置有滤波电阻,滤波电阻用于保证led指示灯输入和输出的信号正常。当某一待测芯片存在故障,故障信号会由芯片接入插座104的信号输出引脚so输出至引脚定义模块 101对应的so定义引脚,进而传输至测试系统,测试系统根据接收到的故障信号进行分析判断哪一个待测芯片发生故障,发送故障待测芯片对应的led指示灯点亮,使测试人员及时准确找到存在故障的待测芯片进行检修,节约时间,提高测试效率。如图8和图9所示,测试板上的电源模块103设置有不同的电源接口,不用电源接口可以满足待测芯片对不同电压的需求。通过开关模块105 进行不同电源接口的选择,实现对待测芯片104在不同电压下的测试。如图11 所示,电源模块103包括电连接外部电压信号的继电器k1、选择外部电压信号的继电器k2以及用于对接入的外部电压起到滤波作用的电容c1、电容c2、电容c3、电容c4、电感l1以及电感l2。位于芯片接入插座外围的d1、d2、 d3、d4、d5、d6、d7、d8、d9、d10、d1以及d12均为led指示灯。分压电阻r1、分压电阻r2和滤波电容c5;分压电阻r3、分压电阻r4和滤波电容 c6;分压电阻r5、分压电阻r6和滤波电容c7;分压电阻r7、分压电阻r8 和滤波电容c8;分压电阻r9、分压电阻r10和滤波电容c9以及分压电阻r11、分压电阻r12和滤波电容c10均构成芯片接入插座外围设置的芯片外围电路 102,保证输入或输出待测芯片的测试信号正常。

39.可选的,各芯片接入插座的测试引脚连接不同定义引脚。

40.其中,如图11所示,各个芯片接入插座104的测试引脚一一对应连接引脚定义模块101上的定义引脚,使每一测试引脚均有定义引脚与其对应,由于测试板可同时测试多个待测芯片,有效防止不同测试信号之间的串扰。

41.可选的,至少部分数量的待测芯片的相同类型测试引脚电连接。

42.对于实际测试板的应用过程中,如图11所示的测试板,多个子引脚定义模块1011和1012的设置,在测试过程中存在噪声信号的干扰,影响待测芯片104 的测试效果。图12为本实用新型实施例提供的另一种测试板的版图,以测试板设置有一个引脚定义模块1013和三个芯片接入插座为例,图12所示测试板上的芯片外围电路包括滤波电容c1_1、c1_2、c2_1、c2_2、c3_1和c3_2以及分压电阻r1_1、r1_2、r2_1、r2_2、r3_1和r3_2,图11和图12所示测试板的电源模块包括继电器k1、继电器k2、电容c1、电容c2、电容c3、电容c4、电感l1以及电

感l2。在待测芯片接收到测试信号后,相同类型测试引脚可以互通连接,如图12中的线aa连通六个待测芯片的同一引脚,不仅可以有效减少测试信号到不同待测芯片的测试引脚的时间延时,也可以减弱对测试结果的影响。

43.可选的,pcb电路板还包括多个扩展测试引脚;至少部分测试引脚对应连接一扩展测试引脚。

44.其中,测试板还包括多个扩展测试引脚。多个扩展测试引脚例如包括图13 所示的so1引脚、sclk1引脚、si引脚、cs引脚、so4引脚、sclk4引脚以及gnd引脚。外部设备例如示波器,可根据扩展测试引脚对输入或输出的信号波形进行检查,检查输入或输出的信号是否正确,保证测试结果的准确。

45.本实施例的技术方案通过提供一种测试板,测试板包括pcb电路板,pcb 电路板设置多个相同类型的芯片接入插座、引脚定义模块、多个芯片外围电路、电源模块、开关模块、显示模块以及多个扩展测试引脚,合理配置待测芯片的测试引脚与引脚定义模块的定义引脚的对应关系,实现对单个或多个待测芯片的检测,很大程度提升检测效率。设置显示模块和多个扩展引脚,对待测芯片的测试过程进行及时监控,降低人工成本。

46.图13为本实用新型实施例提供了一种测试板的设计方法的流程示意图,如图13所示,该设计方法包括:

47.s210,根据待测芯片类型构建芯片接入插座和芯片外围电路。

48.其中,根据待测芯片类型对应构建芯片接入插座,并结合芯片的应用事项构建芯片外围电路。参见图4所示的芯片外围电路,一般芯片外围电路主要包括去耦电容用于消除电源中的高频噪音,降低对测试的干扰;上拉电阻用于防止待测芯片的测试引脚悬空导致引脚电平异常;阻抗匹配电阻用于防止阻抗不匹配出现信号反射现象,从而导致待测芯片信号输入或输出异常。

49.s211,根据待测芯片类型构建引脚定义模块以及电源模块。

50.其中,根据待测芯片类型对应构建引脚定义模块,用于待测芯片的测试管教均能与引脚定义模块的定义引脚对应电连接,电源模块可根据待测芯片的测试需求进行相应设置。

51.s212,根据芯片接入插座、芯片外围电路、引脚定义模块以及电源模块构建测试板版图。

52.其中,待测芯片包括多个测试引脚;引脚定义模块包括多个定义引脚;每个芯片接入插座外围设置一芯片外围电路;电源模块与引脚定义模块电连接;引脚定义模块通过芯片外围电路与芯片接入插座的多个测试引脚电连接。

53.需要说明的是,本实用新型实施例提供的一种测试板的设计方法,设计得到的测试板具备上述任意所述的测试板相同或相应的效果,在此不过多赘述。

54.注意,上述仅为本实用新型的较佳实施例及所运用技术原理。本领域技术人员会理解,本实用新型不限于这里所述的特定实施例,对本领域技术人员来说能够进行各种明显的变化、重新调整、相互组合和替代而不会脱离本实用新型的保护范围。因此,虽然通过以上实施例对本实用新型进行了较为详细的说明,但是本实用新型不仅仅限于以上实施例,在不脱离本实用新型构思的情况下,还可以包括更多其他等效实施例,而本实用新型的范围由所附的权利要求范围决定。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。