1.本技术涉及显示技术领域,并且更具体地,涉及一种阵列基板及其制备方法、液晶面板和显示装置。

背景技术:

2.随着显示技术的不断发展,面板业超大世代线(generation)体产能释放,出现了例如8.5代线、10代线、10.5代线等高世代线。世代线越高,玻璃基板的尺寸越大,可以切割出来的液晶面板的面积也就越大,相应地,在制备液晶面板过程中使用的光罩(也称掩模版)尺寸也随之增大。

3.目前在制造大尺寸的液晶面板时,由于光罩的有效曝光面积不足以覆盖整个面板,因此多采用光罩拼接工艺进行制备。具体而言,就是将大尺寸的玻璃基板划分成若干区域,使用光罩依次对各个区域进行曝光,最后拼合成大尺寸的液晶面板。这种工艺在曝光过程会存在光罩拼接区域,而在该区域内会产生显示不均的问题,即拼接姆拉(mura)。

4.目前可以通过以下方式来改善拼接mura,一种是将光罩拼接区域的遮光层例如黑色矩阵或遮光金属层的宽幅增加,一种是采用马赛克拼接方法,将锐利的拼接线转变为模糊的拼接线,还有一种是将黑色矩阵设置于阵列基板一侧以此遮盖拼接区域。以上几种方式或者在一定程度上降低了液晶显示器的穿透率,或者额外带来了新的显示问题,例如色差、马赛克mura,可靠性问题等。

技术实现要素:

5.本技术提供一种阵列基板及其制备方法、液晶面板和显示装置,能够在不损失液晶显示器穿透率的情况下,改善拼接姆拉问题,提高面板性能。

6.第一方面,提供一种阵列基板,包括:第一基板;设置于所述第一基板上的栅极线和数据线;设置于所述第一基板上的薄膜晶体管阵列层、色阻层和第一透明导电层;所述薄膜晶体管阵列层包括源漏电极、半导体层和栅极,所述源漏电极与所述数据线同层,且所述源漏电极与所述数据线相连接,所述栅极包括第一栅极部分和第二栅极部分,所述第一栅极部分与所述栅极线同层,且所述第一栅极部分与所述栅极线相连接,所述第二栅极部分与所述数据线同向,且所述第二栅极部分与所述第一栅极部分断开;所述半导体层位于所述源漏电极与所述栅极之间,所述源漏电极位于所述半导体层靠近所述第一基板一侧;所述色阻层位于所述半导体层之上,所述色阻层在与所述栅极线对应的位置设置有挖空区,所述挖空区用于设置所述第一栅极部分和所述栅极线,所述第二栅极部分位于所述色阻层上与所述数据线对应的位置;所述色阻层上设置有过孔,所述第一透明导电层通过所述过孔与所述源漏电极相接触。

7.本技术实施例中,“设置于所述第一基板上”可以是直接设置于第一基板上,也可以是间接设置于第一基板上。

8.本技术实施例中,“所述源漏电极与所述数据线同层”可以理解为源漏电极与数据

线处于同一膜层。同理,“第一栅极部分与所述栅极线同层”可以理解为第一栅极部分与栅极线处于同一膜层。

9.本技术实施例中,“第二栅极部分与第一栅极部分断开”,指的是第二栅极部分与第一栅极部分不相连或不接触,或者第二栅极部分与栅极线不相连。

10.本技术实施例提供的阵列基板中,将色阻层制备在阵列基板一侧,并采用顶栅结构的薄膜晶体管,其中色阻层位于栅极与源漏电极之间,可以利用栅极遮挡光线。栅极与源漏电极之间的距离相比现有技术中黑色矩阵与源漏电极之间的距离缩短,可以有效将穿透光线和反射式光线遮挡住。这样栅极和黑色矩阵可以设计的宽度较小一些,从而能够在不损失开口率的前提下,解决或改善拼接mura的问题。

11.另外,本技术实施例采用coa技术,将色阻层直接制作在阵列基板上,不存在彩膜基板与阵列基板的对位问题,所以可以降低显示面板制备过程中对盒制程的难度,避免了制盒时的误差,因此黑色矩阵可以设计为窄线宽,可以提高像素的开口率。

12.而且,当用栅极作为遮挡层时,与数据线同向的栅极在各处的宽幅可以相同,即不需要在拼接区域加宽遮光层的宽幅。因此液晶面板开口设计在光罩拼接区域和非拼接区域一致,不会带来新的显示问题,例如马赛克拼接导致的马赛克mura,直接拼接导致的色差等。

13.本技术实施例中,栅极线与栅极位于同层,且可以在同一制程中形成。数据线与源漏电极同层,且可以在同一制程中形成。

14.本技术实施例中的栅极包括的第一栅极部分为与栅极驱动器相连的部分,需要接收驱动信号,栅极包括的第二栅极部分为无源栅极,仅用于遮光,不用于驱动薄膜晶体管。

15.本技术实施例中,色阻层位于半导体层之上,在色阻层上开设有缺口,该缺口用于设置第一栅极部分和栅极线,因此此处第一栅极部分与色阻层相当于在同一水平层上。第二栅极部分则位于色阻层之上的与数据线对应的位置上,第二栅极部分的正投影覆盖数据线。因为色阻层位于数据线与第二栅极部分之间,则第二栅极部分可以起到遮光作用。

16.结合第一方面,在一种可能的实现方式中,所述半导体层为金属氧化物半导体层。

17.金属氧化物半导体层的光电效应较弱,当光入射到半导体层上时,对半导体层的特性影响较小。

18.结合第一方面,在一种可能的实现方式中,所述半导体层的材料为氧化铟镓锌igzo。

19.本技术实施例采用顶栅结构tft,半导体层采用igzo,该材料对光不敏感,能够保证tft器件的可靠性。

20.结合第一方面,在一种可能的实现方式中,所述阵列基板还包括:设置于所述第一基板与所述薄膜晶体管阵列层之间的透明层,所述透明层包括对位标记。

21.阵列基板上的膜层在制备时需要用到掩模版,掩模版的定位需要以对位标记来进行定位。本技术实施例中在透明层上做对位标记,可以提高定位精度。

22.结合第一方面,在一种可能的实现方式中,所述透明层通过激光镭射于所述第一基板上。

23.本技术实施例中采用激光镭射形成透明层,当在透明层上做对位标记时,可以通过激光进行定位,能够定位相距基板边缘更精确的位置。这样基于对位标记形成的图形距

离边缘的位置更加精确,这样栅极和黑色矩阵bm可以设计较小的宽幅,间接地提升了开口率。

24.结合第一方面,在一种可能的实现方式中,所述透明层为氧化铟锡ito膜。

25.结合第一方面,在一种可能的实现方式中,所述阵列基板还包括:设置于所述色阻层之上的垫料,所述垫料填充于所述过孔中。

26.本技术实施例中将垫料例如ps制备在阵列基板一侧,可以利用垫料将过孔填充,起到防腐蚀的作用,提高了可靠性。

27.结合第一方面,在一种可能的实现方式中,所述阵列基板还包括:与所述第一透明导电层相绝缘的第二透明导电层,所述第二透明导电层用于形成公共电极;其中,所述第二透明导电层设置于所述薄膜晶体管阵列层与所述第一透明导电层之间;或者,所述第二透明导电层设置于所述第一透明导电层之上。

28.第二透明导电层用作公共电极,可以位于第一透明导电层上方,可以位于第一透明导电层下方。

29.结合第一方面,在一种可能的实现方式中,所述薄膜晶体管阵列层还包括:位于所述半导体层两侧的第一绝缘层和第二绝缘层;其中,所述半导体层与所述源漏电极相接触,并通过所述第一绝缘层相隔;所述半导体层与所述栅极通过所述第二绝缘层相隔。

30.该第一绝缘层和第二绝缘层为二氧化硅等有氧绝缘层,用于保护为半导体层的驱动提供氧富集环,从而稳定半导体层以及tft器件的特性。

31.结合第一方面,在一种可能的实现方式中,所述阵列基板还包括:位于所述栅极两侧的第三绝缘层和第四绝缘层;其中,所述栅极与所述色阻层通过所述第三绝缘层相隔;所述栅极与所述第一透明导电层通过所述第四绝缘层相隔。

32.本技术实施例中,第三绝缘层、第四绝缘层一般采用氮化硅(silicon nitride,iv)(sinx)或二氧化硅(silica)(sio2)制成,主要起绝缘作用,保护薄膜晶体管、栅极线和数据线。

33.第二方面,提供了一种阵列基板的制备方法,提供第一基板;在所述第一基板上设置第一金属层,对所述第一金属层进行图形化处理形成薄膜晶体管的源漏电极,和与所述源漏电极相连接的数据线;在所述第一金属层上形成第一绝缘层,所述第一绝缘层覆盖所述源漏电极和所述数据线,并延伸至所述第一基板上,对所述第一绝缘层进行图形化处理使得所述源漏电极的部分漏出;在所述第一绝缘层上形成所述薄膜晶体管的半导体层,所述半导体层与所述源漏电极漏出的部分相接触;在所述半导体层上形成第二绝缘层,所述第二绝缘层覆盖所述半导体层并延伸至所述第一绝缘层上;在所述第二绝缘层上形成色阻层,对所述色阻层进行图形化处理,得到所述色阻层在与栅极线对应的位置的挖空区;在所述色阻层上形成第三绝缘层;在所述第三绝缘层上形成第二金属层,对所述第二金属层进行图形化处理得到所述薄膜晶体管的栅极和与所述栅极相连接的栅极线,其中所述栅极包括第一栅极部分和第二栅极部分,所述第一栅极部分与所述栅极线同向,所述第二栅极部分与所述数据线同向,且所述第二栅极部分与所述第一栅极部分断开,所述第二栅极部分位于所述色阻层上与所述数据线对应的位置;在所述第二金属层上形成第四绝缘层,所述第四绝缘层覆盖所述栅极并延伸至所述第三绝缘层上;在所述第一绝缘层、所述第二绝缘层、所述色阻层、所述第三绝缘层、所述第四绝缘层上的对应位置开设过孔;在所述第四绝

缘层上形成第一透明导电层,对所述第一透明导电层进行图形化处理得到像素电极,所述像素电极通过所述过孔与所述源漏电极相接触。

34.本技术实施例提供的阵列基板的制备方法中,将色阻层制备在阵列基板一侧,并采用顶栅结构的薄膜晶体管,其中色阻层位于栅极与源漏电极之间,可以利用栅极遮挡光线。栅极与源漏电极之间的距离相比现有技术中黑色矩阵与源漏电极之间的距离缩短,可以有效将穿透光线和反射式光线遮挡住。这样栅极和黑色矩阵可以设计的宽度较小一些,从而能够在不损失开口率的前提下,解决或改善拼接mura的问题。

35.另外,本技术实施例采用coa技术,将色阻层直接制作在阵列基板上,不存在彩膜基板与阵列基板的对位问题,所以可以降低显示面板制备过程中对盒制程的难度,避免了制盒时的误差,因此黑色矩阵可以设计为窄线宽,可以提高像素的开口率。

36.而且,当用栅极作为遮挡层时,与数据线同向的栅极在各处的宽幅可以相同,即不需要在拼接区域加宽遮光层的宽幅。因此液晶面板开口设计在光罩拼接区域和非拼接区域一致,不会带来新的显示问题,例如马赛克拼接导致的马赛克mura,直接拼接导致的色差等。

37.结合第二方面,在一种可能的实现方式中,所述在所述第一基板上设置第一金属层,包括:在所述第一基板上直接形成所述第一金属层;或者,在所述第一基板上依此形成透明层、第六绝缘层、第一金属层,所述第一金属层形成与所述第六绝缘层上,其中所述透明层上包括对位标记。

38.结合第二方面,在一种可能的实现方式中,所述透明层通过激光镭射于所述第一基板上。

39.结合第二方面,在一种可能的实现方式中,所述透明层的材料为氧化铟锡ito。

40.结合第二方面,在一种可能的实现方式中,在所述第四绝缘层上形成垫料,所述垫料填充于所述过孔中。

41.结合第二方面,在一种可能的实现方式中所述半导体层为金属氧化物半导体层。

42.结合第二方面,在一种可能的实现方式中,所述半导体层的材料为氧化铟镓锌igzo。

43.第三方面,提供了一种液晶面板,包括如第一方面以及第一方面中任意一种可能的实现方式中的阵列基板和与所述阵列基板相对设置的彩膜基板。

44.结合第三方面,在一种可能的实现方式中,所述彩膜基板包括:第二基板;设置于所述第二基板上的黑色矩阵,其中所述黑色矩阵的正投影覆盖所述栅极线对应的区域。

45.第四方面,提供了一种显示装置,包括如第一方面以及第一方面中任意一种可能的实现方式中所述的阵列基板。

46.第五方面,提供一种显示装置,包括如第三方面中所述的液晶面板。

附图说明

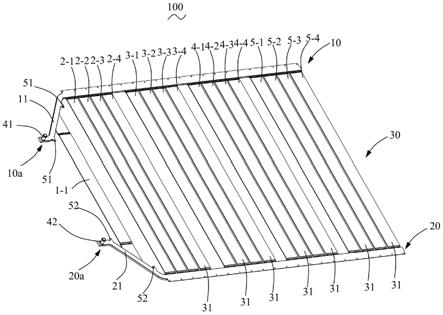

47.图1是一种液晶面板的示意性结构图;

48.图2是液晶面板的单个像素单元的示意性结构图;

49.图3是现有一种液晶面板的示意性剖面结构图;

50.图4是图3中的液晶面板产生拼接姆拉的示意性光路图;

51.图5是本技术实施例提供的一种液晶面板的示意性俯视图;

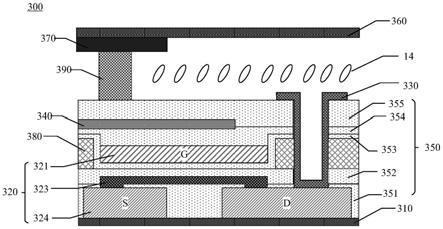

52.图6是本技术实施例提供的一种液晶面板的示意性剖面结构图;

53.图7是本技术实施例提供的液晶面板改善拼接姆拉的示意性光路图;

54.图8是本技术实施例提供的另一种液晶面板的示意性剖面结构图;

55.图9是本技术实施例提供的另一种液晶面板的示意性剖面结构图;

56.图10是本技术实施例提供的一种阵列基板的制备方法的示意性流程图。

57.附图标记:

58.1-显示模组;11-下偏光板;12-阵列基板;13-彩膜基板;14-液晶层;15-上偏光板;2-背光模组;121-行电极;122-列电极;123-像素电极;124-薄膜晶体管tft;210-第一基板;220-薄膜晶体管tft;221-栅极;222-栅极绝缘层;223-半导体层;224-源漏电极;230-第一透明导电层(像素电极);240-第二透明导电层(公共电极);250-钝化绝缘层;251-第二钝化绝缘层;252-第三钝化绝缘层;260-第二基板;270-黑色矩阵;280-色阻层;290-垫料;310-第一基板;320-薄膜晶体管tft;321-栅极;323-半导体层;324-源漏电极;330-第一透明导电层(像素电极);340-第二透明导电层(公共电极);350-绝缘层;351-第一绝缘层;352-第二绝缘层;353-第三绝缘层;354-第四绝缘层;355-第五绝缘层;356-第六绝缘层;360-第二基板;370-黑色矩阵;380-色阻层;390-垫料;400-第三透明层。

具体实施方式

59.下面将结合附图,对本技术中的技术方案进行描述。显然,所描述的实施例仅仅是本技术一部分实施例,而不是全部的实施例。

60.以下,术语“第一”、“第二”等仅用于描述目的,而不能理解为指示或暗示相对重要性或者隐含指明所指示的技术特征的数量。由此,限定有“第一”、“第二”等的特征可以明示或者隐含地包括一个或者更多个该特征。

61.此外,本技术中,“上”、“下”、“左”、“右”、“顶”、“底”、“横向”、“纵向”等方位术语是相对于附图中的部件示意放置的方位或位置来定义的,应当理解到,这些方向性术语是相对的概念,它们用于相对于的描述和澄清,而不是指示或暗示所指的装置或元器件必须具有的特定的方位、或以特定的方位构造和操作,其可以根据附图中部件所放置的方位的变化而相应地发生变化,因此不能理解为对本技术的限定。

62.还需说明的是,本技术实施例中以同一附图标记表示同一组成部分或同一零部件。

63.本技术实施例提供的技术方案应用于各种液晶驱动和显示模式的薄膜晶体管液晶显示器(thin film transistor liquid crystal display,tft-lcd),包括但不限于扭曲向列型(twisted nematic,tn)面板、垂直配向型(vertical alignment,va)面板、平面转换型(in-plane switching,ips)面板等。其中va面板可以包括多域垂直配向(multi-domain vertical alignment,mva)面板、图案垂直配向(patterned vertical alignment,pva)面板、连续焰火状排列模式(continuous pinwheel alignment,cpa)面板、紫外垂直配向(ultraviolet induced multi-domain vertical alignment,uvva)、聚合物垂直配向(polmer stabilized vertivally aligned,psva)、稳态的垂直配向(stabilized vertivally aligned,sva)。ips面板包括采用边缘场开关技术(fringe field switching,

ffs)的面板。

64.随着显示技术的发展,液晶显示器因具有高画质、省电、机身薄及应用范围广等优点,而被广泛应用于各类电子设备中,包括但不限于蜂窝电话(cellular phone)、智能手机(smart phone)、电视(television)、个人数字助理(personal digital assistant,pda)、数字相机、智能手表(smart watch)、智能手环(smart wristband)、平板型电脑、手提电脑、膝上型电脑(laptop computer)、笔记本电脑、台式计算机、计算器、车载设备以及其他消费性电子产品等,成为显示装置中的主流。薄膜晶体管液晶显示器(thin film transistor liquid crystal display,tft-lcd)是多数液晶显示器的一种,它使用薄膜晶体管技术改善影像品质,即屏幕上的每个像素点都是由集成于像素点后面的薄膜晶体管tft来驱动,可以实现各个像素点对点的独立控制。tft-lcd以大容量、高清晰度和高品质全真彩色受到人们的广泛青睐,本技术实施例将对tft-lcd进行详细介绍。

65.需要说明的是,为方便描述,本技术实施例的以下描述中,薄膜晶体管液晶显示器tft-lcd也可以简称为液晶显示器lcd,或者以下描述中的液晶显示器lcd可以理解为是薄膜晶体管液晶显示器tft-lcd。

66.液晶面板(panel)是液晶显示器的最重要部件,液晶面板质量、技术的好坏关系到液晶显示器整体性能的高低。液晶面板的工作原理是在两张玻璃基板之间填充液晶分子,通入电压后液晶分子排列状况发生变化,屏幕通过电子群的冲撞,制造画面并通过外部光线的透视反射来形成画面。

67.图1示出了一种液晶面板的示意性结构图。如图1所示,液晶面板100主要包括显示模组1和背光模组2,显示模组1用于显示图像,背光模组2用于为显示模组1提供光源。

68.显示模组1主要包括下偏光板11、阵列基板12、彩膜基板13、液晶层14和上偏光板15等。

69.阵列基板(array substrate)12上分布着许多横竖排列并且互相绝缘的格状金属膜导线,将阵列基板12分隔成许多微小的格子,称为像素单元(或称子像素)。

70.参考图2,图中示出了一个像素单元的示意性结构图。如2图所示,横向(也称x方向)布置的金属膜导线为行电极121,用于控制一行像素单元的打开和关闭,也即控制tft的开关。行电极121连接到栅极驱动器上,其上施加扫描电压。在一些实施例中行电极121也可以称为栅极扫描线(gate scan line)、栅极母线、扫描线(scan line)、选通线、扫描电极、x电极等。行电极121与各子像素内薄膜晶体管tft的栅极相连。如图2所示,纵向(也称y方向)布置的金属膜导线为列电极122,用于向液晶面板传输电压,该电压用于驱动液晶扭转的程度。列电极122连接到源极驱动器上,其上施加信号电压。在一些实施例中列电极122也可以称为数据线(data line)、信号线、信号电极、y电极等。列电极122与各子像素内薄膜晶体管tft的源极相连。行电极121列电极122行电极121和列电极122通常会被镀上一层不透光的金属(metal)镀层用于遮光,因此行电极121和列电极122上的光振幅透过率为0。

71.像素单元中有一片与周围导线绝缘的透明金属膜电极,为像素电极123,也称显示电极,用于与透明公共电极共同形成充电电极,对各子像素点内的液晶进行充电。在像素电极123的一角通过薄膜晶体管tft 124分别与行电极121、列电极122连接。薄膜晶体管tft 124可以主动地对屏幕上的各个独立的像素单元进行控制,是液晶显示器上每个像素单元点亮与关闭的开关。具体地,tft 124是一个三端开关管,其栅极(gate,g)连接至横向的行

电极121,源极(source,s)连接至纵向的列电极122,漏极(drain,d)连接至像素电极123。在栅极控制下,源极的数据线可以通过tft 124向漏极的像素实施充放电。例如,在栅极没有电压时,在源极与漏极之间不会有电流流过,此时tft处于截止状态,像素单元不能调整显示。在行电极121上施加足够的电压,会使得电性连接至该行电极121上的tft 124打开,从而列电极122上的信号电压能够写入像素,控制液晶的透光度,实现显示效果。

72.返回参考图1,阵列基板12上呈阵列式排布着像素单元,像素单元之间有互相绝缘的、相互垂直的行电极和列电极,行电极和列电极的交点处制备有薄膜晶体管tft,行电极、列电极和像素电极分别连接到tft的栅极、源极和漏极上。像素单元所在的行电极和列电极同时施加电信号时,该像素单元对应的tft导通,相当于该像素单元被选通。tft开和关的时间由行电极控制。

73.彩膜基板(color filter substrate)可简称为cf基板)13包括排列整齐的与像素单元(即子像素)对应的色阻单元。色阻单元具有多种颜色,可为像素单元提供色彩,从而实现液晶面板的彩色显示。在一些实施例中,不同颜色的色阻单元可以统称为色阻层、彩膜层或彩色滤光层。示例性的,彩膜基板13包括红色(red,r)色阻单元、绿色(green,g)色阻单元、蓝色(blue,b)色阻单元,其分别由红、绿、蓝三色的色阻材料制成,分别对应形成红色像素单元、绿色像素单元和蓝色像素单元。色阻单元可以利用滤光的方式产生rgb三原色,而r、g、b三原色各自拥有的不同的灰阶变化,将临近的三个rgb显示的像素单元当做一个显示的基本单位,即像素(pixel),这个像素可以将三原色以不同的强弱比例混合而呈现不同的色彩变化。换句话说,一个像素可以包括临近的r色阻单元对应的子像素、g色阻单元对应的子像素和b色阻单元对应的子像素。参考图1,为了遮住不透光的部分,相邻色阻单元之间可以通过黑色矩阵(black matrix,bm)遮住。具体地,黑色矩阵bm可以用于遮挡阵列基板12上的行电极、列电极等信号线的走线部分以及薄膜晶体管tft。因此色阻单元看起来并不是矩形,而是具有黑色缺角。在一些实施例中,彩膜基板13上的色阻单元排列方式可以为马赛克式、直条式、三角形式、四画素式等,本技术实施例不做限定。

74.液晶层14置于阵列基板12和彩膜基板13之间,用于改变光线偏光状态。液晶分子在电场作用下,其排列方向会发生变化,光线穿透液晶层14时的光学特性发生变化。因此利用液晶层的性质可以改变入射光的强度,以便形成灰阶,然后应用于显示器组件上。在一些实施例中,阵列基板12、彩膜基板13和液晶层14可以统称为液晶盒。

75.下偏光板11和上偏光板15分别置于液晶盒在出射光方向的两侧,即下偏光板11置于阵列基板12的远离液晶层14的一侧,上偏光板15置于彩膜基板13的远离液晶层14的一侧。或者说,阵列基板12位于下偏光板11和液晶层14之间,彩膜基板13位于上偏光板15与液晶层14之间。下偏光板11和上偏光板15用于形成偏振光。下偏光板11和上偏光板15具有一定角度,即下偏光板11和上偏光板15的偏光轴方向(或偏振方向)具有一定角度,该角度可根据液晶面板采用的显示技术不同而相应设计。可选地,下偏光板11和上偏光板15的偏光轴方向垂直,即其中一个偏光板为垂直偏光板,另一个为水平偏光板。如果两个偏光板之间不放置液晶层14的话,则入射到下偏光板11的光再入射到上偏光板15时,没有光线穿过上偏光板15而被人眼看到,液晶面板会显示黑色。若将液晶层14置于两个偏光板之间,当利用电场控制液晶转动时,可以改变光的行进方向,光可以从上偏光板15穿过。当施加不同的电场大小时,液晶分子的扭转形成不同,从上偏光板15穿过的光量不同,在液晶面板上就可以

形成不同的灰阶亮度了。应理解,本技术实施例中的“上”可以理解为是人在观看屏幕时靠近人眼的一侧,即出射光一侧;“下”可以理解为人在观看屏幕时远离人眼的一侧,即与出射光相背的方向。

76.由于液晶分子自身是无法发光的,因此液晶面板需要专门的发光源来提供光线,背光模组2起到的就是提供均匀、高亮度的光源的作用。背光模组2具体结构可参考现有技术,这里不再做详细介绍。

77.应理解,图1所示的液晶面板结构仅仅是示例性的,仅用于对tft-lcd液晶面板的基本结构和工作原理做简要介绍,不应理解为对本技术实施例的限定。

78.图3示出了现有一种液晶面板的示意性剖面结构图。图中示出的是液晶面板200在tft处的膜层堆叠示意图,这里只示意出显示模组的部分结构。如图3所示,液晶面板200包括阵列基板、彩膜基板和设置于阵列基板和彩膜基板之间的液晶层14。

79.阵列基板从下到上依序包括第一基板210、栅极221、栅极绝缘层222、半导体层223、源漏电极224、第二透明导电层240、钝化绝缘层250、像素电极230。

80.第一基板210位于阵列基板的最底层,用作形成其他膜层的支撑板。第一基板210可以为玻璃基板。

81.栅极221(gate,g)形成在第一基板210上,并与栅极扫描线相连接(图中未示出)。栅极绝缘层222(gate insulator,gi)形成在第一基板210上并覆盖栅极221,也可以说,栅极绝缘层222形成于栅极221上,覆盖栅极221并延伸至第一基板210上。半导体层223(本技术中也称有源层)形成在栅极绝缘层222上并位于栅极221上方。栅极绝缘层222位于栅极221与半导体层223之间,用于防止栅极221与半导体层223的导通,起到绝缘和防静电的作用。栅极221为导体。栅极绝缘层222为绝缘材质,例如可以采用氮化硅(sinx)等。半导体层223可以由非晶硅(a-si,as)制成。源漏电极(source/drain,s/d)224形成在栅极绝缘层222上。源漏电极224包括源极(source,s)和漏极(drain,d),其中源极s和漏极d彼此分隔并分别与半导体层223相接触,以使部分半导体层223从源极s和漏极d之间漏出。源极s与数据线(或称信号电极)连接,漏极d与像素电极(pixel electrode,pe)230连接,用于控制像素电极230的打开和闭合。

82.液晶面板200中,薄膜晶体管(thin film transistor,tft)220包括栅极221、栅极绝缘层222、半导体层223、源漏电极224。栅极221用于控制tft 220的导电程度。源极s和漏极d之间的半导体层223可以形成导电沟道。其中沟道的电阻越小,沟道的导电能力越强,电流越大,tft 220对像素电极230充放电。沟道的电阻越大,沟道的导电能力越弱,电流越小,tft 220不需要对像素电极230充放电。当栅极221上施加正电压时,栅压在栅极绝缘层222中产生电场,电力线由栅极221指向半导体层223表面,并在表面处产生感应电荷。当栅极221上施加的电压达到开启电压时,源极s和漏极d之间会有电压,源极s和漏极d之间会有载流子通过沟道。当源漏电压很小时,导电沟道近似为一恒定电阻,漏电流随着源漏电压增加而线性增大。当源漏电压很大时,源漏电压使得栅极绝缘层222中电场由源端到漏端逐渐减弱,沟道电阻随着源漏电压增大而增加,漏电流增加变得缓慢,对应线性区向饱和区过渡。当源漏电压增到一定程度,栅极221施加的电压在增加,但器件进入饱和区。因此,tft 220相当于一个可调电阻,利用tft 220的开态可以对像素电极230进行充电,利用tft 220的关态可以保持像素电极230的电压。

83.液晶面板200中,源漏电极224与栅极221位于半导体层223的两侧,其中,栅极221在半导体层223下侧,源漏电极224在半导体层223上侧,形成的是底栅结构(或称倒栅交错结构)tft。交错结构的tft可以连续积淀,倒栅还可以作遮光层(不需另设遮光层),挡住射向半导体层223的光线。这是因为a-si对光敏感,一旦有光流入引起漏电流增加,将会导致像质恶化。

84.第二透明导电层240在源漏电极224之上,并与源漏电极224之间通过绝缘层例如钝化绝缘层250相隔,第二透明导电层240与像素电极230通过绝缘层例如钝化绝缘层250相隔。第二透明导电层240为公共电极(a-com),可以提供透明的导电通路,与像素电极230之间形成电容,在通放电过程中控制液晶偏转,从而控制每个像素点是否透光。本技术实施例中,公共电极a-com为阵列基板电极电压,在大尺寸液晶面板中可用于抑制垂直串扰。

85.钝化绝缘层(passivition)250覆盖在第二透明导电层240、部分源漏电极224、部分栅极绝缘层222上。部分钝化绝缘层250形成于源漏电极224中间漏出的半导体层223上。具体地,钝化绝缘层250可以包括第一钝化绝缘层251和第二钝化绝缘层252。第一钝化绝缘层251位于第二透明导电层240与源漏电极224之间,并且第一钝化绝缘层251覆盖源漏电极224中间的半导体层223,并延伸至栅极绝缘层222上。第二透明导电层240形成于第一钝化绝缘层251上,第二钝化绝缘层252形成于第二透明导电层240之上,并延伸至第一钝化绝缘层251。钝化绝缘层250一般采用氮化硅(silicon nitride,iv)sinx)或二氧化硅(silica)sio2制成,主要起绝缘作用,保护薄膜晶体管、信号线和扫描线。

86.像素电极230形成于第二钝化绝缘层252之上,并部分位于漏极d上方。一般像素电极230可以通过过孔(via)与源漏电极224中的漏极d相接触,以实现导电。液晶面板200中,第一钝化绝缘层251和第二钝化绝缘层252上形成有过孔,用于像素电极230与源漏电极224中的漏极d相接触。像素电极230为透明的导电膜层,例如ito导电薄膜,本技术实施例中,将像素电极所在的膜层称为第一透明导电层。像素电极230与公共电极可以形成电容,在通放电过程中控制液晶偏转,从而控制每个像素点是否透光。

87.阵列基板上的各个膜层可以通过涂膜、光刻和显影等技术分别制备,例如对图3所示的阵列基板来说,在第一基板210上的膜层制备顺序依次为栅极221、栅极绝缘层222、半导体层223、源漏电极224、第一钝化绝缘层251、第二透明导电层240、第二钝化绝缘层252、像素电极230。

88.彩膜基板自上到下依序包括第二基板260、黑色矩阵270、色阻层280。

89.第二基板260位于彩膜基板的最外层,是彩色滤光片(即色阻层280)的载体。第二基板260可以为无碱的硼玻璃基板。

90.黑色矩阵270可以定义出像素和子像素的图案,其主要作用是区隔各种颜色色阻单元,并且能够增加对比度,作为遮光层可以避免杂色光的产生。色阻层280形成于第二基板260之上,并位于黑色矩阵270形成的图案(pattern)中。色阻层280具有滤光功能,一般具有耐热性佳、色彩饱和度高和穿透性好等特点。色阻层280的每个像素可以由红绿蓝三个子像素构成,三个子像素的排布方式有条形、品字形、马赛克型等。

91.阵列基板与彩膜基板之间设置有液晶层14,阵列基板上通过驱动器的电压改变,可以使液晶层14中的液晶分子排排站立或呈扭转状,形成光开关来选择背光模组中的光线穿透与否。这样就可以产生画面,液晶层14控制透光程度,色阻层280能够形成彩色。

92.为了使阵列基板和彩膜基板之间保持均匀的间隙(cell gap),阵列基板和彩膜基板之间还设置有垫料(spacer)290,用于防止液晶厚度不均造成显示模糊。垫料290可以使用间隙球(ball spacer,bs)或间隔柱(photo spacer,ps)。液晶面板200采用间隔柱ps,ps形成于彩膜基板侧的色阻层280上。

93.液晶面板200还可以包括比图示更多的零部件,例如封框胶、印刷电路板、触摸屏等,这里仅对液晶面板在tft处的堆叠结构做主要介绍。液晶面板200中有关膜层特性的一些介绍同样适用于本技术提供的方案。

94.在液晶面板的制备过程中,不论是阵列基板上的膜层,还是彩膜基板上的膜层,都可以用曝光显影技术制备。具体来说,即先利用物理气相沉积(physical vapor deposition,pvd)(例如溅射)、化学气相沉积(chemical vapor deposition,cvd)等方法涂膜。然后在曝光过程中,将光刻胶涂覆于膜层上,在涂好光刻胶的膜层表面覆盖掩模版(mask或photo mask),通过紫外光进行选择性照射,使受光照部分的光刻胶发生化学反应。在显影过程中,将感光部分(或非感光部分)的光刻胶溶除,留下来的胶膜显示的是所需要的形状。最后在光刻过程中,用适当的蚀刻液将没有光刻胶覆盖的膜层腐蚀掉,这样就得到了所需要的膜层图形。上述流程也可以称为光刻和腐蚀工艺(photolithography and etching process,pep)。

95.表1示出了液晶面板200的阵列基板和彩膜基板制备工艺路线示例。应理解,表中标识有pep的膜层是需要进行图形化处理的膜层,即在制备该膜层过程中需要使用掩模版。

96.表1

[0097][0098]

制备膜层图案过程中所用的掩模版也称光罩,一般情况下,一个光罩可以覆盖一个面板(panel),这样曝光一次就可以得到完整图案。随着显示技术的不断发展,面板业超大世代线(generation)体产能释放,例如出现了8.5代线(即g8.5,玻璃基板的尺寸为2200*

2500mm,其经济切割的最大屏幕尺寸为55英寸)、10代线(即g10,玻璃基板的尺寸为2880*3130mm,其经济切割的最大屏幕尺寸为70英寸)、10.5代线(即g10.5,玻璃基板的尺寸为2940*3370mm,其经济切割的最大屏幕尺寸为75英寸)等。随着高世代线的发展,玻璃基板的尺寸逐渐变大,可以切割的液晶面板的面积也越来越大,相应地,在制备液晶面板过程中使用的掩模版尺寸也随之增大。但曝光机对掩模版的尺寸有一定限制,并且大尺寸的掩模版也存在制造困难、成本高、存放不方便、应力变形大等问题。因此,在制造大尺寸的液晶面板时,很难实现整体曝光,通常分段曝光并重复进行。具体地,一般需要将大尺寸的玻璃基板划分成若干区域,并使用掩模版依次对各个区域进行曝光,最后拼合成大尺寸的液晶面板,这一过程称为光罩拼接工艺。以g8.5/g8.6/g10为例,理论上需要的最大单次曝光尺寸分别为55英寸/58英寸/75英寸,超出了掩模版的有效曝光区域,因此需要进行多次曝光(或需要多个光罩拼接覆盖整个面板),才能形成需要的膜层图案。但光罩拼接工艺相较小尺寸面板而言,在光罩拼接区域(即相邻光罩之间的重叠区域)会产生显示不均的问题,即拼接姆拉(mura)现象。

[0099]

mura是指显示器亮度不均匀,造成各种痕迹的现象。mura产生的主要原因是视觉上对于感受到的光源有不同的亮度而感觉到颜色的差异。拼接mura现象可以简单理解为光罩拼接区域内每个像素的亮度值与基准亮度(可以是面板中心位置的像素的亮度)的差值变化范围相对于非光罩拼接区域内的每个像素的亮度值与基准亮度的差值变化范围要大。下面结合附图简要介绍下现有液晶面板产生拼接mura的原因。

[0100]

图4示出了图3中的液晶面板产生拼接姆拉的示意性光路图。应理解,图4是将图3中的液晶面板进行膜层简化得到的,阵列基板侧只示意性示出了源漏电极s/d,彩膜基板侧示意性示出了黑色矩阵bm以及黑色矩阵所分隔的两个色阻单元cf-1和cf-2,其中相邻的色阻单元cf-1和色阻单元cf-2在制程过程中会产生一定程度的交接区域,即相邻色阻单元相接触的地方存在色层混合(如图中两个色阻单元之间的深色阴影部分)。

[0101]

图4中的(a)示出的是在理想状态下不产生拼接mura的示意图。在理想状态下,面板设计会根据制程线幅变异、层别对位精度偏差等,在黑色矩阵bm上预留较小的防止漏光和混色的宽度边距(margin)。因此如图所示,当外界光线以预设角度穿过色阻层并入射到源漏电极s/d上后,光线经源漏电极s/d反射后返回色阻层。理想状态下,被源漏电极s/d反射的光线都将被黑色矩阵bm遮挡,从黑色矩阵bm边缘出射的光线也是单色光。

[0102]

而实际生产制程中,线幅变异受地形影响加剧,层别对位精度也会因为多膜层叠加的组合公差而较差,这导致设计预留的边距(margin)远远不能覆盖(cover)制程变异。这种情况下,反射式拼接mura便会突显出来。图4中的(b)和(c)示出的是制程变异后产生拼接mura的示意图。如图4中的(b)所示,这里假设黑色矩阵bm和源漏电极s/d是对准的,相对图4中的(a)来说位置没有发生变化,只有彩膜(color filter,cf)制程发生变异。假设在光罩拼接区域,光罩拼接导致cf制程发生变异,色阻单元相对黑色矩阵发生偏移。这样,经源漏电极s/d反射后的光线将有部分光线穿过色层混合区域,再经过单色色阻单元后从彩膜基板上出射,会造成混色问题。如图4中的(c)所示,cf制程相比图4中的(b)变异更大,经源漏电极s/d反射后的光线中有部分光线直接穿过色层混合区域便从彩膜基板上出射,混色问题更为严重。对于阵列基板发生的制程变异,可能会产生穿透式拼接mura例如漏光问题,原理同上,在此不再做详细说明。

[0103]

目前可以通过以下几种方式来改善拼接mura。一种方式是将拼接区域的遮光层(例如黑色矩阵bm或遮光金属层)的宽幅增加,从而覆盖更大范围的穿透显示不均。例如图4中的(d)所示,可以将黑色矩阵bm的宽度增加,则可以将经源漏电极s/d反射后的光线遮挡住。但无论是增加黑色矩阵bm的宽幅还是增加金属镀层的宽幅,都会导致显示器穿透力下降(因为像素开口率减小),变相增加背光模组(backlight units,blu)的成本。并且拼接处因为遮光层与其他显示区域(即非拼接区域)遮光层的宽幅不同,lcd的穿透力不同,显示亮度存在差异。开口率(aperture ratio),等于每个像素可透光的有效区域除以像素的总面积。开口率越高,整体画面越亮。提高像素开口率可以提高面板透过率,降低背光模组的成本,还可以降低功耗、降低模块厚度。

[0104]

另外一种方式是将黑色矩阵设置于阵列基板(bm on array,boa)一侧,或者采用黑色支撑柱(black photo spacer,bps)来遮盖拼接区域,直接将来自背光模组的光吸收,可以同时避免穿透式和反射式的拼接mura。但这种实现方式技术难度大,在材料、膜层堆叠、器件可靠性方面均存在挑战。另外,将全部lcd膜层集成在阵列基板一侧,制备每个膜层时都要经过变异,应力变化和不同膜层之间对位精度变异相较常规方案偏大,在设计时需要预留更多的边距margin避免无法覆盖拼接mura,影响lcd穿透率。

[0105]

还有一种方式是通过马赛克光罩(mosaic mask)拼接方法,两块马赛克区域随机设置拼接像素,使之成为互补形式,通过两次曝光可以形成一个完整的图形。这种方式是将锐利的拼接线转变为模糊的拼接线,例如将拼接过渡区域分散到约40mm的区域内,可以欺骗人眼无法识别。但这种方式会导致单次曝光面积减少,部分区域无法以大区曝光进行,严重影响面板生产的生产节拍可用时间(takt time,tat),产生的产能损失较大。另外,相比直接拼接方式,马赛克拼接方法中的拼接宽度和拼接区域数量都明显增加。马赛克拼接为了保证自动光学检测(automated optical inspection,aoi)的检出效率,需要将拼接区域全部过滤,变相增加不良漏出和良率损失的风险。

[0106]

以上几种方式或者在一定程度上降低了液晶显示器的穿透率,或者额外带来了新的显示问题,例如色差、马赛克mura,可靠性问题等。因此,本技术实施例将提供一种阵列基板及其制备方法,能够在不损失穿透率(或开口率)设计的情况下,改善大尺寸lcd拼接导致的拼接显示不均问题。

[0107]

图5示出了本技术实施例提供的一种液晶面板的示意性俯视图。图中仅示例性示出了一个像素单元的俯视图,如图所示,色阻单元cf-1、cf-2、cf-3相邻,cf-2位于cf-1、和cf-3之间。tft位于像素单元的一角,将tft按照图中所示的a-a线剖开,可以得到如图6所示的液晶面板的示意性剖面结构图。

[0108]

如图6所示,本技术实施例提供的液晶面板300包括阵列基板、彩膜基板和设置于阵列基板和彩膜基板之间的液晶层。与图3所示的液晶面板200不同的是,本技术实施例中阵列基板为coa型阵列基板,即彩膜基板上的色阻层被制备于阵列基板上。因此本技术实施例中的彩膜基板仅用于表示液晶面板中除阵列基板外的另一个基板的位置关系,不限定彩膜基板一定包括色阻层。在一些实施例中,为便于理解,也可以将彩膜基板称为前基板,将阵列基板称为后基板。

[0109]

阵列基板自下而上依序包括第一基板310、源漏电极324、第一绝缘层351、半导体层323、第二绝缘层352、色阻层380、第三绝缘层353、栅极321、第四绝缘层354、第二透明导

电层340、像素电极330(即第一透明导电层)。

[0110]

第一基板310位于阵列基板的最底层,用作形成其他膜层的支撑板。第一基板310可以为玻璃基板。

[0111]

源漏电极324形成于第一基板310上,源漏电极324包括源极(source,s)和漏极(drain,d),其中源极s和漏极d彼此分隔。源漏电极324中的源极s与数据线(data line或称source line)相连,如图5中所示,图中纵向的数据线(data line)走线与源漏电极324可以使用同一个光罩,在一道工序中完成。

[0112]

第一绝缘层351形成于第一基板310之上并覆盖源漏电极324,也即第一绝缘层351形成于源漏电极324上并延伸至第一基板310上。第一绝缘层351可以为二氧化硅等有氧绝缘层,用于为半导体层323的驱动提供氧富集环境,从而稳定半导体层323以及tft器件的特性栅极321与半导体层323的导通,起到绝缘和防静电的作用。

[0113]

色阻层380形成于第二绝缘层352之上。本技术实施例中采用了coa技术,将色阻层380制备于阵列基板上。如图6所示,在tft堆叠处,色阻层380在与半导体层232对应的位置处设置有缺口(例如挖空),用来设置栅极321。如图5中所示的tft处,cf-2在该处设置有缺口。

[0114]

栅极321与半导体层323之间通过第三绝缘层353相隔。即,第三绝缘层353形成于色阻层380之上,覆盖色阻层380并延伸至色阻层380上的挖空区域,第三绝缘层353的部分覆盖色阻层380上漏出的第二绝缘层352之上。栅极321形成于第三绝缘层353之上并并位于半导体层323的上方。栅极321位于色阻层380的挖空区域,与色阻层380通过第三绝缘层353相隔。如图5中所示,tft位于数据线的上方,在tft堆叠处,栅极(参见图6中的栅极321)直接横向延伸形成栅极扫描线。即本技术实施例中tft中的栅极与扫描线为同一膜层,可以在同一道工序中制备,因此本技术实施例将扫描线和tft中的栅极称为第一栅极部分,如图5中横向所示的第一栅极(gate)部分301所示。在制备栅极321时,在数据线上方对应的位置形成第二部分栅极,如图5中所示的第二栅极部分302。第二栅极部分302位于数据线上方,色阻层位于数据线(即源漏电极)与第二栅极部分302之间。该第二栅极部分302为无源栅极,即第二栅极部分302不会与驱动器相连,不用于控制像素电极的开启关闭,仅代替黑色矩阵起到遮光作用。因此,本技术实施例中第二栅极部分302可以实现黑色矩阵的遮光作用,并且可以改善拼接姆拉现象,具体原理将在下文结合附图介绍,在此暂不详述。

[0115]

本技术实施例中,由于扫描线(即栅极线)与tft的栅极同时制备,因此在一些实施例中也将栅极线看做栅极的一部分,为横向的栅极(或x方向的栅极)。位于数据线上方的第二栅极部分,为纵向的栅极(或y方向的栅极)。同理,在一些实施例中也将数据线看成是源漏电极的一部分,为纵向的源漏电极(或y方向的源漏电极)。

[0116]

本技术实施例提供的液晶面板300中,薄膜晶体管(thin film transistor,tft)320包括栅极321、第三绝缘层353、第二绝缘层352、半导体层323、第一绝缘层351、源漏电极324。与液晶面板200类似,栅极321用于控制tft 320的导电程度,源极s和漏极d之间的半导体层323可以形成导电沟道。栅极321的材质可以采用金属铬(cr)、铬的合金材料或钼钽(mota)合金、铝(al)或者其他电性良好的导体。半导体层323材料为igzo,因此第一绝缘层351和第二绝缘层352分别位于半导体层323的上下两侧,以保护igzo。第一绝缘层351和第二绝缘层352的材质为有氧绝缘层,例如二氧化硅绝缘层。

[0117]

液晶面板300中,源漏电极324与栅极321位于半导体层323的两侧,其中,栅极321在半导体层323上侧,源漏电极324在半导体层323下侧,形成的是顶栅结构(topgate)(或称正栅交错结构)tft。顶栅结构tft中,源漏电极324位于半导体层323下方,由于源漏电极324中的源极s和漏极d之间由绝缘材料相隔,且相隔部分不遮光,也就是说来自背光模组的光源透过第一基板310后可以通过源极s和漏极d之间的不遮光部分入射到半导体层323上。本技术实施例半导体层323采用igzo材料,igzo对光不敏感,因此这种顶栅结构不会影响tft器件性能。

[0118]

第二透明导电层340位于栅极321之上,并与栅极321之间通过第四绝缘层354相隔。即第四绝缘层354形成于栅极321之上,覆盖栅极321并延伸至第三绝缘层353上。第二透明导电层340用于公共电极(a-com),可以提供透明的导电通路,与像素电极330之间形成电容,在通放电过程中控制液晶偏转,从而控制每个像素点是否透光。

[0119]

第二透明导电层340形成于第四绝缘层354上,第五绝缘层355形成于第二透明导电层340之上,覆盖第二透明导电层340并延伸至第四绝缘层354。第二透明导电层340可以为整面透明导电薄膜。本技术实施例中,第三绝缘层353、第四绝缘层354和第五绝缘层355一般采用氮化硅sinx或二氧化硅sio2制成,主要起绝缘作用,保护薄膜晶体管、信号线和扫描线。

[0120]

像素电极330形成于第五绝缘层355之上,并部分位于漏极d上方。液晶面板300中,在第五绝缘层355、第四绝缘层354、第三绝缘层353、色阻层380、第二绝缘层352和第一绝缘层351上的对应位置形成有过孔,用于像素电极330与源漏电极324中的漏极d相接触。本技术实施例中,第二透明导电层340与像素电极330通过第五绝缘层355相隔开,栅极321与像素电极330通过第三绝缘层353和第四绝缘层相隔开。色阻层380可以与像素电极330直接接触,可以不用以绝缘材料相隔离。如图5中所示,过孔位置即图6中所示的像素电极330与漏极d相接触的位置。cf-2在该位置处设置有缺口,即色阻层在该位置处挖空以用于像素电极与源漏电极过孔连接。

[0121]

像素电极330为透明的导电薄膜,在一些实施例中将像素电极330称为第一透明导电层。像素电极330一般采用金属氧化物制成,例如氧化铟锡(indium tin oxide,ito)、氧化铟锌(indium zinc oxide,izo)、氧化镉锡、氧化铝锡、氧化铟锌锡(indium tin zinc,itzo)、氧化锌(zinc oxide)、氧化铬(chromic oxide)、氧化铟镓锌(indium gallium zinc oxide,igzo)、氧化铟镓锌镁、氧化铟锌镁等。本技术实施例中,像素电极330可以为ito薄膜,像素电极330形状可以呈如图5中的条状。

[0122]

阵列基板上的各个膜层可以通过成膜、光刻和显影等技术分别制备,例如对图5所示的阵列基板来说,在第一基板310上的制备顺序依次为源漏电极324、第一绝缘层351、半导体层323、第二绝缘层352、色阻层380、第三绝缘层353、栅极321、第四绝缘层354、第二透明导电层340、第五绝缘层355、像素电极330。从第一基板310开始,不断经过成膜、曝光和刻蚀三个工序的循环,最终在第一基板310上得到所需要的tft阵列图形。

[0123]

彩膜基板自上而下依序包括第二基板360、黑色矩阵370。由于色阻层380制备于阵列基板一侧,因此在彩膜基板一侧,在第二基板320上制备黑色矩阵370即可。第二基板360可以为无碱的硼玻璃基板。可选地,黑色矩阵370上还可以设置保护层(over coat,oc)(图中未示出),用于隔离液晶与防止污染。

[0124]

阵列基板与彩膜基板之间设置有液晶层14,阵列基板上通过驱动器的电压改变,可以使液晶层14中的液晶分子排排站立或呈扭转状,形成光开关来选择背光模组中的光线穿透与否。这样就可以产生画面,液晶层14控制透光程度,色阻层380能够形成彩色。

[0125]

阵列基板和彩膜基板之间设置有垫料(spacer)390,用以维持阵列基板与彩膜基板之间的间隙高度。本技术实施例中垫料390采用间隔柱ps,将间隔柱ps制备在阵列基板一侧(ps on array,poa)。ps的可靠性会直接影响液晶显示器的可靠性。

[0126]

可选地,垫料390可以填充像素电极330上的过孔。由上述可知,像素电极330形成于第五绝缘层355上,源漏电极324与像素电极330之间的膜层均需开设过孔使像素电极330能够通过过孔与源漏电极324中的漏极相接触。当过孔较深时,在高温高湿可靠性等测试中,过孔电极容易腐蚀掉。另外,开设过孔的膜层(例如第一绝缘层351或第二绝缘层352)中可能含有氧化硅,其形成的过孔相较氮化硅膜层形成的过孔而言,形貌较差,可靠风险增加。因此,本技术实施例中将垫料390例如ps制备在阵列基板一侧,可以利用ps将过孔填充,起到防腐蚀的作用,提高了可靠性。

[0127]

可选地,垫料390的制备和填充过孔可以在一道制程中完成。

[0128]

可选地,液晶面板200中还可以包括更多的膜层,例如设置保护层、配向层等,本技术实施例不做限定。

[0129]

图3提供的液晶面板200中,色阻层制备于彩膜基板上,因此在成盒工艺过程中彩膜基板和阵列基板必须完全紧密贴合才能尽可能减少对准偏差。这不仅对彩膜基板与阵列基板的大小要求一致,而且彩膜基板上每个色阻单元位置和大小必须与阵列基板的每个像素单元精确对准。当上下两片基板分别加工完薄膜晶体管和彩色滤光层后,需要将两片基板上相应的像素位置对准后再封盒,对准工艺的准确性直接影响产品的质量。本技术实施例提供的阵列基板采用coa技术,薄膜晶体管和彩色滤光层都制备在同一片基板上,可以自对准,省却对准工艺,简化加工过程,提高产品质量。另外,彩色滤光层制备在薄膜晶体管上,简化了彩色滤光层的制作工艺,有效降低了成本。而且彩色滤光片集成技术可以将黑色矩阵bm的宽幅减少,因此可以增大开口率,提高透光率。更为重要的是,本技术实施例中采用的coa技术中,彩色滤光片设置于栅极和源漏电极之间,栅极可以起到遮光作用,并且由于栅极和彩色滤光层之间的距离缩短,可以有效将穿透光线和反射式光线遮挡住,还可以有效减少栅极和黑色矩阵的宽幅。这样可以在不损失开口率设计的情况下,有效改善拼接姆拉的问题。

[0130]

图7示出了本技术实施例提供的液晶面板改善拼接姆拉的示意性光路图。参考图5所示,在像素单元纵向上,色阻层位于源漏电极(即数据线)之上,栅极(即第二栅极部分302)位于色阻层之上,并位于数据线对应位置的上方。因此,色阻层位于源漏电极与栅极之间,在纵向的栅极(即第二栅极部分302)的作用相当于黑色矩阵,可以遮挡住穿透式和反射式光线。图7中的(b)示出了栅极、色阻层和源漏电极的位置关系简化示意图,本技术实施例中利用栅极遮挡光线,由于色阻层制备在阵列基板一侧,因此栅极和源漏电极之间的距离相比图7中的(a)所示的黑色矩阵与源漏电极之间的距离减少,这样以相同入射角度入射到源漏电极并被反射的光线可以被栅极遮挡。或者可以理解为,当bm与源漏电极之间的距离缩短时,原本从黑色矩阵bm边缘射出的光线将会被黑色矩阵中间的位置遮挡住,而有一部分黑色矩阵因为没有光线到达而不能起到遮挡光线的作用。这样在纵向上的第二栅极部分

和黑色矩阵可以设计较小一些的宽度,既不损失开口率,又能够解决或改善拼接mura的问题。另外,当用栅极作为遮挡层时,纵向上的栅极在各处的宽幅可以相同,即不需要在拼接区域加宽遮光层的宽幅。因此液晶面板开口设计在光罩拼接区域和非拼接区域一致,不会带来新的显示问题,例如马赛克拼接导致的马赛克mura,直接拼接导致的色差等。

[0131]

另一方面,参考图5所示,在tft堆叠处,tft的栅极与扫描线同层制备,形成横向的第一栅极部分301,彩膜基板上的黑色矩阵可以只保留横向第一栅极部分301对应的部分,用以遮挡光线。即在tft处通过彩膜基板上的黑色矩阵遮光,在信号线(数据线)处通过第二栅极部分遮光。

[0132]

图6所示的液晶面板300中,第二透明导电层340(即公共电极)位于第一透明导电层330(即像素电极)的下方,形成了中间电极(middle-com)架构。在一些实施例中,第二透明导电层340(即公共电极)也可以位于第一透明导电层330(即像素电极)的上方,并且二者通过绝缘层相隔。示例性的,参考图6对液晶面板300的结构进行调整,第一绝缘层351至第四绝缘层354之间的膜层的形成与图6中相同。不同之处在于,像素电极330形成于第四绝缘层354之上,并通过过孔与源漏电极324中的漏极d相接触。第五绝缘层355形成于第四绝缘层354之上,并覆盖像素电极330。第二透明导电层340则形成于第五绝缘层355之上。

[0133]

图6所示的液晶面板300中,第二透明导电层340(即公共电极)设置于阵列基板一侧。在一些实施例中,第二透明导电层340(即公共电极)也可以设置在彩膜基板一侧。示例性的,如图8所示,本技术实施例提供的液晶面板400中,第一绝缘层351至第四绝缘层354之间的膜层的形成与图6中相同。不同之处在于,像素电极330形成于第四绝缘层354之上,并通过过孔与源漏电极324中的漏极d相接触。第二透明导电层340形成于第二基板360上,并覆盖黑色矩阵370。第二透明导电层340作为液晶面板的公共电极,与阵列基板上的像素电极330构成正负极,以驱动液晶分子。也就是说,当第二透明导电层340设置于阵列基板一侧时,绝缘层350包括五层绝缘层,第一绝缘层351至第五绝缘层355。当第二透明导电层340设置于彩膜基板一侧时,绝缘层350包括四层绝缘层,相当于将图6所示第四绝缘层354与第五绝缘层355合并为一个绝缘层。

[0134]

图9示出了本技术实施例提供的另一种液晶面板的示意性剖面结构图。如图9所示,图9所示的液晶面板500与图6所示的液晶面板300类似,不同之处在于,液晶面板500中的tft 320与第一基板310之间增加了两个膜层,分别为第三透明层400和第六绝缘层356。其中,第三透明层400形成于第一基板310上,第六绝缘层356形成于第三透明层400之上,这样源漏电极324则形成于第六绝缘层356之上。另外第一绝缘层351至像素电极330的膜层位置与液晶面板300相同,具体可参考图6中相关描述,为简洁,不再赘述。

[0135]

可选地,液晶500中第二透明导电层340也可以设置于像素电极330上方,并且二者通过绝缘层相隔。不同之处在于,像素电极330形成于第四绝缘层354之上,并通过过孔与源漏电极324中的漏极d相接触。第五绝缘层355形成于第四绝缘层354之上,并覆盖像素电极330。第二透明导电层340则形成于第五绝缘层355之上。

[0136]

可选地,液晶500中第二透明导电层340也可以设置于彩膜基板一侧,具体参考图8所示,在此不再赘述。

[0137]

可选地,第六绝缘层356可以作为缓冲绝缘层。

[0138]

可选地,第三透明层400可以为透明的ito膜。该ito膜可以通过曝光或者激光镭射

工艺制备,其中ito激光镭射(laser on ito,loi)工艺指的是利用溅射、蒸发等多种方法在基片上镀上一层ito膜。

[0139]

本技术实施例中,第三透明层400上可以做对位标记(mark),对位标记用于制备膜层过程中对掩模版进行定位。由于loi工艺可以通过激光在第一基板310上定位,定位精度可以达到几个微米级,相比现有技术在金属上(例如数据线和扫描线)做对位标记而言,定位精度大大提高。本领域技术人员知道,玻璃面板的一个特性是越靠近面板中心,应力变化越小,越靠近边缘,应力变化越大。即膜层应力变化越靠近面板边缘越大。现有技术在金属上做定位标记时,需要对玻璃基板和掩模版做夹持定位,这样做出来的定位标记距离中心越远,对位标记应力变化越大。此后以对位标记为准的膜层图形在玻璃基板上的位置偏差更大,定位精度往往能达到几百微米甚至毫米级,导致实际值与设计值偏差较大。为了能够补偿偏差,栅极和黑色矩阵bm需要设计较大的宽幅,减低了像素开口率。本技术实施例中采用激光在第三透明层上进行定位,能够定位相距边缘更精确的位置。这样基于对位标记形成的图形距离边缘的位置更加精确,这样栅极和黑色矩阵bm可以设计较小的宽幅,间接地提升了开口率。

[0140]

示例性的,表2示出了图9所示的液晶面板500的阵列基板和彩膜基板制备工艺路线示例。应理解,表中标识有pep的膜层是需要进行图形化处理的膜层,即在制备该膜层过程中需要使用掩模版。

[0141]

表2

[0142]

[0143]

可选地,制备每个膜层时,可以根据膜层的材料等具体选择沉膜方式(例如pvd或者cvd)、曝光方式、蚀刻方式、光阻剥离以及补充制程(例如退火、激光镭射)等,在此不再详细举例。

[0144]

综上,本技术实施例提供一种阵列基板,该阵列基板包括:

[0145]

第一基板(例如上述第一基板310);设置于该第一基板上的栅极线(例如图5所示的第一栅极部分301)和数据线(例如图5所示的数据线);设置于该第一基板上的薄膜晶体管阵列层、色阻层(例如上述色阻层380)和第一透明导电层(例如上述像素电极330)。

[0146]

该薄膜晶体管阵列层包括源漏电极(例如上述源漏电极324)、半导体层(例如上述半导体层323)和栅极(例如上述栅极321),该源漏电极与该数据线同层,且该源漏电极与该数据线相连接,该栅极包括第一栅极部分(例如图5所示的第一栅极部分301)和第二栅极部分(例如图5所示的第二栅极部分302),该第一栅极部分与该栅极线同层,且该第一栅极部分与该栅极线相连接,该第二栅极部分与该数据线同向,且该第二栅极部分与该第一栅极部分断开。

[0147]

该半导体层位于该源漏电极与该栅极之间,该源漏电极位于该半导体层靠近该第一基板一侧。本技术实施例中,薄膜晶体管为顶栅结构。

[0148]

该色阻层位于该半导体层之上,该色阻层在与该栅极线对应的位置设置有挖空区(例如图5所示的第一栅极部分301对应的位置),该挖空区用于设置该第一栅极部分和该栅极线,该第二栅极部分位于该色阻层上与该数据线对应的位置。

[0149]

该色阻层上设置有过孔(例如图5所示的过孔位置),该第一透明导电层通过该过孔与该源漏电极相接触。

[0150]

本技术实施例提供的阵列基板中,将色阻层制备在阵列基板一侧,并采用顶栅结构的薄膜晶体管,其中色阻层位于栅极与源漏电极之间,可以利用栅极遮挡光线。栅极与源漏电极之间的距离相比现有技术中黑色矩阵与源漏电极之间的距离缩短,可以有效将穿透光线和反射式光线遮挡住。这样栅极和黑色矩阵可以设计的宽度较小一些,从而能够在不损失开口率的前提下,解决或改善拼接mura的问题。

[0151]

另外,本技术实施例采用coa技术,将色阻层直接制作在阵列基板上,不存在彩膜基板与阵列基板的对位问题,所以可以降低显示面板制备过程中对盒制程的难度,避免了制盒时的误差,因此黑色矩阵可以设计为窄线宽,可以提高像素的开口率。

[0152]

而且,当用栅极作为遮挡层时,与数据线同向的栅极在各处的宽幅可以相同,即不需要在拼接区域加宽遮光层的宽幅。因此液晶面板开口设计在光罩拼接区域和非拼接区域一致,不会带来新的显示问题,例如马赛克拼接导致的马赛克mura,直接拼接导致的色差等。可选地,该半导体层为金属氧化物半导体层。

[0153]

可选地,该半导体层的材料为氧化铟镓锌igzo。

[0154]

可选地,该阵列基板还包括:设置于该第一基板与该薄膜晶体管阵列层之间的透明层,该透明层包括对位标记。

[0155]

可选地,该透明层通过激光镭射于该第一基板上。

[0156]

可选地,该透明层的材料为氧化铟锡ito。

[0157]

可选地,该阵列基板还包括:设置于该色阻层之上的垫料,该垫料填充于该过孔中。

[0158]

可选地,该阵列基板还包括:与该第一透明导电层相绝缘的第二透明导电层,该第二透明导电层用于形成公共电极;其中,该第二透明导电层设置于该薄膜晶体管阵列层与该第一透明导电层之间;或者,该第二透明导电层设置于该第一透明导电层之上。

[0159]

可选地,该薄膜晶体管阵列层还包括:位于该半导体层两侧的第一绝缘层和第二绝缘层;其中,该半导体层与该源漏电极相接触,并通过该第一绝缘层相隔;该半导体层与该栅极通过该第二绝缘层相隔。

[0160]

可选地,该阵列基板还包括:位于该栅极两侧的第三绝缘层和第四绝缘层;其中,该栅极与该色阻层通过该第三绝缘层相隔;该栅极与该第一透明导电层通过该第四绝缘层相隔。

[0161]

本技术实施例中提供的阵列基板中,其具有的有益效果可参考图6至图8中的相关描述,为简洁,在此不再详细描述。

[0162]

图10示出了本技术实施例提供的一种阵列基板的制备方法的示意性流程图。如图10所示,该制备方法600包括步骤601至606。

[0163]

601,提供第一基板,在第一基板上依次形成第一金属层和第一绝缘层。

[0164]

该第一基板可以为玻璃基板。该第一基板为图6所示的第一基板310。

[0165]

该第一金属层经过图形化处理后包括薄膜晶体管的源漏电极,例如图6所示的源漏电极324。

[0166]

第一金属层可以直接在第一基板上制备,也可以间接在第一基板上制备,例如在位于第一基板上的膜层上制备。

[0167]

当第一金属层直接在第一基板上制备时,该第一绝缘层覆盖第一金属层(即薄膜晶体管的源漏电极和数据线)并延伸至第一基板。第一绝缘层进行图形化处理后源漏电极的部分漏出该第一绝缘层。该第一绝缘层可以为图6所示的第一绝缘层351。

[0168]

具体地,步骤601包括:在第一基板上形成第一金属层,对所述第一金属层进行图形化处理形成薄膜晶体管的源极和漏极,和与所述源漏电极相连接的数据线;在第一金属层上形成第一绝缘层,第一绝缘层覆盖源漏电极和数据线,并延伸至第一基板上,对第一绝缘层进行图形化处理使得源漏电极的部分漏出。

[0169]

602,在第一绝缘层上依次形成半导体层和第二绝缘层,该半导体层与第一金属层相接触。

[0170]

该半导体层可以为图6所示的半导体层323。该半导体层的材料为金属氧化物半导体,例如igzo氧化物。

[0171]

第二绝缘层可以为图6所示的第二绝缘层352。该第二绝缘层形成于半导体层并延伸至第一绝缘层。

[0172]

具体地,步骤602包括:在第一绝缘层上形成薄膜晶体管的半导体层,半导体层与源漏电极漏出的部分相接触;在半导体层上形成第二绝缘层,第二绝缘层覆盖半导体层并延伸至第一绝缘层上。

[0173]

603,在第二绝缘层上依次形成色阻层、第三绝缘层。

[0174]

该色阻层可以为图6所示的色阻层380。该色阻层上可以挖空以形成部分第二金属层。

[0175]

具体地,步骤603包括:在第二绝缘层上形成色阻层,对色阻层进行图形化处理,得

到色阻层在与栅极线对应的位置的挖空区;在色阻层上形成第三绝缘层。

[0176]

604,在第三绝缘层上依次形成第二金属层、第四绝缘层。

[0177]

在第二金属层上形成第四绝缘层,该第四绝缘层覆盖所述栅极,并延伸至所述第三绝缘层。

[0178]

具体地,步骤604包括:在第三绝缘层上形成第二金属层,对第二金属层进行图形化处理得到薄膜晶体管的栅极和与栅极相连接的栅极线,其中栅极包括第一栅极部分和第二栅极部分,第一栅极部分与栅极线同向,第二栅极部分与数据线同向,且第二栅极部分与第一栅极部分断开,第二栅极部分位于色阻层上与数据线对应的位置;在第二金属层上形成第四绝缘层,第四绝缘层覆盖栅极并延伸至第三绝缘层上。

[0179]

605,在第一绝缘层、第二绝缘层、色阻层、第三绝缘层、第四绝缘层上的对应位置开设过孔。

[0180]

该过孔使得第一金属层露出。

[0181]

606,在第四绝缘层上形成第一透明导电层,该第一透明导电层通过所述过孔与第一金属层相接触。

[0182]

该第一透明导电层可以为图6所示的像素电极330。

[0183]

具体地,步骤606包括,在第四绝缘层上形成第一透明导电层,对第一透明导电层进行图形化处理得到像素电极,像素电极通过所述过孔与源漏电极相接触。

[0184]

可选地,方法600还包括:在第四绝缘层上形成垫料。该垫料可以为图6所示的垫料390,例如间隔柱ps。

[0185]

可选地,该垫料填充于步骤606后第一透明导电层覆盖后的过孔中。

[0186]

可选地,当第一金属层间接设置于第一基板上时,步骤601可以替换为:在第一基板上依此形成透明层、第六绝缘层、第一金属层、第一绝缘层。透明层形成于第一基板上,第六绝缘层形成于透明层上,第一金属层形成于第六绝缘层上,其中透明层上包括对位标记。

[0187]

可选地,当公共电极设置于阵列基板一侧时,在步骤605之前,还包括:在第四绝缘层上形成第二透明导电层,在第二透明导电层上形成第五绝缘层,第五绝缘层覆盖第二透明导电层并延伸至第四透明导电层上。相应地,步骤605替换为:在第一绝缘层、第二绝缘层、色阻层、第三绝缘层、第四绝缘层、第五绝缘层上的对应位置开设过孔。步骤606替换为:在第五绝缘层上形成第一透明导电层,该第一透明导电层通过所述过孔与第一金属层相接触。

[0188]

可选地,公共电极也可以设置于第一透明导电层之上,并通过绝缘层相隔。

[0189]

可选地,所述透明层通过激光镭射于所述第一基板上。

[0190]

可选地,所述透明层的材料为氧化铟锡ito。

[0191]

可选地,方法600还包括:在所述第四绝缘层上形成垫料,所述垫料填充于所述过孔中。

[0192]

可选地,所述半导体层为金属氧化物半导体层。

[0193]

可选地,所述半导体层的材料为氧化铟镓锌igzo。

[0194]

本技术实施例提供的阵列基板制备方法中采用coa技术,将色阻层直接制作在阵列基板上,以栅极作为遮光层,可以有效改善拼接姆拉问题。并且可以降低显示面板制备过程中对盒制程的难度,黑色矩阵可以设计为窄线宽,可以提高像素的开口率。

[0195]

另外,本技术实施例中垫料例如ps制备在阵列基板一侧,能够将像素电极的过孔填充,避免在对液晶面板进行测试过程中腐蚀电极,提高了可靠性。

[0196]

本技术实施例提供一种loi coa 顶栅tft结构,通过源漏电极s/d与栅极夹层coa的模式,同时解决穿透式和反射式拼接mura。

[0197]

在本技术的描述中,需要说明的是,除非另有明确的规定和限定,术语“安装”“相连”“连接”应做广义理解,例如可以是固定连接,也可以是可拆卸连接,或一体式连接;可以是机械连接,也可以是电连接;可以是直接连接,也可以是通过中间媒介间接相连,可以是两个元件内部的连通。对于本领域的普通技术人员而言,可以具体情况理解上述术语在本技术中具体含义。

[0198]

以上所述,仅为本技术的具体实施方式,但本技术的保护范围并不局限于此,任何熟悉本技术领域的技术人员在本技术揭露的技术范围内,可轻易想到变化或替换,都应涵盖在本技术的保护范围之内。因此,本技术的保护范围应所述以权利要求的保护范围为准。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。