1.本发明涉及半导体装置的制造方法及电力控制电路的制造方法。

背景技术:

2.在专利文献1中公开了对内置进行通电的pn结二极管的半导体元件进行pn结二极管的通电试验的试验装置及通电试验的试验条件,该半导体元件为使用了sic的金属氧化物半导体场效应晶体管(mosfet)等。

3.在对使用了sic的mosfet进行了正向通电的情况下,堆垛缺陷扩大而产生接通电压上升的双极劣化。为了对该双极劣化进行抑制,通过在基板之上形成缓冲层,在缓冲层之上形成漂移层,从而使得双极电流没有到达基板所包含的堆垛缺陷。

4.在非专利文献1中公开了将缓冲层所包含的堆垛缺陷的密度设定得比基板所包含的堆垛缺陷的密度显著地小。

5.但是,在市场上为了对产生双极劣化进行抑制,希望通过通电试验来确定缓冲层包含堆垛缺陷的半导体元件而对该半导体元件流出到市场进行抑制。但是,根据电流密度、最大结温等半导体元件的使用条件,通电试验的必要充分条件产生变化。但是,为了在半导体元件的寿命中保证缓冲层所包含的堆垛缺陷不生长,有时需要进行高温、长时间或高电流密度的通电试验。

6.而且,在专利文献2中公开了为了提高通电试验的电流密度,使用层叠金属箔而逐个芯片地进行通电试验。

7.专利文献1:日本专利第6104363号公报

8.专利文献2:日本专利第6289287号公报

9.非专利文献1:hironori itoh et.al.,"high reliable 4h

‑

sic epitaxial wafer with bpd free recombination

‑

enhanced buffer layer for high current applications",icscrm,2019

10.在如专利文献1公开的那样进行了通电试验的情况下,为了在进行通电试验后将半导体元件组装于半导体装置,必须对半导体元件所具有的电极产生劣化进行抑制。因此,必须将进行通电试验时的试验温度限制为小于或等于230℃。通过提高试验温度能够将进行通电试验时的通电时间缩短,但由于用于进行了通电试验后的工序的限制而使试验温度受到限制,因此在实际实施通电试验时,必须使通电时间是以分钟为单位的。而且,在对流动具有大的电流密度的电流的半导体元件进行通电试验的情况下,必须严格设置通电试验的条件。因此,必须延长通电时间。另外,根据半导体元件所具有的电极的规格及安装方法,必须在更低的温度下进行筛选试验。因此,必须延长通电时间。另外,由于逐个芯片地进行通电试验,因此进行通电试验的试验装置的数量增多。另外,由于进行半导体元件其本身的通电试验,因此必须使用精密的输送半导体元件的输送系统、用于进行通电试验的探针夹具等。因此,试验装置的成本上升。这些问题使半导体装置的生产率降低。

11.在如专利文献2所公开的那样使用层叠金属箔而逐个芯片地进行了通电试验的情

况下,在每次进行通电时必须更换层叠金属箔。因此,层叠金属箔的间接部件成本增加。另外,进行通电试验的试验装置的运转率降低。这些问题使半导体装置的成本上升。

12.还想到对具有被模块化的多个半导体元件的半导体装置进行通电试验。但是,在对该半导体装置进行了通电试验的情况下,与对没有被模块化的半导体元件的单体进行通电试验的情况相比,包含堆垛缺陷的概率上升,不良率上升。另外,进行通电试验的试验装置大型化。另外,由于半导体元件之外的周边部件的耐热温度,进行通电试验时的试验温度受到限制。另外,在进行通电试验时由半导体元件发出的热量滞留在半导体装置的内部,半导体装置的内部温度变高。而且,在该多个半导体元件被电并联连接的情况下,由于在该多个半导体元件分别内置的多个pn结二极管的正向特性的差异的影响,试验电流偏聚于具有低正向特性的特定的半导体元件而流动,在该特定的半导体元件流动过剩电流。这些问题使半导体装置的生产率降低。

技术实现要素:

13.本发明就是鉴于这些问题而提出的。

14.本发明的目的在于,在对半导体装置进行pn结二极管的通电试验的情况下,提高半导体装置的生产率,使半导体装置的成本降低,对进行通电试验时的通电用半导体元件的温度上升进行抑制。

15.在半导体装置的制造方法中,分别内置多个pn结二极管的多个通电用半导体元件的背面与导体板的第1主面连接。另外,导体片连接于多个通电用半导体元件的表面。之后,在导体板的第2主面在具有多个通电用半导体元件、导体板及导体片的半导体装置的半成品的底面露出的状态下进行多个pn结二极管的通电试验。

16.发明的效果

17.根据本发明,多个pn结二极管的通电试验是在被配备于半导体装置的半成品处的状态下进行的。因此,能够同时进行多个通电用半导体元件的筛选试验。由此,能够提高半导体装置的生产率。

18.另外,根据本发明,能够将通电试验所使用的试验探针抵接于导体片。因此,能够对由于试验探针而损伤通电用半导体元件的表面电极这一情况进行抑制。另外,能够在之后的装配工序中将导体片用作电极接合用金属膜。由此,不需要用于对通电用半导体元件的表面电极进行保护的金属箔等缓冲材料,能够使半导体装置的成本降低。

19.另外,根据本发明,在进行通电试验时由通电用半导体元件发出的热量被导体板吸收,从在半成品的底面露出的导体板的第2主面有效地释放到试验工作台等。由此,能够对进行通电试验时的通电用半导体元件的温度上升进行抑制。

20.通过下面的详细的说明和附图,本发明的目的、特征、方案及优点会变得更加明了。

附图说明

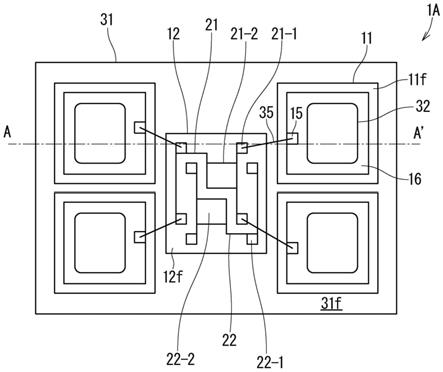

21.图1是示意性地图示通过实施方式1的半导体装置的制造方法制造的半导体装置的第1半成品的俯视图。

22.图2是示意性地图示通过实施方式1的半导体装置的制造方法制造的半导体装置

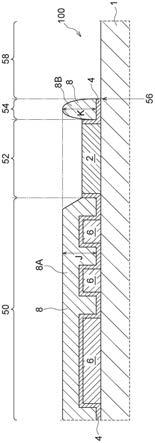

的第1半成品的剖视图。

23.图3是示意性地图示通过实施方式1的半导体装置的制造方法制造的半导体装置的第2半成品的俯视图。

24.图4是示意性地图示通过实施方式1的半导体装置的制造方法制造的半导体装置的俯视图。

25.图5是示意性地图示通过实施方式1的半导体装置的制造方法制造的半导体装置的剖视图。

26.图6是表示实施方式1的半导体装置的制造方法及电力控制电路的制造方法的流程图。

27.图7是示意性地图示通过实施方式2的半导体装置的制造方法制造的半导体装置的第1半成品的俯视图。

28.图8是表示实施方式2的半导体装置的制造方法及电力控制电路的制造方法的流程图。

29.图9是示意性地图示通过实施方式3的半导体装置的制造方法制造的半导体装置的第1半成品的俯视图。

30.图10是示意性地图示通过实施方式3的半导体装置的制造方法制造的半导体装置的第2半成品的俯视图。

31.图11是表示实施方式3的半导体装置的制造方法及电力控制电路的制造方法的流程图。

具体实施方式

32.1实施方式1

33.1.1半导体装置的制造方法

34.图1及图2分别是示意性地图示通过实施方式1的半导体装置的制造方法制造的半导体装置的第1半成品的俯视图及剖视图。图3是示意性地图示通过实施方式1的半导体装置的制造方法制造的半导体装置的第2半成品的俯视图。图4及图5分别是示意性地图示通过实施方式1的半导体装置的制造方法制造的半导体装置的俯视图及剖视图。图2及图5分别图示出图1及图4所描绘的剖断线a

‑

a’位置处的剖面。

35.图6是表示实施方式1的半导体装置的制造方法及电力控制电路的制造方法的流程图。

36.实施方式1的半导体装置的制造方法具有图6所图示的工序s1至s12。

37.通过图4及图5所图示的实施方式1的半导体装置的制造方法制造的半导体装置1为电力用半导体装置,是使用了sic的金属氧化物半导体场效应晶体管(mosfet)。半导体装置1也可以是使用了sic的mosfet之外的半导体装置。

38.在工序s1中,如图1及图2所图示的那样,在多个通电用半导体元件11所包含的大于或等于两个通电用半导体元件11的表面11f之上分别形成大于或等于两个栅极电极15。在实施方式1中,大于或等于两个通电用半导体元件11是多个通电用半导体元件11的全部。多个通电用半导体元件11分别内置多个pn结二极管。对多个pn结二极管进行通电。

39.在工序s2中,如图1及图2所图示的那样,在多个通电用半导体元件11所包含的大

于或等于两个通电用半导体元件11的表面11f之上分别形成大于或等于两个源极电极16。在实施方式1中,该大于或等于两个通电用半导体元件11是多个通电用半导体元件11的全部。

40.工序s1及s2可以同时执行,也可以不同时执行。工序s1及s2的执行顺序是任意的。

41.在工序s3中,如图1及图2所图示的那样,将多个通电用半导体元件11的背面11b连接于导体板31的第1主面31f。在实施方式1中,导体板31的第1主面31f为导体板31的表面。在实施方式1中,通过烧结接合将多个通电用半导体元件11的背面11b连接于导体板31的第1主面31f。由此,多个通电用半导体元件11的背面11b与导体板31的第1主面31f进行电及热连接。

42.在工序s4中,如图1及图2所图示的那样,将导体片32连接于多个通电用半导体元件11的表面11f。在实施方式1中,导体片32是与多个通电用半导体元件11的表面11f分别连接的多个导体片。在实施方式1中,多个导体片32彼此独立。在实施方式1中,通过烧结接合将导体片32连接于多个通电用半导体元件11的表面11f。由此,导体片32与多个通电用半导体元件11的表面11f进行电及热连接。在实施方式1中,多个导体片32所包含的大于或等于两个导体片32分别经由大于或等于两个源极电极16与大于或等于两个通电用半导体元件11的表面11f连接。

43.在工序s5中,如图1及图2所图示的那样,将中继基板12连接于导体板31的第1主面31f。在实施方式1中,通过烧结接合将中继基板12连接于导体板31的第1主面31f。由此,中继基板12与导体板31的第1主面31f进行热连接。在实施方式1中,中继基板12为一个中继基板。中继基板12也可以是多个中继基板。中继基板12具有栅极电路图案21及源极电路图案22。栅极电路图案21及源极电路图案22具有导电性。栅极电路图案21及源极电路图案22配置于中继基板12的表面12f侧。栅极电路图案21具有大于或等于两个第1栅极焊盘21

‑

1及第2栅极焊盘21

‑

2。在实施方式1中,第2栅极焊盘21

‑

2为一个第2栅极焊盘。第2栅极焊盘21

‑

2也可以是多个第2栅极焊盘。第2栅极焊盘21

‑

2主要用于在对图1及图2所图示的半导体装置1的第1半成品1a进行通电试验时将信号输入至半导体装置1的第1半成品1a,以及用于在将半导体装置1组装于具有大的电路结构的半导体装置的情况下从半导体装置1取出信号电位。源极电路图案22具有大于或等于两个第1源极焊盘22

‑

1及第2源极焊盘22

‑

2。在实施方式1中,第2源极焊盘22

‑

2为一个第2源极焊盘。第2源极焊盘22

‑

2也可以是多个第2源极焊盘。

44.在工序s3、s4及s5中进行的烧结接合所使用的烧结接合材料是由ag、cu等构成的材料。烧结接合经过加压接合工艺或无加压接合工艺而进行。烧结接合也称为烧结连接。

45.工序s3、s4及s5可以同时执行,也可以不同时执行。工序s3、s4及s5的执行顺序是任意的。

46.在工序s6中,如图1及图2所图示的那样,大于或等于两个栅极电极15经由栅极电路图案21彼此电连接。由此,对大于或等于两个栅极电极赋予共通的栅极电位。在实施方式1中,大于或等于两个栅极电极通过大于或等于两个导电导线35分别与大于或等于两个第1栅极焊盘21

‑

1电连接,由此大于或等于两个栅极电极15经由栅极电路图案21彼此电连接。

47.通过工序s1至s6,得到图1及图2所图示的具有多个通电用半导体元件11、中继基板12、大于或等于两个栅极电极15、大于或等于两个源极电极16、导体板31、导体片32及大

于或等于两个导电导线35的半导体装置1的第1半成品1a。导体板31的第2主面31b在半导体装置1的第1半成品1a的底面1ab露出。在实施方式1中,导体板31的第2主面31b为导体板31的背面。

48.在工序s7中,在导体板31的第2主面31b在半导体装置1的第1半成品1a的底面1ab露出的状态下,对半导体装置1的第1半成品1a进行多个通电用半导体元件11所具有的多个pn结二极管的通电试验。此外,在对半导体模块进行通电试验的情况下,绝缘材料附着于导体板31的第2主面31b。

49.在进行通电试验时,导体板31的第2主面31b设置于通电工作台之上。由此,向多个通电用半导体元件11赋予共通的漏极电位。另外,能够从多个通电用半导体元件11经由导体板31及通电工作台而释放由多个通电用半导体元件11发出的热量。另外,能够使得用于将进行通电试验时的多个通电用半导体元件11的试验温度设得高的热量经由通电工作台及导体板31而流入到多个通电用半导体元件11。

50.另外,在进行通电试验时,对第2栅极焊盘21

‑

2进行电探测。由此,对大于或等于两个通电用半导体元件11赋予共通的栅极电位。另外,对大于或等于两个导体片32进行电探测。由此,对大于或等于两个通电用半导体元件11赋予彼此独立的源极电位。对大于或等于两个通电用半导体元件11赋予彼此独立的源极电位的原因在于,如上所述,与大于或等于两个源极电极16分别连接的大于或等于两个导体片32彼此独立,对大于或等于两个源极电极16赋予彼此独立的源极电位。另外,向在各通电用半导体元件11形成的栅极电极15及源极电极16之间施加成为负偏置的电压。成为负偏置的电压是赋予给源极电极16的源极电位比赋予给栅极电极15的栅极电位高的电压。由此,能够可靠地断开mosfet即各通电用半导体元件11的沟道。由此,能够使在进行各通电用半导体元件11的通电试验时流过各通电用半导体元件11的试验电流的大部分为在内置于各通电用半导体元件11的pn结二极管流动的双极电流。由此,能够将各通电用半导体元件11的筛选试验的条件设为恰当的条件。

51.另外,在进行通电试验时,在对各通电用半导体元件11赋予了上述漏极电位、栅极电位及源极电位的状态下,从在各通电用半导体元件11形成的源极电极16向在各通电用半导体元件11形成的栅极电极15进行通电。由此,进行在多个通电用半导体元件11分别内置的多个pn结二极管的通电试验。

52.另外,在进行通电试验时,例如,通过对各通电用半导体元件11供给试验电流的恒流源而对在各通电用半导体元件11流动的试验电流的电流值进行调整,将试验电流的电流密度控制为所希望的电流密度。另外,对通电工作台的温度进行调整,将各通电用半导体元件11的试验温度控制为所希望的试验温度。由于在进行通电试验时各通电用半导体元件11发热,因此通电工作台的温度被设定得比各通电用半导体元件11的所希望的试验温度低。各通电用半导体元件11的发热量依赖于在各通电用半导体元件11内置的pn结二极管的正向损耗及试验电流的电流值。试验温度例如通过将发热量乘以通电工作台和各通电用半导体元件11的最大温度部之间的热阻而得到的值加上通电工作台的温度来进行预测。通电工作台的温度例如被设定为200℃。在进行通电试验时,在对内置于各通电用半导体元件11的pn结二极管设定的时间范围进行通电。

53.另外,在进行通电试验时,对进行通电试验前后的pn结二极管的正向特性进行比较而验证双极劣化度。此时,在进行通电试验前后的pn结二极管的正向特性的变动量落在

规格外的情况下,内置有pn结二极管的各通电用半导体元件11被排除在出厂对象之外。

54.在工序s8中,如图3所图示的那样,大于或等于两个源极电极16经由源极电路图案22彼此电连接。由此,对大于或等于两个源极电极16赋予共通的源极电位。在实施方式1中,大于或等于两个源极电极16通过大于或等于两个导电导线36分别与大于或等于两个第1源极焊盘22

‑

1电连接,由此大于或等于两个源极电极16经由源极电路图案22彼此电连接。

55.在工序s9中,如图3所图示的那样,大于或等于两个栅极电极15经由栅极电路图案21彼此重新电连接。在实施方式1中,大于或等于两个栅极电极15通过新的大于或等于两个导电导线37分别与大于或等于两个第1栅极焊盘21

‑

1重新电连接,由此大于或等于两个栅极电极15经由栅极电路图案21彼此重新电连接。由此,即使在进行通电试验前形成的导电导线35的长期可靠性及导电性能在进行通电试验时降低的情况下,也能够通过导电导线37确保长期可靠性及导电性能。在进行通电试验前形成的导电导线35的长期可靠性及导电性能在进行通电试验时降低的原因在于,导电导线35与栅极电极15及栅极电路图案21之间的接合界面暴露于高温,在该接合界面处金属间化合物生长而使导电导线35的连接强度降低。

56.工序s8及s9可以同时执行,也可以不同时执行。工序s8及s9的执行顺序是任意的。

57.通过工序s1至s9,得到图3所图示的具有多个通电用半导体元件11、中继基板12、大于或等于两个栅极电极15、大于或等于两个源极电极16、导体板31、导体片32、导电导线35、导电导线36及导电导线37的半导体装置1的第2半成品1b。

58.在工序s10中,如图4及图5所图示的那样,多个间隔导体(spacer conductor)33连接于栅极电路图案21及源极电路图案22。在实施方式1中,多个间隔导体33包含与第2栅极焊盘21

‑

2连接的间隔导体及与第2源极焊盘22

‑

2连接的间隔导体。多个间隔导体33优选具有与导体片32的厚度相同程度的厚度。

59.工序s10可以在工序s8及s9前执行,也可以在工序s8及s9后执行。工序s10也可以在执行工序s7前执行。

60.在工序s11中,如图4及图5所图示的那样,形成树脂封装材料41。树脂封装材料41将多个通电用半导体元件11、中继基板12、导体板31的至少一部分、导体片32的至少一部分、及多个间隔导体33的至少一部分覆盖。

61.在工序s12中,如图4及图5所图示的那样,对树脂封装材料41的至少一部分、导体片32的至少一部分及多个间隔导体33的至少一部分进行研磨而使导体片32的一个面及多个间隔导体33的一个面在树脂封装材料41的研磨面露出。也可以对导体板31的一部分进行研磨。

62.在实施方式1的半导体装置的制造方法中,在执行了工序s1至s6后执行工序s7。另外,在执行了s7后执行工序s8至s12。

63.通过工序s1至s12,得到图4及图5所图示的具有多个通电用半导体元件11、中继基板12、大于或等于两个栅极电极15、大于或等于两个源极电极16、导体板31、导体片32、多个间隔导体33、导电导线35、导电导线36、导电导线37及树脂封装材料41的半导体装置1。对半导体装置1进行高温反向偏置(htrb)试验、通断试验等将与半导体装置1的耐压相当的电压施加于半导体装置1的试验。

64.1.2电力控制电路的制造方法

65.实施方式1的电力控制电路的制造方法具有图6所图示的工序s1至s13。

66.在对电力控制电路进行制造的情况下,通过具有工序s1至s12的实施方式1的半导体装置的制造方法对多个半导体装置1进行制造。

67.在工序s13中,对具有制造出的多个半导体装置1的电力控制电路进行制造。制造的电力控制电路构成具有比各半导体装置1的电路结构大的电路结构的半导体装置。

68.在半导体装置1的等价电路具有单相的mosfet的情况下,通过将2个半导体装置1搭载于带有电路图案的绝缘基板之上,从而能够对由半桥电路构成的半导体装置进行制造。另外,通过将6个半导体装置1搭载于带有电路图案的绝缘基板之上,从而能够对由全桥电路构成的半导体装置进行制造。另外,通过对半桥电路、全桥电路等进行组合,能够对由升压电路等构成的半导体装置进行制造。在将半导体装置1搭载于带有电路图案的绝缘基板之上后,将信号电极、主电流电极等接合于半导体装置1。也可以通过封装材料覆盖半导体装置1及带有电路图案的绝缘基板。对由电力控制电路构成的半导体装置进行出厂检查。在出厂检查中,能够缩短进行筛选试验的筛选试验时间,能够省略筛选试验其本身。原因在于,在制造出半导体装置1的时间点已经进行了筛选试验。

69.1.3实施方式1的效果

70.根据实施方式1,并非是针对单体的通电用半导体元件11,而是针对具有多个通电用半导体元件11的半导体装置1的第1半成品1a进行多个pn结二极管的通电试验。由此,在多个pn结二极管被配备于半导体装置1的第1半成品1a的状态下进行多个pn结二极管的通电试验。由此,能够同时进行多个通电用半导体元件11的筛选试验。由此,能够提高半导体装置1的生产率。

71.另外,根据实施方式1,并非是针对由电力控制电路构成的半导体装置,而是针对具有多个通电用半导体元件11的半导体装置1的第1半成品1a进行多个pn结二极管的通电试验。由此,能够对同时进行通电试验的通电用半导体元件11的数量进行抑制。由此,能够对通电试验中的成品率的降低进行抑制。例如,在半导体装置1的等价电路具有单相的mosfet,对由半桥电路构成的半导体装置进行制造的情况下,能够将同时进行通电试验的通电用半导体元件11的数量设为1/2。在半导体装置1的等价电路具有单相的mosfet,对由全桥电路构成的半导体装置进行制造的情况下,能够将同时进行通电试验的通电用半导体元件11的数量设为1/6。另外,在半导体装置1的等价电路具有单相的mosfet的情况下,不需要对半导体装置1的背面1b赋予绝缘性。因此,半导体装置1的搬运变得容易。另外,能够将进行通电试验的通电装置小型化。

72.另外,根据实施方式1,导体片32连接于通电用半导体元件11的表面11f。由此,能够使通电试验所使用的试验探针与导体片32接触。因此,能够对由于试验探针而使通电用半导体元件11的表面电极损伤这一情况进行抑制。另外,能够在之后的装配工序中将导体片32用作电极接合用金属膜。由此,不需要专门用于对通电用半导体元件11的表面电极进行保护的金属箔等缓冲材料,能够使半导体装置1的成本降低。另外,能够不考虑通电用半导体元件11的表面电极损伤这一情况地对试验探针进行选定。由此,能够选定具有管脚的试验探针,该管脚简易且具有高通电能力。另外,根据实施方式1,导体片32连接于通电用半导体元件11的源极电极16。由此,能够使用具有大的剖面面积且仅具有小的面方向的电阻成分的电极而进行通电。由此,即使在探测位置少的情况下,也能够在通电用半导体元件11

均匀地流动电流。另外,当在探测位置产生接触电阻,在进行通电时通过接触电阻产生了热量的情况下,产生的热量也会在导体片32的内部扩散直至产生的热量传递至通电用半导体元件11。由此,能够对在通电用半导体元件11产生热点这一情况进行抑制。

73.另外,根据实施方式1,在进行通电试验时由通电用半导体元件11发出的热量被导体板31吸收,从在半导体装置1的第1半成品1a的底面1ab露出的导体板31的第2主面31b有效地释放到试验工作台等。由此,能够对进行通电试验时的通电用半导体元件11的温度上升进行抑制。

74.另外,根据实施方式1,对在大于或等于两个通电用半导体元件11的表面11f分别形成的大于或等于两个栅极电极15赋予共通的栅极电位。由此,能够减少用于对栅极偏置进行控制的探测位置的数量。由此,能够容易地对通电试验的条件进行控制。由此,能够缩小通电用半导体元件11的焊盘尺寸,能够缩小通电用半导体元件11的无效区域。其结果,能够增加从各晶片的通电用半导体元件11的获取数量。

75.在进行通电试验时,在对大于或等于两个通电用半导体元件11赋予共通的栅极电位,对大于或等于两个通电用半导体元件11赋予共通的源极电位,对大于或等于两个通电用半导体元件11赋予共通的漏极电位的情况下,无法在进行通电试验时对在大于或等于两个通电用半导体元件11流动的试验电流进行独立的控制。而且,试验电流的比率大致为大于或等于两个通电用半导体元件11分别具有的多个pn结二极管的正向电压的倒数的比率。因此,产生与大于或等于两个通电用半导体元件11的特性的波动对应的试验电流的波动。因此,无法使试验电流均匀化。因此,在特定的通电用半导体元件11流动过剩的电流。因此,通电试验中的成品率降低。

76.相对于此,如实施方式1所示,在进行通电试验时,在对大于或等于两个通电用半导体元件11赋予共通的栅极电位,对大于或等于两个通电用半导体元件11赋予彼此独立的源极电位,对大于或等于两个通电用半导体元件11赋予共通的漏极电位的情况下,能够在进行通电试验时对在大于或等于两个通电用半导体元件11流动的试验电流进行独立的控制。另外,能够使试验电流均匀化。例如,通过从与大于或等于两个通电用半导体元件11的数量相同的数量的大于或等于两个的恒流源分别供给在大于或等于两个通电用半导体元件11流动的试验电流,从而能够在进行通电试验时对试验电流进行独立的控制,能够使试验电流均匀化。因此,在大于或等于两个通电用半导体元件11的特性存在差异的情况下,也能够使试验电流均匀化。因此,通电试验中的成品率上升。

77.在无法对流过大于或等于两个通电用半导体元件11的试验电流进行独立的控制的情况下,试验电流的波动通常比实际使用时在大于或等于两个通电用半导体元件11流动的电流的波动大。因此,由无法使试验电流均匀化导致的通电试验中的成品率的降低是过剩的。对该点进行说明。

78.在进行通电试验时在各通电用半导体元件11流动的试验电流主要由直流成分构成。因此,试验电流的电流值主要依赖于各通电用半导体元件11的阻抗的正向的电阻成分。相对于此,在实际使用时在各通电用半导体元件11流动的电流包含直流成分及交流成分。原因在于,该电流的电流值大多随时间变化。因此,该电流的电流值不仅依赖于阻抗的电阻成分,还依赖于阻抗的电感成分。因此,相对而言,该电流的电流值难以受到各通电用半导体元件11的正向电压特性的影响。特别地,在使用同步整流方式仅在死区时间期间中的极

短时间对内置的pn结二极管进行通电的半导体装置中,由于在实际使用时在各通电用半导体元件流动的电流所包含的直流成分小,因此该电流的电流值不易受到各通电用半导体元件11的正向电压特性的影响。因此,试验电流的波动通常比在实际使用时在大于或等于两个通电用半导体元件11流动的电流的波动大。

79.另外,根据实施方式1,在进行了通电试验后,对大于或等于两个通电用半导体元件11赋予共通的栅极电位,对大于或等于两个通电用半导体元件11赋予共通的源极电位,对大于或等于两个通电用半导体元件11赋予共通的漏极电位。这是因为,进行了通电试验后不需要对在大于或等于两个通电用半导体元件11流动的试验电流进行独立的控制。由此,能够将大于或等于两个通电用半导体元件11作为单一的通电用发电元件进行控制。

80.另外,根据实施方式1,通过烧结接合将多个通电用半导体元件11的背面11b连接于导体板31的第1主面31f。另外,通过烧结接合将导体片32连接于多个通电用半导体元件11的表面11f。另外,通过烧结接合将中继基板12连接于导体板31的第1主面31f。由此,即使在为了缩短进行通电试验的试验时间而在进行通电试验时将半导体装置1的第1半成品1a暴露于高温的情况下,也能够对接合界面的劣化进行抑制。由此,能够对具有高可靠性的半导体装置1进行制造。

81.另外,根据实施方式1,在进行了通电试验后,将大于或等于两个栅极电极15重新连接于栅极电路图案21。由此,即使在为了缩短进行通电试验的试验时间而在进行通电试验时将半导体装置1的第1半成品1a暴露于高温,导电导线35的长期可靠性及导电性能在进行通电试验时降低的情况下,也能够对具有高可靠性的半导体装置1进行制造。

82.另外,根据实施方式1,在进行了通电试验后,形成树脂封装材料41。由此,即使在为了缩短进行通电试验的试验时间而在进行通电试验时将半导体装置1的第1半成品1a暴露于高温的情况下,也能够防止树脂封装材料41产生劣化,能够对树脂封装材料41的重量减少进行抑制。此外,在进行了通电试验后形成树脂封装材料41的情况下,在进行通电试验时不存在树脂封装材料41。但是,由于在进行pn结二极管的通电试验时没有施加高电压,因此在不存在树脂封装材料41的情况下,在通电用半导体元件11也不产生沿面放电。因此,能够将进行通电试验时的通电用半导体元件11的试验温度设定为适于缩短进行通电试验的试验时间的试验温度。

83.另外,根据实施方式1,在进行了通电试验后,对导体片32的至少一部分进行研磨。由此,除去在进行通电试验时形成于导体片32的至少一部分的表面处的氧化膜。由此,能够恢复导体片32的至少一部分的通电性能、与焊料等连接材料的接合性。

84.另外,在实施方式1中,在执行工序s7前执行工序s10的情况下,通过在进行了通电试验后对多个间隔导体33的至少一部分进行研磨而使多个间隔导体33的一个面在树脂封装材料41的研磨面露出,从而能够恢复多个间隔导体33的至少一部分的通电性能、与焊料等连接材料的接合性。

85.另外,根据实施方式1,在制造出半导体装置1的时间点已经进行了筛选试验。由此,能够缩短由电力控制电路构成的半导体装置的出厂检查所需要的时间。另外,能够提高出厂检查的成品率。由于进行出厂检查的检查装置大多是大型且高成本的,因此能够缩短出厂检查所需要的时间会产生经济效益。另外,具有大的电路结构的半导体装置由多个部件构成,该半导体装置被判定为不合格品的情况下的损耗成本大。因此,能够提高出厂检查

的成品率这一点有助于减小损耗成本。

86.2实施方式2

87.图7是示意性地图示通过实施方式2的半导体装置的制造方法制造的半导体装置的第1半成品的俯视图。

88.图8是表示实施方式2的半导体装置的制造方法及电力控制电路的制造方法的流程图。

89.实施方式2的半导体装置的制造方法及电力控制电路的制造方法主要在下述点上与实施方式1的半导体装置的制造方法及电力控制电路的制造方法不同。关于未在下面叙述的点,与在实施方式1的半导体装置的制造方法及电力控制电路的制造方法中采用的结构相同的结构也被用于实施方式2的半导体装置的制造方法及电力控制电路的制造方法。

90.实施方式2的半导体装置的制造方法具有图8所图示的工序s1至s12、s21及s22。

91.在工序s21中,如图7所图示的那样,将温度检测用元件13搭载于多个通电用半导体元件11所包含的通电用半导体元件11之上。温度检测用元件13由温度检测用二极管等构成。在温度检测用元件13由温度检测用二极管构成的情况下,温度检测用二极管的阳极焊盘43及阴极焊盘44通过导电导线38及导电导线39而分别与中继基板12所具有的第1阳极焊盘23

‑

1及第1阴极焊盘24

‑

1电连接。第1阳极焊盘23

‑

1及第1阴极焊盘24

‑

1经由中继基板12所具有的阳极电路图案23及阴极电路图案24而分别与中继基板12所具有的第2阳极焊盘23

‑

2及第2阴极焊盘24

‑

2连接。由此,通过对第2阳极焊盘23

‑

2及第2阴极焊盘24

‑

2进行电探测,能够取得温度检测用二极管的电位。例如,在温度检测用二极管流动温度确认用的小电流,通过读取温度检测用二极管的正向电压,能够对进行通电试验时的通电用半导体元件11的温度进行测定。在实施方式2中,在一个通电用半导体元件11之上搭载温度检测用元件13。由此,与在大于或等于两个通电用半导体元件11之上搭载有温度检测用元件13的情况相比,能够将半导体装置1小型化。例如,也可以是将搭载有温度检测用元件13的通电用半导体元件11及没有搭载温度检测用元件13的通电用半导体元件11电并联连接而构成半导体装置1。由此,能够使通电用半导体元件11的制造成本降低。

92.在工序s7中,优选的是,通过向将发热量乘以通电用半导体元件11和温度检测用元件13之间的热阻而得到的值加上由温度检测用元件13检测到的温度,从而与实施方式1相比能够准确地对通电用半导体元件11的温度进行预测。原因在于,由于通电用半导体元件11和温度检测用元件13之间的热阻比通电工作台和各通电用半导体元件11的最大温度部之间的热阻小,因此预测的误差小。

93.在工序s22中,温度检测用二极管的阳极焊盘43及阴极焊盘44通过新的导电导线与中继基板12所具有的第1阳极焊盘23

‑

1及第1阴极焊盘24

‑

1重新电连接。由此,即使在进行通电试验前形成的导电导线38及导电导线39的长期可靠性及导电性能在进行通电试验时降低的情况下,也能够通过新的导电导线确保长期可靠性及导电性能。

94.工序s22可以与工序s8及s9同时进行,也可以不与工序s8及s9同时进行。

95.在执行了工序s7后执行工序s22。

96.3实施方式3

97.图9是示意性地图示通过实施方式3的半导体装置的制造方法制造的半导体装置的第1半成品的俯视图。图10是示意性地图示通过实施方式3的半导体装置的制造方法制造

的半导体装置的第2半成品的俯视图。

98.图11是表示实施方式3的半导体装置的制造方法及电力控制电路的制造方法的流程图。

99.实施方式3的半导体装置的制造方法及电力控制电路的制造方法主要在下述点上与实施方式1的半导体装置的制造方法及电力控制电路的制造方法不同。关于未在下面叙述的点,与在实施方式1的半导体装置的制造方法及电力控制电路的制造方法中采用的结构相同的结构也被用于实施方式3的半导体装置的制造方法及电力控制电路的制造方法。

100.实施方式3的半导体装置的制造方法具有图11所图示的工序s1至s7、s9至s13及s31。

101.在工序s5中,在与导体板31的第1主面31f连接的中继基板12处,如图9所图示的那样,第2源极焊盘22

‑

2是被分割开的大于或等于两个第2源极焊盘。大于或等于两个第2源极焊盘22

‑

2分别与大于或等于两个第1源极焊盘22

‑

1电连接。因此,源极电路图案22具有彼此电气独立的大于或等于两个图案。

102.另外,在工序s5中,在与导体板31的第1主面31f连接的中继基板12处,在第2栅极焊盘21

‑

2及大于或等于两个第2源极焊盘22

‑

2的表面设置接合膜。接合膜是能够进行焊料接合、烧结接合等接合的膜。作为接合膜能够使用将nip膜、pd膜及au膜以记载的顺序层叠后的镀膜等。

103.在工序s31中,如图9所图示的那样,大于或等于两个源极电极16分别与源极电路图案22所具有的大于或等于两个图案电连接。在实施方式3中,大于或等于两个源极电极16通过大于或等于两个导电导线36分别与大于或等于两个第1源极焊盘22

‑

1电连接,由此大于或等于两个源极电极16分别与大于或等于两个图案电连接。在图9所图示的第1半成品1a中,由于大于或等于两个图案彼此电气独立,因此在大于或等于两个源极电极16分别与大于或等于两个图案电连接的情况下,也能够对大于或等于两个源极电极16赋予彼此独立的源极电位。在执行工序s7前执行工序s31。

104.在工序s10中被与源极电路图案22连接的间隔导体33将源极电路图案22所具有的大于或等于两个图案彼此电连接。由此,对大于或等于两个源极电极16赋予共通的源极电位。在实施方式3中,通过将与源极电路图案22连接的间隔导体33连接于横跨大于或等于两个第2源极焊盘22

‑

2的间隔导体33的连接区域,从而源极电路图案22所具有的大于或等于两个图案彼此电连接,多个通电用半导体元件11电并联连接。在执行了工序s7后执行工序s10。

105.在工序s10中被连接于第2栅极焊盘21

‑

2的间隔导体33与设置于第2栅极焊盘21

‑

2的表面处的接合膜接合。另外,与大于或等于两个第2源极焊盘22

‑

2连接的间隔导体33与设置于大于或等于两个第2源极焊盘22

‑

2的表面处的接合膜接合。

106.也可以在工序s1中形成的栅极电极15及在工序s2中形成的源极电极16的表面设置具有上述镀膜的接合膜。当在栅极电极15的表面设置该接合膜的情况下,在工序s6中,将导电导线35与设置于栅极电极15的表面处的接合膜接合。另外,在工序s31中,将导电导线36与设置于源极电极16的表面处的接合膜接合。

107.根据实施方式3,即使在大于或等于两个源极电极16与源极电路图案22电连接的情况下,也会对大于或等于两个通电用半导体元件11赋予彼此独立的源极电位。因此,能够

对在进行通电试验时在大于或等于两个通电用半导体元件11流动的试验电流进行独立的控制。另外,能够使试验电流均匀化。因此,在大于或等于两个通电用半导体元件11的特性存在差异的情况下,也能够使试验电流均匀化。因此,通电试验中的成品率上升。

108.另外,根据实施方式3,不需要在进行了通电试验后通过大于或等于两个导电导线36将大于或等于两个源极电极16分别与大于或等于两个第1源极焊盘22

‑

1电连接。因此,能够提高半导体装置1的生产率。

109.另外,在实施方式3中,当在源极电极16的表面设置具有上述镀膜的接合膜的情况下,能够对由于在工序s7中进行的通电试验中的温度上升而使接合膜的表面氧化这一情况、及由于该加热而使下层的膜所包含的ni涌到au膜之上这一情况进行抑制。由此,在进行了通电试验后将导体片32连接于源极电极16的情况下,也能够对导体片32的连接不良进行抑制。因此,也能够在工序s7后执行工序s4。

110.另外,当由在实施方式3中在工序s7中进行的通电试验中的温度上升导致的热应力被抑制为不会引起导电导线36和第1源极焊盘22

‑

1的接合界面劣化的程度的情况下,不需要在进行了通电试验后通过大于或等于两个导电导线36将大于或等于两个源极电极16分别与大于或等于两个第1源极焊盘22

‑

1重新电连接。另外,在该热应力被抑制为不会引起导电导线35和第1栅极焊盘21

‑

1的接合界面劣化的程度的情况下,经由栅极电路图案21将大于或等于两个栅极电极15彼此重新电连接的工序s9也能够同样地省略。

111.此外,可以将各实施方式自由地组合,对各实施方式适当进行变形、省略。

112.虽然对本发明进行了详细的说明,但上述说明在全部的方面都只是例示,并不是限定性的内容。应当理解为,能够设想到未例示的无数的变形例。

113.标号的说明

114.1半导体装置,1a第1半成品,1b第2半成品,11通电用半导体元件,12中继基板,13温度检测用元件,15栅极电极,16源极电极,21栅极电路图案,22源极电路图案,31导体板,32导体片。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。