1.本发明的实施例涉及半导体封装件。

背景技术:

2.扇出型衬底上芯片(focos)封装结构中,扇出重分布层/线路层(rdl)与微凸块/微焊盘周围的底胶一般使用有机介电材料作为填充材料(underfill),受限于目前的材料性质,这些材料在高温进入橡胶态后对线路层的保护力减弱,其周边结构产生的应力就有可能会破坏线路层。

技术实现要素:

3.针对相关技术中存在的问题,本发明的目的在于提供半导体封装件,以提升半导体封装件的性能。

4.本技术的实施例提供一种半导体封装件,包括:并排设置的第一芯片和第二芯片;接垫,位于第一芯片的邻近第二芯片的一侧的下表面上;迹线,电连接至接垫,在俯视图中,第一芯片的第一中心与接垫定义第一连线,第一连线与接垫的周边的相交处定义较靠近第一中心的第一交界区及较远离第一中心的第二交界区,迹线与第二交界区不重叠。

5.在一些实施例中,第二交界区中的点与接垫的第二中心的第二连线与经过接垫的第二中心的第一连线的夹角不超过正负30度。

6.在一些实施例中,第二交界区相比于第一交界区更靠近所述第二芯片位于接垫的远离第一芯片的第一中心的外侧部。

7.在一些实施例中,接垫直接连接通孔,通孔与迹线电连接,在俯视图中,通孔位于接垫的投影范围内。

8.在一些实施例中,在俯视图中,第一芯片具有将第一芯片分为上部和下部的中心水平线,与上部和下部中的接垫电连接的迹线从通孔朝靠近中心水平线延伸。

9.在一些实施例中,在俯视图中,迹线从通孔垂直于中心水平线延伸。

10.在一些实施例中,在俯视图中,迹线从通孔沿垂直于第一连线的方向延伸。

11.在一些实施例中,还包括:焊盘,将迹线连接至通孔。

12.在一些实施例中,在俯视图中,接垫的直径大于焊盘的直径大于通孔的直径。

13.在一些实施例中,在俯视图中,接垫的第二中心与通孔的第三中心以及焊盘的第四中心重叠。

14.本技术的实施例还提供一种半导体封装件,包括:并排设置的第一芯片和第二芯片;接垫,位于第一芯片的邻近第二芯片的一侧的下表面上;迹线,位于迹线的端部处的焊盘电连接至接垫,在俯视图中,第一芯片的第一中心与接垫定义第一连线,第一连线与接垫的周边的相交处定义较靠近第一中心的第一交界区及较远离第一中心的第二交界区,焊盘与第二交界区重叠。

15.在一些实施例中,焊盘的在与第二交界区重叠的位置处的宽度大于接垫的直径的

以及其衍生性的用词(例如“水平地”、“向下地”、“向上地”等等)应该解释成引用在讨论中所描述或在附图中所描示的方向。这些相对性的用词仅用于描述上的方便,且并不要求将本技术以特定的方向建构或操作。

28.另外,有时在本文中以范围格式呈现量、比率和其它数值。应理解,此类范围格式是用于便利及简洁起见,且应灵活地理解,不仅包含明确地指定为范围限制的数值,而且包含涵盖于所述范围内的所有个别数值或子范围,如同明确地指定每一数值及子范围一般。

29.再者,为便于描述,“第一”、“第二”、“第三”等等可在本文中用于区分一个图或一系列图的不同组件。“第一”、“第二”、“第三”等等不意欲描述对应组件。

30.扇出型衬底上芯片(focos)封装结构的异质整合为目前着重研发的三维(3d)堆叠结构技术,目的在于为多个紧密相连的芯片(例如,芯片和芯片之间的间距<300μm)提供高速传输的互连(例如,扇出线路层互连),其中扇出线路层内极其细小的线路易因较大的翘曲或局部较大的应力造成迹线破裂的问题。

31.下面参照附图,对本技术的半导体封装件作具体阐述。

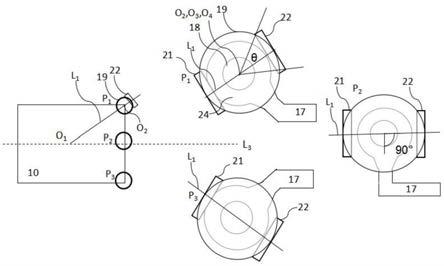

32.模拟得知,线路层被破坏的原因在于,靠近芯片【例如,特定应用集成电路(asic)芯片、高带宽存储器(high bandwidth memory,hbm)芯片】的边界的凸块/接垫对下方线路层的迹线造成的应力过大,如图1,其中,由于第一芯片10与第二芯片12之间的填充材料14刚性较低,造成线路层16易往上翘曲(如箭头a所示),线路层16承受较大应力(如箭头c所示)的区域为由第一芯片10中心向外放射状延伸且靠近第二芯片12的通孔18/接垫19投影区下交界处,因此迹线17在此处若无法承受应力将导致破裂b。在实施例中,通孔18为微凸块,通孔18和接垫19通过焊料15互连。在实施例中,线路层16包括迹线17以及包覆迹线17的聚合物层20。在实施例中,线路层16中迹线17的线宽/间距小于3μm/3μm,线路层16的厚度小于5μm。

33.本技术的实施例提供一种半导体封装件,包括:并排设置的第一芯片10和第二芯片12;接垫19,位于第一芯片10的邻近第二芯片12的一侧的下表面上;迹线17,电连接至接垫19。

34.参见图2,示出了第一芯片10和分别位于p1、p2、p3三个位置处的接垫19。图2的右侧示出了位于的接垫19的放大图。在俯视图中,第一芯片10的第一中心o1与接垫19定义第一连线l1,进一步而言,第一芯片10的第一中心o1与接垫19的第二中心o2定义第一连线l1,第一连线l1与接垫19的周边的相交处定义较靠近第一中心o1的第一交界区21和较远离第一中心o1的第二交界区22,迹线17与第二交界区22不重叠。

35.在一些实施例中,第二交界区22中的点与接垫19的第二中心的第二连线与经过第二中心o2的第一连线l1的夹角θ不超过正负30度。在一些实施例中,第二交界区22位于接垫19的远离第一芯片10的第一中心o1的外侧部。在一些实施例中,接垫19连接通孔18,通孔18与迹线17电连接,在俯视图中,通孔18位于接垫19的投影范围内。在一些实施例中,在俯视图中,第一芯片10具有将第一芯片分为上部和下部的中心水平线l3,与上部和下部中的接垫19电连接的迹线17从通孔18朝靠近中心水平线l3延伸。在一些实施例中,在俯视图中,如p2位置处的接垫19,迹线17从通孔18垂直于中心水平线l3延伸。在一些实施例中,还包括:焊盘24,将迹线17连接至通孔18。在一些实施例中,在俯视图中,接垫19的直径大于焊盘24的直径大于通孔18的直径。在一些实施例中,在俯视图中,接垫19的第二中心o2与通孔的第三

中心o3以及焊盘24的第四中心o4重叠。第二交界区22相比于第一交界区21更靠近第二芯片12。

36.本技术的实施例还提供一种半导体封装件,包括:并排设置的第一芯片10和第二芯片12;接垫19,位于第一芯片10的邻近第二芯片12的一侧的下表面上;迹线17,位于迹线17的端部处的焊盘24电连接至接垫19,在俯视图中,第一芯片19的第一中心o1与接垫19定义第一连线l1,进一步而言,第一芯片10的第一中心o1与接垫19的第二中心o2定义第一连线l1,第一连线l1与接垫17的周边的相交处定义较靠近第一中心o1的第一交界区21和较远离第一中心o1的第二交界区22,焊盘24与第二交界区22重叠。

37.如图3所示,图3示出了图2中位于p2位置处的接垫19,在一些实施例中,焊盘22的在与第二交界区22重叠的位置处的宽度大于接垫19的直径的一半。在一些实施例中,在俯视图中,通孔18的第三中心o3以及焊盘24的第四中心o4与接垫19的第二中心o2不重叠,通孔的第三中心o3以及焊盘24的第四中心o4位于第二中心o2与第二交界区22之间。在一些实施例中,在俯视图中,焊盘24的周边与第二交界区22重叠。在一些实施例中,在俯视图中,接垫19、通孔18和焊盘24为圆形。

38.在一些实施例中,如图4所示,在俯视图中,接垫19在第一连线的延伸方向上具有第一最大宽度w1,接垫19在垂直于第一连线的方向上具有第二最大宽度w2,第一最大宽度w1小于第二最大宽度w2。也就是说,接垫19为椭圆形,其长轴垂直于经过第二中心o2的第一连线l1。在一些实施例中,在俯视图中,焊盘的周边与第二交界区22重叠。

39.在一些实施例中,如图5所示,在俯视图中,接垫24在靠近第二交界区22的一侧的宽度变宽,直至接垫24可以覆盖整个第二交界区22。

40.本技术的实施例的扇出线路层的迹线绕过第二交界区,或者由宽度更大的焊盘与第二交界区重叠(使接垫内缩;加宽焊盘宽度;使焊盘中心相对于接垫中心偏移)以增强扇出线路层的结构强度,使得在焊盘/迹线的单位面积上承受的应力减小,进而减低扇出线路层失效的风险,可解决多芯片同/异质整合产品中扇出线路层失效与可靠度良率问题。

41.以上所述仅为本发明的优选实施例而已,并不用于限制本发明,对于本领域的技术人员来说,本发明可以有各种更改和变化。凡在本发明的精神和原则之内,所作的任何修改、等同替换、改进等,均应包含在本发明的保护范围之内。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。