1.本发明涉及半导体制造技术领域,特别涉及一种半导体器件的形成方法。

背景技术:

2.在半导体器件中,射频(radio frequency,rf),表示可以辐射到空间的电磁频率,频率范围从300khz~300ghz之间。由于具有超强的辐射能力,因此在远距离传输上得以被利用,基于此,射频器件应运而生,并作为了无线通信领域中的重要设备。在现有的半导体器件(如射频器件)中,由于基底与沟道区之间间隔着绝缘层,故所述基底、绝缘层和沟道区同样也构成了一半导体结构,故将所述基底对沟道区产生的影响(例如影响了阈值电压的大小)称为背栅效应,背栅效应会导致半导体器件的阈值电压改变。目前,通过在基底上形成半导体层作为可控的背栅以实现对背栅效应的控制,但是,在制备具有背栅的半导体器件时,需要在半导体层中形成浅沟槽隔离结构,该浅沟槽隔离结构通常贯穿半导层与基底之间的绝缘层,并且在形成浅沟槽隔离结构以后,需要在浅沟槽隔离结构中形成用于制备导电插塞的接触孔,也就是说,在形成用于制备导电插塞的接触孔之前,需对其他的一些膜层进行刻蚀,例如硬掩膜层和绝缘层的刻蚀等,由此导致浅沟槽隔离结构的底部形成有较多的副产物,在后续在浅沟槽隔离结构中形成接触孔时,该副产物会阻挡接触孔的刻蚀,从而导致后续形成的导电插塞产生短路的问题。

技术实现要素:

3.本发明的目的在于提供一种半导体器件的形成方法,以解决因副产物而导致的导电插塞短路的问题。

4.为解决上述技术问题,本发明提供一种半导体器件的形成方法,包括:

5.提供一基底,所述基底上形成有绝缘层、覆盖所述绝缘层的半导体层以及贯穿所述半导体层并与所述绝缘层相接触的浅沟槽隔离结构;

6.依次形成硬掩膜层和层间介质层,所述硬掩膜层覆盖所述浅沟槽隔离结构和所述半导体层;

7.依次刻蚀所述层间介质层、所述硬掩膜层、所述浅沟槽隔离结构和所述绝缘层,以形成依次贯穿所述层间介质层、所述硬掩膜层、所述浅沟槽隔离结构和所述绝缘层的至少一个第一接触孔;

8.在所述第一接触孔中填充第一导电层,以形成第一导电插塞。

9.可选的,在所述的半导体器件的形成方法中,依次刻蚀所述层间介质层、所述硬掩膜层、所述绝缘层及所述浅沟槽隔离结构的方法包括:

10.在所述层间介质层上形成图形化的第一光刻胶层,所述图形化的第一光刻胶层中具有至少一个第一开槽,所述第一开槽对准所述浅沟槽隔离结构并暴露出所述浅沟槽隔离结构上的部分所述层间介质层;

11.以所述图形化的第一光刻胶层为掩膜,依次刻蚀暴露出的所述层间介质层、所述

硬掩膜层、所述浅沟槽隔离结构和所述绝缘层,以形成至少一个所述第一接触孔;以及,

12.去除所述图形化的第一光刻胶层。

13.可选的,在所述的半导体器件的形成方法中,在形成所述第一导电插塞以后,所述半导体器件的形成方法还包括:

14.形成至少一个第二导电插塞,所述第二导电插塞依次贯穿所述层间介质层及所述硬掩膜层并与所述半导体层相接触,其中,所述第二导电插塞的表面与所述层间介质层的表面平齐。

15.可选的,在所述的半导体器件的形成方法中,所述导电插塞的形成方法包括:

16.在所述层间介质层上形成图形化的第二光刻胶层,所述图形化的第二光刻胶层中具有至少一个第二开槽,所述第二开槽对准所述半导体层并暴露出所述半导体层上的部分所述层间介质层;

17.以所述图形化的第二光刻胶层为掩膜,依次刻蚀暴露出的所述层间介质层及所述硬掩膜层,以形成至少一个第二接触孔;

18.去除所述图形化的第二光刻胶层;以及,

19.在所述第二接触孔中填充导电层以形成第二导电插塞。

20.可选的,在所述的半导体器件的形成方法中,所述第二接触孔的深度为1000埃~2000埃。

21.可选的,在所述的半导体器件的形成方法中在刻蚀暴露出的所述层间介质层、所述硬掩膜层、所述浅沟槽隔离结构和所述绝缘层时,采用干法刻蚀工艺,所述干法刻蚀采用的气体包括氯气、氧气、二氧化硫和氦气,其中,所述二氧化硫的流量为90sccm~210sccm,所述氧气和所述氯气的流量均为5sccm~60sccm,所述氦气的流量为20sccm~100sccm。

22.可选的,在所述的半导体器件的形成方法中,所述第一开槽的宽度至少小于所述浅沟槽隔离结构的宽度的二分之一,以及所述第一接触孔的宽度至少小于所述浅沟槽隔离结构的宽度的二分之一;所述第一接触孔的深度为3000埃~4000埃。

23.可选的,在所述的半导体器件的形成方法中,所述绝缘层的材质为氧化硅;所述半导体层的材质为硅;所述硬掩膜层的材质为氧化硅和/或氮化硅。

24.可选的,在所述的半导体器件的形成方法中,在形成于所述硬掩膜层之前还包括:在所述半导体层上形成一晶体管,在形成所述硬掩膜层之后,所述硬掩膜层覆盖所述晶体管。

25.可选的,在所述的半导体器件的形成方法中,所述半导体器件包括射频器件。

26.在本发明提供的半导体器件的形成方法中,浅沟槽隔离结构仅形成于半导体层中,如此在形成浅沟槽隔离结构时,可避免对半导体层与基底之间的绝缘层进行刻蚀,可减少副产物。并且硬掩膜层形成于浅沟槽隔离结构形成之后,如此,在形成浅沟槽隔离结构时,无需对所述硬掩膜层进行刻蚀,即在形成第一导电插塞之前,无需对所述硬掩膜层和所述绝缘层进行刻蚀,从而可避免因刻蚀所述硬掩膜层和所述绝缘层而产生的副产物,由此避免因所述副产物造成的第一导电插塞短路的问题。并且,由于在形成第一导电插塞之前,无需对所述硬掩膜层进行刻蚀,从而可简化工艺步骤,节省工艺时间。

附图说明

27.图1是本发明实施例提供的半导体器件的形成方法的流程示意图;

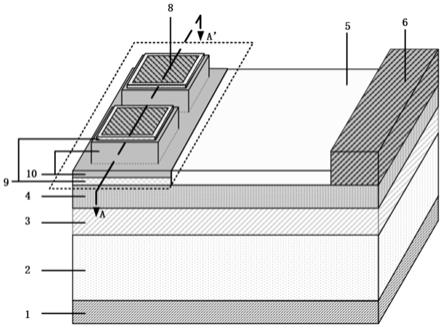

28.图2~图11是本发明实施例提供的半导体器件的形成方法中形成的结构示意图;

29.其中,附图标记说明如下:

30.101

‑

基底;110

‑

绝缘层;120

‑

半导体层;130

‑

浅沟槽隔离结构;140

‑

硬掩膜层;150

‑

层间介质层;160

‑

图形化的第一光刻胶层;160a

‑

第一开槽;170a

‑

第一接触孔;170

‑

第一导电插塞;180

‑

图形化的第二光刻胶层;180a

‑

第二开槽;190a

‑

第二接触孔;190

‑

第二导电插塞。

具体实施方式

31.以下结合附图和具体实施例对本发明提出的半导体器件的形成方法作进一步详细说明。根据下面说明,本发明的优点和特征将更清楚。需说明的是,附图均采用非常简化的形式且均使用非精准的比例,仅用以方便、明晰地辅助说明本发明实施例的目的。

32.本发明的核心思想在于,提供一种半导体器件的形成方法,在所述的半导体器件的形成方法中,浅沟槽隔离结构仅形成于半导体层中,如此在形成浅沟槽隔离结构时,可避免对半导体层与基底之间的绝缘层进行刻蚀,可减少副产物。并且硬掩膜层形成于浅沟槽隔离结构形成之后,如此,在形成浅沟槽隔离结构时,无需对所述硬掩膜层进行刻蚀,即在形成第一导电插塞之前,无需对所述硬掩膜层和所述绝缘层进行刻蚀,从而可避免因刻蚀所述硬掩膜层和所述绝缘层而产生的副产物,由此避免因所述副产物造成的第一导电插塞短路的问题。并且,由于在形成第一导电插塞之前,无需对所述硬掩膜层和所述绝缘层进行刻蚀,从而可简化工艺步骤,节省工艺时间。

33.图1是本发明实施例提供的半导体器件的形成方法的流程示意图。如图1所示,所述半导体器件的形成方法包括:

34.步骤s1:提供一基底,所述基底上形成有绝缘层、覆盖所述绝缘层的半导体层以及贯穿所述半导体层并与所述绝缘层相接触的浅沟槽隔离结构;

35.步骤s2:依次形成硬掩膜层和层间介质层,所述硬掩膜层覆盖所述浅沟槽隔离结构和所述半导体层;

36.步骤s3:依次刻蚀所述层间介质层、所述硬掩膜层、所述浅沟槽隔离结构和所述绝缘层,以形成依次贯穿所述层间介质层、所述硬掩膜层、所述浅沟槽隔离结构和所述绝缘层的至少一个第一接触孔;

37.步骤s4:在所述第一接触孔中填充第一导电层,以形成第一导电插塞。

38.图2~图11是本发明实施例提供的半导体器件的形成方法中形成的结构示意图。下文将结合2~图11对本实施例所提供的半导体器件的形成方法作更详细的说明。

39.首先,执行步骤s1,如图2所示,提供一基底101,所述基底101上形成有绝缘层110、覆盖所述绝缘层110的半导体层120以及贯穿所述半导体层120并与所述绝缘层110相接触的浅沟槽隔离结构130。所述基底101例如为硅基底。所述绝缘层110具有隔离所述基底101与所述半导体层120的作用,所述绝缘层110的材质可以为氧化硅。

40.进一步的,所述半导体层120具有多个半导体区(未图示)和隔离区(未图示),所述浅沟槽隔离结构130形成于所述隔离区,以将所述多个半导体区隔离。所述浅沟槽隔离结构

130的顶面可以与所述半导体层120的顶面平齐。在其他的实施例中,所述浅沟槽隔离结构130的顶面可以高于所述半导体层120的顶面,以使得所述多个半导体区之间具有较好的隔离性能。在后续制备半导体器件的过程中,可利用所述半导体层120(即半导体区的半导体层120)直接形成背栅,不仅能够简化半导体器件(例如射频器件)的制备过程,还能够使背栅具有良好的隔离性,使得背栅对半导体器件(例如射频器件)的阈值电压的控制更为准确。

41.优选的方案中,所述浅沟槽隔离结构130的材质与所述绝缘层110的材质相同,由于所述绝缘层110次用的材质为氧化硅,若所述浅沟槽隔离结构130采用其他材料,容易导致材料之间的应力不匹配的问题,故所述浅沟槽隔离结构130采用的材质可与所述绝缘层110采用的材质相同,例如均采用氧化硅,以避免出现不同材质的膜层之间的应力不匹配的问题。具体而言,所述浅沟槽隔离结构130例如可以采用浅沟槽隔离结构130工艺形成。由于,所述浅沟槽隔离结构130仅形成于所述半导体层120中,如此,在形成浅沟槽隔离结构时,可避免对所述半导体层120与所述基底101之间的所述绝缘层110进行刻蚀,从而可减少副产物。

42.此外,所述半导体层120上形成有半导体结构(未图示),所述半导体结构例如为一晶体管,所述晶体管可以为射频晶体管,包括栅极和位于所述栅极两侧的侧墙,以及,还包括形成于所述栅极两侧的所述半导体层120中的源区和漏区(未图示)。所述半导体层120可与位于其上方的半导体结构相应组成半导体器件,即本实施例中具有背栅的射频器件。其中,所述半导体层120的材质为硅。

43.接着,执行步骤s2,如图3所示,在所述浅沟槽隔离结构130上依次形成硬掩膜层140和层间介质层150,所述硬掩膜层140覆盖所述浅沟槽隔离结构130并延伸覆盖所述半导体层120。其中,所述硬掩膜层140的材质包括氧化硅和/或氮化硅,其用于在后续的刻蚀工艺中保护所述半导体层120和所述浅沟槽隔离结构130。所述硬掩膜层140可以采用化学气相沉积工艺(cvd)形成。

44.本实施例中,所述层间介质层150的材质为氧化硅,在其他的实施例中,所述层间介质层150的材质也可以为氮化硅或者硼磷硅玻璃等绝缘材料。所述层间介质层150用于隔离后续形成第一导电插塞170和第二导电插塞190。所述层间介质层150可以通过化学气相沉积工艺(cvd)形成。

45.本实施例中,所述硬掩膜层140形成于浅沟槽隔离结构130形成之后,如此,在形成第一导电插塞170之前,无需对所述硬掩膜层140进行刻蚀,从而可避免因刻蚀所述硬掩膜层140而产生的副产物。此外,在形成导电插塞之前,无需对所述硬掩膜层140进行刻蚀,从而可简化工艺步骤,节省工艺时间。

46.接着,执行步骤s3,如图4~6所示,依次刻蚀所述层间介质层150、所述硬掩膜层140、所述浅沟槽隔离结构130和所述绝缘层110,以形成依次贯穿浅沟槽隔离结构130、所述硬掩膜层140、所述层间介质层150和所述绝缘层110的至少一个第一接触孔170a。

47.具体的,依次刻蚀所述层间介质层150、所述硬掩膜层140、所述浅沟槽隔离结构130和所述绝缘层110的方法包括:首先,如图4所示,在所述层间介质层150上形成图形化的第一光刻胶层160,所述图形化的第一光刻胶层160中具有至少一个第一开槽160a,所述第一开槽160a对准所述浅沟槽隔离结构130并暴露出部分所述层间介质层150,所述第一开槽

160a主要用于定义所述第一接触孔170a的位置。并且所述第一开槽160a的宽度至少小于所述浅沟槽隔离结构130的宽度的二分之一,以使得后续形成的第一接触孔170a的宽度至少小于所述浅沟槽隔离结构130的宽度的二分之一。

48.然后,如图5所示,以所述图形化的第一光刻胶层160为掩膜,依次刻蚀暴露出的所述层间介质层150、所述硬掩膜层140、所述浅沟槽隔离结构130和所述绝缘层110,以形成至少一个所述第一接触孔170a,其中,可以采用干法刻蚀工艺进行刻蚀,该干法刻蚀过程可以在采用反应离子刻蚀(reactive ion etching,rie)方式或者电感耦合等离子体刻蚀(inductively coupled plasma,icp)方式的刻蚀机台进行,该干法刻蚀过程中的压强可以为9mtorr(毫托)至25mtorr,激发功率可以为500w至800w。但本实施例并不局限于此,所述干法刻蚀工艺的具体参数可以根据工艺需求以及所刻蚀材料的性质进行调节。

49.进一步的,所述干法刻蚀工艺采用的气体包括氯气、氧气、二氧化硫和氦气,其中,所述二氧化硫的流量为90sccm~210sccm,所述氧气和所述氯气的流量均为5sccm~60sccm,所述氦气的流量为20sccm~100sccm。干法刻蚀通常是各向异性刻蚀,刻蚀速率较为恒定,因而刻蚀精度更好,另外采用以上刻蚀气体,可减少刻蚀时产生的副产物。同时,本实施例中的干法刻蚀对半导体层120的刻蚀速率较低,从而可以减小或避免该干法刻蚀过程对半导体层120造成破坏。

50.本实施例中,所述第一接触孔170a的宽度至少小于所述浅沟槽隔离结构130的宽度的二分之一,如此一来,可使得所述第一接触孔170a与所述半导体层120之间还间隔有浅沟槽隔离结构130,避免后续形成的导电插塞与所述半导体层120接触。其中,所述第一接触孔170a的深度可以为3000埃~4000埃,例如3000埃、3500埃或者4000埃。

51.如图6所示,在形成所述第一接触孔170a之后,去除所述图形化的第一光刻胶层160,其中,可以利用灰化工艺或者剥离的方法去除所述图形化的第一光刻胶层160。

52.接着,如图7所示,在所述第一接触孔170a中填充第一导电层,以形成第一导电插塞170。其中,所述第一导电层的材质可以选自钨、铝、银、铬、镍、钯、钼、钛、钽或者铜,或者选自钨、铝、银、铬、镍、钯、钛、钽或者铜的合金,在另一实施例中,所述第一导电层的材质还可包括钴、氮化钛或其组合。所述第一导电层可通过高密度等离子化学气相沉积工艺(hdp cvd)形成。此外,所述第一导电插塞170与所述基底101电性连接,从而可将所述基底101引出,例如,可以将所述基底101与外围电路连接在一起。

53.如图8~11所示,在形成所述第一导电插塞170之后,所述半导体器件的形成方法还包括:形成至少一个第二导电插塞190,所述第二导电插塞190依次贯穿所述层间介质层150及所述硬掩膜层140并与所述半导体层120相接触,以实现所述第二导电插塞190与所述半导体层120的电性连接。其中,所述第二导电插塞190的表面与所述层间介质层150的表面平齐。

54.具体的,所述第二导电插塞190的形成方法包括:首先,如图8所示,在所述层间介质层150上形成图形化的第二光刻胶层180,所述图形化的第二光刻胶层180中具有至少一个第二开槽180a,所述第二开槽180a对准所述半导体层120并暴露出部分所述层间介质层150;其中,所述图形化的第二光刻胶层180覆盖所述第一导电插塞170,以避免所述第一导电插塞170在后续的工艺中被损伤。

55.然后,如图9所示,以所述图形化的第二光刻胶层180为掩膜,依次刻蚀暴露出的所

述层间介质层150及所述硬掩膜层140,以形成至少一个第二接触孔190a,其中,可以采用干法刻蚀工艺进行刻蚀,该干法刻蚀过程可以在采用反应离子刻蚀(reactive ion etching,rie)方式或者电感耦合等离子体刻蚀(inductively coupledplasma,icp)方式的刻蚀机台进行,该干法刻蚀过程中的压强可以为9mtorr(毫托)至25mtorr,激发功率可以为500w至800w。但本实施例并不局限于此,所述干法刻蚀工艺的具体参数可以根据工艺需求以及所刻蚀材料的性质进行调节。

56.进一步的,所述干法刻蚀工艺采用的气体包括氯气、氧气、二氧化硫和氦气,其中,所述二氧化硫的流量为90sccm~210sccm,所述氧气和所述氯气的流量均为5sccm~60sccm,所述氦气的流量为20sccm~100sccm。干法刻蚀通常是各向异性刻蚀,刻蚀速率较为恒定,因而刻蚀精度更好,另外采用以上刻蚀气体,可减少刻蚀时产生的副产物。同时,本实施例中的干法刻蚀对半导体层120的刻蚀速率较低,从而可以减小或避免该干法刻蚀过程对半导体层120造成破坏。即,形成所述第二接触孔190a时所采用的刻蚀气体,可以与形成所述第一接触孔170a时所采用的刻蚀气体相同。

57.如图10所示,在形成所述第二接触孔190a之后,可利用灰化工艺去除所述图形化的第二光刻胶层180,进而暴露出所述层间介质层150。

58.接着,在所述第二接触孔190a中填充第二导电层以形成第二导电插塞190,即所述第二导电插塞190形成于所述半导体层120上方,如此一来,可通过所述第二导电插塞190实现与所述半导体层120的电连接。其中,所述第二导电层的材质可以为金属钨,在其他的实施例中,所述第二导电层的材质可以选自钨、铝、银、铬、镍、钯、钼、钛、钽或者铜,或者选自钨、铝、银、铬、镍、钯、钛、钽或者铜的合金,在另一实施例中,所述第二导电层的材质还可包括钴、氮化钛或其组合。所述第二导电层可通过高密度等离子体化学气相沉积工艺形成。

59.此外,所述第二导电层填充所述第二接触孔190a之后,可以进一步对所述第二导电层执行平坦化步骤,从而形成表面平整度较好的所述第二导电插塞190,所述第二导电插塞190可与后续在其上方形成的金属互连层电性连接。

60.本实施例中,所述半导体器件包括射频器件,即所述的半导体器件的形成方法可用于射频器件的制造工艺中。

61.综上可见,在本发明提供的半导体器件的形成方法中,浅沟槽隔离结构仅形成于半导体层中,如此在形成浅沟槽隔离结构时,可避免对半导体层与基底之间的绝缘层进行刻蚀,可减少副产物。并且硬掩膜层形成于浅沟槽隔离结构形成之后,如此,在形成浅沟槽隔离结构时,无需对所述硬掩膜层进行刻蚀,即在形成第一导电插塞之前,无需对所述硬掩膜层和所述绝缘层进行刻蚀,从而可避免因刻蚀所述硬掩膜层和所述绝缘层而产生的副产物,由此避免因所述副产物造成的第一导电插塞短路的问题。并且,由于在形成第一导电插塞之前,无需对所述硬掩膜层进行刻蚀,从而可简化工艺步骤,节省工艺时间。

62.上述描述仅是对本发明较佳实施例的描述,并非对本发明范围的任何限定,本发明领域的普通技术人员根据上述揭示内容做的任何变更、修饰,均属于权利要求书的保护范围。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。