1.本发明涉及一种具有电容在晶体管上方的存储单元结构,尤其涉及一种具有更致密的结构,较小的面积,较低的漏电流,较高的电容值等优点的存储单元结构。

背景技术:

2.在现有技术中,最重要的易失性存储器(volatile

‑

memory)集成电路之一是使用1t1c存储单元的动态随机存取存储器(dynamic random access memory,dram)。所述动态随机存取存储器不仅提供了最佳的性价比功能并作为计算和通信应用程序的主存储器和/或缓冲存储器,也可作为用以从硅片上的最小特征尺寸(从几微米到二十纳米(nm)左右)微缩制造工艺技术以维持摩尔定律的最佳驱动力。近来持续使用嵌入式静态随机存取存储器(static random access memory,sram)作为其微缩制造工艺驱动力的逻辑技术声称获得接近5纳米的制造工艺的最先进的技术节点。相较之下,所述动态随机存取存储器所声称的最佳技术节点仍在10至12纳米以上,其主要问题在于即使通过非常激进的设计规则也很难进一步微缩所述1t1c存储单元的结构,其中所述非常激进的设计规则是用于微缩所述1t1c存储单元内的存取晶体管(也就是1t)和立体(three

‑

dimensional,3d)存储电容(也就是1c),且所述立体存储电容例如为在所述存取晶体管的一部分的上方和隔离区上方的堆叠电容,或为可能位于所述存取晶体管下方非常深的沟槽电容。

3.在此详细阐述尽管在技术、设计和设备上投入巨额的资金和研发的情况下微缩所述1t1c存储器单元所面临的众所周知的困难。以下列举一些众所周知困难的例子:(1)所述存取晶体管的结构遭受不可避免且更严重的的漏电流问题,从而降低了所述1t1c存储单元的存储功能(例如减少所述动态随机存取存储器刷新时间);(2)布局字线,位线和存储电容的几何和表面形貌的复杂性以及所述字线、所述位线、所述存储电容和所述存取晶体管的栅极,源极和漏极之间的连接在微缩所述动态随机存取存储器时变得越来越糟;(3)所述沟槽电容遭受所述沟槽电容的深度与开口尺寸的长宽比过大的问题,且所述沟槽电容的制造工艺几乎停止在14纳米节点工艺;(4)所述堆叠电容遭受更糟的表面形貌,并且在所述存取晶体管的主动区域从20度扭转到50度以上后,几乎没有空间可作为所述存储电容的存储电极与所述存取晶体管的源极之间的接触空间。另外,用于所述位线与所述存取晶体管的漏极的接触的可允许空间越来越小,但却又必须艰难地维持自对准特征;(5)除非能够发现用于获得较高存储电容的电容值的高介电常数(high

‑

k)绝缘体材料,否则所述存取晶体管恶化的漏电流问题将要求增加所述堆叠电容器的电容值并保持持续增加堆叠电容器的高度以得到更大的电容面积;(6)因为在日益要求更高的密度/容量和性能的情况下,对所述动态随机存取存储器芯片更好的可靠性,质量和弹性的所有日益增长的要求都变得越来越难以满足等等。

4.然而现有技术并没有任何技术突破以解决上述问题,所以如何设计所述1t1c存储单元的新结构去解决上述问题已成为所述1t1c存储单元的设计者的一项重要课题。

技术实现要素:

5.本发明公开了一种应用于动态随机存取存储器的新的存储单元结构,其中所述存储单元结构在存取晶体管(1t)上直接垂直集成存储电容(1c)。本发明利用具有设计良好的渐变掺杂浓度并与所述存取晶体管的栅极结构自对准的三维(three

‑

dimensional,3d)的源极电极的所述存储单元结构将漏电流大幅降低至毫微安(femto

‑

ampere)等级,其中所述漏电流包含最困难的泄漏源例如栅极引起的漏极泄漏以及结泄漏(junction leakages)。因为所述漏电流显着地降低,所以可以将所述存储电容的电容值维持在合理的范围,也就是说所述存储电容的尺寸可以缩小,进而减少所述存储电容的的寄生电容。所述3d源极电极也通过自对准技术进行扩展以连接到所述存储电容的信号存储节点。因为所述存储电容另以自对准方式像住宅上的电塔一样地直接形成在所述存取晶体管上方,所以所述存储单元结构称为在所述存取晶体管上的电容塔,也称为tot单元。另外,本发明也公开所述存储电容的新的对电极板,其中所述对电极板使用金属材料覆盖几乎向下到所述存取晶体管的主动区的表面以及向上到所述存储电容的顶部的高介电常数绝缘体,其中所述对电极板可作为用于所述存储电容的非常牢靠的(也就是极低的阻抗和噪声)恒定电压平面(通常偏置在half

‑

vcc电平)。所述存储单元结构的硅表面下位线是用于减小所述存储单元结构的形貌并自对准以连接到所述存取晶体管的漏极,以及提供给所述字线的良好设计的正交结构也大大降低硅表面下位线和所述字线之间的耦合效应。另外,降低了与所述硅表面下位线相关的寄生电容和电阻电容(rc)时间常数可允许将更多位连接到所述硅表面下位线或扩大传感信号,其中所述传感信号是所述存储电容的电容值与所述位线的电容值的比值。垂直建构的所述对电极板可创造一个被金属材料很好覆盖的tot单元的平坦表面使得电场在所述存储单元结构内更均匀地分布并具有更佳的散热效果。另外,所述字线的结构不同于现有技术的埋入式(buried)字线结构,其中所述字线的结构可以自对准所述存取晶体管的栅极结构。因为可通过所述自对准技术形成所述字线,所述硅表面下位线,所述源极,所述漏极,所述信号电极,所述对电极板,以及所有相关的连接,所以当制造工艺微缩时,所述tot单元的尺寸更加可控,如此提供了扩展所述1t1c存储单元微缩至10纳米以下的解决方案。

6.本发明的一实施例公开一种存储单元结构。所述存储单元结构包含一硅基板,一晶体管,一位线,和一电容。所述硅基板具有一硅表面。所述晶体管耦接所述硅表面,其中所述晶体管包含一栅极结构、一第一导通区以及一第二导通区。所述位线电耦接所述晶体管的第一导通区以及位在所述硅表面下方。所述电容位在所述晶体管上方以及电耦接所述晶体管的第二导通区。

7.在本发明的另一实施例中,所述电容至少包围所述晶体管的顶部和一侧壁。

8.在本发明的另一实施例中,所述位线通过一桥接触电耦接所述晶体管的第一导通区,所述桥接触位在所述硅表面下方,所述桥接触的第一侧壁与所述位线的边缘对齐,以及所述桥接触包含一上半部和一下半部,其中所述桥接触的上半部毗邻所述硅基板,以及所述桥接触下半部通过一第一隔离层与所述硅基板隔离。

9.在本发明的另一实施例中,所述存储单元结构另包含一字线,其中所述字线延伸至所述晶体管外以及耦接所述晶体管的栅极结构,所述字线包含一上半部,所述字线的上半部位于所述硅表面上,以及所述字线的上半部的一侧壁与所述栅极结构的一侧壁对齐。

10.在本发明的另一实施例中,所述晶体管另包含一介电层,且所述介电层围绕所述字线和所述栅极结构。

11.在本发明的另一实施例中,所述栅极结构的至少一部分从所述硅表面向下延伸。

12.在本发明的另一实施例中,所述存储单元结构另包含一第一间隔层和一第二间隔层。所述第一间隔层覆盖所述栅极结构的第一侧壁且位在所述硅表面上方。所述第二间隔层覆盖所述栅极结构的第二侧壁且位在所述硅表面上方。所述晶体管的第一导通区从所述硅表面向上延伸以及毗邻所述第一间隔层,以及所述晶体管的第二导通区从所述硅表面向上延伸以及毗邻所述第二间隔层。

13.本发明的另一实施例公开了一种存储单元结构。所述存储单元结构包含一硅基板,一晶体管,一位线,和一电容。所述硅基板具有一硅表面。所述晶体管耦接所述硅表面,其中所述晶体管包含一栅极结构、一第一导通区以及一第二导通区。所述位线电耦接所述晶体管的第一导通区。所述电容电耦接所述晶体管的第二导通区以及围绕所述晶体管。

14.在本发明的另一实施例中,所述电容包含一第一部和一第二部,所述电容的第一部垂直堆迭在所述晶体管的顶部上方,以及所述电容的第二部毗邻所述晶体管的一侧壁。

15.在本发明的另一实施例中,所述位线位在所述硅表面下方以及通过一桥接触电耦接所述晶体管的第一导通区。

16.在本发明的另一实施例中,所述桥接触位在所述硅表面下方以及所述桥接触的第一侧壁与所述位线的边缘对齐。

17.在本发明的另一实施例中,所述桥接触包含一上半部和一下半部,所述桥接触的上半部毗邻所述硅基板,以及所述桥接触下半部通过一第一隔离层与所述硅基板隔离。

18.在本发明的另一实施例中,所述第一隔离层至少覆盖所述桥接触的下半部的一第一侧壁、一第二侧壁和一底部。

19.在本发明的另一实施例中,所述桥接触的上半部包含一金属区和一掺杂半导体区,所述掺杂半导体区围绕所述金属区,以及所述掺杂半导体区毗邻所述硅基板。

20.在本发明的另一实施例中,所述桥接触位在所述硅表面下方以及一第一介电帽覆盖所述桥接触的顶部表面。

21.在本发明的另一实施例中,所述晶体管另包含一第一间隔层和一第二间隔层,所述第一间隔层覆盖所述栅极结构的第一侧壁以及位在所述硅表面上方,以及所述第二间隔层覆盖所述栅极结构的第二侧壁和位在所述硅表面上方;其中所述晶体管的第一导通区从所述硅表面向上延伸和毗邻所述第一间隔层,以及所述晶体管的第二导通区从所述硅表面向上延伸和毗邻所述第二间隔层。

22.在本发明的另一实施例中,所述存储单元结构另包含一第二介电帽,其中所述第二介电帽覆盖所述晶体管的第一导通区的顶部表面。

23.本发明的另一实施例公开了一种存储单元结构。所述存储单元结构包含一硅基板,一晶体管,和一电容。所述硅基板具有一硅表面。所述晶体管耦接所述硅表面,其中所述晶体管包含一栅极结构、一第一导通区以及一第二导通区。所述电容位在所述晶体管上方以及电耦接所述晶体管的第二导通区。所述存储单元结构的平面尺寸小于λ2的10倍,λ是一最小特征尺寸,以及所述最小特征尺寸等于或小于10纳米。

24.在本发明的另一实施例中,所述晶体管另包含一介电帽和一间隔层,所述介电帽

垂直堆迭在所述栅极结构上方,以及所述间隔层覆盖所述栅极结构的一侧壁;其中所述晶体管的第二导通区从所述硅表面向上延伸以及毗邻所述间隔层;其中所述电容包含第一部和一第二部,所述电容的第一部垂直位于所述介电帽上方,以及所述电容的第二部毗邻所述第二导通区。

25.本发明的另一实施例公开了一种存储单元结构。所述存储单元结构包含一硅基板,一晶体管,和一电容。所述硅基板具有一硅表面。所述晶体管耦接所述硅表面,其中所述晶体管包含一栅极结构、一第一导通区以及一第二导通区。所述电容位在所述晶体管上方以及电耦接所述晶体管的第二导通区。所述电容包含围绕所述晶体管的一金属电极。

26.在本发明的另一实施例中,所述电容另包含一介电层,所述金属电极围绕所述介电层,以及所述介电层围绕所述晶体管。

27.在本发明的另一实施例中,所述电容另包含一半导体电极,以及所述介电层围绕所述半导体电极。

28.本发明的另一实施例公开了一种存储单元结构,其中所述存储单元结构形成在一桥接触和一隔离沟槽之间,所述桥接触和所述隔离沟槽的至少一部分是在一硅基板的一硅表面下方,以及所述存储单元结构耦接一字线和一位线。所述存储单元结构包含一晶体管和一电容。所述晶体管耦接所述硅表面,其中所述晶体管包含一栅极结构、一第一导通区以及一第二导通区。所述电容位在所述晶体管上方以及电耦接所述晶体管的第二导通区。所述位线是设置在所述硅表面下方,所述桥接触的下半部毗邻所述位线,以及所述桥接触的上半部毗邻位在所述第一导通区下方的所述硅基板的部分。

29.在本发明的另一实施例中,所述字线延伸至所述晶体管外以及耦接所述晶体管的栅极结构,所述字线包含一上半部,所述字线的上半部位于所述硅表面上,以及一互连导线的上半部的一侧壁与所述栅极结构的一侧壁对齐。

30.在本发明的另一实施例中,所述电容另包含一金属电极,以及所述金属电极的第一部垂直位于所述隔离沟槽上方。

31.在本发明的另一实施例中,所述电容另包含一介电层,所述金属电极围绕所述介电层,以及所述介电层的第一部毗邻所述第二导通区和所述金属电极的第一部。

32.在本发明的另一实施例中,所述金属电极的第一部的延伸方向平行所述硅基板的法线方向,所述介电层的第一部的延伸方向平行所述硅基板的法线方向,以及所述第二导通区的延伸方向平行所述硅基板的法线方向。

附图说明

33.图1a是本发明的一实施例所公开的一种动态随机存取存储器存储单元(1t1c cell)阵列的制造方法的流程图。

34.图1b

‑

1j是说明图1a的示意图。

35.图2是说明沉积衬垫氮化层和衬垫氧化层以及形成浅沟槽隔离后的上视图和沿着所述x方向的剖面图的示意图。

36.图3是说明沉积和回蚀第一氮化层以形成第一氮化间隔层,以及沉积旋涂电介质层和光刻胶层的示意图。

37.图4是说明蚀刻掉没有被光刻胶层覆盖的上边缘第一氮化间隔层和旋涂电介质的

示意图。

38.图5是说明剥离光刻胶层和旋涂电介质,且生成第一氧化层的示意图。

39.图6是说明沉积金属层在沟槽中且通过所述化学机械平坦化技术平坦化的示意图。

40.图7是说明沉积光刻胶层的示意图。

41.图8是说明蚀刻对应所述主动区的末端的金属层的示意图。

42.图9是说明移除光刻胶层且回蚀金属层以形成硅表面下位线的示意图。

43.图10是说明在沟槽中沉积第二氧化层的示意图。

44.图11是说明沉积第三氧化层,第二氮化层,以及光刻胶层,然后移除第三氧化层,第二氮化层,以及光刻胶层的不必要部份的示意图。

45.图12是说明移除光刻胶层,衬垫氮化层,以及衬垫氧化层的示意图。

46.图13是说明形成u形凹槽,形成高介电常数绝缘层以作为存取晶体管的栅极介电层,以及沉积并回蚀栅极材料以形成存取晶体管的字线和栅极结构的示意图。

47.图14是说明沉积第三氮化层和第四氧化层,之后回蚀或平坦化第三氮化层和第四氧化层的示意图。

48.图15是说明蚀刻掉第二氮化层和第三氧化层的示意图。

49.图16是说明移除衬垫氮化层,回蚀第二氧化层,以及沉积和蚀刻第四氮化层,第五氧化层,以及第一多晶硅层的示意图。

50.图17是说明沉积和平坦化旋涂电介质,蚀刻第一多晶硅层的上半部,以及沉积和平坦化第一氧化帽层的示意图。

51.图18是说明移除旋涂电介质,然后沉积第五氮化层的示意图。

52.图19是说明沉积旋涂电介质层,沉积光刻胶,以及移除对应所述源极的旋涂电介质层的示意图。

53.图20是说明蚀刻掉暴露的第五氮化层和位在所述源极的区域的中心的衬垫氧化层,以及挖掘对应所述源极的区域的中心的硅材料以产生孔洞的示意图。

54.图21是说明在孔洞热生成第七氧化层的示意图。

55.图22是说明沉积和回蚀旋涂电介质层的示意图。

56.图23是说明沉积光刻胶覆盖对应所述源极的区域以及暴露出为所述漏极保留的区域,然后移除暴露的旋涂电介质层,暴露的第五氮化层,暴露的衬垫氧化层,以及移除对应水平硅表面的硅材料以产生孔洞的示意图。

57.图24是说明移除光刻胶,然后热生成第八氧化层以产生第八氧化间隔层的示意图。

58.图25是说明所述动态随机存取存储器存储单元阵列沿着所述y2方向的剖面图的示意图。

59.图26是说明蚀刻孔洞内的下边缘第一氮化间隔层的示意图。

60.图27是说明移除第五氮化层的示意图。

61.图28是说明沉积和回蚀金属层以在孔洞内留下钨插销,以及沉积和蚀刻第六氮化层的示意图。

62.图29是说明回蚀所述钨插销在水平硅表面下方的上半部的示意图。

63.图30是说明所述钨插销连接至ugbl的示意图。

64.图31是说明移除第八氧化层的上半部的示意图。

65.图32是说明横向生长n 原位掺杂硅层以形成n 硅漏环的示意图。

66.图33是说明在n 硅漏环上局部热生成第九氧化层的示意图。

67.图34是说明移除所有的旋涂电介质层,第五氮化层,和第六氮化层的示意图。

68.图35是说明所述动态随机存取存储器存储单元阵列的上视图的示意图。

69.图36是说明沉积和回蚀金属层的示意图。

70.图37是说明移除第一氧化帽层,第一多晶硅间隔层,和衬垫氧化层以暴露出对应所述源极和所述漏极的水平硅表面的示意图。

71.图38是说明生成源极电极和漏极电极的示意图。

72.图39是说明蚀刻掉第五氧化间隔层,以及热生成和蚀刻氧化层

‑

a的示意图。

73.图40是说明生成源极电极和漏极电极的示意图。

74.图41是说明蚀刻掉钨缓冲墙的示意图。

75.图42是说明形成高介电常数(high

‑

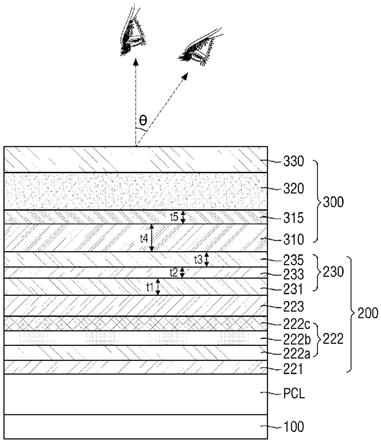

k)绝缘体材料的示意图。

76.图43是说明沉积和回蚀金属层的示意图。

77.图44是说明蚀刻掉在第四氧化层上方的第一高介电常数绝缘层,然后蚀刻掉第四氧化层的示意图。

78.图45是说明移除第三氮化层的上半部以及也移除所述第四氮化间隔层的上半部的示意图。

79.图46是说明横向生长源极电极和漏极电极的示意图。

80.图47是说明热生成氧化层

‑

b,然后沉积和回蚀第十氧化层示意图。

81.图48是说明沉积光刻胶层的示意图。

82.图49是说明蚀刻在漏极电极的顶部上方的第一金属对电极板和壁(mcepw

‑

1)以形成钨插销,以及蚀刻掉部分曝露的第一高介电常数绝缘层以形成第一高介电常数绝缘间隔层a的示意图。

83.图50是说明蚀刻掉漏极电极的上半部,移除光刻胶,热生成氧化层

‑

c,以及沉积和回蚀氧化层

‑

c1的示意图。

84.图51是说明移除第一金属对电极板和壁的示意图。

85.图52是说明蚀刻掉在所有平面上暴露的第一高介电常数绝缘层但是留下第一高介电常数绝缘间隔层的示意图。

86.图53是说明沉积和回蚀旋涂电介质层的示意图。

87.图54是说明蚀刻氧化层

‑

b,第十氧化层,以及氧化层

‑

c1在所述储存电极塔的晶种基础的高度上方的部分,然后蚀刻掉旋涂电介质层示意图。

88.图55是说明长出n 原位重掺杂硅塔=的示意图。

89.图56是说明形成第二高介电常数绝缘层的示意图。

90.图57是说明沉积金属层的示意图。

91.图58是说明回蚀所述第二金属对电极板和壁以使其高度低于存储电极的高度,以及蚀刻掉第二高介电常数绝缘层在n 原位重掺杂硅塔的顶部上方的部分的示意图。

92.图59是说明长出更高的n 原位重掺杂硅塔以作为存储电容的信号电极,然后形成

第三高介电常数绝缘层的示意图。

93.图60是说明形成光刻胶的示意图。

94.图61是说明蚀刻掉暴露的第三高介电常数绝缘层以暴露出第二金属对电极板和壁的边缘区域的示意图。

95.图62是说明移除光刻胶的示意图。

96.图63是说明沉积金属以完成存储电容的对电极板的示意图。

97.图64是说明本发明所公开的所述tot单元的结构的示意图。

98.其中,附图标记说明如下:

99.202

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

基板

100.204

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

衬垫氧化层

101.206

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

衬垫氮化层

102.208、hss

‑

1/2、hss

‑

1/3、hss

ꢀꢀꢀꢀꢀꢀ

水平硅表面

103.210

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

沟槽

104.214

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

氧化层

105.304、1902、2202、5302

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

旋涂电介质

106.306、702、1106、4802

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

光刻胶层

107.502

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

第一氧化层

108.504

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

第一氧化/sti层

109.602、3602、4302、mcepw

‑

1、5702、 金属层

110.6302

111.902、ugbl

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

硅表面下位线

112.1002、cvd

‑

sti

‑

oxide2

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

第二氧化层

113.1102

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

第三氧化层

114.1104

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

第二氮化层

115.1302

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

u形通道

116.1304

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

高介电常数绝缘层

117.1306

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

栅极材料

118.1402

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

第三氮化层

119.1404

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

第四氧化层

120.1602

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

第四氮化层

121.1604

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

第五氧化层

122.1606

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

第一多晶硅层

123.1702

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

旋涂电介质

124.1704

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

第一氧化帽层

125.1802

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

第五氮化层

126.1904、2302、6002

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

光刻胶

127.2102

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

第七氧化层

128.2402

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

第八氧化层

129.2802

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

钨插销

130.2804

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

第六氮化层

131.3202

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

n 原位掺杂硅层

132.3302

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

第九氧化层

133.3902

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

氧化层

‑

a

134.4202

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

第一高介电常数绝缘层

135.4204

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

水平high

‑

k

‑

cap

‑1136.4206

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

垂直间隔层部分

137.4702

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

氧化层

‑

b

138.4704

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

第十氧化层

139.4902

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

tungsten

‑

a

140.4904

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

第一高介电常数绝缘间隔层a

141.5002

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

氧化层

‑

c

142.5004

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

氧化层

‑

c1

143.5502、5902

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

n 原位重掺杂硅塔

144.5602

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

第二高介电常数绝缘层

145.5904

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

第三高介电常数绝缘层

146.aq1、aq2、aq3

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

存取晶体管

147.drain

‑1ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

第一漏极

148.drain

‑2ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

第二漏极

149.eh

‑

1d、eh

‑

2d、eh

‑

1 2d、lgs

‑

2d

ꢀꢀꢀ

漏极电极

150.eh

‑

1s、eh

‑

2s、eh

‑

1 2s、lgs

‑

2s

ꢀꢀꢀ

源极电极

151.hole

‑

1/2、hole

‑

1/3

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

孔洞

152.shar

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

用于源极和漏极的晶种硅表面区

153.source

‑1ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

第一源极

154.sti

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

浅沟槽隔离

155.source

‑3ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

第三源极

156.sbset

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

储存电极塔的晶种基础

157.wordline

‑1ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

第一字线

158.wordline

‑2ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

第二字线

159.wordline

‑3ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

第三字线

160.10

‑

55、102

‑

198

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

步骤

具体实施方式

161.请参照图1a

‑

1f,其中图1a是本发明的一实施例所公开的一种动态随机存取存储器存储单元(1t1c cell)阵列的制造方法的流程图,详细步骤如下∶

162.步骤10:开始;

163.步骤15:基于一基板(例如,一p型硅基板),定义所述动态随机存取存储器存储单元阵列的主动区并形成浅沟槽隔离(shallow trench isolation,sti);

164.步骤20:沿着所述主动区的侧壁,形成非对称的间隔层;

165.步骤25:在所述非对称的间隔层和所述基板的水平表面之下,形成硅表面下导线(例如位线);

166.步骤30:形成所述动态随机存取存储器存储单元阵列的存取晶体管的字线和栅极结构;

167.步骤35:定义所述动态随机存取存储器存储单元阵列的存取晶体管漏极(也就是第一导通区)和源极(也就是第二导通区);

168.步骤40:在所述水平表面下导线和所述存取晶体管的漏极之间形成连结;

169.步骤45:形成所述存取晶体管的漏极和源极;

170.步骤50:在所述存取晶体管上方形成一电容塔;

171.步骤55:结束。

172.请参照图1b和图2,步骤15包含:

173.步骤102:在基板202的水平硅表面208(也就是所述水平表面)上方沉积衬垫氧化层204和衬垫氮化层206;

174.步骤104:定义所述动态随机存取存储器存储单元阵列的主动区,且移除对应所述主动区之外的水平硅表面208的基板材料(例如硅材料)以产生沟槽210;

175.步骤106:在沟槽210内沉积且回蚀(etch back)氧化层214以在水平硅表面208下方形成所述浅沟槽隔离(sti)。

176.请参照图1c和图3

‑

5,步骤20包含:

177.步骤108:沉积和回蚀第一氮化层以形成第一氮化间隔层(图3);

178.步骤110:在沟槽210内沉积旋涂电介质(spin

‑

on dielectrics,旋涂电介质层)304且通过化学机械平坦化(chemical mechanical polishing,cmp)技术平坦化(图3);

179.步骤112:在旋涂电介质304和衬垫氮化层206上方沉积光刻胶层306(图3);

180.步骤114:完全蚀刻没有被光刻胶层306覆盖的上边缘第一氮化间隔层和旋涂电介质304(图4);

181.步骤116:剥离光刻胶层306和旋涂电介质304,且生成(例如热生成)第一氧化层502(图5)。

182.请参照图1d和图6

‑

10,步骤25包含:

183.步骤118:沉积金属层602在沟槽210中且通过所述化学机械平坦化技术平坦化(图6);

184.步骤120:沉积并图案化光刻胶层702(图7);

185.步骤122:蚀刻对应所述主动区的末端的金属层602以形成多条导线(图8);

186.步骤124:移除光刻胶层702且回蚀金属层602(所述多条导线)以形成硅表面下位线(underground bit line,ugbl)902或硅表面下导线(图9);

187.步骤126:在沟槽210中沉积第二氧化层1002且通过所述化学机械平坦化技术平坦化(图10)。

188.请参照图1e和图11

‑

15,步骤30包含:

189.步骤128:沉积第三氧化层1102,第二氮化层1104,以及图案化的光刻胶层1106,然后蚀刻掉第三氧化层1102和第二氮化层1104的不必要部份(图11);

190.步骤130:移除图案化的光刻胶层1106,衬垫氮化层206,以及衬垫氧化层204,以及

露出水平硅表面208(图12);

191.步骤132:蚀刻水平硅表面208以形成u形凹槽,在所述u形凹槽内形成高介电常数(high

‑

k)绝缘层1304,以及沉积并回蚀栅极材料1306(例如钨)以形成所述存取晶体管的字线和栅极结构(图13),其中所述存取晶体管可以称为u型晶体管;

192.步骤134:沉积并回蚀第三氮化层1402,随后沉积第四氧化层1404,之后回蚀或平坦化第四氧化层1404(图14);

193.步骤136:蚀刻掉第二氮化层1104和第三氧化层1102(图15)。

194.请参照图1f和图16

‑

22,步骤35包含:

195.步骤138:移除衬垫氮化层206,以及回蚀第二氧化层1002至衬垫氧化层204的顶部;

196.步骤140:分别沉积以及各向异性蚀刻(anisotropic etch)第四氮化层1602,第五氧化层1604,以及第一多晶硅层1606(图16);

197.步骤142:沉积和通过所述化学机械平坦化技术平坦化旋涂电介质1702,蚀刻第一多晶硅层1606的上半部,以及沉积和通过所述化学机械平坦化技术平坦化第一氧化帽层1704(图17);

198.步骤144:移除旋涂电介质1702,然后沉积第五氮化层1802(图18);

199.步骤146:沉积和通过所述化学机械平坦化技术平坦化旋涂电介质1902,沉积光刻胶1904,然后回蚀要移除的旋涂电介质1902(图19);

200.步骤148:蚀刻掉暴露的第五氮化层1802,衬垫氧化层204,以及对应水平硅表面hss

‑

1/3的硅材料以产生孔洞hole

‑

1/3(图20);

201.步骤150:移除光刻胶1904以及热生成第七氧化层2102(图21);

202.步骤152:在第七氧化层2102上方沉积旋涂电介质层2202,然后回蚀旋涂电介质层2202(图22)。

203.请参照图1g和图23

‑

33,步骤40包含:

204.步骤154:沉积光刻胶2302,移除暴露的旋涂电介质1902、暴露的第五氮化层1802以及暴露的衬垫氧化层204,然后挖掘和移除对应水平硅表面hss

‑

1/2的硅材料以产生孔洞hole

‑

1/2(图23);

205.步骤156:移除光刻胶2302和热生成第八氧化层2402(图24和图25);

206.步骤158:移除所述第一氮化间隔层的下边缘以露出硅表面下位线902(ugbl)的侧壁,以及移除第五氮化层1802(图26和图27);

207.步骤160:在孔洞hole

‑

1/2中沉积金属层2802以接触硅表面下位线902(ugbl)的侧壁,然后沉积和回蚀第六氮化层2804创造出第六氮化间隔层(图28);

208.步骤162:回蚀金属层2802的上半部(图29和图30);

209.步骤164:回蚀第八氧化层2402的上半部以露出对应孔洞hole

‑

1/2的硅材料(图31);

210.步骤166:基于露出的硅材料横向生长n 原位掺杂(n in

‑

situ doped)硅层3202以接触所述漏极和钨插销(图32);

211.步骤168:在n 原位掺杂硅层3202上方热生成第九氧化层3302(图33)。

212.请参照图1h和图34

‑

41,步骤45包含:

213.步骤170:移除所有的旋涂电介质层(也就是旋涂电介质层和旋涂电介质层2202),第五氮化层1802,以及第六氮化层2804(图34);

214.步骤171:沉积和回蚀金属层3602(图36);

215.步骤172:蚀刻掉第一氧化帽层1704,所述第一多晶硅间隔层,以及所述第一多晶硅间隔层下方的衬垫氧化层204以暴露出对应所述源极所述漏极的水平硅表面208(图37);

216.步骤173:通过所述选择性外延生长技术生成源极电极eh

‑

1s和漏极电极eh

‑

1d(图38);

217.步骤174:蚀刻掉所述第五氧化间隔层,以及热生成并蚀刻氧化层

‑

a3902(图39);

218.步骤175:根据源极电极eh

‑

1s和漏极电极eh

‑

1d,通过所述选择性外延生长技术分别生成源极电极eh

‑

2s和漏极电极eh

‑

2d(图40);

219.步骤176:蚀刻掉金属层3602(图41)。

220.请参照图1i、1j和图42

‑

64,步骤50包含:

221.步骤177:形成第一高介电常数绝缘层4202(图42);

222.步骤178:沉积和回蚀金属层4302,例如钨(图43);

223.步骤179:蚀刻掉在第四氧化层1404上方的第一高介电常数绝缘层4202,然后蚀刻掉第四氧化层1404(图44);

224.步骤180:移除第三氮化层1402的上半部和所述第四氮化间隔层的上半部(图45);

225.步骤181:通过所述选择性外延生长技术利用所述eh

‑

2电极暴露的硅侧壁在第三氮化层1402上方横向生长n 原位重掺杂硅材料(图46);

226.步骤182:在上述横向生长的n 原位重掺杂硅材料的顶部上方热生成氧化层

‑

b 4702(以下称为储存电极塔的晶种基础(seeding base for growing storage

‑

electrode tower,sbset)),以及沉积和回蚀第十氧化层4704(图47);

227.步骤183:沉积光刻胶层4802(图48);

228.步骤184:蚀刻在漏极电极eh

‑

2d的顶部上方的暴露的金属层4302以形成金属插销(或钨插销)4902(以下称为tungsten

‑

a 4902),以及也蚀刻部分曝露的第一高介电常数绝缘层4202以形成第一高介电常数绝缘间隔层a 4904(图49);

229.步骤185:蚀刻掉部分漏极电极eh

‑

2d的上半部,移除光刻胶4802,在漏极电极eh

‑

2d的剩余部分的顶部上方热生成氧化层

‑

c 5002,以及沉积和回蚀氧化层

‑

c1 5004(图50);

230.步骤186:移除暴露的金属层4302(图51);

231.步骤187:蚀刻掉在所有平面上暴露的第一高介电常数绝缘层4202,但是留下第一高介电常数绝缘层4202的垂直间隔层部分4206(图52);

232.步骤188:沉积和回蚀旋涂电介质层5302(图53);

233.步骤189:蚀刻氧化层

‑

b 4702,第十氧化层4704,以及氧化层

‑

c1 5004在所述储存电极塔的晶种基础的高度上方的部分,然后蚀刻掉旋涂电介质层5302(图54);

234.步骤190:通过所述选择性外延生长技术长出n 原位重掺杂硅塔5502(图55);

235.步骤191:形成覆盖包含n 原位重掺杂硅塔5502的所有侧壁和顶部的第二高介电常数绝缘层5602(图56);

236.步骤192:沉积金属层5702(图57);

237.步骤193:回蚀金属层5702,然后蚀刻第二高介电常数绝缘层5602在n 原位重掺杂

硅塔5502的顶部上方的部分(图58);

238.步骤194:通过所述选择性外延生长技术长出n 原位重掺杂硅塔5902以及形成第三高介电常数绝缘层5904(图59);

239.步骤195:形成光刻胶6002以覆盖除了暴露的第三高介电常数绝缘层5904的边缘区域外的所有存储单元阵列区域(图60);

240.步骤196:蚀刻掉暴露的第三高介电常数绝缘层5904以暴露出金属层5702的边缘区域(图61);

241.步骤197:移除光刻胶6002(图62);

242.步骤198:沉积金属层6302(图63)。

243.上述制造方法的详细说明如下。上述制造方法是从p型硅片(也就是p型基底202)开始。在步骤102,如图2(a)所示,在水平硅表面208(如果所述基板是硅基板)上方形成衬垫氧化层204,然后在衬垫氧化层204上方沉积衬垫氮化层206,其中水平硅表面208也称为hss(horizontal silicon surface)或oss(original silicon surface),之后的附图说明是以水平硅表面208或hss为例。

244.在步骤104中,可通过光刻掩模技术(photolithographic mask technique)定义所述动态随机存取存储器存储单元阵列的主动区,其中图2(a)所示,因为所述动态随机存取存储器存储单元阵列的主动区对应衬垫氧化层204和衬垫氮化层206,所以在主动区图案(active region pattern)之外的水平硅表面208将据此而暴露。因为在所述主动区图案之外的水平硅表面208被暴露,所以对应所述主动区图案之外的水平硅表面208的硅材料可被各向异性蚀刻技术(anisotropic etching technique)移除以制造出沟槽(或渠道)210,其中例如,沟槽210可在水平硅表面208之下达到250纳米(nm)深。

245.在步骤106中,沉积氧化层214以填满沟槽210,然后回蚀氧化层214以在沟槽210内形成在水平硅表面208下方的所述浅沟槽隔离。另外,图2(b)是对应图2(a)的上视图,其中图2(a)是沿着如图2(b)所示的x方向的切割线的剖面图。另外,如图2(a)所示,例如,所述浅沟槽隔离具有约50纳米的厚度,以及如果低于水平硅表面208的沟槽210具有250纳米的深度,则所述浅沟槽隔离的顶部距离水平硅表面208约200纳米深。

246.在步骤108,如图3(a)所示,沉积所述第一氮化层和利用所述各向异性蚀刻技术回蚀所述第一氮化层以沿着沟槽210的两边缘(也就是上边缘和下边缘)形成所述第一氮化间隔层。在步骤110中,如图3(a)所示,在沟槽210内的所述浅沟槽隔离上方沉积旋涂电介质304以填充沟槽210。然后过所述化学机械平坦化技术平坦化旋涂电介质304以使旋涂电介质304的顶部和衬垫氮化层206的顶部平齐。

247.在步骤112中,如图3(a)所示,利用所述光刻掩模技术通过光刻胶层306保护沿着沟槽210的下边缘的所述第一氮化间隔层的下边缘第一氮化间隔层,但是沿着沟槽210的上边缘的所述第一氮化间隔层的上边缘第一氮化间隔层则不被光刻胶层306保护。也就是说在旋涂电介质304和衬垫氮化层206上方沉积光刻胶层306后,因为在所述上边缘第一氮化间隔层上的光刻胶层306被移除但所述下边缘第一氮化间隔层上的光刻胶层306被保留,所以之后所述下边缘第一氮化间隔层可被保留但所述上边缘第一氮化间隔层会被移除。另外,图3(b)是对应图3(a)的上视图,其中图3(a)是沿着如图3(b)所示的y方向的切割线的剖面图。在步骤114中,如图4所示,可通过蚀刻工艺蚀刻掉没有被光刻胶层306覆盖的所述上

边缘第一氮化间隔层和旋涂电介质304。

248.在步骤116中,如图5所示,剥离光刻胶层306和旋涂电介质304,其中旋涂电介质304具有远高于热生成氧化层和沉积氧化层的蚀刻速率。然后热生成第一氧化层502以形成第一氧化间隔层,其中所述第一氧化间隔层覆盖沟槽210的上边缘,第一氧化层502不会长超过衬垫氮化层206,以及仅有非常薄的氧化层(称为第一氧化/sti层504)形成在所述浅沟槽隔离上方。如图5所示,步骤116导致非对称的间隔层(也就是所述下边缘第一氮化间隔层(也就是权利要求7、16所述的第一间隔层)和所述第一氧化间隔层(也就是权利要求7、16所述的第二间隔层))分别形成在沟槽210的两对称边缘(也就是沟槽210的上边缘和下边缘)。例如,所述第一氧化间隔层的厚度是4纳米以及所述下边缘第一氮化间隔层的厚度是3纳米。另一方面,所述非对称的间隔层也是沿着所述主动区的侧壁形成。所述非对称的间隔层(如图5所示)的结构和上述相关的步骤是本发明的第一主要技术特征,其称为在沟槽(或渠道)的两对称边缘上的非对称的间隔层(asymmetric spacers on two symmetrical edges of a trench or a canal,asose)。

249.在步骤118中,如图6所示,沉积金属层602(或需要承受后续工艺条件的导电材料)以填满沟槽210且通过所述化学机械平坦化技术平坦化以使金属层602的顶部和衬垫氮化层206的顶部平齐(如图6所示)。另外,在本发明的一实施例中,金属层602可以是钨(其缩写为w)。

250.在步骤120中,如图7所示,沉积光刻胶层702以覆盖所述下边缘第一氮化间隔层和所述第一氧化间隔层,但暴露所述下边缘第一氮化间隔层和所述第一氧化间隔层对应所述主动区的末端的两边缘。

251.在步骤122中,如图8所示,蚀刻对应所述主动区的末端的金属层602直到暴露第一氧化/sti层504的顶部以分隔所述多条导线(也就是也就是金属层602)。

252.在步骤124中,如图9(a)所示,在移除光刻胶层702之后,回蚀沟槽210内的金属层602至合理厚度以形成硅表面下位线(或硅表面下导线)902,其中硅表面下位线902的顶部是远低于水平硅表面208(例如,硅表面下位线902的厚度约为40纳米)。另外,如图9(a)所示,硅表面下位线902位于所述浅沟槽隔离的顶部之上以及硅表面下位线902的两侧壁分别受限于所述非对称间隔层(也就是所述下边缘第一氮化间隔层和所述第一氧化间隔层)。另外,图9(a)是沿着如图9(b)所示的y方向的切割线的剖面图。

253.在步骤126,如图10(沿着如图9(b)所示的y方向的切割线的剖面图)所示,第二氧化层1002(也称为cvd

‑

sti

‑

oxide2)需要有足够的厚度以填充硅表面下位线902上方的沟槽210,然后通过所述化学机械平坦化技术抛光第二氧化层1002以保留第二氧化层1002的部分,其中第二氧化层1002被保留的部分的顶部和衬垫氮化层206的顶部平齐,以及覆盖所述下边缘第一氮化间隔层和所述第一氧化间隔层。如图10所示,步骤126可使硅表面下位线902(也就是互连导线)嵌入至沟槽210内所有绝缘体(也就是隔离区)中且受限于所述所有绝缘体(之后硅表面下位线902将连接至所述动态随机存取存储器存储单元阵列的存取晶体管的汲极),其中如图10所示的结构称为绝缘体包围的硅表面下位线(underground bit

‑

lines,ugbl),且所述硅表面下位线(ugbl)是本发明的第二主要技术特征。

254.以下的说明将介绍如何同时通过自对准方法(self

‑

alignment method)形成所述动态随机存取存储器存储单元(1t1c单元)阵列的存取晶体管和字线以及形成字线连接所

述存取晶体管的所有相关栅极结构。如此,所述动态随机存取存储器存储单元(1t1c单元)阵列的存取晶体管的栅极结构和字线将被连接成为一体的金属(例如钨(w))。

255.在步骤128中,如图11(a)所示,首先沉积第三氧化层1102,第二氮化层1104,以及图案化的光刻胶层1106。然后利用蚀刻技术移除第三氧化层1102和第二氮化层1104中的不必要部份。另外,可通过第三氧化层1102和第二氮化层1104的复合层定义晶体管/字线图案(transistor/word line pattern),其中第三氧化层1102和第二氮化层1104的复合层是由垂直于所述主动区方向的方向上的多个条状的第三氧化层1102和第二氮化层1104所组成。因此,如图11(a)和图11(b)所示,用于定义所述存取晶体管和所述字线的纵向(所述y方向)条纹(由第三氧化层1102和第二氮化层1104组成),以及用于定义所述主动区的交叉点方形(cross

‑

point square)将被形成,其中所述主动区是位于两纵向条纹之间的交叉点方形,以及图11(a)是沿着如图11(b)所示的x方向的切割线的剖面图。

256.如图11(b)所示,图11(b)所示的上视图显示了位于衬垫氮化层206和衬垫氧化层204上方的具有第三氧化层1102和第二氮化层1104所组成的纵向条纹的织物状棋盘图案(fabric

‑

like checkerboard pattern),以及也显示了在水平方向(也就是如图11(b)所示的x方向)上的所述主动区和所述浅沟槽隔离。如图11(b)所示,所述主动区允许所述存取晶体管通过一种自对准技术(self

‑

alignment technique)制成。这种用于在一个工艺步骤中制造所述存取晶体管的栅极结构和所述字线的自对准结构的织物状棋盘图案是本发明的第三主要技术特征。

257.在步骤130中,如图12(a)所示,保留光刻胶层1106以蚀刻掉衬垫氮化层206,但保留衬垫氧化层204,以及如图12(b)所示,移除光刻胶层1106和衬垫氧化层204。因此,水平硅表面208(也就是hss)暴露在如图12(b)所示的交叉点方形区域(cross

‑

point square area),其中所述交叉点方形区域对应所述主动区(位于图11(a)和图11(b)所示的交叉点方形)。

258.在步骤132中,如图13所示,通过所述各向异性蚀刻技术蚀刻暴露在所述交叉点方形区域的水平硅表面208以形成凹槽(例如所述u形凹槽),其中所述u形凹槽是用于形成所述存取晶体管的u形通道1302,以及例如从水平硅表面208开始算起所述u形凹槽的垂直深度可达约60纳米,也就是说如图13所示,u型通道1302是位于水平硅表面208之下。因为所述存取晶体管的u形凹槽被暴露出来,所以可通过合理设计的硼(p型掺杂剂)的浓度来掺杂所述u形凹槽内的u形通道1302以实现通道掺杂,其中所述通道掺杂是为了使所述存取晶体管在随后的高介电常数金属

‑

栅极结构(high

‑

k metal

‑

gate structure)形成之后具有所需的阈值电压(threshold voltage)。之后在所述u形凹槽的底部和侧壁形成高介电常数绝缘层1304,其中高介电常数绝缘层1304是作为所述存取晶体管的栅极介电层,其中如图13所示,高介电常数绝缘层1304的两边缘的顶部是高于水平硅表面208。然后选择适合于字线导电率并且可以实现所述存取晶体管的目标功函数(targeted work

‑

function)性能的栅极材料1306,以使所述存取晶体管具有较低的阈值电压(选择栅极材料1306的目的是将升压后的字线电压降到尽可能低但仍能提供足够的驱动力以完成用以恢复(restore)所述电容(1c)的足够电荷量,以及在另一方面是有利于更快的电荷转移以进行信号检测)。

259.栅极材料1306足以填充两相邻纵向条纹(由第三氧化层1102和第二氮化层1104组成)之间的所述u形凹槽(如图13所示)。然后栅回蚀极材料1306以产生夹在所述两相邻纵向

条纹(由第三氧化层1102和第二氮化层1104组成)之间的纵向(所述y方向)字线。例如,栅极材料1306可以是用以形成所述高介电常数金属

‑

栅极结构的钨(w),其中如果u型通道1302具有合适的掺杂浓度,则所述高介电常数金属

‑

栅极结构可允许所述存取晶体管具有所需的较低阈值电压。

260.本发明所公开的具有u形通道1302的所述存取晶体管(以下称为u型晶体管)是不同于现有技术所公开的常用于埋入式字线设计(buried word line design)中的嵌入式晶体管(recessed transistor)。所述u型晶体管的主体沿着所述y方向(也就是通道宽度方向)的两边被第二氧化层1002(也就是cvd

‑

sti

‑

oxide2)限制住,以及所述u型晶体管的通道长度包含u形通道1302对应所述u型晶体管的漏极的一边的深度,u形通道1302的底部的长度,以及u形通道1302对应所述u型晶体管的源极的一边的深度。例如,如果所述u形凹槽的垂直深度为60纳米以及所述u形凹槽沿着所述x方向(也就是通道长度方向)的开口为7纳米,则所述u型晶体管的u形通道1302的总长度约可达127纳米。相较之下,所述嵌入式晶体管的通道长度必须更多地取决于所述嵌入式晶体管的栅极材料被嵌入的深度以及所述嵌入式晶体管的源极结和漏极结所形成的深度。

261.由于所述u型晶体管和所述嵌入式晶体管之间的结构差异,所以可以更好地控制u形通道1302的通道长度(尤其特别的是当u形通道1302的通道长度不需要取决于所述u型晶体管的栅极结构高度时)。另外,因为水平硅表面208是固定的,所以所述u型晶体管的漏极和源极的掺杂浓度分布具有更少的组件设计参数变化(device

‑

design

‑

parameter variation)而可控性更高,这将在之后有关如何完成所述u型晶体管的漏极和源极时有更详细地描述。另外,在所述纵向方向上,通过所述两相邻纵向条纹(由第三氧化层1102和第二氮化层1104组成)之间的自对准同时形成所述u型晶体管的栅极结构和所述字线是一种使所述字线不会位在水平硅表面208下方的方式,其中不会位在水平硅表面208下方的所述字线具有与现有技术中常用的埋入式字线相当不同的设计与性能参数。另外,如图13所示,通过回蚀使所述字线(也就是栅极材料1306)的高度被设计成低于所述复合层(由第三氧化层1102和第二氮化层1104组成)的高度。另外,所述u型晶体管的栅极结构自对准地连接到所述字线的结构设计是本发明的第四主要技术特征。

262.在步骤134中,如图14所示,沉积第三氮化层1402,以及随后沉积第四氧化层1404,其中第三氮化层1402和第四氧化层1404堆叠在一起使其总厚度足以填充所述两相邻纵向条纹(由第三氧化层1102和第二氮化层1104组成)之间的空缺。然后,回蚀(或抛光)第四氧化层1404以使第四氧化层1404的顶部平齐第二氮化层1104的顶部从而直接在所述字线(也就是栅极材料1306)的正上方形成由第四氧化层1404和第三氮化层1402组成的复合层。

263.在步骤136中,如图15所示,通过所述各向异性蚀刻技术蚀刻掉第二氮化层1104,以及保留所述字线之上的第四氧化层1404/第三氮化层1402。然后也通过所述各向异性蚀刻技术蚀刻掉第三氧化层1102以暴露衬垫氮化层206。所述栅极结构(例如,第四氧化层1404/第三氮化层1402/栅极材料1306)同时实现了在所述u形凹槽内的所述u型晶体管的栅极结构以及在所述纵向方向(也就是所述y方向)上的所述字线。

264.在步骤138中,如图16所示,移除衬垫氮化层206以留下衬垫氧化层204。回蚀第二氧化层1002(也就是cvd

‑

sti

‑

oxide2)以使第二氧化层1002的顶部平齐衬垫氧化层204的顶部。

265.在步骤140中,如图16所示,沉积第四氮化层1602以及通过所述各向异性蚀刻技术蚀刻第四氮化层1602以生成具有精心设计的厚度的第四氮化间隔层。然后沉积第五氧化层1604以及通过所述各向异性蚀刻技术蚀刻第五氧化层1604以生成第五氧化间隔层。然后沉积第一多晶硅层1606(其中第一多晶硅层1606是固有未掺杂的(intrinsic and undoped))在如图16所示的整个表面上方。然后通过所述各向异性蚀刻技术蚀刻第一多晶硅层1606创造出第一多晶硅间隔层以制作环绕字线(例如第一字线wordline

‑

1,第二字线wordline

‑

2,第三字线word line

‑

3)。因此,总结而言,所述第一多晶硅间隔层是在所述第五氮化间隔层之外,所述第五氧化间隔层是在所述第四氮化间隔层之外,以及上述所有间隔层都围绕且沿着所述栅极结构(例如,第四氧化层1404/第三氮化层1402/栅极材料1306)。

266.如图16,17所示,为了方便和清楚地描述具有所述字线和所述位线的所述动态随机存取存储器存储单元阵列,位于中心的字线标注为第一字线wordline

‑

1(对应存取晶体管aq1),比邻第一字线wordline

‑

1左边的字线标注为第二字线wordline

‑

2(对应比邻存取晶体管aq1左边的存取晶体管aq2),以及衬垫氧化层204仍然覆盖第一字线wordline

‑

1和第二字线wordline

‑

2之间作为所述漏极的区域以保留给存取晶体管aq1的第一漏极drain

‑

1以及存取晶体管aq2的第二漏极第二漏极drain

‑

2。比邻第一字线wordline

‑

1右边的字线标注为第三字线wordline

‑

3(对应比邻存取晶体管aq1右边的存取晶体管aq3),以及衬垫氧化层204仍然覆盖第一字线wordline

‑

1和第三字线wordline

‑

3之间作为所述源极的区域以保留给存取晶体管aq1的第一源极source

‑

1以及存取晶体管aq3的第三源极source

‑

3。

267.在步骤142中,如图17所示,沉积旋涂电介质1702,其中旋涂电介质1702的厚度足以填充在上述字线(第一字线wordline

‑

1、第二字线wordline

‑

2和第三字线wordline

‑

3)之间的空缺(对应所述漏极的区域和作为所述源极的区域),之后通过所述化学机械平坦化技术抛光旋涂电介质1702以使旋涂电介质1702的顶部与第四氧化层1404的的顶部平齐。然后通过所述各向异性蚀刻技术蚀刻第一多晶硅层1606的上半部。之后沉积第一氧化帽层1704以填充所述第一多晶硅间隔层的顶部上方的空缺,然后通过所述化学机械平坦化技术平坦化第一氧化帽层1704以使第一氧化帽层1704的顶部与第四氧化层1404的的顶部平齐。

268.在步骤144中,如图18所示,蚀刻掉旋涂电介质1702,其中旋涂电介质1702具有远高于热生成氧化层和沉积氧化层的蚀刻速率,所以在蚀刻掉旋涂电介质1702时,热生成氧化层和沉积氧化层仍可保持良好状态。然后沉积第五氮化层1802在如图18所示的整个表面上方。

269.在步骤146中,如图19所示,沉积旋涂电介质1902,其中旋涂电介质1902的厚度足以填充在上述字线(第一字线wordline

‑

1、第二字线wordline

‑

2和第三字线wordline

‑

3)之间的空缺,之后通过所述化学机械平坦化技术抛光旋涂电介质1902以使旋涂电介质1902的顶部与第五氮化层1802的的顶部的的顶部平齐。然后沉积光刻胶1904在平齐的表面上以覆盖对应所述漏极(第一漏极drain

‑

1以及第二漏极第二漏极drain

‑

2)的旋涂电介质1902,以及暴露对应所述源极(第一源极source

‑

1以及第三源极source

‑

3)的旋涂电介质1902做后续处理。然后围绕上述字线(第一字线wordline

‑

1、第二字线wordline

‑

2和第三字线wordline

‑

3)的第五氮化层1802可作为自对准掩膜(self

‑

alignment mask)以移除对应所述漏极(第一漏极drain

‑

1以及第二漏极第二漏极drain

‑

2)的旋涂电介质1902。当所需的图案已转移到旋涂电介质1902后,所有不必要的光刻胶均被清除,从而使旋涂电介质1902平

坦化(如图19所示)。

270.在步骤148中,如图20所示,蚀刻掉暴露的第五氮化层1802以及位在两条字线(第一字线wordline

‑

1和第三字线wordline

‑

3)之间的所述源极的区域的中心的衬垫氧化层204以暴露出水平硅表面208。因为被暴露的水平硅表面208是位于存取晶体管aq1的第一源极source

‑

1和存取晶体管aq3的第三源极source

‑

3之间,所以在第一源极source

‑

1和第三源极source

‑

3之间的水平硅表面208称为水平硅表面hss

‑

1/3。如图20所示,在第一字线wordline

‑

1和第二字线wordline

‑

2之间的水平硅表面hss

‑

1/2是作为第一漏极drain

‑

1(也就是存取晶体管aq1的漏极)以及第二漏极drain

‑

2(也就是存取晶体管aq2的漏极)的区域,以及也作为垂直连接存取晶体管aq1、aq2至硅表面下位线902的区域。另外,在第一字线wordline

‑

1的右边,在第一字线wordline

‑

1和第三字线wordline

‑

3之间的水平硅表面hss

‑

1/3是作为第一源极source

‑

1(也就是存取晶体管aq1的源极)以及第三源极source

‑

3(也就是存取晶体管aq3的源极)的区域,但是因为第一源极source

‑

1和第三源极source

‑

3将分别连接至单元存储节点csn1、csn3,所以第一源极source

‑

1和第三源极source

‑

3必须是分开无法连接。

271.另外,总结而言,以上所述光刻掩模技术是用于覆盖水平硅表面hss

‑

1/2,但是所述光刻掩模技术所使用的掩模并不是关键的掩模,其功能仅是让处理水平硅表面hss

‑

1/3的工艺与处理水平硅表面hss

‑

1/2的工艺分开。如上所述,沉积旋涂电介质1902的厚度须足以形成光滑的表面形貌,然后沉积光刻胶1904作为掩模材料以保护覆盖所述漏极的旋涂电介质1902但曝露所述源极。另外,使用旋涂电介质1902是因为旋涂电介质1902具有很高的蚀刻速率,可以在不损害其他现有材料的情况下将其去除,并且旋涂电介质1902可以抵抗除光刻胶以外的其他热工艺。

272.如图20所示,通过所述各向异性蚀刻挖掘在水平硅表面hss

‑

1/3(对应所述源极的区域的中心)下方的硅材料以产生孔洞hole

‑

1/3,其中孔洞hole

‑

1/3的两对边(未绘示于图20)被所述下边缘第一氮化间隔层和所述第一氧化间隔层围绕以及孔洞hole

‑

1/3的另外两对边被基板202围绕。

273.在步骤150中,如图21所示,移除光刻胶1904,以及热生成第七氧化层2102以填充孔洞hole

‑

1/3,其中因为第五氮化层1802上不会有氧化物的生长,所以第七氧化层2102只会部分生长在没有被第五氮化层1802覆盖的第一氧化帽层1704的顶部上。另外,填充孔洞hole

‑

1/3的第七氧化层2102称为第七氧化物插销(oxide

‑

7plug),其中所述第七氧化物插销具有光滑表面,且其高度与衬垫氧化层204的顶部平齐。

274.在步骤152中,如图22所示,沉积旋涂电介质层2202,其中旋涂电介质层2202须足够厚以填充到在孔洞hole

‑

1/3中的第七氧化层2102顶部上方的空缺中,然后通过所述化学机械平坦化技术移除旋涂电介质层2202的顶部材料直到旋涂电介质层2202的顶部与第五氮化层1802的顶部平齐。

275.在步骤154中,如图23所示,沉积光刻胶2302覆盖对应所述源极的区域以及暴露出上述为所述漏极保留的区域,其中在步骤154中所使用的掩模并不是关键的掩模,其功能仅是让处理水平硅表面hss

‑

1/3的工艺与处理水平硅表面hss

‑

1/2的工艺分开。然后暴露的旋涂电介质1902、暴露的第五氮化层1802以及暴露的衬垫氧化层204被移除以露出水平硅表面(也就是水平硅表面hss

‑

1/2)。然后通过所述各向异性蚀刻技术挖掘和移除对应水平硅

表面hss

‑

1/2的硅材料以产生孔洞hole

‑

1/2,其中孔洞hole

‑

1/2的两对边被基板202围绕,孔洞hole

‑

1/2的第三边(未绘示于图23)被所述下边缘第一氮化间隔层围绕,孔洞hole

‑

1/2的第四边(未绘示于图23)被所述第一氧化间隔层围绕,以及孔洞hole

‑

1/2的第三边和第四边进一步由第二氧化层1002(也就是cvd

‑

sti

‑

oxide2)在外部限制。

276.在步骤156中,如图24所示,移除光刻胶2302,然后热生成第八氧化层2402热生成以产生第八氧化间隔层,其中孔洞hole

‑

1/2的四个侧壁中除了第三侧壁被所述下边缘第一氮化间隔层覆盖之外,所述第八氧化间隔层覆盖孔洞hole

‑

1/2的四个侧壁中的其余三个侧壁和孔洞hole

‑

1/2的底部。另外,第八氧化层2402部分生长在第一氧化帽层1704的顶部。图25是说明所述动态随机存取存储器存储单元阵列沿着所述y2方向的剖面图的示意图,其中所述y2方向沿着孔洞hole

‑

1/2的中心延伸并垂直于所述x方向。另外,如图25所示,所述主动区被夹在第二氧化层1002(cvd

‑

sti

‑

oxide2),硅表面下位线902(ugbl),所述第一氧化间隔层,以及所述下边缘第一氮化间隔层之间。

277.在步骤158中,如图26、27所示,通过所述各向同性蚀刻技术(isotropic etching technique)移除孔洞hole

‑

1/2内所述第三侧壁上的所述下边缘第一氮化间隔层,以及同时移除第五氮化层1802(如图27所示,因为所述下边缘第一氮化间隔层非常薄,所以所述各向同性蚀刻技术不会损害水平硅表面208之上的其他结构,且也不会移除孔洞hole

‑

1/2内的第八氧化层2402)。

278.在步骤160中,如图28所示,沉积金属层(例如钨)2802,其中金属层2802的厚度足以填充孔洞hole

‑

1/2,然后通过所述各向同性蚀刻技术蚀回在水平硅表面208上的金属层2802以在孔洞hole

‑

1/2内留下钨插销。如图28所示,所述钨插销通过孔洞hole

‑

1/2的第三侧壁上的开口连接硅表面下位线902(ugbl),其中孔洞hole

‑

1/2的第三侧壁原来是被所述下边缘第一氮化间隔层覆盖。然后沉积第六氮化层2804以及通过所述各向异性蚀刻技术蚀刻创造出所述第六氮化间隔层,其中所述第六氮化间隔层围绕对应所述漏极的所述第一多晶硅间隔层。

279.在步骤162中,如图29所示,回蚀所述钨插销在水平硅表面208下方的上半部,其中如图30所示,在孔洞hole

‑

1/2内,所述钨插销是通过其侧壁连接至硅表面下位线902(ugbl)的侧壁。

280.在步骤164中,如图31所示,通过所述各向异性蚀刻技术移除适量的第八氧化层2402的上半部,导致所述第八氧化间隔层的高度因此低于所述钨插销的高度。另外,如图31所示,第一氧化帽层1704的部分也可被蚀刻掉。

281.在步骤166中,如图32所示,通过选择性外延生长(selective epitaxy growth,seg)技术从两个暴露的硅边缘(邻近以及在第八氧化层2402和所述钨插销的上方)横向生长n 原位掺杂硅层3202,如此导致连接到孔洞hole

‑

1/2的两侧上的水平硅表面208的项链型(necklace

‑

type)导电n 硅漏极(称为n 硅漏环(n silicon drain

‑

collar))可分别作为存取晶体管aq1的第一漏极drain

‑

1和存取晶体管aq2的第二漏极drain

‑

2,也可作为在硅表面下位线902(ugbl)和存取晶体管aq1、aq2之间的导电桥(也就是桥接触)。

282.在步骤168中,如图33所示,在n 硅漏环上局部热生成具有良好设计厚度的第九氧化层3302以盖住水平硅表面hss

‑

1/2(且第九氧化层3302可能覆盖第一氧化帽层1704)。在硅表面下位线902(ugbl)和第一漏极drain

‑

1(或第二漏极drain

‑

2)之间形成所述导电桥的

上述连接方法是本发明的第六主要技术特征,其中第一漏极drain

‑

1和第二漏极drain

‑

2是氧化物覆盖(oxide

‑

capped)的n 漏极。

283.在步骤170中,如图34所示,通过所述各向同性蚀刻技术移除所有的旋涂电介质层(也就是旋涂电介质层和旋涂电介质层2202),以及移除第五氮化层1802和第六氮化层2804(其中第九氧化层3302覆盖第一氧化帽层1704的部分也可能被移除)。另外,图35是说明所述动态随机存取存储器存储单元阵列的上视图的示意图,其中图35特别显示了所述字线(第一字线wordline

‑

1,第二字线wordline

‑

2,第三字线wordline

‑

3),硅表面下导线(ugbl),存取晶体管aq1、aq3的所述源极(第一源极source

‑

1和第三源极source

‑

3),以及存取晶体管aq1、aq2的所述漏极(第一漏极drain

‑

1和第二漏极drain

‑

2)的几何排列。

284.在步骤171中,如图36所示,沉积和回蚀金属层(例如钨)3602以使蚀刻后的金属层3602具有精心设计的高度,其中蚀刻后的金属层3602的高度略低于所述复合层(由第四氧化层1404和第三氮化层1402组成)的高度。另外,如图36所示,在空缺中的钨支柱被称为钨缓冲墙(w

‑

buffer

‑

walls,wbw)。

285.在步骤172中,如图37所示,移除在所述第一多晶硅间隔层上方的第一氧化帽层1704,然后蚀刻掉所述第一多晶硅间隔层以及所述第一多晶硅间隔层下方的衬垫氧化层204。如此,分别暴露出对应所述源极和所述漏极的水平硅表面208(称为用于源极和漏极的晶种硅表面区(the seeding hss area for source and drain regions,shar))。

286.在步骤173中,如图38所示,通过所述用于源极和漏极的晶种硅表面区作为晶种,利用所述选择性外延生长技术在水平硅表面208上方的垂直方向分别生成源极电极eh

‑

1s和漏极电极eh

‑

1d,其中源极电极eh

‑

1s和漏极电极eh

‑

1d生长到特定的高度。因为源极电极eh

‑

1s和漏极电极eh

‑

1d可通过所述用于源极和漏极的晶种硅表面区作为晶种良好地逐渐生成,所以源极电极eh

‑

1s和漏极电极eh

‑

1d可以是纯硅材料而不是多晶或非晶硅材料。源极电极eh

‑

1s和漏极电极eh

‑

1d沿着所述x方向的左侧壁和右侧壁分别被所述钨缓冲墙和所述第五氧化间隔层围绕。虽然沿着所述y方向的其他两个侧壁是开放的,但是第二氧化层1002(cvd

‑

sti

‑

oxide2)不能提供用于生长选择性外延硅的晶种功能。因此,选择性外延硅的生长应导致一些横向过度生长的纯硅材料停止在第二氧化层1002(cvd

‑

sti

‑

oxide2)的边缘,并且不可能引起相邻电极的连接(源极电极eh

‑

1s和漏极电极eh

‑

1d的生成可参考参考文件中有关硅材料的选择性外延生长的一些实验结果:“a buried trench dram cell using a self

‑

aligned epitaxy over trench technology,”1988ieee iedm dig.tech.papers,pp.588

‑

591,n.lu,et al,其中本发明可引用所述参考文件的全部内容;尤其是如下将要描述的一种新的实现源电极eh

‑

1s和漏电极eh

‑

1d的逐步生长方法)。

287.完成源极电极eh

‑

1s和漏极电极eh

‑

1d的新工艺设计描述如下:

288.(1)通过所述用于源极和漏极的晶种硅表面区(shar)作为晶种利用所述选择性外延生长技术生成源极电极eh

‑

1s和漏极电极eh

‑

1d时,重要的是在硅生长过程中设计合适的n 原位掺杂浓度(in

‑

situn

‑

type doping concentration)以实现所述存取晶体管的通道区的适当界面电导(其中所述界面电导分别包含位于所述栅极介电层(高介电常数绝缘层1304)正下方的水平硅表面208的电导,位于所述第四氮化间隔层/所述第五氧化间隔层下方的水平硅表面208的电导,以及位于源极电极eh

‑

1s或导电电极eh

‑

1d下方的水平硅表面208的电导)以实现低漏电流,特别是栅极引起的漏极泄漏(gate induced drain leakage,

gidl),漏极引起的势垒降低(drain induced barrier lowering,dibl),由于短通道引起的次阈值泄漏(sub

‑

threshold leakage due to the short

‑

channel effect),以及结泄漏(junction leakages)等等。

289.(2)在步骤174中,如图39所示,通过所述各向同性蚀刻技术蚀刻掉所述第五氧化间隔层以在所述第四氮化间隔层和漏极电极eh

‑

1d之间(在所述第四氮化间隔层和源极电极eh

‑

1s之间)留下接缝。热生成氧化层

‑

a 3902以覆盖除了漏电极eh

‑

1d(或源电极eh

‑

1s)的第四侧壁外的漏电极eh

‑

1d(或源电极eh

‑

1s)的三个侧壁及顶部(称为氧化

‑

a帽层(oxide

‑

a

‑

cap layer)),其中漏电极eh

‑

1d(或源电极eh

‑

1s)的第四侧壁是由所述钨缓冲墙限制住。如下所述执行这种精细的阶梯状源电极形成工艺的目的是在于因热生成氧化层

‑

a 3902具有非常高质量的二氧化硅到硅电极键而能确保实现源极电极eh

‑

1s的顶部(或漏极电极eh

‑

1d的顶部)具有高性能的氧化硅界面(其中毫无疑问地由所述选择性外延生长工艺衍生出的非晶态或低品质的硅材料可能会降低硅源极电极的品质从而不是造成降低的载子迁移率(导致当所述存取晶体管开启时可能无法传送足够的开启电流(on

‑

current)),或造成当所述存取晶体管关闭时可能会增加漏电流的大量缺陷)。然后通过所述各向异性蚀刻技术蚀刻氧化层

‑

a3902的帽盖部分以留下部分的氧化层

‑

a 3902存在于所述第四氮化间隔层源极电极eh

‑

1s之间(或存在于所述第四氮化间隔层和漏极电极eh

‑

1d之间)。

290.(3)在步骤175中,如图40所示,通过利用源极电极eh

‑

1s和漏极电极eh

‑

1d暴露的硅表面作为高品质的硅晶种执行第二次选择性外延生长以分别生成源极电极eh

‑

2s和漏极电极eh

‑

2d。而在执行第二次选择性外延生长的过程中,为了在源极电极eh

‑

2s(或漏极电极eh

‑

2d)和之后制作的堆叠式储存电容(stacked storage capacitor,ssc)的信号电极之间的低阻抗连接做准备,可在源极电极eh

‑

2s和漏极电极eh

‑

2d中实现良好设计的n 原位重掺杂浓度。另外,源极电极eh

‑

1s和源极电极eh

‑

2s的结合称为源极电极eh

‑

1 2s(同样地,漏极电极eh

‑

1d和漏极电极eh

‑

2d的结合称为漏极电极eh

‑

1 2d)。另外,以源极电极eh

‑

1 2s为例,如图40所示,源极电极eh

‑

1 2s的上半部(也就是源极电极eh

‑

2s)有一些高品质的特性,例如源极电极eh

‑

2s的一个侧壁的n 掺杂硅材料直接毗邻所述第四氮化间隔层,对应源极电极eh

‑

2s的所述侧壁的一个相反方向的侧壁毗邻所述钨缓冲墙,以及源极电极eh

‑

2s的其余两个侧壁沿所述纵向字线在所述y方向上敞开。另外,源极电极eh

‑

1 2s(或漏极电极eh

‑

1 2d)的高度是被良好设计以低于所述第四氮化间隔层的高度。

291.总结而言,源极电极eh

‑

1 2s的下半部(源极电极eh

‑

1s)具有适当的n 掺杂浓度以在垂直于水平硅表面208(或用于源极和漏极的晶种硅表面区(shar))方向上形成自对准的n对p结(n

‑

to

‑

p junction),其中所述n对p结建立水平通道连接至所述存取晶体管的栅极结构下方的通道1302(同样也适用于在通道1302的另一侧的漏极电极eh

‑

1 2d)。以n 重掺杂浓度生成源极电极eh

‑

1 2s的上半部(漏极电极eh

‑

2s)从而完成自对准且垂直的低阻抗连接至所述堆叠式储存电容的信号电极(同样也适用于漏极电极eh

‑

1 2d)。因为源极电极eh

‑

1 2s(或漏极电极eh

‑

1 2d)是通过所述选择性外延生长技术生成,所以源极电极eh

‑

1 2s(或漏极电极eh

‑

1 2d)中的掺杂浓度可轻易地控制,例如逐渐增加或减少所述掺杂浓度,逐步增加或减少所述掺杂浓度等等。此外,不需要使用离子注入进行掺杂。在步骤176中,如图41所示,蚀刻掉在整个晶圆表面上的所述钨缓冲墙(不会损害整个晶圆表面上的其他材料以及嵌入在表面氧化物层和表面氮化物层下面作为保护层的其他一些材料)。

growing storage

‑

electrode tower,sbset)),其中所述信号电极的基础(也就是源极电极lgs

‑

2s和漏极电极lgs

‑

2d)连接到源极电极eh

‑

2s和漏极电极eh

‑

2d以及提供最好的晶种以进一步将硅生长成高的信号电极。

297.如图46所示,在漏极电极lgs

‑

2d和源极电极lgs

‑

2s(或sbset)形成后,所述第一金属对电极板和壁(mcepw

‑

1)除了漏极电极lgs

‑

2d和源极电极lgs

‑

2s(或sbset)之外,分别在源极电极eh

‑

1 2s和漏极电极eh

‑

1 2d的顶部上方覆盖high

‑

k

‑

cap

‑

1和其他区域。在步骤182中,如图47所示,因为晶圆表面的其余部分被所述复合字线上方的第三氮化层1402和所述第一金属对电极板和壁覆盖,所以只能在所述储存电极塔的晶种基础(sbset)上方热生成氧化层

‑

b 4702。然后沉积和回蚀第十氧化层4704使其具有平坦的平面(如图47所示)。

298.在步骤183中,如图48所示,利用所述光刻掩膜技术沉积光刻胶层4802以覆盖氧化层

‑

b 4702相邻源极电极lgs

‑

2s的部分和源极电极eh

‑

2s的顶部上方的high

‑

k

‑

cap

‑1‑

source(如图42所示,high

‑

k

‑

cap

‑1‑

source是第一高介电常数绝缘层4202的部分),但暴露出三个其他区域分别为漏极电极eh

‑

2d的顶部上方的high

‑

k

‑

cap

‑1‑

drain(如图42所示,high

‑

k

‑

cap

‑1‑

drain也是第一高介电常数绝缘层4202的部分),在漏极电极eh

‑

2d的顶部上方的所述第一金属对电极板和壁(mcepw

‑

1),以及相邻存取晶体管aq1和存取晶体管aq2的漏极电极lgs

‑

2d的侧面的硅晶种区的顶部上方的氧化层

‑

b 4702。

299.在步骤184中,如图49所示,部分蚀刻在漏极电极eh

‑

2d的顶部上方的所述第一金属对电极板和壁(mcepw

‑

1)以形成所述钨插销(称为tungsten

‑

a4902),以及通过一些专门设计的蚀刻技术蚀刻掉部分曝露的第一高介电常数绝缘层4202以形成第一高介电常数绝缘间隔层a 4904,其中第一高介电常数绝缘间隔层a 4904的高度和tungsten

‑

a 4902的高度平齐,步骤184会导致暴露漏极电极eh

‑

1 2d的上半部,以及漏极电极eh

‑

1 2d的上半部具有漏极电极暴露的硅材料。

300.在步骤185中,如图50所示,通过所述各向异性蚀刻技术蚀刻掉漏极电极eh

‑

2d的上半部在所述储存电极塔的晶种基础(sbset)的底部边缘下方的硅材料。然后移除光刻胶4802以及在漏极电极eh

‑

2d的剩余部分的顶部上方热生成氧化层

‑

c 5002,其中氧化层

‑

c 5002是为了形成绝缘层以避免从漏极电极eh

‑

2d到所述储存电极塔的晶种基础之间的任何电性连接(因为在漏极电极eh

‑

2d顶部形成开口部分以暴露出n 掺杂硅材料后,所述n 掺杂硅材料可被热氧化以产生高品质的二氧化硅膜(氧化层

‑

c 5002),其中氧化层

‑

c 5002可完全密封从漏极电极eh

‑

2d到所述储存电极塔的晶种基础之间的任何可能的连接。之后沉积和回蚀氧化层

‑

c1 5004以使氧化层

‑

c1 5004的高度和氧化层

‑

b4702的高度平齐。

301.在步骤186中,如图51所示,除了被氧化层

‑

c1 5004保护的tungsten

‑

a 4902之外,移除暴露的金属层4302(所述第一金属对电极板和壁(mcepw

‑

1))。

302.在步骤187中,如图52所示,通过所述各向异性蚀刻技术蚀刻掉在所有平面上暴露的第一高介电常数绝缘层4202,但是留下所述第一高介电常数绝缘间隔层(也就是第一高介电常数绝缘层4202的垂直间隔层部分4206)。

303.在步骤188中,如图53所示,沉积旋涂电介质层5302以填充在所述第七氧化物插销上方的空缺中,然后回蚀旋涂电介质层5302使其具有平坦的表面。

304.在步骤189中,如图54所示,通过所述各向异性蚀刻技术蚀刻氧化层

‑

b4702,第十氧化层4704,以及氧化层

‑

c1 5004在所述储存电极塔的晶种基础的高度上方的部分以曝露

出所述储存电极塔的晶种基础(sbset),然后蚀刻掉旋涂电介质层5302。

305.在步骤190中,如图55所示,通过所述储存电极塔的晶种基础(sbset)以及所述eh

‑

2电极(也就是源极电极eh

‑

2s)的上半部暴露的硅材料作为晶种,利用所述选择性外延生长技术长出足够高的n 原位重掺杂硅塔5502,其中所述n 原位重掺杂硅塔5502可称为储存电容的信号塔存储电极(signal

‑

tower storage electrode of the storage capacitor,stsec

‑

1)。

306.在步骤191中,如图56所示,形成覆盖包含n 原位重掺杂硅塔5502(stsec

‑

1)的所有侧壁和顶部的第二高介电常数绝缘层5602(例如通过原子层沉积生长技术(atomic layer deposition(ald)growth technique),其中第二高介电常数绝缘层5602不允许从暴露的n 原位重掺杂硅塔5502(stsec

‑

1)到稍后即将形成的金属对电极板之间的任何可能的电连接或漏电流机制。

307.在步骤192中,如图57所示,沉积金属(例如钨)层5702,其中金属层5702将所有所述储存电容的信号塔存储电极(stsec

‑

1)的侧壁和水平硅表面208上的其他山谷状(valley

‑

like)的区域包裹成一个平坦的高原,且被称为第二金属对电极板和壁(mcepw

‑

2)。所述第二金属对电极板和壁(mcepw

‑

2)不仅可以用作偏置在恒定电压电平(例如half

‑

vcc)的所述存储电容的对电极板,而且还可以用作金属屏蔽板像金属散热器一样实现更好的散热,并因为电场可以在电容器板上更均匀地分布和屏蔽而进一步降低所述复合字线和所述存取晶体管的栅极结构的噪声或提高所述复合字线和所述存取晶体管的栅极结构的抗噪声能力。图57示出了通过如上所述的自对准技术工艺所实现的新的垂直集成电容覆盖存取晶体管(1c

‑

over

‑

1t)结构的动态随机存取存储器存储单元,其中所述电容覆盖存取晶体管结构的动态随机存取存储器存储单元创建一个世界上最密集且最有效的动态随机存取存储体存储单元结构,所述动态随机存取存储体存储单元结构更有效地使用的平面硅芯片面积,并通过在所述存取晶体管上方重叠塔状(tower

‑

like)储存电容(也称为tot单元,tower

‑

like capacitor over transistor cell)来同时优化所述动态随机存取存储器存储单元的体积集成。因为非常有效地采用了垂直和水平自对准技术来构造和成形所述tot单元内部的基本微结构的几何形状以满足字线、位线、晶体管(包含栅极,源极,漏极,和基板)、存储电容(包含信号电极和对电极板)以及所有在所述微结构之间的接触孔和互连的要求,所以所述tot单元的结构可以保留至少6到10平方单位的优点(每个平方单位是单位长度乘以单位宽度乘以单位宽度,其中每个平方单位是作为可以允许印刷在平坦的硅表面上的最小特征尺寸,例如,即使当最小特征尺寸远小于10纳米时,最小特征尺寸也要5纳米。如此,所述tot单元将可和现有技术所提供的存储单元架构区分开来。

308.另外,在接下来的说明书中可以添加结构增强及其工艺方法的其他发明要点。也就是说如果需要进一步增加储存电容的电容值,则可以使用一些额外的步骤来增加所述储存电容的信号塔存储电极(stsec

‑

1)的高度。在步骤193中,从图58所示的结构开始,回蚀所述第二金属对电极板和壁(mcepw

‑

2)以使其高度低于存储电极(也就是stsec

‑

1)的高度。然后通过所述各向异性蚀刻技术蚀刻掉第二高介电常数绝缘层5602在n 原位重掺杂硅塔5502的顶部上方的部分以及仅保留第二高介电常数绝缘层5602围绕n 原位重掺杂硅塔5502的部分。

309.在步骤194中,如图59所示,通过在n 原位重掺杂硅塔5502的顶部上方暴露的硅材

料作为晶种,利用所述选择性外延生长技术长出更高的n 原位重掺杂硅塔5902(称为stsec

‑

2)以作为所述存储电容的信号电极。然后形成覆盖包含n 原位重掺杂硅塔5902(stsec

‑

2)的所有侧壁和顶部的第三高介电常数绝缘层5904,其中第三高介电常数绝缘层5904不允许从暴露的n 原位重掺杂硅塔5902(stsec

‑

2)到金属层5702(也就是所述第二金属对电极板和壁(mcepw

‑

2))之间的任何可能的电连接或漏电流机制。

310.在步骤195中,如图60所示,形成光刻胶6002以覆盖除了暴露的第三高介电常数绝缘层5904的边缘区域外的所有存储单元阵列区域。在步骤196中,如图61所示,蚀刻掉暴露的第三高介电常数绝缘层5904以暴露出金属层5702(也就是所述第二金属对电极板和壁(mcepw

‑

2))的边缘区域。在步骤197中,如图62所示,移除光刻胶6002。

311.在步骤198中,如图63所示,沉积金属(例如钨)层6302,其中金属层6302将所有n 原位重掺杂硅塔5902(stsec

‑

2)的侧壁和水平硅表面208上的其他山谷状(valley

‑

like)的区域包裹成一个平坦的高原,且被称为第三金属对电极板和壁(mcepw

‑

3)。所述第三金属对电极板和壁(mcepw

‑

3)加上已存在的所述第二金属对电极板和壁(mcepw

‑

2)不仅可以用作偏置在恒定电压电平(例如half

‑

vcc)的所述存储电容的对电极板,而且还可以用作金属屏蔽板像金属散热器一样实现更好的散热,并因为电场可以在电容器板上更均匀地分布和屏蔽而进一步降低所述复合字线和所述存取晶体管的栅极结构的噪声或提高所述复合字线和所述存取晶体管的栅极结构的抗噪声能力。图63示出了新的具有较高的电容以扩大电容值的垂直集成电容覆盖存取晶体管(1c

‑

over

‑

1t)结构的动态随机存取存储器存储单元。

312.总结而言,本发明公开了一种动态随机存取存储器存储单元的新结构,所述新结构不仅缩小了所述动态随机存取存储存储单元的尺寸,而且还提高了在所述动态随机存取存储器操作期间的信噪比。因为所述存储电容是位在所述存取晶体管上方并在很大程度上涵盖了所述存取晶体管,并发明了用于排列和连接所述动态随机存取存储存储单元中的基本微结构的几何形状的垂直和水平自对准技术,所以所述新结构(所述tot单元的结构)可以在即使最小特征尺寸远小于10纳米时仍能保留至少6到10平方单位的优点。

313.此外,在所述新结构中的所述存储电容的金属电极为散热提供了一条有效途径,所以在操作期间所述动态随机存取存储存储单元的温度可相对应地降低,然后较低的温度将同时减少热/操作噪声和所述存储电容的漏电流。另外,所述金属电极进一步围绕穿过所述存取晶体管的所述复合字线,并且被围绕的所述复合字线与位在硅表面下方的硅表面下位线(ugbl)的组合可以有效屏蔽不同字线/位线之间的交叉耦合噪声。如此,在现有技术所公开的动态随机存取存储器存储单元阵列操作时所发生的有问题的模式敏感性问题(problematic pattern sensitivity issue)将可大大减少。

314.另外,良好设计的晶体管结构也可降低栅极引起的漏极泄漏(gidl)电流,以及所述降低的栅极引起的漏极泄漏电流和衍生自较低操作温度的降低电流的结合更可进一步扩大信噪比并实现在所述tot单元的结构中使用较小尺寸的存储电容的可能性,而不会对储存数据的可靠性产生负面影响。

315.此外,本发明所公开的硅表面下位线(ugbl)可以灵活地降低所述硅表面下位线的寄生电阻和寄生电容,所以可以提高所述存储电容和所述硅表面下位线在电荷共享期间的信号灵敏度,从而可以提高所述tot单元的结构的操作速度。

316.综上所述,图64是说明本发明所公开的所述tot单元的结构的示意图,其中图64对

应图63。相较于现有技术所公开的动态随机存取存储器存储单元阵列的结构,当λ等于或小于10纳米时,所述tot单元的结构显示了具有以下可帮助存储单元尺寸实现约6至10平方单位(或6~10λ2)的功能:(1)所述存储电容的信号电极围绕所述存取晶体管,(2)所述对电极板围绕所述存取晶体管以及覆盖整个所述动态随机存取存储器存储单元阵列,(3)所述硅表面下位线位在所述水平硅表面下方以简化所述动态随机存取存储器存储单元阵列的表面形貌,(4)自对准源极电极具有可调的对所述通道边缘的导电率以最小化所述tot单元的漏电流,(5)自对准信号电极从所述源极伸出并骑在所述存取晶体管上方,就像是具有自对准电容塔的马鞍,(6)多数所述存储单元都可通过可靠的材料扩展其特征以及具有足够可靠性和品质的工艺步骤。

317.以上所述仅为本发明的优选实施例而已,并不用于限制本发明,对于本领域的技术人员来说,本发明可以有各种更改和变化。凡在本发明的精神和原则之内,所作的任何修改、等同替换、改进等,均应包含在本发明的保护范围之内。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。