1.本发明涉及信号输出技术,尤其涉及一种具有抗干扰机制的信号输出电路及方法。

背景技术:

2.在芯片中,往往需要设置包含放大器与变压器的信号输出电路,以将信号经过阻抗匹配后放大并且输出。然而在进行芯片的封装时,因为配置上的考虑,电源以及信号输出的线路经常是在同一侧或是彼此接近。放大器的信号输出路径上的信号会经由键合线的耦合产生噪声,直接干扰到电源。

3.进一步地上述的噪声经由共享电源线经由变压器的电压馈入点稳压电容传送至放大器的接地端混和出额外的二次谐波,会增加对信号输出电路的干扰。

技术实现要素:

4.鉴于先前技术的问题,本发明的一目的在于提供一种具有抗干扰机制的信号输出电路及方法,以改善先前技术。

5.本发明的一目的在于提供一种具有抗干扰机制的信号输出电路及方法,藉由较小电路面积的抗干扰电路直接滤除具有基本谐波的耦合信号,大幅提升抗干扰的效率。

6.本发明包含一种具有抗干扰机制的信号输出电路,其一实施例包含:放大器、变压电路以及电源端抗干扰电路。放大器分别通过第一放大器键合线(bond)电性耦接于供应电源以及通过第二放大器键合线电性耦接于接地端,并配置以根据供应电源运作并产生放大输出信号。变压电路包含配置以根据放大输出信号进行阻抗转换以产生变压输出信号的变压器以及配置以对放大器进行二次谐波抑制的稳压电容。电源端抗干扰电路包含:电源端键合线以及电源端抗干扰电容。电源端键合线配置以电性耦接于接地端。电源端抗干扰电容配置以电性耦接于电源端键合线与第一放大器键合线之间,以与电源端键合线共同运作以滤除由变压电路产生的变压输出信号耦合至第一放大器键合线的基本谐波耦合信号。

7.本发明还包含一种具有抗干扰机制的信号输出方法,应用于设置于信号输出电路中,其一实施例包含下列步骤:使放大器根据供应电源运作并产生放大输出信号,其中放大器分别通过第一放大器键合线电性耦接于供应电源以及通过第二放大器键合线电性耦接于接地端;使变压电路包含的变压器根据放大输出信号进行阻抗转换产生变压输出信号以及使变压电路的稳压电容对放大器进行二次谐波抑制;以及使电源端抗干扰电路包含的电源端键合线以及电源端抗干扰电容共同运作以滤除由变压电路产生的变压输出信号耦合至第一放大器键合线的基本谐波耦合信号,且耦合信号具有基本谐波,其中电源端键合线电性耦接于接地端,电源端抗干扰电容电性耦接于电源端键合线与第一放大器键合线之间。

8.有关本发明的特征、实际操作与效果,兹配合图式作优选实施例详细说明如下。

附图说明

9.图1显示本发明的一实施例中,一种具有抗干扰机制的信号输出电路的电路图;

10.图2显示本发明的一实施例中,一种具有抗干扰机制的信号输出电路的电路图;

11.图3显示本发明的一实施例中,一种具有抗干扰机制的信号输出电路的电路图;以及

12.图4显示本发明的一实施例中,一种具有抗干扰机制的信号输出方法的流程图。

具体实施方式

13.本发明的一目的在于提供一种具有抗干扰机制的信号输出电路及方法,以较小电路面积的抗干扰电路直接滤除具有基本谐波的耦合信号,大幅提升抗干扰的效率。

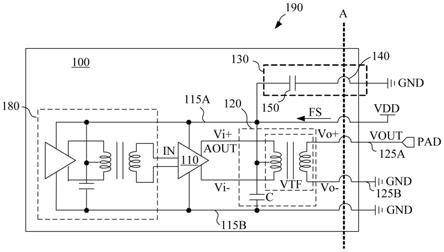

14.请参照图1。图1为本发明的一实施例中,一种具有抗干扰机制的信号输出电路100的电路图。信号输出电路100在一实施例中是设置于1个封装结构190的内部的芯片(未示出)中。在图1中,是以一个虚线a来进行划分,虚线a具有信号输出电路100的一侧是封装结构190的内部,且虚线a的另一侧是封装结构190的外部。

15.信号输出电路100包含:放大器110、变压电路120以及电源端抗干扰电路130。

16.放大器110分别通过第一放大器键合线(bond)115a电性耦接于供应电源vdd以及通过第二放大器键合线115b电性耦接于接地端gnd。其中,第一放大器键合线115a以及第二放大器键合线115b跨接于封装结构190的内外侧,以使放大器110得以电性耦接于封装结构190的外部的供应电源vdd以及接地端gnd。

17.放大器110配置以根据供应电源vdd运作并产生放大输出信号aout。在一实施例中,放大器110电性耦接于一个输入电路180,以自输入电路180接收输入信号in,以将输入信号in进行放大产生放大输出信号aout。

18.变压电路120包含变压器vtf以及稳压电容c。其中,变压器vtf配置以根据放大输出信号aout进行阻抗转换以产生变压输出信号vout,稳压电容c配置以对放大器110进行二次谐波抑制。在一实施例中,变压器vtf包含:输入端vi 以及vi-、输出信号端vo 以及输出接地端vo-。

19.输入端vi 以及vi-配置以接收放大器110的放大输出信号aout。输出信号端vo 配置以通过第一变压电路键合线125a电性耦接于输出接垫pad,以通过第一变压电路键合线125a输出变压输出信号vout至输出接垫pad。输出接地端vo-配置以通过第二变压电路键合线125b电性耦接于接地端gnd。

20.其中,第一变压电路键合线125a以及第二变压电路键合线125b跨接于封装结构190的内外侧,以使变压器vtf得以电性耦接于封装结构190的外部的输出接垫pad以及接地端gnd。

21.当第一放大器键合线115a以及第一变压电路键合线125a以较接近的距离设置时,变压器vtf运作产生的变压输出信号vout容易通过第一变压电路键合线125a耦合至第一放大器键合线115a上产生的基本谐波耦合信号fs。基本谐波耦合信号fs具有基本谐波(fundamentalharmonic),并对第一放大器键合线115a自供应电源vdd接收的电源信号造成干扰。因此,电源端抗干扰电路130将提供抗干扰的机制,以避免基本谐波耦合信号fs的影响。

22.电源端抗干扰电路130包含:电源端键合线140以及电源端抗干扰电容150。

23.电源端键合线140配置以电性耦接于接地端gnd。电源端抗干扰电容150配置以电性耦接于电源端键合线140与第一放大器键合线115a之间。其中,电源端键合线140跨接于封装结构190的内外侧,以使电源端抗干扰电容150得以电性耦接于封装结构190的外部的接地端gnd。

24.在一实施例中,电源端键合线140运作为电感。因此,电源端键合线140与电源端抗干扰电容150共同运作为自振(self-resonate)电路,以滤除基本谐波耦合信号fs,避免对第一放大器键合线115a自供应电源vdd接收的电源信号造成干扰。在一实施例中,电源端键合线140的电感值为l,且电源端抗干扰电容150的电容值为c,电源端键合线140与电源端抗干扰电容150的容感共振频率f0可表示为:

25.f0=1/(2π

×

sqrt(l

×

c))

26.在一实施例中,电源端键合线140与电源端抗干扰电容150的容感共振频率f0相当于基本谐波耦合信号fs的频率,以有效地滤除基本谐波耦合信号fs。

27.请参照图2。图2为本发明一实施例中,一种具有抗干扰机制的信号输出电路200的电路图。类似于图1的信号输出电路100,图2的信号输出电路200包含:放大器110、变压电路120以及电源端抗干扰电路130。其中,图2中的放大器110以及变压电路120的结构与连接关系与图1相同,因此不再赘述。

28.在本实施例中,电源端抗干扰电路130除包含电源端键合线140以及电源端抗干扰电容150,还包含电源端抗干扰电感210。电源端抗干扰电感210与电源端键合线140以及电源端抗干扰电容150共同运作为容感电路,以增加电路设计上的弹性。

29.并且,在一实施例中,包含电源端键合线140、电源端抗干扰电容150以及电源端抗干扰电感210的容感电路的容感共振频率,亦可在适当的电感值与电容值的选择下,相当于基本谐波耦合信号fs的频率,以有效地滤除具有基本谐波耦合信号fs。

30.请参照图3。图3为本发明一实施例中,一种具有抗干扰机制的信号输出电路300的电路图。类似于图1的信号输出电路100,图3的信号输出电路300包含:放大器110、变压电路120以及电源端抗干扰电路130。其中,图3中的放大器110、变压电路120以及电源端抗干扰电路130的结构与连接关系与图1相同,因此不再赘述。

31.在本实施例中,信号输出电路300还包含接地端抗干扰电路310。接地端抗干扰电路310包含接地端键合线320以及接地端抗干扰电容330。

32.接地端键合线320配置以电性耦接于接地端gnd。接地端抗干扰电容330配置以电性耦接于接地端键合线320与第二放大器键合线115b之间。其中,接地端键合线320跨接于封装结构190的内外侧,以使接地端抗干扰电容330得以电性耦接于封装结构190的外部的接地端gnd。

33.因此,接地端抗干扰电路310可如电源端抗干扰电路130一般形成容感电路,滤除变压电路120在第二放大器键合线115b上耦合产生的信号,例如但不限于具有基本谐波与二次谐波的信号。并且,接地端抗干扰电路310亦可如图2的实施例额外设置接地端抗干扰电感(未示出),以与接地端键合线320以及第二放大器键合线115b共同形成容感电路达到抗干扰的目的。

34.在部分技术中,包含放大器以及变压电路的信号输出电路在滤波电路摆设的位置

或是滤除频率上无法有效滤除信号,往往造成二次谐波的产生,且亦可能影响放大器的放大效率。

35.本发明的信号输出电路直接对于基本谐波耦合信号进行滤除,将可大幅提升抗干扰的效率,亦可避免基本谐波耦合信号通过电源线进入前端的输入电路造成其他的二次谐波。并且,直接藉由键合线与电容形成容感电路,亦可进行以较小的电路面积达到抗干扰的目的。

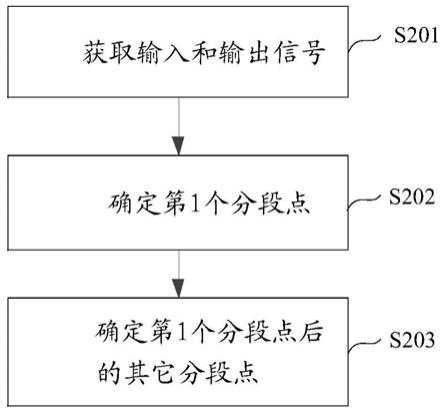

36.请参照图4。图为4本发明一实施例中,一种具有抗干扰机制的信号输出方法400的流程图。

37.除前述装置外,本发明还揭露一种具有抗干扰机制的信号输出方法400,应用于例如,但不限于图1的信号输出电路100中。信号输出方法400的一实施例如图4所示,包含下列步骤:

38.s410:使放大器110根据供应电源vdd运作并产生放大输出信号aout。其中放大器110分别通过第一放大器键合线115a电性耦接于供应电源vdd以及通过第二放大器键合线115b电性耦接于接地端gnd。

39.s420:使变压电路120包含的变压器vtf根据放大输出信号aout进行阻抗转换产生变压输出信号vout以及使变压电路120的稳压电容c对放大器110进行二次谐波抑制。

40.s430:使电源端抗干扰电路130包含的电源端键合线140以及电源端抗干扰电容150共同运作以滤除由变压电路120产生的变压输出信号vout耦合至第一放大器键合线115a的基本谐波耦合信号fs。其中电源端键合线140电性耦接于接地端gnd,电源端抗干扰电容150电性耦接于电源端键合线140与第一放大器键合线115a之间。

41.需注意的是,上述的实施方式仅为一范例。在其他实施例中,本领域的通常知识者当可在不违背本发明的精神下进行更动。

42.综合上述,本发明中具有抗干扰机制的信号输出电路及方法以较小电路面积的抗干扰电路直接滤除基本谐波耦合信号,大幅提升抗干扰的效率。

43.虽然本发明的实施例如上所述,然而该些实施例并非用来限定本发明,本技术领域具有通常知识者可依据本发明的明示或隐含的内容对本发明的技术特征施以变化,凡此种种变化均可能属于本发明所寻求的专利保护范畴,换言之,本发明的专利保护范围须视本说明书的权利要求范围所界定者为准。

44.【符号说明】

45.100:信号输出电路

46.110:放大器

47.115a:第一放大器键合线

48.115b:第二放大器键合线

49.120:变压电路

50.125a:第一变压电路键合线

51.125b:第二变压电路键合线

52.130:电源端抗干扰电路

53.140:电源端键合线

54.150:电源端抗干扰电容

55.190:封装结构

56.180:输入电路

57.200:信号输出电路

58.210:电源端抗干扰电感

59.300:信号输出电路

60.310:接地端抗干扰电路

61.320:接地端键合线

62.330:接地端抗干扰电容

63.400:信号输出方法

64.s410~s430:步骤

65.a:虚线

66.aout:放大输出信号

67.c:稳压电容

68.fs:基本谐波耦合信号

69.gnd:接地端

70.in:输入信号

71.pad:输出接垫

72.vdd:供应电源

73.vi 、vi-:输入端

74.vo :输出信号端

75.vo-:输出接地端

76.vout:变压输出信号

77.vtf:变压器。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。