pn结及调制器

技术领域

1.本技术实施例涉及半导体技术领域,特别涉及一种pn结及调制器。

背景技术:

2.pn结是指在一块单晶半导体两侧分别掺杂成p型半导体和n型半导体时,p型半导体和n型半导体的交界面附近的过渡区。也就是说,p型半导体和n型半导体之间相连的接触面称为pn结。pn结是电子技术中许多元件,例如半导体二极管、双极性晶体管的物质基础。

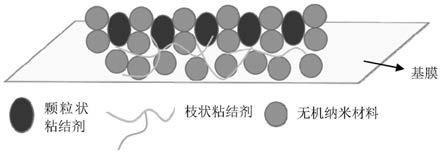

3.现有技术的pn结的结构为图1所示的水平型的pn结。如图1所示,硅基底上设置有绝缘层,绝缘层的材料为二氧化硅,硅波导位于绝缘层上面。在硅波导上掺杂硼原子和磷原子分别形成p区域和n区域,从而形成如图1所示的水平型的pn结。其中,脊形波导内的低浓度掺杂(p/n)区域用于电光调制,中浓度掺杂(p /n )区域用于降低pn结的电阻以增大带宽,高浓度掺杂(p /n )区域与电极金属进行欧姆接触从而加载调制电压,以便于低浓度掺杂(p/n)区域进行电光调制。

4.上述水平型的pn结的调制效率低,应用于调制器中时无法满足更高光信号调制速率、更低驱压的需求。

技术实现要素:

5.本技术实施例提供一种pn结及调制器,能够在不引入较高的工艺掺杂复杂度的同时提高pn结的调制效率,从而能够满足更高光信号调制速率、更低驱压的需求。

6.本技术实施例第一方面提供一种pn结。该pn结包括衬底和设置在所述衬底上的波导层。其中,所述波导层包括第一p型区域和脊形波导层,所述第一p型区域设在所述衬底上,所述脊形波导层位于所述第一p型区域背离所述衬底的一面上;所述脊形波导层包括第二p型区域和n型区域,所述n型区域位于所述第二p型区域中,且所述n型区域的延伸方向垂直于所述第一p型区域的延伸方向。

7.通过n型区域位于第二p型区域中,且所述n型区域的延伸方向垂直于所述第一p型区域的延伸方向,增大了n型区域和p型区域之间的掺杂区域,提高了pn结的调制效率,从而能够满足更高光信号调制速率、更低驱压的需求。同时,通过采用在第二p型区域中形成n型区域的方式,无需在n型区域与第二p型区域之间形成的掺杂区域内进行多次掺杂,相对简化了掺杂工序,提升了掺杂效率。

8.在一种可能的实现方式中,所述第一p型区域包括两个第二p型掺杂区域和位于所述两个第二p型掺杂区域之间的第一p型掺杂区域;所述第一p型掺杂区域的掺杂浓度小于所述两个第二p型掺杂区域的掺杂浓度;所述脊形波导层位于所述第一p型掺杂区域上。

9.在一种可能的实现方式中,所述n型区域的底端端面延伸到所述第一p型掺杂区域内,且n型区域的底端端面与所述衬底之间具有部分所述第一p型掺杂区域。

10.在一种可能的实现方式中,所述第一p型区域还包括两个第三p型掺杂区域,其中一个所述第三p型掺杂区域位于所述第一p型掺杂区域和所述两个第二p型掺杂区域中的其

中一个所述第二p型掺杂区域之间,另一个所述第三p型掺杂区域位于所述第一p型掺杂区域和所述两个第二p型掺杂区域中的另一个所述第二p型掺杂区域之间。通过设置第三p型掺杂区域能够降低pn结的电阻,从而增大带宽。

11.在一种可能的实现方式中,所述第一p型掺杂区域的掺杂浓度小于所述第三p型掺杂区域的掺杂浓度,所述第三p型掺杂区域的掺杂浓度小于所述第二p型掺杂区域的掺杂浓度。

12.在一种可能的实现方式中,所述n型区域包括第一n型掺杂区域和第二n型掺杂区域,所述第二n型掺杂区域位于所述第一n型掺杂区域的上方;所述第一n型掺杂区域的掺杂浓度小于所述第二n型掺杂区域的掺杂浓度。

13.在一种可能的实现方式中,所述n型区域还包括第三n型掺杂区域,所述第三n型掺杂区域位于所述第一n型掺杂区域和所述第二n型掺杂区域之间。通过设置第三n型掺杂区域能够降低pn结的电阻,从而增大带宽。

14.在一种可能的实现方式中,所述第一n型掺杂区域的掺杂浓度小于所述第三n型掺杂区域的掺杂浓度,所述第三n型掺杂区域的掺杂浓度小于所述第二n型掺杂区域的掺杂浓度。

15.在一种可能的实现方式中,所述第二n型掺杂区域的端面与所述第二p型区域的端面齐平。这样,相比于第二n型掺杂区域的端面高于第二p型区域的端面或者第二n型掺杂区域的端面低于第二p型区域的端面,掺杂工艺相对简单,从而能够提高生产效率。

16.在一种可能的实现方式中,所述第二p型区域的掺杂浓度与第一p型掺杂区域的掺杂浓度相同。

17.在一种可能的实现方式中,还包括电极金属层。所述电极金属层包括阳极金属层和阴极金属层,两个所述第二p型掺杂区域与所述阳极金属层电连接,所述第二n型掺杂区域与所述阴极金属层电连接。这样,在电极金属层上加载反向偏压(即阴极金属层上加载正偏压,阳极金属层上加载负偏压)时,载流子会在pn结处形成耗尽区域,这样,载流子的分布与波导内光场的重叠发生改变,会使波导等效折射率发生变化,从而进行电光调制。

18.在一种可能的实现方式中,还包括电极连接层。所述电极连接层包括第一电极连接层和第二电极连接层,每个所述第二p型掺杂区域与所述阳极金属层之间通过所述第一电极连接层电连接,所述第二n型掺杂区域与所述阴极金属层之间通过所述第二电极连接层电连接。

19.在一种可能的实现方式中,还包括包覆层,所述包覆层覆盖在所述第一p型区域和所述脊形波导层上,所述电极金属层位于所述包覆层上;所述第一电极连接层和所述第二电极连接层位于所述包覆层中,且所述第一电极连接层的一端与所述第二p型掺杂区域电接触,所述第一电极连接层的另一端与所述阳极金属层电接触;

20.所述第二电极连接层的一端与所述第二n型掺杂区域电接触,所述第二电极连接层的另一端与所述阴极金属层电接触。

21.在一种可能的实现方式中,所述电极连接层还包括第三电极连接层,两个所述第二p型掺杂区域电连接的所述第一电极连接层通过所述第三电极连接层导通,所述阳极金属层与所述第三电极连接层电连接。这样,即可实现两个第二p型掺杂区域同时与一个阳极金属层301电连接。

22.在一种可能的实现方式中,所述衬底包括硅基底和设在所述硅基底上的绝缘层;所述波导层位于所述绝缘层上。

23.在一种可能的实现方式中,所述pn结为环形结构,其中一个所述第二p型掺杂区域位于所述环形结构的外圈,另一个所述第二p型掺杂区域位于所述环形结构的内圈;且位于所述环形结构外圈的所述第二p型掺杂区域上开设至少一个缺口,所述缺口的一端延伸到所述第二n型掺杂区域;所述缺口内设置有n型延伸区域,所述n型延伸区域的一端与所述第二n型掺杂区域电接触,所述n型延伸区域的另一端与所述第二电极连接层电连接。

24.在一种可能的实现方式中,所述pn结为条状结构,其中一个所述第二p型掺杂区域上开设至少一个缺口,所述缺口的一端延伸到所述第二n型掺杂区域;所述缺口内设置有n型延伸区域,所述n型延伸区域的一端与所述第二n型掺杂区域电接触,所述n型延伸区域的另一端与所述第二电极连接层电连接。

25.本技术实施例第二方面提供一种调制器,至少包括壳体、主线波导和上述任一所述的pn结。所述pn结位于所述壳体内,且所述壳体上开设可供其中一个所述主线波导穿过的第一光入口和第一调制穿通光出口;所述主线波导与所述pn结的脊形波导层导通。

26.本技术实施例第三方面提供一种调制器,至少包括分束器、非对称波导结构、两个反射回路和上述任一所述的pn结;所述分束器的一端具有第二光入口和第二调制穿通光出口,所述分束器的另一端与所述非对称波导结构的一端相连,所述非对称波导结构的另一端与其中一个所述pn结一端的脊形波导层相连,所述pn结另一端的脊形波导层与其中一个反射回路相连;所述分束器的第三端与另一个所述pn结一端的脊形波导层相连,所述pn结另一端的脊形波导层与另一个所述反射回路相连。

27.本技术实施例第四方面提供一种调制器,至少包括分束器、非对称波导层、平板波导层、两个反射回路和上述任一所述的pn结;所述pn结结构的数量为一个,所述分束器的一端具有第二光入口和第二调制穿通光出口,所述分束器的另一端与所述非对称波导结构的一端相连,所述非对称波导结构的另一端与其中一个所述pn结结构一端的脊形波导结构,所述pn结结构另一端的脊形波导结构与其中一个反射回路相连;所述分束器的第三端与所述平板波导层的一端相连,所述平板波导层的另一端与另一个所述反射回路相连。

28.本技术实施例第五方面提供一种调制器,至少包括耦合器和上述任一所述的pn结;所述耦合器的一端具有第三光入口和调制反射光出口,所述耦合器的另一端与所述pn结一端的脊形波导层相连,所述pn结另一端的脊形波导层与第三调制穿通光出口相连;所述pn结中靠近所述耦合器一端的所述脊形波导层呈波浪状。

29.上述第二至第五方面的调制器的有益效果参见第一方面关于pn结的相关描述,在此不再赘述。

30.本技术实施例第六方面提供一种pn结的制作方法,包括多个步骤。首先,提供衬底;然后,在所述衬底上形成第一p型区域;接着,在所述第一p型区域上形成脊形波导层,所述脊形波导层包括第二p型区域以及n型区域,所述n型区域位于所述第二p型区域中,且所述n型区域的延伸方向垂直于所述第一p型区域的延伸方向。

31.本技术实施例提供的pn结的制作方法,通过在第一p型区域上形成脊形波导层,脊形波导层包括第二p型区域以及n型区域,n型区域位于第二p型区域中,且n型区域的延伸方向垂直于第一p型区域的延伸方向,这样,无需在n型区域与第二p型区域之间形成的掺杂区

域内进行多次掺杂,简化了掺杂工序,提升了掺杂效率,同时还能够提高pn结的调制效率,从而使该pn结应用于调制器中时能够满足更高光信号调制速率、更低驱压的需求。

32.在一种可能的实现方式中,所述在所述第一p型区域上形成脊形波导层,包括:在所述第一p型区域上形成第二p型区域;从所述第二p型区域的部分端面向所述第二p型区域内注入磷原子,以在所述第二p型区域中形成n形区域,所述第二p型区域以及位于所述第二p型区域中的所述n型区域组成所述脊形波导层。

33.在一种可能的实现方式中,所述从所述第二p型区域的部分端面向所述第二p型区域内注入磷原子,以在所述第二p型区域中形成n形区域,包括:在所述第二p型区域的部分端面中注入磷原子形成第一n型掺杂区域;在所述第一n型掺杂区域的部分区域中注入磷原子形成第二n型掺杂区域,所述第二n型掺杂区域中磷原子的掺杂浓度大于所述第一n型掺杂区域中磷原子的掺杂浓度。

34.在一种可能的实现方式中,所述在所述第一n型掺杂区域的部分区域注入磷原子形成第二n型掺杂区域之前,还包括:在所述第一n型掺杂区域的部分区域内注入磷原子形成第三n型掺杂区域;

35.所述在所述第一n型掺杂区域的部分区域注入磷原子形成第二n型掺杂区域,包括:在所述第三n型掺杂区域的部分区域内注入磷原子形成第二n型掺杂区域,其中,所述第三n型掺杂区域中磷原子的掺杂浓度大于所述第一n型掺杂区域中磷原子的掺杂浓度且小于所述第二n型掺杂区域中磷原子的掺杂浓度。

36.在一种可能的实现方式中,所述在所述衬底上形成第一p型区域,包括:在所述衬底上形成平板波导层;在所述平板波导层的至少部分区域注入硼原子,且注入所述硼原子的所述平板波导层作为所述第一p型区域。

37.在一种可能的实现方式中,所述在所述平板波导层的至少部分注入硼原子,包括:在所述平板波导层的中间区域注入所述硼原子,形成第一p型掺杂区域;所述在所述第一p型区域上形成第二p型区域,包括:在所述第一p型掺杂区域上形成所述第二p型区域。

38.在一种可能的实现方式中,所述在所述第一p型掺杂区域上形成所述第二p型区域,包括:在所述平板波导层的中部区域上形成脊形硅层;在所述平板波导层上靠近所述脊形硅层的区域注入所述硼原子,形成第一p型掺杂区域,所述脊形硅层中注入硼原子形成所述第二p型区域。

39.在一种可能的实现方式中,所述在所述第三n型掺杂区域的部分区域内注入磷原子形成第二n型掺杂区域之后,还包括:在所述平板波导层上靠近所述第一p型掺杂区域的区域中注入硼原子,形成两个第二p型掺杂区域,且所述第一p型掺杂区域位于两个所述第二p型掺杂区域之间,所述第一p型掺杂区域的掺杂浓度小于所述第二p型掺杂区域的掺杂浓度。

40.在一种可能的实现方式中,在所述形成两个第二p型掺杂区域之前,还包括:在所述平板波导层上靠近所述第一p型掺杂区域的部分区域中注入硼原子,形成两个第三p型掺杂区域,所述第一p型掺杂区域位于两个所述第三p型掺杂区域之间;

41.所述在所述平板波导层上靠近所述第一p型掺杂区域的区域中注入硼原子,形成两个第二p型掺杂区域,包括:在所述平板波导层上靠近所述第三p型掺杂区域的区域注入硼原子,形成两个第二p型掺杂区域,所述第一p型掺杂区域的掺杂浓度小于所述第三p型掺

杂区域的掺杂浓度,所述第三p型掺杂区域的掺杂浓度小于所述第二p型掺杂区域的掺杂浓度。

42.在一种可能的实现方式中,所述形成第二p型掺杂区域之后,还包括:在所述第二p型掺杂区域上设置阳极金属层;在所述n型区域中的第二n型掺杂区域上设置阴极金属层。

43.在一种可能的实现方式中,所述在所述第二p型掺杂区域上设置阳极金属层之前还包括:在所述第一p型区域和所述脊形波导层上形成包覆层;所述在所述第二p型掺杂区域上设置阳极金属层,在所述n型区域中的第二n型掺杂区域上设置阴极金属层,包括:

44.在所述包覆层中设有第一电极连接层和第二电极连接层,所述第一电极连接层的一端与所述第二p型掺杂区域抵接,所述第二电极连接层的一端与第二n型掺杂区域抵接;

45.在所述包覆层上分别设有所述阳极金属层和所述阴极金属层,且所述阳极金属层与所述第一电极连接层电连接,所述阴极金属层与所述第二电极连接层的另一端电连接。

46.在一种可能的实现方式中,所述提供衬底,包括:提供硅基底;在所述硅基底上形成绝缘层;所述在所述衬底上形成第一p型区域,包括:在所述绝缘层上形成所述第一p型区域。

附图说明

47.图1为现有技术中水平型pn结的结构示意图;

48.图2为现有技术中l型pn结的结构示意图;

49.图3为现有技术中u/c型pn结的结构示意图;

50.图4为本技术实施例提供的pn结的一种结构示意图;

51.图5为本技术实施例提供的pn结的立体截面图;

52.图6为本技术实施例提供的pn结的另一种结构示意图;

53.图7为本技术实施例提供的pn结的再一种结构示意图;

54.图8为本技术实施例提供的pn结的又一种结构示意图;

55.图9为本技术实施例提供的pn结与现有技术中的三种pn结的调制效率对比图;

56.图10为本技术实施例提供的pn结与现有技术中的三种pn结的波导损耗对比图;

57.图11为本技术实施例提供的一种pn结的俯视图;

58.图12为本技术实施例提供的另一种pn结的俯视图;

59.图13为本技术实施例提供的调制器的一种结构示意图;

60.图14为本技术实施例提供的调制器的另一种结构示意图;

61.图15为本技术实施例提供的调制器与现有技术中的三种pn结应用于调制器时的调制效率和动态er对比图;

62.图16为本技术实施例提供的调制器的实际调制效率和动态er图;

63.图17为本技术实施例提供的调制器的一种结构示意图;

64.图18为本技术实施例提供的调制器的另一种结构示意图;

65.图19为本技术实施例提供的调制器的结构示意图;

66.图20为本技术实施例提供的pn结制作方法的流程示意图。

67.附图标记说明:

68.100-pn结;1-波导层;11-平板波导层;10-第一p型区域;101-第一p型掺杂区域;

102-第二p型掺杂区域;1021-缺口;103-第三p型掺杂区域;20,20a-脊形波导层;201-第二p型区域;202-n型区域;2021-第一n型掺杂区域;2022-第二n型掺杂区域;2023-第三n型掺杂区域;2024-n型延伸区域;30-电极金属层;301-阳极金属层;302-阴极金属层;40-电极连接层;401-第一电极连接层;402-第二电极连接层;403-第三电极连接层;50-包覆层;2-衬底;21-硅基底;22-绝缘层;200-调制器;3-壳体;31-主线波导;32-第一光入口;33-第一调制穿通光出口;34-输入端口;35-调制下载光出口;4-分束器;41-第一端;42-第二光入口;43-第二调制穿通光出口;44-第二端;45-第三端;5-非对称波导结构;6-反射回路;7-耦合器;71-第三光入口;72-调制反射光出口;73-第三调制穿通光出口。

具体实施方式

69.本技术的实施方式部分使用的术语仅用于对本技术的具体实施例进行解释,而非旨在限定本技术,下面将结合附图对本技术实施例的实施方式进行详细描述。

70.随着数据中心内部及数据中心之间的信息交换量的极速增长,低功耗、高带宽的电光器件因可实现低成本的高速信号传输、接收和交换而颇受青睐。其中,绝缘体上硅(silicon on insulator,soi)集成电光器件有以下优势:第一,与互补型金属氧化物半导体(complementary metal oxide semiconductor,cmos)工艺兼容,使得电器件和电光器件有较高的统一集成的可能性;第二,soi晶元尺寸大且成本低,使得soi集成器件的价格较磷化铟等集成器件的价格更便宜;第三,硅与二氧化硅的折射率差异较大,使光场能有效地限制在soi波导中,因此器件弯曲半径和尺寸更小,例如soi微环调制器(microring resonator modulator,mrm)半径仅几微米到几十微米,有利于电光器件大规模、高密度地集成;第四,soi波导掺杂硼、磷原子形成的pn结,有较高的电光调制效率和带宽,从而形成低驱压高速调制器。

71.soi高速调制器的原理是基于加载反向偏压的pn结的载流子耗尽效应进行电光调制。目前,常见的pn结为如图1所示的水平型pn结。其调制效率过低,应用于调制器中时无法满足更高光信号调制速率、更低驱压的需求。但是将pn结的调制效率提升后,又会增加pn结的掺杂工艺复杂程度,往往需要在掺杂区域内进行多次掺杂,效率低下,且该掺杂技术目前并不完全成熟,形成的pn结的调制效率与仿真值有较大差距。如图2所示,在脊形波导内,低浓度掺杂n区域位于p区域上方或p区域位于n区域上方,形成l型pn结,l型的pn结的掺杂工艺复杂,需要在脊形波导上的l型掺杂区域内进行多次掺杂。又如图3所示,在脊形波导内,低浓度掺杂n区域和低浓度掺杂p区域形成u型(也称为c型)pn结,u型的pn结调制效率较水平型的pn结并没有太大提升,而且由于掺杂结构更为复杂,其pn结的掺杂工艺的实现更为困难,即需要在u型区域进行多次掺杂,效率低下。

72.基于此,本技术实施例提供一种新的pn结。参照图4所示,pn结100包括衬底2和设置在衬底2上的波导层1。其中,波导层1包括第一p型区域10和脊形波导层20,第一p型区域10设在衬底2上,脊形波导层20位于第一p型区域10背离衬底2的一面上。

73.脊形波导层20包括第二p型区域201和n型区域202,n型区域202位于第二p型区域201中,且n型区域202的延伸方向垂直于第一p型区域10的延伸方向。通过n型区域201位于第二p型区域201中,无需在n型区域202与第二p型区域201之间形成的掺杂区域内进行多次掺杂,简化了掺杂工序,提升了掺杂效率,同时还能够提高pn结的调制效率,从而使该pn结

应用于调制器中时能够满足更高光信号调制速率、更低驱压的需求。

74.具体地,第一p型区域10包括第一p型掺杂区域101和两个第二p型掺杂区域102,且第一p型掺杂区域101位于两个第二p型掺杂区域102之间。其中,第一p型掺杂区域101的掺杂浓度小于第二p型掺杂区域102的掺杂浓度,且脊形波导层20位于第一p型掺杂区域101上。

75.在本技术实施例中,第二p型区域201的掺杂浓度与第一p型掺杂区域101的掺杂浓度相同。

76.n型区域202包括第一n型掺杂区域2021和第二n型掺杂区域2022,第二n型掺杂区域2022位于第一n型掺杂区域2021的上方,其中,第一n型掺杂区域2021的掺杂浓度小于第二n型掺杂区域2022的掺杂浓度。

77.需要说明的是,第一p型掺杂区域101和第一n型掺杂区域2021用于电光调制,第二p型掺杂区域102和第二n型掺杂区域2022分别与电极进行欧姆接触从而用于加载调制电压,以便于第一p型掺杂区域101和第一n型掺杂区域2021进行电光调制。

78.在一种可能的实现方式中,如图5所示,n型区域202的底端端面(即图5中第一n型掺杂区域2021的底端端面)延伸到第一p型掺杂区域101内,且n型区域202的底端端面与衬底2之间具有部分第一p型掺杂区域101。例如,n型区域202和衬底2之间由部分第一p型掺杂区域101隔开,n型区域202的底端端面未延伸至衬底2处,以确保位第一p型掺杂区域101处于导通状态。

79.在可能的具体实现方式中,第一p型区域10还包括两个第三p型掺杂区域103。如图6所示,其中一个第三p型掺杂区域103位于第一p型掺杂区域101和两个第二p型掺杂区域102中的其中一个第二p型掺杂区域102之间,另一个第三p型掺杂区域103位于第一p型掺杂区域101和两个第二p型掺杂区域102中的另一个第二p型掺杂区域102之间。

80.其中,第一p型掺杂区域101的掺杂浓度小于第三p型掺杂区域103的掺杂浓度,第三p型掺杂区域103的掺杂浓度小于第二p型掺杂区域102的掺杂浓度。例如,第二p型掺杂区域102的掺杂浓度为1

×

10

20

cm-3

,第三p型掺杂区域103的掺杂浓度为2

×

10

18

cm-3

,第一p型掺杂区域101的掺杂浓度为5

×

10

17

cm-3

。

81.在可能的具体实现方式中,n型区域202还包括第三n型掺杂区域2023,如图6所示,第三n型掺杂区域2023位于第一n型掺杂区域2021和第二n型掺杂区域2022之间。其中,第一n型掺杂区域2021的掺杂浓度小于第三n型掺杂区域2023的掺杂浓度,第三n型掺杂区域2023的掺杂浓度小于第二n型掺杂区域2022的掺杂浓度。例如,第二n型掺杂区域2022的掺杂浓度为1

×

10

20

cm-3

,第三n型掺杂区域2023的掺杂浓度为3

×

10

18

cm-3

,第一n型掺杂区域2021的掺杂浓度为3

×

10

17

cm-3

。

82.具体地,第一p型掺杂区域101、第二p型掺杂区域102和第三p型掺杂区域103通过掺杂硼原子形成,第一n型掺杂区域2021、第二n型掺杂区域2022和第三n型掺杂区域2023通过掺杂磷原子形成。

83.需要说明的是,第三p型掺杂区域103和第三n型掺杂区域2023用于降低pn结100的电阻以增大带宽。在本技术实施例中,pn结100可以包括第三p型掺杂区域103和第三n型掺杂区域2023,也可以不包括第三p型掺杂区域103和第三n型掺杂区域2023,本技术实施例对此并不加以限定。

84.在一种可能的实现方式中,第二n型掺杂区域2022的端面与第二p型区域201的端面齐平。这样,相比于第二n型掺杂区域2022的端面高于第二p型区域201的端面或者第二n型掺杂区域2022的端面低于第二p型区域201的端面,掺杂工艺相对简单,从而能够提高生产效率。

85.如图7所示,pn结100还包括电极金属层30,电极金属层30包括阳极金属层301和阴极金属层302。其中,两个第二p型掺杂区域102与阳极金属层301电连接,第二n型掺杂区域2022与阴极金属层302电连接。在电极金属层30上加载反向偏压(即阴极金属层302上加载正偏压,阳极金属层301上加载负偏压)时,载流子会在pn结处形成耗尽区域,这样,载流子的分布与波导内光场的重叠发生改变,会使波导等效折射率发生变化,从而进行电光调制。

86.在一种可能的实现方式中,电极金属层30包括多层的电极金属层30。这样,多层的电极金属层30会比单层具有更大的设计自由度。电极金属层30也可以包括具有氮化钛(tin)等用于热调的金属层,热调金属层能够加载电压到该层,该层导热使得硅波导被加热,相对于其他金属层进行电光调制,该层是通过热调来调节波导的中光场的相位等。

87.在本技术实施例中,第二p型掺杂区域102与阳极金属层301之间,以及第二n型掺杂区域2022与阴极金属层302之间通过电极连接层40实现电连接,具体地,电极连接层40包括第一电极连接层401和第二电极连接层402,每个第二p型掺杂区域102与阳极金属层301之间通过第一电极连接层401实现电连接,第二n型掺杂区域2022与阴极金属层302之间通过第二电极连接层402实现电连接。

88.作为一种可选的实施方式,该pn结100中还包括包覆层50。如图7所示,包覆层50覆盖在第一p型区域10和脊形波导层20上,电极金属层30位于包覆层50上,包覆层的材料可以为二氧化硅、空气等。

89.第一电极连接层401和第二电极连接层402位于包覆层50中,且第一电极连接层401的一端与第二p型掺杂区域102电接触,第一电极连接层401的另一端与阳极金属层301电接触,以此实现第二p型掺杂区域102与包覆层50上的阳极金属层301之间的电连接。

90.第二电极连接层402的一端与第二n型掺杂区域2022电接触,第二电极连接层402的另一端与阴极金属层302电接触。以此实现第二n型掺杂区域2022与包覆层50上的阴极金属层302之间的电连接。

91.在本技术实施例中,如图8所示,电极连接层40还包括第三电极连接层403,两个第二p型掺杂区域102电连接的第一电极连接层401通过第三电极连接层403导通,阳极金属层301与第三电极连接层403电连接。这样,即可实现两个第二p型掺杂区域102同时与一个阳极金属层301电连接。

92.在一种可能的实现方式中,电极连接层40包括多层的电极连接层40。多层的电极连接层40设计的有益效果类似多层的电极金属层30,不再赘述。

93.此外,如图8所示,衬底2包括硅基底21和设在硅基底21上的绝缘层22,波导层1位于绝缘层22上,绝缘层22的材料可以为二氧化硅。

94.具体地,对现有技术中的水平型pn结(图1)、l型pn结(图2)、u/c型pn结(图3)和本技术实施例中的pn结100进行了调制效率的仿真对比。在仿真模拟中,除四种pn结的结构不同外,其他参数均保持一致:脊形波导层20的宽度均为600μm,第二p型掺杂区域102和第二n型掺杂区域2022的掺杂浓度均为1

×

10

20

cm-3

,第一p型掺杂区域101和第一n型掺杂区域的

掺杂浓度均为5

×

10

17

cm-3

,且均无第三p型掺杂区域103和第三n型掺杂区域。

95.参照图9所示,在同样的偏压下,本技术实施例中的pn结100的等效折射率改变最大,即调制效率最高。在-2v和-4v时,水平pn结、l型pn结、u/c型pn结和本技术中的pn结100所对应的等效折射率分别如下表所示:

[0096][0097]

因此,本技术实施例中的pn结100的等效折射率改变(即调制效率)较l型pn结分别提升17%和22%,较水平型pn结分别提升63%和48%,较u型pn分别提升67%和50%。但是,由于本技术实施例中的pn结100中,第二n型掺杂区域2022(高浓度掺杂区域)位于波导层1的内部,导致该pn结100的波导损耗较其他三种pn结大很多(如图10所示)。但本技术实施例中的pn结主要应用于尺寸较小的soi调制器,如mrm、迈克尔逊干涉调制器(michelson interferometric modulator,mim)、布拉格光栅调制器(bragg grating modulator,bgm)等,因此并不会引入太大的插损代价。例如,如图10所示,对于半径为7.5μm的mrm,采用本技术实施例中的pn结100,仿真得到的-2v波导损耗为118.3db/cm,半径为7.5μm的mrm,周长为47.1239μm,乘以波导损耗得出的微环整体损耗为0.5575db。因此,将本技术实施例中的pn结应用于尺寸较小的调制器时,在提高调制器调制效率的同时,不会影响调制器的其他性能。

[0098]

在本技术实施例中,该pn结100的结构包括但不限于以下两种可能的实现方式:

[0099]

一种可能的实现方式为:如图11所示,pn结100为环形结构。具体地,其中一个第二p型掺杂区域102位于环形结构的外圈,另一个第二p型掺杂区域102位于环形结构的内圈,而且,位于环形结构外圈的第二p型掺杂区域102上开设至少一个缺口1021(如图11中,位于环形结构外圈的第二p型掺杂区域102上开设有一个缺口1021),缺口1021的一端延伸到第二n型掺杂区域2022。

[0100]

缺口1021内设置有n型延伸区域2024,n型延伸区域2024的一端与第二n型掺杂区域2022电接触,n型延伸区域2024的另一端与第二电极连接层402电连接。这样,位于环形结构外圈的第二p型掺杂区域102靠近缺口1021的位置通过第一电极连接层401与阳极金属层301连接,第二n型掺杂区域2022通过位于缺口1021内的n型延伸区域2024和第二电极连接层402与阴极金属层302连接。

[0101]

另一种可能的实现方式为:如图12所示,pn结100为条状结构,其中一个第二p型掺杂区域102上开设至少一个缺口1021(如图12中,其中一个第二p型掺杂区域102上开设有两个缺口1021),缺口1021的一端延伸到第二n型掺杂区域2022。

[0102]

缺口1021内设置有n型延伸区域2024,n型延伸区域2024的一端与第二n型掺杂区域2022电接触,n型延伸区域2024的另一端与第二电极连接层402电连接。这样,第二p型掺杂区域102通过第一电极连接层401与阳极金属层301连接,第二n型掺杂区域2022通过位于缺口1021内的n型延伸区域2024和第二电极连接层402与阴极金属层302连接。

[0103]

参照附图13所示,本技术实施例还提供一种调制器200。调制器200例如可以为mrm,该调制器200至少包括壳体3、主线波导31和上述的pn结100。其中,pn结100位于壳体3

内,且壳体3上开设可供其中一个主线波导31穿过的第一光入口32和第一调制穿通光出口33,主线波导31与pn结100的脊形波导层20导通。

[0104]

在实际使用时,调制器200的第一光入口32输入特定波长的激光光源,将调制器200的阳极金属层301接地,阴极金属层302输入高速电信号,不同电平的电信号使得pn结100内的载流子耗尽的程度不同,因此载流子与pn结100内光场的重叠也不同,光场的有效折射率便因此得到调制,从而使得调制器200的第一调制穿通光出口33可以输出不同强度的光信号。

[0105]

在一种可能的实现方式中,如图14所示,调制器200的主线波导31为两个,壳体3上还开设有可供另一个主线波导31穿过的输入端口34和调制下载光出口35,且另一个主线波导31与pn结100的脊形波导层20导通。

[0106]

在本技术实施例中,该调制器200中的pn结100为图11所示,位于微环内圈的第二p型掺杂区域102和位于微环外圈的第二p型掺杂区域102均需连接阳极金属层301,因此两者的阳极金属层301相连,如图13和图14所示,将调制器200置于显微镜下,第三电极连接层403可被明显看到,但如果水平型pn结、l型pn结和u/c型pn结这样连接,则第二p型掺杂区域102会与第二n型掺杂区域2022共地,导致mrm无法进行调制。

[0107]

在其它的一些实施例中,位于微环内圈的第二p型掺杂区域102与位于微环外圈的第二p型掺杂区域102之间的阳极金属层301之间的连接也可能不以图13和图14的形式出现,但只要是脊形波导层两侧20的电极金属层30相连,且该调制器200可正常工作,则说明采用了本技术实施例中的pn结100。

[0108]

示例性地,对现有技术中的水平型pn结(图1)、l型pn结(图2)、u/c型pn结(图3)和本技术实施例中的pn结100分别应用于mrm时,进行了调制效率和动态er(即动态消光比)的仿真对比。在仿真模拟中,为使mrm应用于高带宽、低串扰的多通道级联调制系统,其半径设定为7.5μm,通过设计mrm结构使其3-db光带宽均为60ghz,以上设计在用于对比的四个mrm中均保持一致,且均保持阳极电压为0v,在阴极上分别加载0v和2v偏压。

[0109]

如图15所示,应用上述四种不同的pn结的mrm均工作在1550nm波长附近,应用申请实施例中的pn结100的mrm具有最高的调制效率和动态er。四种pn结所对应的调制效率和动态er分别如下表所示:

[0110] 水平型pn结l型pn结u/c型pn结本技术中的pn结调制效率(pm/v)25352540动态er(db)2.263.482.254.44

[0111]

相对于水平型pn结和u/c型pn结,本技术实施例中的pn结100的调制效率提高了60%,5-db工作点处的动态er提高了2.18db。相对于l型pn结,本技术实施例中的pn结100的调制效率提高了14%,5-db工作点处的动态er提高了0.96db。

[0112]

此外,如图11所示,为连接阴极金属层302,mrm结构需设置缺口1021以及位于缺口处的n型延伸区域2024将第二n型掺杂区域2022引出,因此整个mrm约有10%的周长不构成pn结。附图16为将本技术实施例中的pn结的调制效率调整为图18中本技术实施例中的pn结的仿真数据的90%后的结果。这样,相对于图15中应用水平型pn结、l型pn结和u/c型pn结的mrm,本技术实施例依然具有最高的调制效率和动态er,相对于水平型pn结和u/c型pn结,本技术实施例的调制效率提高了56%,5-db工作点处的动态er提高了2.10db;相对于l型pn

结,本技术实施例的调制效率提高了11%,5-db工作点处的动态er提高了0.88db。

[0113]

需要说明的是,无论mrm是否有多个第二p型掺杂区域102和n型延伸区域2024形成分段式掺杂,只要在mrm中应用本技术实施例中的pn结100,都在本技术的保护范围内。

[0114]

参照附图17所示,本技术实施例提供另一种调制器200,调制器200例如可以为mim,该调制器200至少包括分束器4、非对称波导结构5、两个反射回路6和上述的pn结100。

[0115]

在一些实施例中,调制器200为双臂掺杂时,pn结100的数量可以为两个。分束器4的第一端41具有第二光入口42和第二调制穿通光出口43,分束器4的第二端44与非对称波导结构5的一端相连,非对称波导结构5的另一端与其中一个pn结100一端的脊形波导层20相连,pn结100另一端的脊形波导层20与其中一个反射回路6相连。其中,非对称波导结构5能够使mim在光谱上具有天然的干涉相消波长。

[0116]

分束器4的第三端45与另一个pn结100一端的脊形波导层20相连,pn结100另一端的脊形波导层20与另一个反射回路6相连。

[0117]

在一种可能的实现方式中,至少其中一个臂上的pn结100的两个第二p型掺杂区域102通过第三电极连接层403导通,阳极金属层301与第三电极连接层403电连接。这样,即可实现两个第二p型掺杂区域102同时与一个阳极金属层301电连接。

[0118]

这样,将调制器200置于显微镜下,第三电极连接层403可被明显看到,但如果水平型pn结、l型pn结和u/c型pn结这样连接,则第二p型掺杂区域102会与第二n型掺杂区域2022共地,导致mim无法进行调制。

[0119]

在一种可能的实现方式中,其中一个臂上的pn结100中的阳极金属层301和阴极金属层302分别与另一个臂上的pn结100中的阳极金属层301和阴极金属层302相连。

[0120]

在一些其它的实施例中,调制器200为单臂掺杂时,pn结100的数量可以为一个。如图18所示,分束器4的第一端41具有第二光入口42和第二调制穿通光出口43,分束器4的第二端44与非对称波导结构5的一端相连,非对称波导结构5的另一端与其中一个pn结100一端的脊形波导层20相连,pn结100另一端的脊形波导层20与其中一个反射回路6相连。

[0121]

分束器4的第三端45与平板波导层11相连,平板波导层11的另一端与另一个反射回路6相连,其中,平板波导层11上设置有脊形波导层20a。

[0122]

需要说明的是,无论是否mim中的第二p型掺杂区域102、第一p型掺杂区域101和n型延伸区域2024形成分段式结构,无论分段式结构中这几个区域的数目是多少(例如,图17中,第二p型掺杂区域102和第一p型掺杂区域101有三个,n型延伸区域2024有两个),只要在mim中应用本技术实施例中的pn结100,都在本技术的保护范围内。

[0123]

需要说明的是,无论mim是否有多个第二p型掺杂区域102和n型延伸区域2024形成分段式掺杂,只要在mim中应用本技术实施例中的pn结100,都在本技术的保护范围内。

[0124]

在实际使用时,调制器200的第二光入口42输入特定波长的激光光源;调制器200的阳极金属层301接地,阴极金属层302输入高速电信号,不同电平的电信号使得pn结100内载流子耗尽的程度不同,因此载流子与pn结100内光场的重叠也不同,光场的有效折射率便因此得到调制,从而使调制器200的第二调制穿通光出口43可以输出不同强度的光信号。

[0125]

参照附图19所示,本技术实施例还提供一种调制器200,该调制器200例如可以为bgm。该调制器200至少包括耦合器7和上述的pn结100,耦合器7的一端具有第三光入口71和调制反射光出口72,耦合器7的另一端与pn结100一端的脊形波导层20相连,pn结100另一端

的脊形波导层20与第三调制穿通光出口73相连。其中,pn结100中靠近耦合器7一端的脊形波导层20呈波浪状(图中未示出)。

[0126]

在实际使用时,调制器200的第三光入口71输入特定波长的激光光源;调制器200的阳极金属层301接地,阴极金属层302输入高速电信号,不同电平的电信号使得pn结100内载流子耗尽的程度不同,因此载流子与pn结100内光场的重叠也不同,光场的有效折射率便因此得到调制,从而使调制器200的第三调制穿通光出口73可以输出不同强度的光信号。

[0127]

参照附图20所示,本技术实施例还提供一种pn结100的制作方法。该方法包括:

[0128]

s101:提供衬底2;

[0129]

其中,衬底2包括硅基底21和绝缘层22,提供硅基底21后,在硅基底21上形成绝缘层22,绝缘层22的材料可以为二氧化硅。

[0130]

s102:在衬底2上形成第一p型区域10;

[0131]

具体地,在衬底2中的绝缘层22上形成第一p型区域10。

[0132]

s103:在第一p型区域10上形成脊形波导层20,脊形波导层20包括第二p型区域201以及n型区域202,n型区域202位于第二p型区域201中,且n型区域202的延伸方向垂直于第一p型区域的延伸方向。

[0133]

通过n型区域201位于第二p型区域201中,无需在n型区域202与第二p型区域201之间形成的掺杂区域内进行多次掺杂,简化了掺杂工序,提升了掺杂效率,同时还能够提高pn结的调制效率,从而使该pn结应用于调制器中时能够满足更高光信号调制速率、更低驱压的需求。

[0134]

其中,s103具体包括:

[0135]

步骤a1:在第一p型区域10上形成第二p型区域201;

[0136]

步骤a2:从第二p型区域201的部分端面向第二p型区域201内注入磷原子,以在第二p型区域201中形成n形区域,第二p型区域201以及位于第二p型区域201中的n型区域202组成脊形波导层20。

[0137]

进一步地,步骤a2包括:

[0138]

步骤a21:在第二p型区域201的部分端面中注入磷原子形成第一n型掺杂区域2021;

[0139]

步骤a23:在第一n型掺杂区域2021的部分区域中注入磷原子形成第二n型掺杂区域2022。

[0140]

其中,第二n型掺杂区域2022中磷原子的掺杂浓度大于第一n型掺杂区域2021中磷原子的掺杂浓度。

[0141]

在一种可能的实现方式中,在步骤a23之前,还包括:

[0142]

步骤a22:在第一n型掺杂区域2021的部分区域内注入磷原子形成第三n型掺杂区域2023。

[0143]

这样,步骤a23具体包括:

[0144]

a231:在第三n型掺杂区域2023的部分区域内注入磷原子形成第二n型掺杂区域2022。

[0145]

其中,第三n型掺杂区域2023中磷原子的掺杂浓度大于第一n型掺杂区域2021中磷原子的掺杂浓度且小于第二n型掺杂区域2022中磷原子的掺杂浓度。

[0146]

在一种可能的实现方式中,s102具体包括:

[0147]

步骤b1:在衬底2上形成平板波导层11(即第一p型区域10所处的位置);

[0148]

步骤b2:在平板波导层11的至少部分区域注入硼原子,且注入硼原子的平板波导层11作为第一p型区域10。

[0149]

其中,步骤b2具体包括:

[0150]

步骤b21:在平板波导层11的中间区域注入硼原子,形成第一p型掺杂区域101;

[0151]

步骤a1具体包括:

[0152]

步骤a11:在第一p型掺杂区域101上形成第二p型区域201。

[0153]

在一种可能的实现方式中,步骤a11包括:

[0154]

步骤a111:在平板波导层11的中部区域上形成脊形硅层;

[0155]

步骤a112:在平板波导层11上靠近脊形硅层的区域注入硼原子,形成第一p型掺杂区域101,脊形硅层中注入硼原子形成第二p型区域201。

[0156]

在一种可能的实现方式中,在步骤a231之后,还包括:

[0157]

步骤a233:在平板波导层11上靠近第一p型掺杂区域101的区域中注入硼原子,形成两个第二p型掺杂区域102,且第一p型掺杂区域101位于两个第二p型掺杂区域102之间,第一p型掺杂区域101的掺杂浓度小于第二p型掺杂区域102的掺杂浓度。

[0158]

在一种可能的实现方式中,在步骤a233之前,还包括:

[0159]

a232:在平板波导层11上靠近第一p型掺杂区域101的部分区域中注入硼原子,形成两个第三p型掺杂区域103,第一p型掺杂区域101位于两个第三p型掺杂区域103之间;

[0160]

步骤a233具体包括:

[0161]

在平板波导层11上靠近第三p型掺杂区域103的区域注入硼原子,形成两个第二p型掺杂区域102,第一p型掺杂区域101的掺杂浓度小于第三p型掺杂区域103的掺杂浓度,第三p型掺杂区域103的掺杂浓度小于第二p型掺杂区域102的掺杂浓度。

[0162]

需要说明的是,第一p型掺杂区域101和第一n型掺杂区域2021用于电光调制,第二p型掺杂区域102和第二n型掺杂区域2022分别与电极进行欧姆接触从而用于加载调制电压,以便于第一p型掺杂区域101和第一n型掺杂区域2021进行电光调制,第三p型掺杂区域103和第三n型掺杂区域2023用于降低pn结100的电阻以增大带宽。

[0163]

在一种可能的实现方式中,在步骤a233之后,还包括:

[0164]

步骤c1:在第二p型掺杂区域102上设置阳极金属层301;

[0165]

步骤c3:在n型区域202中的第二n型掺杂区域2022上设置阴极金属层302。

[0166]

在阴极金属层302上加载正偏压,阳极金属层301上加载负偏压时,载流子会在pn结处形成耗尽区域,这样,载流子的分布与波导内光场的重叠发生改变,会使波导等效折射率发生变化,从而进行电光调制。

[0167]

在一种可能的实现方式中,在c3之前,还包括:

[0168]

c2:在第一p型区域10和脊形波导层20上形成包覆层50;

[0169]

进一步地,步骤c2具体包括:

[0170]

c21:在包覆层50中设有第一电极连接层401第一电极连接层401的一端与第二p型掺杂区域102抵接;

[0171]

c22:在包覆层50上设有阳极金属层301,且阳极金属层301与第一电极连接层401

电连接。

[0172]

步骤c3具体包括;

[0173]

c31:在包覆层50中设有第二电极连接层402,第二电极连接层402的一端与第二n型掺杂区域2022抵接;

[0174]

c32:在包覆层50上设有阴极金属层302,且阴极金属层302与第二电极连接层402的另一端电连接。

[0175]

需要说明的是,本技术实施例只是作为一种示例介绍了pn结100的一种制作方法。在其它的一些实施例中,当然也可以通过调整上述各步骤的顺序来实现上述的pn结,因此,本技术实施例对pn结100的制作方法并不加以限定,也不限于上述示例。

[0176]

在本技术实施例的描述中,需要说明的是,除非另有明确的规定和限定,术语“安装”、“相连”、“连接”应作广义理解,例如,可以是固定连接,也可以是通过中间媒介间接相连,可以是两个元件内部的连通或者两个元件的相互作用关系。对于本领域的普通技术人员而言,可以根据具体情况理解上述术语在本技术实施例中的具体含义。

[0177]

本技术实施例的说明书和权利要求书及上述附图中的术语“第一”、“第二”、“第三”、“第四”等(如果存在)是用于区别类似的对象,而不必用于描述特定的顺序或先后次序。

[0178]

最后应说明的是:以上各实施例仅用以说明本技术实施例的技术方案,而非对其限制;尽管参照前述各实施例对本技术实施例进行了详细的说明,本领域的普通技术人员应当理解:其依然可以对前述各实施例所记载的技术方案进行修改,或者对其中部分或者全部技术特征进行等同替换;而这些修改或者替换,并不使相应技术方案的本质脱离本技术实施例各实施例技术方案的范围。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。