1.本发明涉及像素驱动技术领域,特别是涉及一种像素驱动装置和像素驱动方法。

背景技术:

2.micro led显示技术是指以自发光的微米量级的led为发光像素单元,将其组装到驱动面板上形成高密度led阵列的显示技术,由于micro led芯片尺寸小、集成度高和自发光等特点,与lcd、oled相比,其在亮度、分辨率、对比度、能耗、使用寿命、响应速度和热稳定性等方面具有更大的优势。

3.micro led的数字显示驱动方式一般是将n bit灰阶数据存储于像素驱动电路之外的缓存单元中,再将其逐个送入像素驱动电路,采用n个子帧刷新显示,利用脉冲宽度调制方式实现2

n

位显示灰阶。每一个子帧在显示完成后,均需等待一段时间后才能进行下一子帧的显示,直至完成整个像素单元的灰阶显示,因此导致每一个子帧中显示时间存在占空比,尤其是在低灰阶子帧中,占空比会更小,实际显示时间较短,进而降低了显示亮度。

技术实现要素:

4.基于此,有必要针对上述问题,提供一种像素驱动系统和像素驱动方法。

5.一种像素驱动系统,包括由若干个像素驱动装置构成的x行y列的阵列,各所述像素驱动装置用于驱动对应的像素单元;所述像素驱动装置包括像素驱动模块和对应于n位灰阶数据的n个数据中转模块,各所述数据中转模块均包括数据写入单元、数据存储单元以及数据驱动单元,n、x和y均为大于等于2的自然数;

6.所述数据写入单元连接对应的灰阶数据线,用于接入对应的灰阶数据;所述数据存储单元连接所述数据写入单元,用于存储接入的灰阶数据;所述数据驱动单元分别连接所述数据存储单元和所述像素驱动模块,各所述数据驱动单元响应于预设顺序的驱动信号,依次传输对应的所述灰阶数据至所述像素驱动模块,以驱动所述像素驱动模块点亮像素单元,同一行中各像素驱动装置的第i个数据驱动单元对应的驱动信号线互连,i的取值遍历1

‑

n中的自然数,同一行中包括n条驱动信号线;

7.至少一行中的n条驱动信号线与相邻的至少一行中的n条驱动信号线对应连接。

8.在其中一个实施例中,x行中的n条驱动信号线均对应连接。

9.在其中一个实施例中,所述数据中转模块还包括数据复位单元,所述数据复位单元连接所述数据存储单元,用于在写入灰阶数据之前,响应于数据复位信号线上的数据复位信号,对所述数据存储单元内的存储数据进行清零;

10.同一行中各像素驱动装置的数据复位单元的数据复位信号线互连,至少一行中的数据复位信号线与相邻的至少一行中的数据复位信号线连接。

11.在其中一个实施例中,所述数据复位单元包括第三开关单元,所述第三开关单元包括控制端、第一端和第二端,所述控制端连接所述数据复位信号线,所述第一端连接所述数据存储单元,所述第二端接地,当所述数据复位信号线被选通时,各所述第三开关单元的

第一端和第二端导通。

12.在其中一个实施例中,所述数据写入单元包括第一开关单元和选通信号线,所述第一开关单元包括控制端、第一端和第二端,所述控制端连接所述选通信号线,所述第一端连接所述灰阶数据线,所述第二端连接所述数据存储单元;

13.同一行中各像素驱动装置的所述数据写入单元的选通信号线互连,当所述选通信号线被选通时,同一行中的各所述第一开关单元的第一端和第二端导通。

14.在其中一个实施例中,所述数据存储单元包括存储电容,所述存储电容的第一端连接所述数据写入单元,所述存储电容的第二端接地。

15.在其中一个实施例中,所述数据驱动单元包括第二开关单元和驱动信号线,所述第二开关单元包括控制端、第一端和第二端,所述控制端连接所述驱动信号线,用于接入驱动信号,所述第一端连接所述数据存储单元,第二端连接所述像素驱动模块;

16.当按预设顺序选通各所述驱动信号线时,对应的所述第二开关单元的第一端和第二端导通,依次将对应的所述灰阶数据传输至所述像素驱动模块,以驱动所述像素驱动模块点亮像素单元。

17.在其中一个实施例中,所述像素驱动模块包括像素复位信号线、第四开关单元和第五开关单元;

18.所述第四开关单元包括控制端、第一端和第二端,所述控制端连接各所述数据驱动单元,所述第一端连接电流源,所述第二端连接像素单元;

19.所述第五开关单元包括控制端、第一端和第二端,所述控制端连接像素复位信号线,所述第一端连接所述第四开关单元的控制端,所述第二端接地;

20.同一行中各像素驱动装置的像素复位信号线互连,至少一行中的像素复位信号线与相邻的至少一行中的像素复位信号线连接。

21.在其中一个实施例中,同一列中各像素驱动装置的第j个灰阶数据线互连,j的取值遍历1

‑

n中的自然数。

22.在其中一个实施例中,所述像素驱动系统还包括数据转换模块,所述数据转换模块连接各所述数据中转模块,用于将n位灰阶数据由串行数据转换为并行数据,并将n位并行的灰阶数据分别发送至各像素驱动装置中的n个数据中转模块。

23.一种像素驱动方法,应用于上述的像素驱动系统,所述像素驱动方法包括:

24.控制当前行中n*y个数据写入单元并行写入n*y个灰阶数据,并将写入的n*y个灰阶数据存储于各自对应的数据存储单元中;

25.控制所述当前行的关联行中n*y个数据写入单元并行写入n*y个灰阶数据,并将写入的n*y个灰阶数据存储于各自对应的数据存储单元中,其中,所述关联行中的n条驱动信号线与当前行的n条驱动信号线对应连接;

26.选通当前行及其关联行中各像素驱动装置的第i个数据驱动单元对应的驱动信号线,同步驱动当前行及其关联行中各像素驱动装置的第i个数据驱动单元,将灰阶数据传输至各自对应的像素驱动模块,以驱动各像素驱动模块点亮各像素单元,其中,i的取值按照预设顺序遍历1

‑

n中的自然数;

27.按照上述方式依次点亮x行像素单元。

28.在其中一个实施例中,所述数据中转模块还包括数据复位单元,所述数据复位单

元连接所述数据存储单元,响应于数据复位信号线上的数据复位信号,对所述数据存储单元内的存储数据进行清零,同一行中各像素驱动装置的数据复位单元的数据复位信号线互连,至少一行中的数据复位信号线与相邻的至少一行中的数据复位信号线连接;在所述控制当前行中n*y个数据写入单元并行写入n*y个灰阶数据,并将写入的n*y个灰阶数据存储于各自对应的数据存储单元中的步骤之前,所述像素驱动方法还包括:

29.选通所述当前行及其关联行的数据复位信号线,对所述当前行及其关联行中的各数据存储单元内的存储数据进行同步清零。

30.在其中一个实施例中,在所述选通当前行及其关联行中各像素驱动装置的第i个数据驱动单元对应的驱动信号线,同步驱动当前行及其关联行中各像素驱动装置的第i个数据驱动单元,将灰阶数据传输至各自对应的像素驱动模块,以驱动各像素驱动模块点亮各像素单元的步骤中,

31.在同步驱动当前行及其关联行中各像素驱动装置的第任意个数据驱动单元,并点亮对应的像素单元达到预设时长之后,同步熄灭对应的像素单元。

32.上述像素驱动系统,在每个像素驱动装置中设置有对应于n位灰阶数据的n个数据中转模块,且每个数据中转模块均包括数据写入单元、数据存储单元和数据驱动单元,n个数据写入单元负责通过各自的灰阶数据线接入n位灰阶数据,并存储于各自对应的数据存储单元中,在驱动像素单元实现灰阶显示之前,可以同步将n位灰阶数据存储于各自对应的数据存储单元中,在灰阶显示过程中,各数据驱动单元只需根据预设顺序的驱动信号,依次将各自对应的数据存储单元中存储的灰阶数据传输至像素驱动模块,以使像素驱动模块点亮像素单元,实现各子帧显示。并且,至少一行中的n条驱动信号线与相邻的至少一行中的n条驱动信号线对应连接,即是说,可同时驱动多行像素单元实现子帧显示。

33.在上述灰阶显示过程中,每一个子帧显示完成后,即可直接进行下一子帧的显示,各子帧显示时间之间几乎无等待时间,有效提高了各子帧显示时间的占空比,进而提高显示亮度。同时,可预先给相邻的几行接入灰阶数据,然后同步驱动相邻行的像素单元,使得驱动信号线相连接的相邻行之间无显示等待时间,可一定程度上减轻显示撕裂感,且由于多行共用驱动信号线,可有效减少走线数量,降低制备工艺难度。

附图说明

34.图1为传统技术中灰阶显示时的占空比状态;

35.图2为本技术实施例一提供的像素驱动装置的结构示意图;

36.图3为本技术实施例一提供的像素驱动装置中单个数据中转模块与像素驱动模块的结构示意图;

37.图4为本技术实施例一提供的像素驱动装置另一种实施方式的结构示意图;

38.图5为本技术实施例一提供的像素驱动装置又一种实施方式的结构示意图;

39.图6为本技术中灰阶显示时的占空比状态;

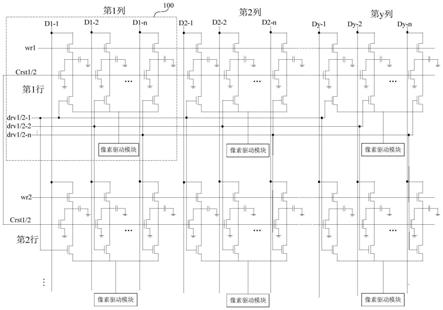

40.图7为本技术实施例二提供的像素驱动系统的结构示意图。

41.附图标记说明:

42.100、像素驱动装置;110、像素驱动模块;111、像素复位信号线;112、第四开关单元;113、第五开关单元;114、电流源;120、数据中转模块;121、数据写入单元;1211、第一开

关单元;1212、选通信号线;122、数据存储单元;123、数据驱动单元;1231、第二开关单元;1232、驱动信号线;130、像素单元;140、数据复位单元;141、数据复位信号线;142、第三开关单元;150、数据转换模块。

具体实施方式

43.为了便于理解本发明,下面将参照相关附图对本发明进行更全面的描述。附图中给出了本发明的优选实施方式。但是,本发明可以以许多不同的形式来实现,并不限于本文所描述的实施方式。相反的,提供这些实施方式的目的是为了对本发明的公开内容理解得更加透彻全面。

44.在本发明中,除非另有明确的规定和限定,术语“安装”、“相连”、“连接”、“固定”等术语应做广义理解,例如,可以是固定连接,也可以是可拆卸连接,或成一体;可以是机械连接,也可以是电连接;可以是直接相连,也可以通过中间媒介间接相连,可以是两个元件内部的连通或两个元件的相互作用关系,除非另有明确的限定。对于本领域的普通技术人员而言,可以根据具体情况理解上述术语在本发明中的具体含义。

45.术语“第一”、“第二”仅用于描述目的,而不能理解为指示或暗示相对重要性或者隐含指明所指示的技术特征的数量。由此,限定有“第一”、“第二”的特征可以明示或者隐含地包括至少一个该特征。在本发明的描述中,“多个”的含义是至少两个,例如两个,三个等,除非另有明确具体的限定。

46.除非另有定义,本文所使用的所有的技术和科学术语与属于本发明的技术领域的技术人员通常理解的含义相同。本文中在本发明的说明书中所使用的术语只是为了描述具体的实施例的目的,不是旨在于限制本发明。本文所使用的术语“及/或”包括一个或多个相关的所列项目的任意的和所有的组合。

47.正如背景技术中所述,micro led的数字显示驱动方式一般是将n bit灰阶数据存储于像素驱动电路之外的缓存单元中,再将其逐个送入像素驱动电路,采用n个子帧刷新显示,利用脉冲宽度调制方式实现2

n

位显示灰阶。参照图1,每一个子帧在显示完成后,均需等待一段时间后才能进行下一子帧的显示,直至完成整个像素单元的灰阶显示,因此导致各子帧均包含了显示时间和等待时间,存在一定的占空比,尤其是在低灰阶子帧中,占空比更小,实际显示时间较短,进而降低了显示亮度。

48.为了解决上述问题,本技术提供了一种像素驱动装置、像素驱动系统及像素驱动方法。

49.实施例一

50.本实施例提供了一种像素驱动装置100,用于驱动像素单元130实现灰阶显示。

51.参照图2,本实施例提供的像素驱动装置100包括像素驱动模块110和对应于n位灰阶数据的n个数据中转模块120,n为大于等于2的自然数。其中,n个数据中转模块120分别用于对n位灰阶数据进行中转处理,像素驱动模块110分别连接像素单元130和n个数据中转模块120,依次根据n位灰阶数据实现n个子帧的显示,完成像素单元130的灰阶显示。其中,n的取值可以根据实际情况而定,可以为2或5或10或15等,在此不一一列举。

52.各数据中转模块120均包括数据写入单元121、数据存储单元122以及数据驱动单元123。

53.其中,数据写入单元121连接对应的灰阶数据线,用于接入对应的灰阶数据。即,具有n个数据写入单元121、n个灰阶数据线以及n位灰阶数据,数据写入单元121、灰阶数据线以及灰阶数据一一对应,每位灰阶数据均通过其对应的灰阶数据线写入至对应的数据写入单元121。本实施例中,通过n个数据写入单元121写入n位灰阶数据的过程可以是同步进行。

54.数据存储单元122连接数据写入单元121,用于存储接入的灰阶数据。同样地,包括n个数据存储单元122,与n个数据写入单元121一一对应,当写入了灰阶数据之后,则通过对应的数据存储单元122将其存储起来。即,在给数据驱动单元123提供驱动信号之前,可以预先将n位灰阶数据分别存储于n个数据存储单元122中,当给数据驱动单元123提供驱动信号时,则直接使用相应的灰阶数据,无需等待从灰阶数据线接入灰阶数据。

55.数据驱动单元123分别连接数据存储单元122和像素驱动模块110,各数据驱动单元123响应于预设顺序的驱动信号,依次传输对应的灰阶数据至像素驱动模块110,以驱动像素驱动模块110点亮像素单元130。本实施例中,包括n个数据驱动单元123,与n个数据存储单元122一一对应,当某一数据驱动单元123接收到驱动信号时,可以将对应的数据存储单元122中的灰阶数据输出至像素驱动模块110,像素驱动模块110点亮像素单元130。其中,各子帧是逐个显示的,即,发给各数据驱动单元123的驱动信号是以预设顺序逐个发出,预设顺序跟数据编码顺序有关,一般地,先驱动第一个数据驱动单元123,再驱动第二个数据驱动单元123,依次类推,直至完成第n个数据驱动单元123的驱动。当然,鉴于编码顺序有可能是随机的,可按实际编码顺序进行驱动信号的发送。另外,每个子帧的点亮时长呈翻倍增长趋势,例如第一子帧的显示时长为20*t,第二子帧的显示时长为21*t,第三子帧的显示时长为22*t,依次类推,第n子帧的显示时长为2

n

‑1*t。

56.由于在驱动点亮过程之前,已经将n位灰阶数据分别存储于n个数据存储单元122中,因此,在驱动点亮过程中,直接使用对应的灰阶数据即可,无需等待从灰阶数据线接入灰阶数据,由此有效减少了各子帧之间的等待时间,提高显示时间的占空比,显著提高了显示亮度,可对照参考图1和6。

57.在其中一个实施例中,参照图3和4,数据写入单元121包括第一开关单元1211和选通信号线1212,第一开关单元1211包括控制端、第一端和第二端,控制端连接选通信号线1212,第一端连接灰阶数据线,第二端连接数据存储单元122。各数据写入单元121的选通信号线1212互连,当选通信号线1212被选通时,各第一开关单元1211的第一端和第二端导通。

58.即,当选通信号线1212未被选通时,第一开关单元1211断开,灰阶数据线与数据存储单元122断开,此时不写入灰阶数据;当选通信号线1212被选通时,第一开关单元1211闭合,灰阶数据线与数据存储单元122连通,此时灰阶数据可经灰阶数据线写入至数据存储单元122中。本实施例中,n个数据写入单元121中的选通信号线1212互连,即共享一根选通信号线1212,由此,当选通该选通信号线1212时,n位灰阶数据可经对应的n个灰阶数据线并行写入对应的数据存储单元122中,同步完成n位灰阶数据的写入过程。

59.在其中一个实施例中,参照图4,第一开关单元1211可以选用n型mosfet(metal

‑

oxide

‑

semiconductor field

‑

effect transistor,金属氧化物半导体场效应晶体管)。当选通信号线1212上为高电平时,则代表选通信号线1212被选通。

60.作为可替换实施方式,第一开关单元1211也可以选用p型mosfet,当选通信号线1212上为低电平时,则代表选通信号线1212被选通。

61.当然,第一开关单元1211还可以为其他形式,只要能够实现上述功能即可,在此不一一列举。

62.在其中一个实施例中,参照图4,数据存储单元122包括存储电容,存储电容的第一端连接数据写入单元121,存储电容的第二端接地。当通过数据写入单元121写入灰阶数据时,灰阶数据可以存储于存储电容中。选用存储电容作为数据存储单元122,有助于简化电路结构,且存储电容成本较低,降低像素驱动装置100的整体成本。

63.在其中一个实施例中,参照图3,数据驱动单元123包括第二开关单元1231和驱动信号线1232,第二开关单元1231包括控制端、第一端和第二端,控制端连接驱动信号线1232,用于接入驱动信号,第一端连接数据存储单元122,第二端连接像素驱动模块110。当按预设顺序选通各驱动信号线1232时,对应的第二开关单元1231的第一端和第二端导通,依次将对应的灰阶数据传输至像素驱动模块110,以驱动像素驱动模块110点亮像素单元130。

64.即,当驱动信号线1232未被选通时,第二开关单元1231断开,数据存储单元122与像素驱动模块110断开,没有灰阶数据传输至像素驱动模块110;当驱动信号线1232被选通时,第二开关单元1231闭合,数据存储单元122与像素驱动模块110导通,数据存储单元122中存储的灰阶数据传输至像素驱动模块110,像素驱动模块110能够点亮像素单元130。

65.本实施例中,每个数据驱动单元123均具有独立的驱动信号线1232,同一时刻,只选通一条驱动信号线1232,以将对应的灰阶数据传输至像素驱动模块110,在实际应用中,可预先设定选通顺序,根据预设顺序依次选通各个驱动信号线1232,进而将n位灰阶数据逐个传输至像素驱动模块110,以实现各子帧的逐个显示。

66.在其中一个实施例中,参照图4,第二开关单元1231可以选用n型mosfet(metal

‑

oxide

‑

semiconductor field

‑

effect transistor,金属氧化物半导体场效应晶体管)。当驱动信号线1232上为高电平时,则代表驱动信号线1232被选通。作为可替换实施方式,第二开关单元1231也可以选用p型mosfet,当驱动信号线1232上为低电平时,则代表驱动信号线1232被选通。当然,第二开关单元1231还可以为其他形式,只要能够实现上述功能即可,在此不一一列举。

67.在其中一个实施例中,参照图3,像素驱动装置100还包括数据复位单元140,数据复位单元140连接数据存储单元122,用于在写入灰阶数据之前,对数据存储单元122内的存储数据进行清零。上一帧的n个子帧显示完毕之后,会进行下一帧的灰阶显示,在写入下一帧的n个灰阶数据之前,首先可通过数据复位单元140对数据存储单元122中存储的上一帧的灰阶数据进行清零,以便准确存入下一帧的灰阶数据。

68.在其中一个实施例中,参照图3,数据复位单元140包括数据复位信号线141和第三开关单元142,第三开关单元142包括控制端、第一端和第二端,控制端连接数据复位信号线141,第一端连接数据存储单元122,第二端接地。各数据复位单元140的数据复位信号线141互连,当数据复位信号线141被选通时,各第三开关单元142的第一端和第二端导通。

69.即,当数据复位信号线141未被选通时,灰阶数据保持存储于数据存储单元122中,当数据复位信号线141被选通时,数据存储单元122接地,数据存储单元122内部存储的灰阶数据被清空,以对数据存储单元122进行复位。

70.本实施例中,参照图4,n个数据复位单元140的数据复位信号线141互连,即共享一

根数据复位信号线141,由此,当选通该数据复位信号线141时,可同步对n个数据存储单元122进行复位,提高复位效率。

71.在其中一个实施例中,参照图3,像素驱动模块110包括像素复位信号线111、第四开关单元112和第五开关单元113。

72.第四开关单元112包括控制端、第一端和第二端,控制端连接各数据驱动单元123,第一端连接电流源114,第二端连接像素单元130。当数据驱动单元123被驱动时,灰阶数据传输至第四开关单元112的控制端,第四开关单元112根据灰阶数据确定是否闭合或断开,若第四开关单元112闭合,则电流源114与像素单元130连通,像素单元130被点亮,若第四开关单元112断开,则电流源114与像素单元130断开,像素单元130熄灭。

73.第五开关单元113包括控制端、第一端和第二端,控制端连接像素复位信号线111,第一端连接第四开关单元112的控制端,第二端接地。当像素复位信号线111被选通时,第四开关单元112的控制端接地,第四开关单元112断开,像素单元130熄灭。在每个子帧显示结束后,可选通像素复位信号线111,实现对像素单元130的复位,以免上一个子帧的残留显示对下一子帧的显示造成影响。

74.在其中一个实施例中,参照图4,第四开关单元112和第五开关单元113可以选用n型mosfet。当灰阶数据为1,则第四开关单元112闭合,像素单元130被点亮,当灰阶数据为0,则第四开关单元112断开,像素单元130熄灭。当像素复位信号线111上为高电平1,则第五开关单元113闭合,第四开关单元112的控制端接地,像素单元130熄灭。

75.当然,第四开关单元112和第五开关单元113也可以选用p型mosfet。此时,当灰阶数据为0,则第四开关单元112闭合,像素单元130被点亮,当灰阶数据为1,则第四开关单元112断开,像素单元130熄灭。当像素复位信号线111上为低电平0,则第五开关单元113闭合,第四开关单元112的控制端接地,像素单元130熄灭。

76.在其中一个实施例中,参照图5,像素驱动装置100还包括数据转换模块150,数据转换模块150连接n个数据中转模块120,用于将n位灰阶数据由串行数据转换为并行数据,并将n位并行的灰阶数据分别发送至n个数据中转模块120。通过数据转换模块150将串行的n位灰阶数据转换为并行的n位灰阶数据,有助于将n位灰阶数据同步传输至n个数据中转模块120,实现灰阶数据的同步传输。

77.在系统架构层面,原始的显示数据一般为8位串行数据,其通过数据接口模块传输至数据校正模块,进行灰阶校正、亮度校正等,数据格式由原始的8位串行数据转化为n位串行数据,最后经数据转换模块150由n位串行数据转化为n位并行数据。其中,数据接口模块可以包括mipi(mobile industry processor interface,移动产业处理器接口)、spi(serial peripheral interface,串行外设接口)、lvds(low

‑

voltage differential signaling,低电压差分信号)、i2c(inter-integrated circuit,两线式串行总线)等。

78.在其中一个实施例中,像素单元130可以包括发光二极管。

79.在其中一个实施例中,数据中转模块120与像素驱动模块110相互独立设计,即,在制备时,分别在不同的电路板上制备数据中转模块120和像素驱动模块110,应用时将数据中转模块120与像素驱动模块110连接即可,由此简化了制备工艺,同时避免将复杂的电路制备于同一片电路板上而导致电路板体积过大,不利于微型设计。

80.实施例二

81.本实施例提供了一种像素驱动系统,参照图7,包括由若干个实施例一提供的像素驱动装置100构成的x行y列的阵列,各像素驱动装置用于驱动对应的像素单元,各像素驱动装置包括像素驱动模块和对应于n位灰阶数据的n个数据中转模块,各数据中转模块均包括数据写入单元、数据存储单元以及数据驱动单元,其中,n、x和y均为大于等于2的自然数。关于像素驱动装置的具体结构可参见实施例一中的具体描述,在此不再赘述。

82.即,实施例一所提供的像素驱动装置100对应的是一个像素单元130,在实际应用中,存在若干个像素单元130,其对应若干个像素驱动装置100,例如包括x行y列个像素单元130,那么像素驱动系统则包括x行y列个像素驱动装置100,分别用于驱动x行y列个像素单元130。其中,x和y的取值可视实际情况而定,例如分辨率为1920

×

1080,则为1080行、1920列的矩阵。

83.在其中一个实施例中,数据写入单元121包括第一开关单元1211和选通信号线1212,第一开关单元1211包括控制端、第一端和第二端,控制端连接选通信号线1212,第一端连接灰阶数据线,第二端连接数据存储单元122。同一行中各像素驱动装置100的数据写入单元121的选通信号线1212互连,当选通信号线被选通时,同一行中的各第一开关单元1211的第一端和第二端导通。其中,图7中,第一行中选通信号线1212为wr1,第二行中选通信号线1212为wr2,第x行中选通信号线1212为wrx。

84.本实施例中,同一行中各像素驱动装置100的选通信号线1212互连。即,当同一行的选通信号线1212被选通时,该行中的y个像素驱动装置100中的数据写入单元121同步写入灰阶数据,每个像素驱动装置100中具有n个数据写入单元121,即,同步写入n*y个灰阶数据,并将其存储于各自对应的数据存储单元122。

85.由于在驱动点亮过程之前,已经将每个像素驱动装置100对应的n位灰阶数据分别存储于n个数据存储单元122中,因此,在驱动点亮过程中,直接使用对应的灰阶数据即可,无需等待从灰阶数据线接入灰阶数据,由此有效减少了各子帧之间的等待时间,提高显示时间的占空比,显著提高了显示亮度。

86.每个像素驱动装置100均具有n个数据驱动单元123,本实施例中,同一行中各像素驱动装置100的第i个数据驱动单元123对应的驱动信号线1232互连,i的取值遍历1

‑

n中的自然数。例如,参照图7,第一行中每个像素驱动装置100的第1个数据驱动单元123对应的驱动信号线1232(drv1

‑

1)互连,每个像素驱动装置100的第2个数据驱动单元123对应的驱动信号线1232(drv1

‑

2)互连,依此类推,每个像素驱动装置100的第n个数据驱动单元123对应的驱动信号线1232(drv1

‑

n)互连。即,一共包括n条驱动信号线1232,在实际驱动过程中,当选通第1条驱动信号线1232时,每个像素驱动装置100中的第一个数据驱动单元123工作,将对应的灰阶数据传输至各像素单元130中,实现第一个子帧的显示;当选通第2条驱动信号线1232时,每个像素驱动装置100中的第二个数据驱动单元123工作,将对应的灰阶数据传输至各像素单元130中,实现第二个子帧的显示,依此类推,当选通第n条驱动信号线1232时,每个像素驱动装置100中的第n个数据驱动单元123工作,将对应的灰阶数据传输至各像素单元130中,实现第n个子帧的显示,完成该行y个像素单元130第一帧的显示。

87.本实施例中,至少一行中的n条驱动信号线与相邻的至少一行中的n条驱动信号线对应连接。需要说明的是,以第一行和第二行为例,n条驱动线对应连接指的是,第一行中各像素驱动装置中的第i个数据驱动单元的驱动信号线与第二行中各像素驱动装置中的第i

个数据驱动单元的驱动信号线互连,i遍历1

‑

n中的自然数。例如,第一行中各像素驱动装置中的第1个数据驱动单元的驱动信号线与第二行中各像素驱动装置中的第1个数据驱动单元的驱动信号线互连,例如图7中的驱动线drv1/2

‑

1;第一行中各像素驱动装置中的第2个数据驱动单元的驱动信号线与第二行中各像素驱动装置中的第2个数据驱动单元的驱动信号线互连,例如图7中的驱动线drv1/2

‑

2;依此类推,第一行中各像素驱动装置中的第n个数据驱动单元的驱动信号线与第二行中各像素驱动装置中的第n个数据驱动单元的驱动信号线互连,例如图7中的驱动线drv1/2

‑

n。

88.本实施例中,可以仅第一行的n条驱动信号线与第二行的n条驱动信号线对应连接;或者仅第一行、第二行以及第三行的n条驱动信号线对应连接;或者第一行与第二行的n条驱动信号线对应连接,同时第三行和第四行的n条驱动信号线对应连接,第x

‑

1行和第x行的n条驱动信号线对应连接;或者第一行和第二行的n条驱动信号线对应连接,第三、第四、第五、第六行的n条驱动信号线对应连接等。以上仅仅是列举出的几种连接方式,在实际应用中,可以有多种连接组合方式,相邻的任意几行的驱动信号线均可对应连接,只要能够实现至少两行同时驱动的目的即可。图7中示出了第一行和第二行的驱动信号线对应连接的情形。第一行和第二行中各像素驱动装置的第一个驱动单元对应的驱动信号线均为drv1/2

‑

1,第二个驱动单元对应的驱动信号线均为drv1/2

‑

2,第n个驱动单元对应的驱动信号线均为drv1/2

‑

n。

89.以相邻行两两连接为例,首先可控制第一行的数据写入单元接入灰阶数据,然后控制第二行的数据写入单元接入灰阶数据,再驱动第一行和第二行中各像素驱动装置的第1个数据驱动单元对应的驱动信号线,以将对应的灰阶数据传输至第一行和第二行中的各像素单元,同步实现各像素单元的第一子帧显示;以同样的方式实现各像素单元的第二个子帧显示,依次类推,同步实现第一行和第二行中的各像素单元的n个子帧显示。参照图6,本实施例仅需在驱动第一行和第二行显示之前,等待少许时间分别接入两行的灰阶数据,即可实现第一行和第二行的像素单元同步显示,即两行之间无显示等待时间,可一定程度上减轻显示撕裂感,且由于第一行和第二行共用驱动信号线,可有效减少走线数量,降低制备工艺难度。

90.在其中一个实施例中,x行中的n条驱动信号线均对应连接。即,所有行中的n条驱动信号线均对应连接,在实际应用中,仅需在驱动显示之前,等待一段时间接入各行的n位灰阶数据,在驱动显示时,可同步驱动x行的像素单元的各子帧显示,相对于传统的显示,无画面撕裂感,且极大地减少了驱动信号线的数量,简化了制备工艺和整体结构。

91.在其中一个实施例中,数据驱动单元123包括第二开关单元1231和驱动信号线1232,第二开关单元1231包括控制端、第一端和第二端,控制端连接驱动信号线1232,用于接入驱动信号,第一端连接数据存储单元122,第二端连接像素驱动模块110,当按预设顺序选通各驱动信号线1232时,对应的第二开关单元1231的第一端和第二端导通,依次将对应的灰阶数据传输至像素驱动模块110。

92.在其中一个实施例中,数据中转模块还包括数据复位单元,数据复位单元连接数据存储单元,用于在写入灰阶数据之前,响应于数据复位信号线上的数据复位信号,对数据存储单元内的存储数据进行清零。

93.同一行中各像素驱动装置的数据复位单元的数据复位信号线互连,至少一行中的

数据复位信号线与相邻的至少一行中的数据复位信号线连接。

94.与各行驱动信号线的互连类似,本技术中各行的数据复位信号线可以与相邻行的数据复位信号线互连,由此可在同步驱动多行像素单元之前,对多行的数据存储单元中的存储数据进行清零,以达到同步清零的目的。

95.一般情况下,驱动信号线对应连接的各行中,数据复位信号线也是相连的。当然,也可以将更多行的数据复位信号线相连。图7中示出了第一行的数据复位信号线和第二行的数据复位信号线相连的情形,共用数据复位信号线crst1/2。

96.由此,在同步写入灰阶数据之前,可通过数据复位信号线141对相邻行中的各数据存储单元122同步复位,效率较高。

97.在其中一个实施例中,数据复位单元包括第三开关单元,第三开关单元包括控制端、第一端和第二端,控制端连接数据复位信号线,第一端连接数据存储单元,第二端接地,当数据复位信号线被选通时,各第三开关单元的第一端和第二端导通。

98.在其中一个实施例中,数据存储单元包括存储电容,存储电容的第一端连接数据写入单元,存储电容的第二端接地。

99.在其中一个实施例中,像素驱动模块110包括像素复位信号线111、第四开关单元112和第五开关单元113。第四开关单元112包括控制端、第一端和第二端,控制端连接各数据驱动单元123,第一端连接电流源114,第二端连接像素单元130。第五开关单元113包括控制端、第一端和第二端,控制端连接像素复位信号线111,第一端连接第四开关单元112的控制端,第二端接地。

100.本实施例中,同一行中各像素驱动装置100的像素复位信号线111互连。即,同一行像素驱动装置100共享一条像素复位信号线111,当同一行的像素复位信号线111被选通时,该行中的y个像素单元130被同步复位,由此在下一帧显示之前,可对同一行的像素单元130进行同步复位,以避免上一帧子帧的残留显示对下一子帧的显示造成影响。

101.本实施例中,至少一行中的像素复位信号线与相邻的至少一行中的像素复位信号线连接。

102.与各行驱动信号线的互连类似,本技术中各行的像素复位信号线可以与相邻行的像素复位信号线互连,由此可在同步驱动多行像素单元的上一子帧点亮之后,可同步对多行的像素单元进行复位,以达到同步复位的目的。

103.一般情况下,驱动信号线对应连接的各行中,像素复位信号线也是相连的。当然,也可以将更多行的像素复位信号线相连。

104.在其中一个实施例中,同一列中各像素驱动装置100的第j个灰阶数据线互连,j的取值遍历1

‑

n中的自然数。每个像素驱动装置100均包括n条灰阶数据线,同一列中包括x个像素驱动装置100,每个像素驱动装置100的第1条灰阶数据线互连,每个像素驱动装置100的第2条灰阶数据线互连,依此类推,每个像素驱动装置100的第n条灰阶数据线互连。即,同一列中包含n条灰阶数据线,第j条灰阶数据线负责该列中各像素驱动装置100的第j个数据中转模块120的数据接入。例如,当扫描第一行像素单元130时,第一列中的第1条灰阶数据线用于接入第一行像素单元130的第1位灰阶数据,当扫描第二行像素单元130时,第一列中的第1条灰阶数据线则用于接入第二列像素单元130的第1位灰阶数据。

105.在其中一个实施例中,像素驱动系统还包括数据转换模块,数据转换模块连接各

数据中转模块,用于将n位灰阶数据由串行数据转换为并行数据,并将n位并行的灰阶数据分别发送至各像素驱动装置中的n个数据中转模块。

106.本实施例所提供的像素驱动系统与实施例一提供的像素驱动装置100属于同一发明构思,像素驱动系统中涉及到的像素驱动装置100的具体内容可参见实施例一中的详细描述,在此不再赘述。

107.实施例三

108.本实施例提供了一种像素驱动方法,应用于如实施例一提供的像素驱动装置100。

109.本实施例所提供的像素驱动方法包括以下步骤:

110.步骤s100、控制n个数据写入单元121并行写入n个灰阶数据。

111.步骤s200、将写入的n个灰阶数据存储于各自对应的数据存储单元122中。

112.步骤s300、根据预设顺序依次驱动n个数据驱动单元123,将n个灰阶数据依次传输至像素驱动模块110,以驱动像素驱动模块110点亮像素单元130。

113.由于在驱动点亮过程之前,已经将n位灰阶数据分别存储于n个数据存储单元122中,因此,在驱动点亮过程中,直接使用对应的灰阶数据即可,无需等待从灰阶数据线接入灰阶数据,由此有效减少了各子帧之间的等待时间,提高显示时间的占空比,显著提高了显示亮度。

114.在其中一个实施例中,像素驱动装置100还包括数据复位单元140,数据复位单元140连接数据存储单元122。

115.在步骤s200,即控制n个数据写入单元121并行写入n个灰阶数据的步骤之前,本实施例提供的像素驱动方法还包括:控制数据复位单元140对数据存储单元122内的存储数据进行清零。

116.在其中一个实施例中,在步骤s600,即根据预设顺序依次驱动n个数据驱动单元123,将n个灰阶数据依次传输至像素驱动模块110,以驱动像素驱动模块110点亮像素单元130的步骤中,在每一个灰阶数据传输至像素驱动模块110,点亮像素单元130达到预设时长之后,均控制像素驱动模块110熄灭像素单元130。即,当第一位灰阶数据传输至像素驱动模块110,点亮像素单元130达到t时,控制像素驱动模块110熄灭像素单元130,之后像素驱动模块110再接收第二位灰阶数据,实现第二帧显示,由此可避免上一帧的残留显示影响下一帧显示。具体地,可以通过选通像素复位信号线111,使得第五开关单元113闭合,第四开关单元112的控制端接地,第四开关单元112断开,像素单元130断开与电流源114的连接而熄灭,实现像素单元130的复位。

117.本实施例所提供的像素驱动方法与实施例一提供的像素驱动装置100属于同一发明构思,关于像素驱动方法的具体内容可参见实施例一中的详细描述,在此不再赘述。

118.实施例四

119.本实施例提供了一种像素驱动方法,应用于如实施例二提供的像素驱动系统。

120.本实施例提供的像素驱动方法包括以下步骤:

121.步骤s400、控制当前行中n*y个数据写入单元并行写入n*y个灰阶数据,并将写入的n*y个灰阶数据存储于各自对应的数据存储单元中。

122.步骤s500、控制所述当前行的关联行中n*y个数据写入单元并行写入n*y个灰阶数据,并将写入的n*y个灰阶数据存储于各自对应的数据存储单元中,其中,所述关联行中的n

条驱动信号线与当前行的n条驱动信号线对应连接。

123.步骤s600、选通当前行及其关联行中各像素驱动装置的第i个数据驱动单元对应的驱动信号线,同步驱动当前行及其关联行中各像素驱动装置的第i个数据驱动单元,将灰阶数据传输至各自对应的像素驱动模块,以驱动各像素驱动模块点亮各像素单元,其中,i的取值按照预设顺序遍历1

‑

n中的自然数。

124.步骤s700、按照上述方式依次点亮x行像素单元130。

125.本实施例中,将驱动信号线与当前行的驱动信号线相连的行称为关联行,例如,图7中第一行为当前行,第二行则为第一行的关联行。即,首先写入并存储当前行的灰阶数据,然后写入并存储关联行的灰阶数据,然后同步驱动当前行和关联行中的所有像素单元的各子帧显示,即,驱动当前行和关联行中像素单元的第1子帧显示,然后驱动当前行和关联行中像素单元的第2子帧显示,直至n个子帧显示完毕。驱动信号线相连接的相邻行之间无显示等待时间,可一定程度上减轻显示撕裂感,且由于多行共用驱动信号线,可有效减少走线数量,降低制备工艺难度。由于在驱动点亮过程之前,已经将每个像素驱动装置100对应的n位灰阶数据分别存储于n个数据存储单元122中,因此,在驱动点亮过程中,直接使用对应的灰阶数据即可,无需等待从灰阶数据线接入灰阶数据,由此有效减少了各子帧之间的等待时间,提高显示时间的占空比,显著提高了显示亮度。

126.例如,可以选通当前行及其关联行中各像素驱动装置100的第1个数据驱动单元123的驱动信号线1232,驱动当前行及其关联行中各像素驱动装置100的第1个数据驱动单元123,使得各像素驱动装置100中的第1位灰阶数据传输至像素驱动模块110中,以驱动当前行及其关联行中各像素单元130实现第一子帧的显示;然后可以选通当前行及其关联行中各像素驱动装置100的第2个数据驱动单元123的驱动信号线1232,驱动当前行及其关联行中各像素驱动装置100的第2个数据驱动单元123,使得各像素驱动装置100中的第2位灰阶数据传输至像素驱动模块110中,以驱动当前行及其关联行中各像素单元130实现第二子帧的显示;依此类推,驱动当前行及其关联行中各像素单元130实现n个子帧的同步显示。

127.在其中一个实施例中,像素驱动装置100还包括数据复位单元140,数据复位单元140连接数据存储单元122,响应于数据复位信号线上的数据复位信号,对所述数据存储单元内的存储数据进行清零,同一行中像素驱动装置100中的各数据复位单元140的数据复位信号线141互连,至少一行中的数据复位信号线与相邻的至少一行中的数据复位信号线连接。

128.在步骤s400,即控制当前行中n*y个数据写入单元并行写入n*y个灰阶数据,并将写入的n*y个灰阶数据存储于各自对应的数据存储单元中的步骤之前,本实施例提供的像素驱动方法还包括:选通当前行及其关联行的数据复位信号线,对当前行及其关联行中的各数据存储单元内的存储数据进行同步清零。

129.在其中一个实施例中,在步骤s600,即选通当前行及其关联行中各像素驱动装置的第i个数据驱动单元对应的驱动信号线,同步驱动当前行及其关联行中各像素驱动装置的第i个数据驱动单元,将灰阶数据传输至各自对应的像素驱动模块,以驱动各像素驱动模块点亮各像素单元的步骤中,在同步驱动当前行及其关联行中各像素驱动装置100的第任意个数据驱动单元123,并点亮对应的像素单元130达到预设时长之后,同步熄灭对应的像素单元130。

130.例如,当同步驱动当前行及其关联行中各像素驱动装置100的第1个数据驱动单元123,并点亮对应的像素单元130达到预设时长之后,可以驱动当前行及其关联行共用的像素复位信号线,以同步控制当前行及其关联行中各像素驱动模块110熄灭对应的像素单元130,以实现像素单元130的同步复位,从而便于进行下一帧显示。

131.本实施例所提供的像素驱动方法与实施例二提供的像素驱动系统属于同一发明构思,关于像素驱动方法的具体内容可参见实施例二中的详细描述,在此不再赘述。

132.以上所述实施例的各技术特征可以进行任意的组合,为使描述简洁,未对上述实施例中的各个技术特征所有可能的组合都进行描述,然而,只要这些技术特征的组合不存在矛盾,都应当认为是本说明书记载的范围。

133.以上所述实施例仅表达了本发明的几种实施方式,其描述较为具体和详细,但并不能因此而理解为对发明专利范围的限制。应当指出的是,对于本领域的普通技术人员来说,在不脱离本发明构思的前提下,还可以做出若干变形和改进,这些都属于本发明的保护范围。因此,本发明专利的保护范围应以所附权利要求为准。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。