1.本发明是有关于半导体结构与形成半导体结构的方法。

背景技术:

2.随着电子工业的快速发展,集成电路(integrated circuits;ics)的发展是为了实现高性能与微型化。集成电路材料与设计的技术进步已经产生了几代的集成电路,其中每一代的集成电路都具有比上一代的集成电路更小与更复杂的电路。

3.随着单一芯片上的电子元件数量快速增加,已针对某些半导体元件使用三维(three-dimensional;3d)集成电路布局、或是堆叠芯片设计,以力求克服与二维(2d)布局相关联的特征尺寸以及密度限制。一般而言,在3d集成电路设计中,两个或多个半导体晶粒(dies)是接合在一起,并且在每个晶粒间形成电性连接。一种促成芯片至芯片(chip-to-chip)电性连接的方法为通过使用硅通孔(through-silicon vias;tsvs)的方法。硅通孔为通过硅晶圆或晶粒的垂直电性连接,其允许垂直排列之电子元件的互连更为简化,从而显著降低集成电路布局的复杂性,以及缩减多芯片电路的整体尺寸。与3d集成电路设计实现的互连技术有关的一些优点包括加速资料交换、减少功率消耗以及更高的输入/输出电压密度。然而,在硅通孔与半导体晶粒之间可能发生应力问题。

技术实现要素:

4.本发明的一方面为一种效能可以被改善的半导体结构。

5.根据本发明一实施方式,一种半导体结构包括第一基板、第二基板、金属层、缓冲结构以及阻障结构。第一基板具有支撑垫。第二基板位于第一基板上。金属层位于第二基板内,且从支撑垫延伸至第二基板的顶面。缓冲结构位于第二基板内,且缓冲层被金属层围绕,其中缓冲结构的顶面低于金属层的顶面。阻障结构位于金属层与缓冲结构上。

6.在本发明一实施方式中,半导体结构进一步包括位于第二基版上的钝化层。

7.在本发明一实施方式中,阻障结构具有第一部分与第二部分,第一部分位于钝化层上,第二部分位于金属层与阻障结构上。

8.在本发明一实施方式中,半导体结构进一步包括位于第二基板的侧壁上的隔离层。

9.在本发明一实施方式中,半导体结构进一步包括第一阻障层与第二阻障层。第一阻障层位于支撑垫与隔离层上。第二阻障层位于金属层上。

10.在本发明一实施方式中,半导体结构进一步包括位于阻障结构上的凸块。

11.在本发明一实施方式中,金属层的一部分位于缓冲结构与第二基板之间。

12.在本发明一实施方式中,第一基板在其上包括内连接结构,并且支撑垫位于内连接结构中。

13.在本发明一实施方式中,缓冲结构由有机材料制成。

14.在本发明一实施方式中,缓冲结构的顶面低于第二基板的顶面。

15.本发明的另一方面为一种形成半导体结构的方法。

16.根据本发明一实施方式,形成半导体结构的方法包括以下步骤。接合第一基板与第二基板,其中第一基板具有支撑垫。蚀刻第二基板,以形成开口,其中支撑垫通过开口而暴露。在支撑垫与围绕开口的第二基板的侧壁上形成金属层。在金属层上形成缓冲结构。蚀刻缓冲结构,使得缓冲结构的顶面低于金属层的顶面。在金属层与缓冲结构上形成阻障结构。

17.在本发明一实施方式中,形成半导体结构的方法进一步包括在蚀刻第二基板之前,在第二基板上形成钝化层。

18.在本发明一实施方式中,形成半导体结构的方法进一步包括蚀刻钝化层,以形成开口,其中钝化层的开口连通于第二基板的开口,且比第二基板的开口宽。

19.在本发明一实施方式中,形成半导体结构的方法进一步包括在形成金属层之前,在第二基板的侧壁上形成隔离层,使得金属层形成于隔离层上。

20.在本发明一实施方式中,形成半导体结构的方法进一步包括以下步骤。在隔离层与支撑垫上形成第一阻障层。在金属层上形成第二阻障层。

21.在本发明一实施方式中,蚀刻缓冲结构,使得缓冲结构的顶面低于第二基板的顶面。

22.在本发明一实施方式中,形成半导体结构的方法进一步包括在阻障结构上形成凸块。

23.在前述的实施方式中,因为缓冲结构位于第二基板内且被金属层围绕,可以达到补偿应力(stress compensation)的效果。因此,半导体结构的效能可以被改善。

24.应当了解前面的一般说明和以下的详细说明都仅是示例,并且旨在提供对本发明的进一步解释。

附图说明

25.本发明的各方面可从以下实施方式的详细说明及随附的附图理解。

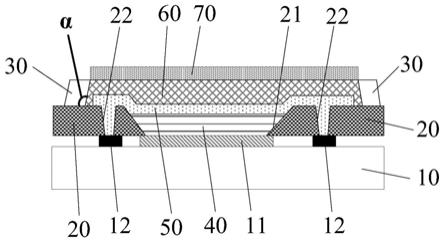

26.图1绘示根据本发明一实施方式的半导体结构的剖面图。

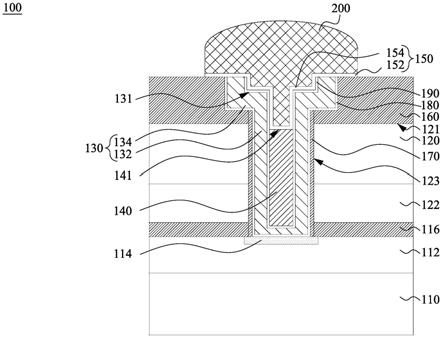

27.图2至图15绘示根据本发明一实施方式在各个阶段形成半导体结构的方法的剖面图。

28.主要附图标记说明:

29.100-半导体结构,110-第一基板,112-第一内连接结构,114-支撑垫,116-介电层,120-第二基板,121-顶面,122-第二内连接结构,123-侧壁,130-金属层,131-顶面,132-第一部分,134-第二部分,140-缓冲结构,141-顶面,141a-顶面,150-阻障结构,150a-第三阻障层,151-部分,152-第一部分,154-第二部分,160-钝化层,170-隔离层,180-第一阻障层,190-第二阻障层,200-凸块,210-图案化遮罩特征,210a-光阻层,o-开口,o1-开口,o2-开口,o3-开口,t1-厚度,t2-厚度。

具体实施方式

30.以下将以附图公开本发明的多个实施方式,为明确说明,许多实务上的细节将在以下叙述中一并说明。然而,应了解到,这些实务上的细节不应用以限制本发明。也就是说,

在本发明部分实施方式中,这些实务上的细节是非必要的。此外,为简化附图起见,一些公知惯用的结构与元件在附图中将以简单示意的方式绘示。

31.图1绘示根据本发明一些实施方式的半导体结构100的剖面图。参阅图1,半导体结构100包括第一基板110、第二基板120、金属层130、缓冲结构140以及阻障结构150。第一基板110具有第一内连接结构112与支撑垫114。第二基板120设置于第一基板110上。金属层130设置于第二基板120内,且从支撑垫114延伸到第二基板120的顶面121。缓冲结构140设置于第二基板120内,且被金属层130围绕,其中缓冲结构140的顶面141低于金属层130的顶面131。阻障结构150设置于金属层130与缓冲结构140上。由于金属层130(例如在一些情况下为铜)与第二基板120(例如在一些情况下为硅)之间的热膨胀系数(coefficient of thermal expansion;cte)不匹配,因此缓冲结构140有助于补偿及平衡金属层130与第二基板120之间的热膨胀系数(cte)。因此,可以实现补偿应力的效果,并且可以改善半导体结构100的性能。再者,设置于金属层130上的缓冲结构140可以节省金属层130的材料,从而可以降低制造成本。

32.第二基板120具有第二内连接结构122。在一些实施方式中,第二内连接结构122可包括一个或多个主动及/或被动元件。在其他的实施方式中,第二内连接结构122可以包括一个或多个金属化层。

33.第二基板120具有第二内连接结构122。在一些实施方式中,第二内连接结构122可包括一个或多个主动及/或被动元件。在其他的实施方式中,第二内连接结构122可以包括一个或多个金属化层。

34.在一些实施方式中,第一基板110及/或第二基板120可以是硅基板。在一些其他的实施方式中,第一基板110及/或第二基板120可包括其他半导体元素,例如:锗(germanium),或包括半导体化合物,例如:碳化硅(silicon carbide)、砷化镓(gallium arsenic)、磷化镓(gallium phosphide)、磷化铟(indium phosphide)、砷化铟(indium arsenic)、及/或锑化铟(indium antimonide),或其他半导体合金,例如:硅锗(sige)、磷化砷镓(gaasp)、砷化铟铝(alinas)、砷化镓铝(algaas)、砷化铟镓(gainas)、磷化铟镓(gainp)、及/或磷砷化铟镓(gainasp),以及以上之任意组合。

35.在一些实施方式中,第一基板110与第二基板120可分别在其上包括介电层116。详细来说,介电层116可设置于第一基板110的第一内连接结构112与第二基板120的第二内连接结构122之间。在一些实施方式中,介电层116可以包括单层或多层。介电层116可以由氧化硅(sio2)、氮化硅(sin)、氧氮化硅(sion)或其他适当的材料制成。

36.在一些实施方式中,钝化层160设置于第二基板120上。钝化层160可以由氧化硅(sio2)或其他适当的材料制成。

37.在一些实施方式中,阻障结构150具有位于钝化层160上的第一部分152以及位于金属层130与缓冲结构140上的第二部分154。换句话说,阻障结构150覆盖金属层130、缓冲结构140以及钝化层160的一部分,而钝化层160的其他部分被暴露。在一些实施方式中,阻障结构150可以由钛(ti)、氮化钛(tin)、钽(ta)、氮化钽(tan)、氮化钨(wn)、硅化钨(wsi)或其他适当的材料制成。

38.在一些实施方式中,金属层130具有第一部份132与位于第一部分132上的第二部分134。金属层130的第一部分132位于缓冲结构140与第二基板120之间,并且金属层130的

第二部分134位于阻障结构150与钝化层160之间。在一些实施方式中,金属层130可以由铜(cu)或其他适当的材料制成。

39.在一些实施方式中,隔离层170设置于第二基板120的侧壁123上。换句话说,隔离层170设置于第二基板120与金属层130之间。隔离层170可以从介电层116延伸到钝化层160。举例来说,隔离层170的顶面高于缓冲结构140的顶面141。隔离层170可以由氧化硅(sio2)或其他适当的材料制成。在一些实施方式中,钝化层160与隔离层170可以由相同的材料制成,例如氧化硅(sio2)。

40.在一些实施方式中,半导体结构100进一步包括第一阻障层180与第二阻障层190。第一阻障层180设置于支撑垫114与隔离层170上。详细来说,第一阻障层180设置于支撑垫114上,并且从介电层116延伸到钝化层160。换句话说,第一阻障层180接触于支撑垫114、金属层130、隔离层170以及钝化层160。第二阻障层190设置于金属层130上。换句话说,第二阻障层190设置于金属层130与缓冲结构140之间,并且设置于金属层130与阻障结构150之间。

41.在一些实施方式中,缓冲结构140被第二阻障层190围绕。缓冲结构140接触于与阻障结构150与第二阻障层190。在本实施方式中,金属层130、缓冲结构140、第一阻障层180以及第二阻障层190可视为硅通孔(through-silicon via;tsv)。缓冲结构140的顶面141低于第二基板120的顶面121。在一些实施方式中,缓冲结构140可以由有机材料制成。

42.在一些实施方式中,半导体结构100进一步包括位于阻障结构150的凸块200。阻障结构150设置于凸块200与金属层130之间。在一些实施方式中,凸块200可以是金属凸块。凸块200可以由锡(sn)或其他适当的导电材料制成。例如,凸块200可以是焊球。

43.图2至图15绘示根据本发明一实施方式在各个阶段形成图1的半导体结构100的方法的剖面图。

44.参阅图2与图3。将第一基板110与第二基板120接合在一起。如图3所示,在将第二基板120结合于第一基板110上之后,介电层116位于第一内连接结构112与第二内连接结构122之间。第一基板110与第二基板120可以通过使用熔融接合(fusion bonding)技术接合在一起。

45.参阅图3与图4。在第一基板110与第二基板120接合在一起之后,减薄第二基板120。举例来说,在图3中的第二基板120的厚度t1大于在图4中的第二基板120的厚度t2。在一些实施方式中,在第二基板120的顶面上执行研磨工艺,以减薄第二基板120。

46.参阅图5。钝化层160形成于第二基板120之上。详细来说,钝化层160可通过例如化学气相沉积(cvd)、物理气相沉积(pvd)或其他适当的沉积技术来沉积于第二基板120之上。在一些实施方式中,钝化层160可以由有机材料制成,例如苯并环丁烯(bcb)或其他适当的材料。在其他的实施方式中,钝化层160可以由无机材料制成,例如氧化硅(sio2)、氮化硅(sin)或其他适当的材料。举例来说,钝化层160与介电层116可以由相同的材料制成。

47.参阅图6。在形成钝化层160之后,蚀刻第二基板120与钝化层160,以形成开口o。详细来说,开口o具有开口o1与开口o2,其中开口o2连通于开口o1且比开口o1宽。蚀刻第二基板120以形成开口o1,并且第一基板110的支撑垫114通过开口o1而暴露。蚀刻钝化层160以形成开口o2,并且钝化层160的侧壁通过开口o2而暴露。在一些实施方式中,开口o1与开口o2可以通过大马士革镶嵌(damascene)工艺而形成。举例来说,可以在钝化层160上形成第一图案化遮罩,然后使用第一图案化遮罩对钝化层160进行蚀刻,以形成开口o2。而后,移除

第一图案化遮罩,并且在钝化层160上形成第二图案化遮罩。钝化层160与第二基板120被蚀刻,以形成连通于开口o1的开口o2。在一些实施方式中,蚀刻第二基板120,以形成开口o1,使得第二基板120的侧壁123被暴露。

48.在形成开口o1与开口o2之后,在第二基板120的侧壁123上形成隔离层170。详细来说,隔离层170形成于钝化层160、第二基板120的侧壁123与支撑垫114之上。换句话说,隔离层170覆盖钝化层160与支撑垫114。在一些实施方式中,隔离层170可以通过物理气相沉积(pvd)、化学气相沉积(cvd)、其他适当的工艺或其组合而形成。

49.在形成隔离层170之后,移除钝化层160与支撑垫114上的隔离层170,从而保留第二基板120的侧壁123上的隔离层170。换句话说,支撑垫114通过开口o(开口o1与开口o2)而暴露。

50.参阅图7。在支撑垫114与围绕开口o1的第二基板120的侧壁123上形成金属层130。详细来说,在隔离层170上形成金属层130。在一些实施方式中,在形成金属层130之前,在隔离层170与支撑垫114上形成第一阻障层180。而后,在第一阻障层180上共形地(conformally)形成金属层130。在一些实施方式中,在形成金属层130之后,在金属层130上共形地形成第二阻障层190。

51.在一些实施方式中,在第一阻障层180、金属层130以及第二阻障层190形成之后,图6的开口o的尺寸会减小为剩余的开口o3。在一些实施方式中,第一阻障层180与第二阻障层190可以由相同的材料制成。举例来说,第一阻障层180与第二阻障层190可以由钛(ti)、氮化钛(tin)、钽(ta)、氮化钽(tan)、氮化钨(wn)、硅化钨(wsi)或其他适当的材料制成。

52.参阅图7与图8。在金属层130上形成缓冲结构140。换句话说,剩余的开口o3被缓冲结构140填充。再换言之,缓冲结构140覆盖第二阻障层190。在一些实施方式中,缓冲结构140可以通过旋涂(spin-coating)工艺或其他适当的工艺在第二阻障层190上形成。在一些实施方式中,缓冲结构140可以由可流动的有机材料制成,例如旋涂玻璃(spin-on glasses;sogs)、旋涂介电层(spin-on dielectrics;sods),或其他适当的材料。

53.参阅图9。执行平坦化工艺,以移除钝化层160上方的多余材料。详细来说,通过例如化学机械研磨(cmp)等的平坦化工艺,移除缓冲结构140、第二阻障层190、金属层130以及第一阻障层180的一部分。在执行平坦化工艺之后,缓冲结构140的顶面141a被暴露。

54.参阅图10。蚀刻缓冲结构140,使得缓冲结构140的顶面141低于金属层130的顶面131。换句话说,在图10中的缓冲结构140的顶面141低于在图9中的缓冲结构140的顶面141a。在一些实施方式中,在图9中的平坦化工艺与在图10中的蚀刻工艺可以是通过使用一蚀刻工艺来平坦化与回蚀缓冲结构140。在一些实施方式中,执行蚀刻缓冲结构140,使得缓冲结构140的顶面141低于第二基板120的顶面121。如此一来,凸块200(参阅图1)与第二阻障层190之间的接触区域可以在随后的工艺中增加。

55.参阅图11。在金属层130与缓冲结构140上形成第三阻障层150a。换句话说,第三阻障层150a覆盖钝化层160、第一阻障层180、金属层130、第二阻障层190,以及缓冲结构140。第三阻障层150a可以通过例如化学气相沉积(cvd)、物理气相沉积(pvd)或其他适当的沉积技术形成在金属层130与缓冲结构140之上。在一些实施方式中,第一阻障层180、第二阻障层190以及第三阻障层150a可以由相同的材料制成。

56.参阅图12。在第三阻障层150a上形成光阻层210a。换句话说,光阻层210a形成于图

11的结构之上。在一些实施方式中,形成光阻层210a的方法可以包括在第三阻障层150a之上形成电浆增强的四乙氧基硅烷(peteos)膜。在一些实施方式中,光阻层210a可以包括有机材料,例如旋涂碳(spin-on carbon;soc)材料,或其他适当的材料。

57.参阅图12与图13。图案化光阻层210a,以形成图案化遮罩特征210,使得第三阻障层150a未被图案化遮罩特征210覆盖的部分151被暴露。光阻层210a可以通过使用显影技术来执行图案化。

58.参阅图13与图14,通过使用图案化遮罩特征210来蚀刻第三阻障层150a的部分151,以形成阻障结构150。此蚀刻工艺导致钝化层160被暴露。

59.参阅图14与图15,移除图案化遮罩特征210。在一些实施方示中,移除图案化遮罩特征210可以通过使用光阻剥离工艺,例如灰化(ashing)工艺、蚀刻工艺或其他适当的工艺。

60.回到图1。在移除图14的图案化遮罩特征210之后,在阻障结构150上形成凸块200。详细来说,凸块200可以包括底部与位于底部上的顶部,其中底部被金属层130围绕,并且顶部从钝化层160凸出。凸块200可以通过执行无电镀工艺(electroless plating process)而形成。因此,可以获得如图1绘示的半导体结构100。

61.虽然本发明已经将实施方式详细地公开如上,然而其他的实施方式也是可能的,并非用以限定本发明。因此,前述权利要求的精神及其范围不应仅限于本发明实施方式的说明。

62.本领域任何技术人员,在不脱离本发明的精神和范围内,当可作各种的改变或替换,因此所有的这些改变或替换都应涵盖于本发明权利要求的保护范围之内。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。