一种通过调整dti钨阻挡层厚度改善bsirts水平的方法

技术领域

1.本发明涉及半导体技术领域,特别是涉及一种通过调整dti钨阻挡层厚度改善bsirts水平的方法。

背景技术:

2.背面照明bsi(backsideilluminatedcis)是将硅片减薄后,在光电二极管背面搭建cf及microlens,光线由背面射入,增大了光电元件感光面积,减少了光线经过布线时的损失,可以大幅提高cis在弱光环境下的感光能力。bsi深沟槽隔离技术(deeptrenchisolation,dti)技术:硅片减薄后,为了防止串扰,需要在光电二极管之间采用dti技术,可大幅降低像素之间的串扰,提高成像质量。

3.rts(随机电报噪声):是表征cis性能的一个重要参数,它是一个随机过程,在cis中,rts噪声会在本该是黑色的地方产生错误的白点,严重影响成像质量;rts主要来源为暗电流(darkcurrent)。钨阻挡氧化层(wblockoxide)一般在dti中采用w填充,wcmp或者刻蚀后表面需沉积一层氧化阻挡层,对dti进行隔离和保护。钨氧化阻挡层的厚度和质量对bsi成像质量有很大的影响。

4.现有的wblockoxide沉积工艺为等离子体增强化学气相沉积法(pevcd)。氧化膜的性质,如厚度,h含量,应力等都会影响界面缺陷的种类和数量,而界面缺陷(如悬挂键)会随机捕获和释放载流子,表现为rts。例如,不同厚度的氧化膜,其应力水平不同,而应力会弱化si

‑

o/si

‑

si键,使其断裂,产生陷阱,进而影响rts。

技术实现要素:

5.鉴于以上所述现有技术的缺点,本发明的目的在于提供一种通过调整dti钨阻挡层厚度改善bsirts水平的方法,用于解决现有技术中cis随机电报噪声水平低下导致cis芯片成像质量低下的问题。

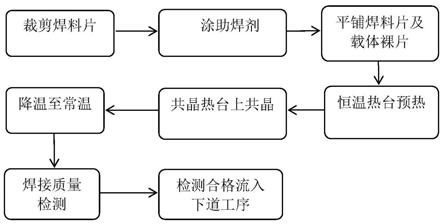

6.为实现上述目的及其他相关目的,本发明提供一种通过调整dti钨阻挡层厚度改善bsirts水平的方法,

7.步骤一、提供硅基底,在所述硅基底上形成深沟槽;

8.步骤二、在所述深沟槽中依次覆盖第一氧化层、hk介质层、第二氧化层、钨粘着层;

9.步骤三、在所述硅基底上沉积钨以填充所述深沟槽;

10.步骤四、刻蚀去除所述硅基底表面的钨;

11.步骤五、在填充满钨的深沟槽上表面通过pecvd的方法沉积厚度为的氧化阻挡层。

12.优选地,步骤一中通过等离子体刻蚀和湿法刻蚀相结合的方式在所述硅基底上形成所述深沟槽。

13.优选地,步骤三中通过物理气相沉积的方法在所述深沟槽中填充钨。

14.优选地,步骤四中通过等离子体刻蚀去除所述硅基底表面的钨。

(chmical oxide)、hk介质层(high

‑

k)、第二氧化层(liner oxide)、钨粘着层(w gluelayer)依次覆盖在所述深沟槽中,也就是说,所述第一氧化层(chmical oxide)直接覆盖在所述深沟槽的表面(底部和侧壁),之后沉积的所述hk介质层(high

‑

k)覆盖在所述第一氧化层(chmical oxide)的表面,接着沉积的所述第二氧化层(liner oxide)覆盖在所述hk 介质层(high

‑

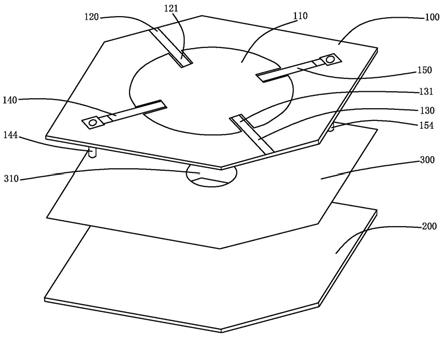

k)上,之后沉积的所述钨粘着层(w glue layer)覆盖在所述所述第二氧化层 (liner oxide)上。如图1所示,本实施例中在所述深沟槽中沉积所述第一氧化层、hk介质层、第二氧化层、钨粘着层时,所述深沟槽之外两侧的硅基底上表面亦被所述第一氧化层、 hk介质层、第二氧化层、钨粘着层覆盖。

33.步骤三、在所述硅基底上沉积钨以填充所述深沟槽;如图1所示,该步骤三在所述硅基底上沉积钨(w)以填充所述深沟槽,也就是说在所述深沟槽中填充钨,同时,所述硅基底上表面会由于在深沟槽内沉积钨时溢出一部分钨,形成如图1所示的所述填充满钨的所述深沟槽上表面覆盖有钨。

34.本发明进一步地,本实施例的步骤三中通过物理气相沉积(pvd)的方法在所述深沟槽中填充钨。

35.步骤四、刻蚀去除所述硅基底表面的钨;如图2所示,图2显示为本发明中刻蚀去除所述硅基上表面的钨后的深沟槽结构示意图。本实施例中,由于所述深沟槽之外两侧的所述硅基底上表面也沉积有所述第一氧化层、hk介质层、第二氧化层、钨粘着层,因此该步骤四中刻蚀去除所述硅基底上表面钨至露出所述钨粘着层为止。

36.本发明进一步地,本实施例的步骤四中通过等离子体刻蚀(plasma etch)去除所述硅基底表面的钨。

37.步骤五、在填充满钨的深沟槽上表面通过pecvd的方法沉积厚度为的氧化阻挡层。如图3所示,图3显示为本发明中在填充满钨的深沟槽上沉积氧化阻挡层后的结构示意图。该步骤五中在填充满钨的深沟槽上表面通过pecvd的方法沉积厚度为的氧化阻挡层(w block oxide)。

38.本发明进一步地,本实施例的步骤五中沉积所述氧化阻挡层的厚度为或本发明再进一步地,本实施例的步骤五中沉积所述氧化阻挡层的厚度为

39.本发明进一步地,本实施例的步骤五中通过改变pecvd的沉积时间来调整沉积的所述氧化阻挡层的厚度。

40.本发明进一步地,本实施例的该方法用于55nm的bis工艺节点。

41.如图4和图5所示,图4显示为不同厚度的氧化阻挡层的rts曲线图。其中每一厚度(图4显示为不同厚度的氧化阻挡层的rts曲线图。其中每一厚度()的氧化阻挡层(block oxide)包含两条曲线,分别对应p50和p97 参数。图5显示为不同厚度的氧化阻挡层的暗电流曲线图。其中每一厚度(参数。图5显示为不同厚度的氧化阻挡层的暗电流曲线图。其中每一厚度()的氧化阻挡层(block oxide)包含两条曲线,分别对应p50和p97参数。

42.如图6和图7所示,图6显示为本发明中两个p参数下不同厚度氧化阻挡层对应的rts 曲线。图7显示为本发明中两个p参数下不同厚度氧化阻挡层对应的暗电流曲线。由此可见,找到最优工艺条件,显著降低了芯片rts的整体水平,p50和p97参数改善20%以上;同

时芯片白点像素和暗电流水平(dc,dark current)也大幅降低;芯片的噪声水平得到显著改善,提高了芯片良率,在相同成本下获得更多利润。

43.综上所述,显著降低了芯片rts的整体水平,p50和p97参数改善20%以上;同时芯片白点像素和暗电流水平也大幅降低;芯片的噪声水平得到显著改善,提高了芯片良率,在相同成本下获得更多利润。所以,本发明有效克服了现有技术中的种种缺点而具高度产业利用价值。

44.上述实施例仅例示性说明本发明的原理及其功效,而非用于限制本发明。任何熟悉此技术的人士皆可在不违背本发明的精神及范畴下,对上述实施例进行修饰或改变。因此,举凡所属技术领域中具有通常知识者在未脱离本发明所揭示的精神与技术思想下所完成的一切等效修饰或改变,仍应由本发明的权利要求所涵盖。

技术特征:

1.一种通过调整dti钨阻挡层厚度改善bsi rts水平的方法,其特征在于,至少包括:步骤一、提供硅基底,在所述硅基底上形成深沟槽;步骤二、在所述深沟槽中依次覆盖第一氧化层、hk介质层、第二氧化层、钨粘着层;步骤三、在所述硅基底上沉积钨以填充所述深沟槽;步骤四、刻蚀去除所述硅基底表面的钨;步骤五、在填充满钨的深沟槽上表面通过pecvd的方法沉积厚度为的氧化阻挡层。2.根据权利要求1所述的通过调整dti钨阻挡层厚度改善bsi rts水平的方法,其特征在于:步骤一中通过等离子体刻蚀和湿法刻蚀相结合的方式在所述硅基底上形成所述深沟槽。3.根据权利要求1所述的通过调整dti钨阻挡层厚度改善bsi rts水平的方法,其特征在于:步骤三中通过物理气相沉积的方法在所述深沟槽中填充钨。4.根据权利要求1所述的通过调整dti钨阻挡层厚度改善bsi rts水平的方法,其特征在于:步骤四中通过等离子体刻蚀去除所述硅基底表面的钨。5.根据权利要求1所述的通过调整dti钨阻挡层厚度改善bsi rts水平的方法,其特征在于:步骤五中沉积所述氧化阻挡层的厚度为或6.根据权利要求1所述的通过调整dti钨阻挡层厚度改善bsi rts水平的方法,其特征在于:步骤五中沉积所述氧化阻挡层的厚度为7.根据权利要求1所述的通过调整dti钨阻挡层厚度改善bsi rts水平的方法,其特征在于:步骤五中通过改变pecvd的沉积时间来调整沉积的所述氧化阻挡层的厚度。8.根据权利要求1所述的通过调整dti钨阻挡层厚度改善bsi rts水平的方法,其特征在于:该方法用于55nm的bis工艺节点。

技术总结

本发明提供一种通过调整DTI钨阻挡层厚度改善BSI RTS水平的方法,提供硅基底,在硅基底上形成深沟槽;在深沟槽中依次覆盖第一氧化层、HK介质层、第二氧化层、钨粘着层;在硅基底上沉积钨以填充深沟槽;刻蚀去除硅基底表面的钨;在填充满钨的深沟槽上表面通过PECVD的方法沉积厚度为的氧化阻挡层。显著降低了芯片RTS的整体水平,P50和P97参数改善20%以上;同时芯片白点像素和暗电流水平也大幅降低;芯片的噪声水平得到显著改善,提高了芯片良率,在相同成本下获得更多利润。在相同成本下获得更多利润。在相同成本下获得更多利润。

技术研发人员:赵春山 康柏 张武志 曹亚民 周维

受保护的技术使用者:上海华力集成电路制造有限公司

技术研发日:2021.07.13

技术公布日:2021/11/14

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。