1.本技术涉及计算机技术领域,特别是涉及一种内存信息获取方法、装置、系统、电子设备及可读存储介质。

背景技术:

2.随着大数据、云计算、人工智能等技术的成熟以及被普及应用在日常生活工作,人工智能时代到来。在人工智能时代,服务器将会广泛地应用于各领域中,普通的服务器是以cpu(central processing unit,中央处理器)为算力的提供者,采用的是串行架构,在逻辑计算、浮点型计算等方面很擅长。因为在进行逻辑判断时需要大量的分支跳转处理,使得cpu的结构复杂,而算力的提升主要依靠堆砌更多的核心数来实现。但是在大数据、云计算、人工智能以及物联网等网络技术的应用,充斥在互联网中的数据呈现几何倍数的增长,这对以cpu为主要算力来源的传统服务提出了严重的考验,并且在目前cpu的制程工艺、单个cpu的核心数已经接近极限,但数据的增加却还在持续,因此必须提升服务器的数据处理能力。

3.目前,服务器行业竞争日趋激烈,服务器的基本功能,各大生成厂商都可以实现。服务器厂家只能从成本、客户体验等方面提升自己的产品优势,增加产品竞争力。如果说服务器是网络数据的核心,那么服务器硬盘就是这个核心的数据仓库,所有的软件和用户数据都存储在这里。在云计算、大数据时代,海量的数据需要存储和计算,数据中心的服务器部署密度越来越大。在数据量暴增的时代,数据时时刻刻都在被分类存储和计算,这就对数据中心服务器的长期稳定性和可靠性要求越来越高;dimm(dual

‑

inline

‑

memory

‑

modules,双列直插式存储模块)作为服务器数据存储的核心,它与普通pc(personal computer,个人计算机)内存在外观和结构上没有什么明显实质性的区别,主要是在内存上引入了一些新的特有的技术,如ecc(error correcting code,错误检查和纠正)技术、chipkill内存技术、热插拔技术等,具有极高的稳定性和纠错性能。

4.可以理解的是,bmc(baseboard management controller,主板理控制器)作为服务器的管理者,其负责监控整个系统的运行状态,用户跟服务器之间的交互都是通过bmc来实现。为了保证服务器的正常运行,bmc需要获取内存如dimm的相关信息。spd(serial presence detect,配置串行探测)是内存模组上面的一个可擦写的eeprom(electrically erasable programmable read only memory,电擦除可编程只读存储器),里面记录了该内存的许多重要信息,也即spd是一组关于内存模组的配置信息,诸如内存的芯片及模组厂商、工作频率、工作电压、速度、容量、电压、行地址、列地址带宽、各种主要操作时序等参数。spd信息一般都是在出厂前,由内存模组制造商根据内存芯片的实际性能写入到容量为256字节的eeprom芯片中。实际上在spd中,jedec规定的标准信息只用了128个字节,剩余的128字节属于厂商自己的专用区。一般的,一个字节至少对应一种参数,有的参数需要多个字节来表述如产品续列号,生产商在jedec组织中的代码。也就是需要获取spd信息。

5.相关技术的内部结构连接如下图1所示,spd信息可以保证dimm稳定上电,当主板

开机时,bios进入post(power on self test,上电自检)阶段,通过spd给ddr(double data rate,双倍速率)上电,当bios post结束以后,上电完成。dimm的spd总线直连到cpu,cpu通过spd总线获取dimm的温度、型号等相关信息。pch(platform controller hub,集成南桥)与cpu之间的dmi(direct media interface,直接媒体接口)总线用来带内传递cpu获取的dimm信息,同时将该信息存放入pch内部的me(management engine,管理引擎)中,bmc与pch之间预留的sm

‑

link0(system management link)是bmc与me之间的通道,bmc通过smlink0获取到dimm的信息。按照现有方案,bmc要获取dimm信息需要通过me,如果me挂死,则bmc则无法获取到dimm的相关信息。换句话说,由于spd直连到cpu,如果要获取dimm的信息就只能通过带内获取。这种带内获取方式实现机制比较繁琐,时效性不强,bmc无法准确快速地读取dimm相关信息,还会影响debug也即计算机排除故障的效率,为问题定位以及板卡调试增加了一定的难度。

6.鉴于此,如何在保证内存可以正常上电的基础上,实现bmc快速有效地获取系统内存信息,且不影响计算机排除故障效率,是所属领域技术人员需要解决的技术问题。

技术实现要素:

7.本技术提供了一种内存信息获取方法、装置、系统、电子设备及可读存储介质,在保证内存可以正常上电的基础上可以实现bmc快速有效地获取系统内存信息,且不影响计算机排除故障的效率。

8.为解决上述技术问题,本发明实施例提供以下技术方案:

9.本发明实施例第一方面提供了一种内存信息获取系统,包括中央处理器,内存、南桥芯片和基板管理控制器,所述南桥芯片与所述基板管理控制器相连,还包括数据选择器、通道控制器和指令触发器;

10.所述数据选择器分别与所述中央处理器、所述基板管理控制器和所述内存相连,所述指令触发器与所述基板管理控制器相连,所述通道控制器分别与所述数据选择器和所述南桥芯片相连;

11.所述基板管理控制器接收到所述指令触发器传入的内存信息获取指令,向所述南桥芯片发送内存上电监控指令;当确定所述内存完成上电,将通道切换指令通过所述南桥芯片发送给所述通道控制器;所述通道控制器通过控制所述数据选择器将所述内存与所述中央处理器的第一连接通道切换至所述内存与所述基板管理控制器的第二连接通道。

12.可选的,所述指令触发器包括第一状态引脚和第二状态引脚,设置在系统外部且由用户控制;

13.所述第一状态引脚用于标识用户不获取内存信息;所述第二状态引脚用于标识用户获取内存信息;

14.所述指令触发器检测到所述第二状态引脚连通,向所述基板管理控制器传入所述内存信息获取指令。

15.可选的,所述通道控制器为cpld或fpga或单片机。

16.可选的,所述基板管理控制器还用于当通过所述第二连接通道读取内存信息完成后,向所述南桥芯片发送信息读取完成指令,以使所述通道控制器在接收到所述南桥芯片的所述信息读取完成指令之后,控制所述数据选择器将所述第二连接通道切换为第一连接

通道。

17.本发明实施例第二方面提供了一种内存信息获取方法,应用于如前任意一项所述内存信息获取系统中的基板管理控制器,包括:

18.当接收到内存信息获取指令,发送内存上电监控指令;

19.当确定内存完成上电,发送通道切换指令,以基于所述通道切换指令控制内存从当前与中央处理器的第一连接通道切换至与所述基板管理控制器的第二连接通道上;

20.当检测到成功切换至所述第二连接通道,读取内存信息。

21.本发明实施例第三方面提供了一种内存信息获取装置,应用于如前任意一项所述内存信息获取系统中的基板管理控制器,包括:

22.上电监控模块,用于当接收到内存信息获取指令,发送内存上电监控指令;

23.连接通道且模块,用于当确定内存完成上电,发送通道切换指令,以基于所述通道切换指令控制内存当前从与中央处理器的连接通道切换至与基板管理控制器的连接通道上;

24.信息读取模块,用于当检测到成功切换至所述第二连接通道,读取内存信息。

25.本发明实施例第四方面提供了一种内存信息获取方法,应用于如前任意一项所述内存信息获取系统中的通道控制器,包括:

26.接收通道切换指令;所述通道切换指令为内存上电完成之后,基板管理控制器通过南桥芯片发送给所述通道控制器;

27.控制数据选择器由第一连接通道切换至第二连接通道,以使所述基板管理控制器基于所述第二连接通道读取内存信息;所述第一连接通道为内存从与中央处理器的连接通道;所述第二连接通道为所述基板管理控制器与所述内存的连接通道。

28.本发明实施例第五方面提供了一种内存信息获取装置,应用于如前任意一项所述内存信息获取系统中的通道控制器,包括:

29.指令接收模块,用于接收通道切换指令;所述通道切换指令为内存上电完成之后,基板管理控制器通过南桥芯片发送给所述通道控制器;

30.通道切换模块,用于控制数据选择器由第一连接通道切换至第二连接通道,以使所述基板管理控制器基于所述第二连接通道读取内存信息;所述第一连接通道为内存从与中央处理器的连接通道;所述第二连接通道为所述基板管理控制器与所述内存的连接通道。

31.本发明实施例还提供了一种电子设备,包括处理器和存储器,所述处理器用于执行存储器中存储的计算机程序时实现如前任一项所述内存信息获取方法的步骤。

32.本发明实施例最后还提供了一种可读存储介质,所述可读存储介质上存储有计算机程序,所述计算机程序被处理器执行时实现如前任一项所述内存信息获取方法的步骤。

33.本技术提供的技术方案的优点在于,在系统开机过程中,内存需要上电才能正常工作,为了不影响内存上电,再不需要获取内存信息时,默认内存与cpu相连,这样便可以保证内存正常上电。当用户需要获取内存信息时,通过指令触发器将获取内存的指令发送给bmc以在内存上电完成之后触发通道切换指令发送至通道控制器,从而将内存与bmc连接通道连通,这样bmc便可直接到内存中读取所需内存信息,保证bmc快速有效地获取到dimm的spd信息,有利于提高服务器运营效率,实现了服务器运行的稳定性,可以满足客户多样化

的产品需求。

34.此外,本发明实施例还针对内存信息获取系统提供了内存信息获取方法及各自相应的实现装置、电子设备及可读存储介质,所述方法、装置、电子设备及可读存储介质具有相应的优点。

35.应当理解的是,以上的一般描述和后文的细节描述仅是示例性的,并不能限制本公开。

附图说明

36.为了更清楚的说明本发明实施例或相关技术的技术方案,下面将对实施例或相关技术描述中所需要使用的附图作简单的介绍,显而易见地,下面描述中的附图仅仅是本发明的一些实施例,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其他的附图。

37.图1为本发明实施例提供的相关技术中一个示例性应用场景的框架示意图;

38.图2为本发明实施例提供的内存信息获取系统的一种具体实施方式结构图;

39.图3为本发明实施例提供的内存信息获取系统的另一种具体实施方式结构图;

40.图4为本发明实施例提供的一种内存信息获取方法的流程示意图;

41.图5为本发明实施例提供的另一种内存信息获取方法的流程示意图;

42.图6为本发明实施例提供的内存信息获取装置的一种具体实施方式结构图;

43.图7为本发明实施例提供的内存信息获取装置的一种具体实施方式结构图;

44.图8为本发明实施例提供的电子设备的一种具体实施方式结构图。

具体实施方式

45.为了使本技术领域的人员更好地理解本发明方案,下面结合附图和具体实施方式对本发明作进一步的详细说明。显然,所描述的实施例仅仅是本发明一部分实施例,而不是全部的实施例。基于本发明中的实施例,本领域普通技术人员在没有做出创造性劳动前提下所获得的所有其他实施例,都属于本发明保护的范围。

46.本技术的说明书和权利要求书及上述附图中的术语“第一”、“第二”、“第三”“第四”等是用于区别不同的对象,而不是用于描述特定的顺序。此外术语“包括”和“具有”以及他们任何变形,意图在于覆盖不排他的包含。例如包含了一系列步骤或单元的过程、方法、系统、产品或设备没有限定于已列出的步骤或单元,而是可包括没有列出的步骤或单元。

47.在介绍了本发明实施例的技术方案后,下面详细的说明本技术的各种非限制性实施方式。

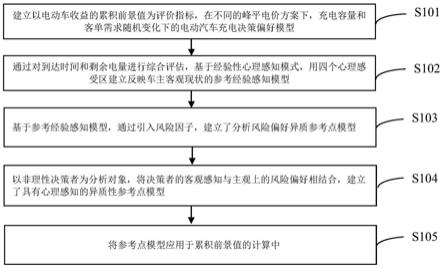

48.首先请参见图2,图2为本发明实施例提供的一种内存信息获取方法的流程示意图,本发明实施例可包括以下内容:

49.一种内存信息获取系统可包括中央处理器cpu21,内存22、南桥芯片pch23、基板管理控制器bmc24、数据选择器25、通道控制器26和指令触发器27。其中,各器件之间的连接关系可为:南桥芯片23与基板管理控制器24相连,数据选择器25分别与中央处理器21、基板管理控制器24、内存22相连,指令触发器27与基板管理控制器24相连,通道控制器26分别与数据选择器25和南桥芯片23相连。内存22可为但并不限制为dimm,相应的,获取的内存信息可

为dimm的spd信息,内存22与数据选择器25之间可通过spd总线相连,pch23与bmc24、通道控制器26之间可基于espi(enhanced serial peripheral interface,增强序列周边接口)进行数据通信。通道控制器26可为任何一种有控制逻辑的器件,例如可为但并不限制于cpld(complex programmable logic device,复杂可编程逻辑器件)、fpga(field programmable gate array,现场可编程逻辑门阵列)、单片机等等,所属领域技术人员可基于硬件配置、实际应用场景进行灵活选择,从控制和编写易用性来说,可采用cpld作为通道控制器26。数据选择器25用于信号切换,在多路数据传送过程中,能够根据需要将其中任意一路选出来,可为任何一种多路开关或者多路选择器,这均不影响本技术的实现。指令触发器27用于作为触发通道切换的一个指示指令,也就是告知系统核实控制数据选择器25进行通道的切换。

50.基于上述系统结构,bmc获取内存信息的实现过程为:数据选择器25在默认情况下连通的通道为内存22与cpu21相连的第一连接通道,当需要进行内存信息获取时,用户通过指令触发器27向系统传入内存信息获取指令,基板管理控制器24接收到指令触发器27传入的内存信息获取指令,向南桥芯片23发送内存上电监控指令;bmc24通过监控该内存上电监控指令判断内存是否完成上电,当确定内存完成上电,向pch23发送通道切换指令,pch23在接收到通道切换指令之后,再将通道切换指令发送给通道控制器26;通道控制器26在接收到该指令,通过控制数据选择器25将内存22与中央处理器21的第一连接通道切换至内存22与基板管理控制器24的第二连接通道,此时,内存22与bmc24就连通了,bmc24可直接通过该通道读取所需内存信息,无需依赖其他任何器件。

51.在本发明实施例提供的技术方案中,在系统开机过程中,内存需要上电才能正常工作,为了不影响内存上电,再不需要获取内存信息时,默认内存与cpu相连,这样便可以保证内存正常上电。当用户需要获取内存信息时,通过指令触发器将获取内存的指令发送给bmc以在内存上电完成之后触发通道切换指令发送至通道控制器,从而将内存与bmc连接通道连通,这样bmc便可直接到内存中读取所需内存信息,保证bmc快速有效地获取到dimm的spd信息,有利于提高服务器运营效率,实现了服务器运行的稳定性,可以满足客户多样化的产品需求。

52.在上述实施例中对指令触发器27的结构并未进行限定,作为一种可选的实施方式,本技术还提供了一种指令触发器27的结构,在本实施例中,考虑到指令触发器27主要是为了告知系统何时进行通道切换,而对应通道切换的条件是用户是否需要获取内存信息,相应的指令触发器27可包括第一状态引脚和第二状态引脚,安装在系统外部且由用户进行控制。第一状态引脚用于标识用户不获取内存信息;第二状态引脚用于标识用户获取内存信息。用户置指令触发器27的第一状态引脚连通,则证明用户不需要获取内存信息,用户置指令触发器27的第二状态引脚连通,则证明用户需要获取内存信息,默认情况下,指令触发器27的第一状态引脚处于连通状态,用户需要获取内存信息,则会置第二状态引脚连通,指令触发器27检测到第二状态引脚连通,向基板管理控制器24传入内存信息获取指令。

53.举例来说,指令触发器27可为跳线帽jumper,跳线帽是可以活动的部件,外层是绝缘塑料,内层是导电材料,可以插在跳线针上面,将两根跳线针连接起来当跳线帽扣在两根跳线针上时是接通状态,有电流通过,称之为on;反之不扣上跳线帽时,就说明是断开的,称之为off。

54.为了进一步提升系统实用性,适用于各种应用场景,基板管理控制器24还用于当通过第二连接通道读取内存信息完成后,向南桥芯片23发送信息读取完成指令,以使通道控制器26在接收到南桥芯片23的信息读取完成指令之后,控制数据选择器25将第二连接通道切换为第一连接通道。也就是说,只要不获取内存信息,则内存22是与cpu21相连通的,只有在需要获取内存信息的场景中,内存22才与bmc24相连通。

55.为了使所属领域技术人员更加清楚明白本技术的技术方案,本技术结合图3以通道控制器26为cpld、数据选择器25为mux,指令触发器为jumper、内存22为dimm为例阐述bmc读取dimm的spd信息过程:

56.dimm的spd信号与cpu之间通过mux(multiplexer)连接,mux的select pin(也即片选信号)由cpld控制,mux包括b1和b2两个接口,当select切换到b2时,dimm的spd总线接到bmc,当select切换到b1时,dimm的spd总线接到cpu。外部jumper是用户控制,jumper默认状态为1

‑

2pin,此时spd总线直连cpu,当用户把jumper选择到2

‑

3pin,此时dimm spd总线直连bmc。

57.由于在系统开机过程中,dimm需要spd信号上电,为了不影响dimm上电过程,需要在dimm完成整个上电过程以后再把spd切换到bmc。当用户需要bmc获取dimm的spd,首先把jumper切换到2

‑

3pin,bmc通过pch发出的post complete信号判断此时dimm是否上电完成。若post complete信号置为有效,说明bios post过程已完成,此时dimm完成上电,可以切换spd总线。bmc通过espi通知pch切换spd总线的master(即控制端),pch接收到该指令以后通过espi给到cpld,cpld切换mux由b1到b2。bmc开始读取dimm信息,读取完成后再通过espi指令通知pch,pch将该指令再发送给cpld,cpld控制mux由b2切换到b1。

58.由上可知,本发明实施例在保证dimm可以正常上电的基础上可以实现bmc快速有效地获取dimm的spd信息,且不影响计算机排除故障的效率。

59.基于上述内存信息获取系统,本技术还分别基于bmc和通道控制器提供了内存信息获取方法,可包括下述内容:

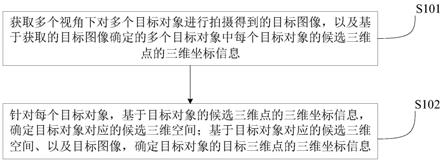

60.首先请参见图4,图4为本发明实施例提供的一种内存信息获取方法的流程示意图,应用于如上任意一个实施例所述内存信息获取系统中的基板管理控制器,本发明实施例可包括以下内容:

61.s401:当接收到内存信息获取指令,发送内存上电监控指令;

62.s402:当确定内存完成上电,发送通道切换指令,以基于通道切换指令控制内存从当前与中央处理器的第一连接通道切换至与基板管理控制器的第二连接通道上;

63.s403:当检测到成功切换至第二连接通道,读取内存信息。

64.作为本实施例的一种可选的实施方式,在s403之后,还可包括:

65.当通过第二连接通道读取内存信息完成后,向南桥芯片发送信息读取完成指令,以使通道控制器在接收到南桥芯片的信息读取完成指令之后,控制数据选择器将第二连接通道切换为第一连接通道。

66.其次,请参见图5,图5为本发明实施例提供的另一种内存信息获取方法的流程示意图,应用于如上任意一个实施例所述内存信息获取系统中的通道控制器,具体的可包括以下内容:

67.s501:接收通道切换指令;

68.其中,通道切换指令为内存上电完成之后,基板管理控制器通过南桥芯片发送给通道控制器。

69.s502:控制数据选择器由第一连接通道切换至第二连接通道,以使基板管理控制器基于第二连接通道读取内存信息。

70.本实施例的第一连接通道为内存从与中央处理器的连接通道;第二连接通道为基板管理控制器与内存的连接通道。

71.上述系统内的各单元之间的信息交互、执行过程等内容,由于与本发明实施例基于同一构思,具体内容可参见上述系统实施例中的叙述,此处,便不再赘述。

72.由上可知,本发明实施例在保证内存可以正常上电的基础上可以实现bmc快速有效地获取系统内存信息,且不影响计算机排除故障的效率。

73.需要说明的是,本技术中各步骤之间没有严格的先后执行顺序,只要符合逻辑上的顺序,则这些步骤可以同时执行,也可按照某种预设顺序执行,图4和图5只是一种示意方式,并不代表只能是这样的执行顺序。

74.本发明实施例还针对内存信息获取方法提供了相应的装置,进一步使得方法更具有实用性。其中,装置可从功能模块的角度和硬件的角度分别说明。下面对本发明实施例提供的内存信息获取装置进行介绍,下文描述的内存信息获取装置与上文描述的内存信息获取方法可相互对应参照。

75.基于功能模块的角度,先请参见图6,图6为本发明实施例提供的内存信息获取装置应用于如上任意一个实施例所述内存信息获取系统中的基板管理控制器在一种具体实施方式下的结构图,该装置可包括:

76.上电监控模块601,用于当接收到内存信息获取指令,发送内存上电监控指令;

77.连接通道且模块602,用于当确定内存完成上电,发送通道切换指令,以基于通道切换指令控制内存当前从与中央处理器的连接通道切换至与基板管理控制器的连接通道上;

78.信息读取模块603,用于当检测到成功切换至第二连接通道,读取内存信息。

79.其次,请参见图7,图7为本发明实施例提供的内存信息获取装置应用于如上任意一个实施例所述内存信息获取系统中的通道控制器在一种具体实施方式下的结构图,包括:

80.指令接收模块701,用于接收通道切换指令;通道切换指令为内存上电完成之后,基板管理控制器通过南桥芯片发送给通道控制器;

81.通道切换模块702,用于控制数据选择器由第一连接通道切换至第二连接通道,以使基板管理控制器基于第二连接通道读取内存信息;第一连接通道为内存从与中央处理器的连接通道;第二连接通道为基板管理控制器与内存的连接通道。

82.本发明实施例内存信息获取装置的各功能模块的功能可根据上述方法实施例中的方法具体实现,其具体实现过程可以参照上述方法实施例的相关描述,此处不再赘述。

83.由上可知,本发明实施例在保证内存可以正常上电的基础上可以实现bmc快速有效地获取系统内存信息,且不影响计算机排除故障的效率。

84.上文中提到的内存信息获取装置是从功能模块的角度描述,进一步的,本技术还提供一种电子设备,是从硬件角度描述。图8为本技术实施例提供的电子设备在一种实施方

式下的结构示意图。如图8所示,该电子设备包括存储器80,用于存储计算机程序;处理器81,用于执行计算机程序时实现如上述任一实施例提到的内存信息获取方法的步骤。

85.其中,处理器81可以包括一个或多个处理核心,比如4核心处理器、8核心处理器等。处理器81可以采用dsp(digital signal processing,数字信号处理)、fpga(field-programmable gate array,现场可编程门阵列)、pla(programmable logic array,可编程逻辑阵列)中的至少一种硬件形式来实现。处理器81也可以包括主处理器和协处理器,主处理器是用于对在唤醒状态下的数据进行处理的处理器,也称cpu(central processing unit,中央处理器);协处理器是用于对在待机状态下的数据进行处理的低功耗处理器。在一些实施例中,处理器81可以在集成有gpu(graphics processing unit,图像处理器),gpu用于负责显示屏所需要显示的内容的渲染和绘制。一些实施例中,处理器81还可以包括ai(artificial intelligence,人工智能)处理器,该ai处理器用于处理有关机器学习的计算操作。

86.存储器80可以包括一个或多个计算机可读存储介质,该计算机可读存储介质可以是非暂态的。存储器80还可包括高速随机存取存储器,以及非易失性存储器,比如一个或多个磁盘存储设备、闪存存储设备。本实施例中,存储器80至少用于存储以下计算机程序801,其中,该计算机程序被处理器81加载并执行之后,能够实现前述任一实施例公开的内存信息获取方法的相关步骤。另外,存储器80所存储的资源还可以包括操作系统802和数据803等,存储方式可以是短暂存储或者永久存储。其中,操作系统802可以包括windows、unix、linux等。数据803可以包括但不限于内存信息获取结果对应的数据等。

87.在一些实施例中,上述电子设备还可包括有显示屏82、输入输出接口83、通信接口84或者称为网络接口、电源85以及通信总线86。其中,显示屏82、输入输出接口83比如键盘(keyboard)属于用户接口,可选的用户接口还可以包括标准的有线接口、无线接口等。可选地,在一些实施例中,显示器可以是led显示器、液晶显示器、触控式液晶显示器以及oled(organic light

‑

emitting diode,有机发光二极管)触摸器等。显示器也可以适当的称为显示屏或显示单元,用于显示在电子设备中处理的信息以及用于显示可视化的用户界面。通信接口84可选的可以包括有线接口和/或无线接口,如wi

‑

fi接口、蓝牙接口等,通常用于在电子设备与其他电子设备之间建立通信连接。通信总线86可以是外设部件互连标准(peripheral component interconnect,简称pci)总线或扩展工业标准结构(extended industry standard architecture,简称eisa)总线等。该总线可以分为地址总线、数据总线、控制总线等。为便于表示,图8中仅用一条粗线表示,但并不表示仅有一根总线或一种类型的总线。

88.本领域技术人员可以理解,图8中示出的结构并不构成对该电子设备的限定,可以包括比图示更多或更少的组件,例如还可包括实现各类功能的传感器87。

89.本发明实施例电子设备的各功能模块的功能可根据上述方法实施例中的方法具体实现,其具体实现过程可以参照上述方法实施例的相关描述,此处不再赘述。

90.由上可知,本发明实施例在保证内存可以正常上电的基础上可以实现bmc快速有效地获取系统内存信息,且不影响计算机排除故障的效率。

91.可以理解的是,如果上述实施例中的内存信息获取方法以软件功能单元的形式实现并作为独立的产品销售或使用时,可以存储在一个计算机可读取存储介质中。基于这样

的理解,本技术的技术方案本质上或者说对现有技术做出贡献的部分或者该技术方案的全部或部分可以以软件产品的形式体现出来,该计算机软件产品存储在一个存储介质中,执行本技术各个实施例方法的全部或部分步骤。而前述的存储介质包括:u盘、移动硬盘、只读存储器(read

‑

only memory,rom)、随机存取存储器(random access memory,ram)、电可擦除可编程rom、寄存器、硬盘、可移动磁盘、cd

‑

rom、磁碟或者光盘等各种可以存储程序代码的介质。

92.基于此,本发明实施例还提供了一种可读存储介质,存储有计算机程序,计算机程序被处理器执行时如上任意一实施例内存信息获取方法的步骤。

93.本发明实施例可读存储介质的各功能模块的功能可根据上述方法实施例中的方法具体实现,其具体实现过程可以参照上述方法实施例的相关描述,此处不再赘述。

94.本说明书中各个实施例采用递进的方式描述,每个实施例重点说明的都是与其它实施例的不同之处,各个实施例之间相同或相似部分互相参见即可。对于实施例公开的硬件包括装置及电子设备而言,由于其与实施例公开的方法相对应,所以描述的比较简单,相关之处参见方法部分说明即可。

95.专业人员还可以进一步意识到,结合本文中所公开的实施例描述的各示例的单元及算法步骤,能够以电子硬件、计算机软件或者二者的结合来实现,为了清楚地说明硬件和软件的可互换性,在上述说明中已经按照功能一般性地描述了各示例的组成及步骤。这些功能究竟以硬件还是软件方式来执行,取决于技术方案的特定应用和设计约束条件。专业技术人员可以对每个特定的应用来使用不同方法来实现所描述的功能,但是这种实现不应认为超出本发明的范围。

96.以上对本技术所提供的一种内存信息获取方法、装置、系统、电子设备及可读存储介质进行了详细介绍。本文中应用了具体个例对本技术原理及实施方式进行了阐述,以上实施例的说明只是用于帮助理解本发明的方法及其核心思想。应当指出,对于本技术领域的普通技术人员来说,在不脱离本发明原理的前提下,还可以对本技术进行若干改进和修饰,这些改进和修饰也落入本技术权利要求的保护范围内。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。