技术特征:

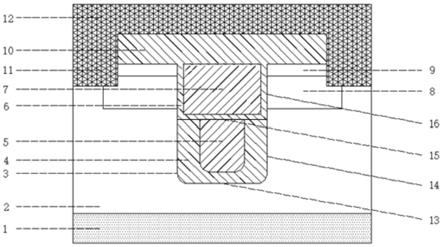

1.一种基于硫化钼的cmos反相器,其特征在于,包括:上表面带有介质层的硅衬底;位于所述介质层上表面的薄膜层;所述薄膜层包括横向连接的p型掺杂硫化钼薄膜和n型掺杂硫化钼薄膜;所述p型掺杂硫化钼薄膜由n型掺杂硫化钼薄膜经等离子体掺杂后制备而成;沉积在所述薄膜层上表面且互不接触的3个电极,依次为位于所述n型掺杂硫化钼薄膜上表面的第一电极、位于所述p型掺杂硫化钼薄膜上表面的第二电极以及位于所述p型掺杂硫化钼薄膜上表面和所述n型硫化钼薄膜连接处上表面的第三电极;工作时,所述第一电极用于接地;所述第二电极用于接工作电压vdd;所述硅衬底作为输入端,用于连接输入电压vin;所述第三电极作为输出端,用于输出电压vout。2.如权利要求1所述的基于硫化钼的cmos反相器,其特征在于,所述电极为双层结构,包括:与所述薄膜层直接接触的ti金属层,以及位于所述ti金属层上表面的保护层;所述ti金属层用于与所述薄膜层形成欧姆接触;所述保护层用于导电并防止所述ti金属层被氧化。3.如权利要求2所述的基于硫化钼的cmos反相器,其特征在于,所述ti金属层的厚度为10~30nm。4.如权利要求2所述的基于硫化钼的cmos反相器,其特征在于,所述保护层为au金属层。5.如权利要求4所述的基于硫化钼的cmos反相器,其特征在于,所述au金属层的厚度为50~100nm。6.如权利要求1~5任一项所述的基于硫化钼的cmos反相器,其特征在于,n型沟道的长度,即所述第一电极和所述第三电极之间的n型掺杂硫化钼薄膜的长度,为5~100μm,并且,p型沟道的长度,及所述第二电极和所述第三电极之间的p型掺杂硫化钼薄膜的长度,为5~100μm。7.如权利要求1~6任一项所述的基于硫化钼的cmos反相器的制备方法,其特征在于,包括如下步骤:(s1)在cvd管式炉前端温区中放入硫粉并加热至第一预设温度;(s2)将moo3放置于钼片上后,将上表面带有二氧化硅介质层的硅片倒扣于该钼片上,并将所述钼片和所述硅片一同放入所述cvd管式炉的后端温区,通入惰性气体并加热到第二预设温度并保温,以在所述介质层上表面形成n型掺杂硫化钼薄膜,得到第一中间产物;(s3)利用光刻胶在所述第一中间产物上表面制作遮挡层,以对n型掺杂硫化钼薄膜进行部分遮挡;(s4)对制作有遮挡层的第一中间产物上表面进行等离子体掺杂,使n型掺杂硫化钼薄膜未被遮挡的部分被掺杂成p型掺杂硫化钼薄膜,之后去除光刻胶,得到第二中间产物;(s5)在所述第二中间产物中的n型掺杂硫化钼薄膜上表面、p型硫化钼薄膜上表面以及两薄膜连接处的上表面制备互不接触的三个电极,得到所述基于硫化钼的cmos反相器。8.如权利要求7所述的制备方法,其特征在于,所述步骤(s4)中,进行等离子体掺杂时,所使用的掺杂气体为氮气。9.如权利要求7或8所述的制备方法,其特征在于,所述步骤(s4)中,进行等离子体掺杂

时,通过磁场控制进行掺杂。10.如权利要求9所述的制备方法,其特征在于,磁场控制包括磁场功率的控制,和/或轰击时间的控制。

技术总结

本发明公开了一种基于硫化钼的CMOS反相器及其制备方法,属于微电子器件技术领域,包括:硅衬底,其上的介质层上表面制备有横向连接的P型掺杂硫化钼薄膜和N型掺杂硫化钼薄膜;P型薄膜由N型经等离子体掺杂而成;沉积在两薄膜上表面以及两薄膜连接处上表面的三个电极;方法包括:在CVD管式炉前端温区中放入硫粉并加热;将MoO3放置于钼片上后,将带有介质层的硅片倒扣于该钼片上并一同放入CVD管式炉的后端温区,通入惰性气体并加热保温,以形成N型掺杂硫化钼薄膜;将N型薄膜上表面部分遮挡后进行等离子体掺杂,使未被遮挡的部分被掺杂成P型掺杂硫化钼薄膜;制备三个电极,得到基于硫化钼的CMOS反相器。本发明中薄膜受损较小,CMOS反相器整体性能较好。CMOS反相器整体性能较好。CMOS反相器整体性能较好。

技术研发人员:曾祥斌 周宇飞 胡一说 王文照 陆晶晶 王士博 王君豪 王曦雅 肖永红 陈铎 张茂发

受保护的技术使用者:华中科技大学

技术研发日:2021.07.27

技术公布日:2021/11/4

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。