一种基于硫化钼的cmos反相器及其制备方法

技术领域

1.本发明属于微电子器件技术领域,更具体地,涉及一种基于硫化钼的cmos反相器及其制备方法。

背景技术:

2.过渡金属硫化物有着自己独特的性质,包括电学、光学和物理特性。而其中二硫化钼(mos2)作为(二维层状过渡金属硫属化物)tmdcs的典型代表,相比于石墨烯的零禁带,mos2有着可变的禁带宽度(1.2ev~1.8ev),能够从间接带隙变成直接带隙,并且是沟道尺寸缩小和超越摩尔定律的替代者。这些性质使得mos2在(场效应管)fet,光电和逻辑器件上有着广阔的发展前景。

3.反相器是逻辑器件中最基础的单元,常见的反相器结构有nmos反相器与cmos反相器。nmos反相器只需一种沟道材料,易于大规模制备,但在工作中负载管始终开启,使功耗大。cmos反相器具有功耗小,增益高,速度快,噪声容限高等优势,因此,在实际应用中获得了更为广泛的应用。

4.利用二维材料构建cmos反相器多为异质cmos反相器,其中的p型沟道材料和n型沟道材料由不同的半导体制备而成。异质cmos反相器面临的问题在于其制备工艺和器件结构复杂,往往需要借助材料的转移,目前对于二维材料的转移工艺有待完善,由于二维材料的薄膜厚度很小,在转移过程中容易产生新的界面态甚至造成对膜的损伤,从而使器件性能下降。

技术实现要素:

5.针对现有技术的缺陷和改进需求,本发明提供了一种基于硫化钼的cmos反相器及其制备方法,其目的在于,提供一种同质的二维cmos反相器,以解决现有的基于二维材料的cmos反相器中薄膜在制备过程中易受损伤,影响器件性能的技术问题。

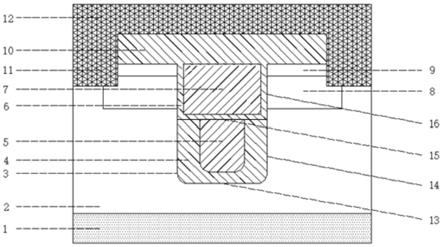

6.为实现上述目的,按照本发明的一个方面,提供了一种基于硫化钼的cmos反相器,包括:

7.上表面带有介质层的硅衬底;

8.位于介质层上表面的薄膜层;薄膜层包括横向连接的p型掺杂硫化钼薄膜和n型掺杂硫化钼薄膜;p型掺杂硫化钼薄膜由n型掺杂硫化钼薄膜经等离子体掺杂后制备而成;

9.沉积在薄膜层上表面且互不接触的3个电极,依次为位于n型掺杂硫化钼薄膜上表面的第一电极、位于p型掺杂硫化钼薄膜上表面的第二电极以及位于p型掺杂硫化钼薄膜上表面和n型硫化钼薄膜连接处上表面的第三电极;

10.工作时,第一电极用于接地;第二电极用于接工作电压vdd;硅衬底作为输入端,用于连接输入电压vin;第三电极作为输出端,用于输出电压vout。

11.本发明所提供的基于硫化钼的cmos反相器,其工作原理如下:当vin输入高电平时,硅衬底、介质层及p型掺杂硫化钼薄膜构成的pmos管处于截止状态,硅衬底、介质层及n

型掺杂硫化钼薄膜nmos处于导通状态,输出vout为低电平,由于mos管截止状态下等效电阻很高,此时流过两管的电流idd≈0,这也就意味着功耗接近于零;当vin输入低电平时,nmos管处于截止状态,pmos管处于导通状态,输出vout为高电平,此时功耗同样接近于零。

12.本发明所提供的基于硫化钼的cmos反相器,其中的薄膜层由二维材料硫化钼制备而成,能够实现低功耗;本发明中,p型掺杂硫化钼薄膜和n型掺杂薄膜含同样的半导体材料mos2,相应地,该cmos反相器为同质cmos反相器,由于p型掺杂硫化钼薄膜由同一n型掺杂硫化钼薄膜经等离子体掺杂后制备而成,因此,在制备过程中,无需定向转移,避免了制备过程中,因转移而导致的薄膜受损;此外,相比于化学掺杂、表面电荷转移等掺杂方式,使用等离子体掺杂能够进一步较小对薄膜的损伤;最终薄膜受损较小,cmos反相器整体性能较好。

13.进一步地,薄膜层的厚度为0.5nm

‑

2nm。

14.本发明所提供的基于硫化钼的cmos反相器,其中的mos2薄膜厚度为0.5nm

‑

2nm,具有较好的光性能和电性能。

15.进一步地,电极为双层结构,包括:与薄膜层直接接触的ti金属层,以及位于ti金属层上表面的保护层;

16.ti金属层用于与薄膜层形成欧姆接触;

17.保护层用于导电并防止ti金属层被氧化。

18.本发明所提供的基于硫化钼的cmos反相器,其中的电极为双层结构;直接与mos2薄膜接触的一层为ti金属层,由于钛的功函数与硫化钼(mos2)相近,可以实现较好的欧姆接触;ti金属层之上的一层为保护层,在导电的同时防止ti金属层被氧化;该电极结构保证了良好的导电性能,并且性能稳定。

19.进一步地,ti金属层的厚度为10~30nm,由此能够实现良好的欧姆接触。

20.进一步地,保护层为au金属层。

21.au的导电性和稳定性较好,本发明使用au金属层作为双层电极结构中的保护层,在提供导电性的同时,能够有效保护底层的ti金属层不被氧化。

22.进一步地,au金属层的厚度为50~100nm,由此能够保证较好的导电性,并有效起到防止ti金属层被氧化的保护作用。

23.进一步地,n型沟道的长度,即第一电极和第三电极之间的n型掺杂硫化钼薄膜的长度,为5~100μm,并且,p型沟道的长度,及第二电极和第三电极之间的p型掺杂硫化钼薄膜的长度,为5~100μm。

24.本发明所提供的基于硫化钼的cmos反相器,其中的n型沟道的长度和p型沟道的长度相当,均为5~100μm,由此能够实现沟道匹配,保证载流子有较高的迁移率。

25.按照本发明的另一个方面,提供了上述基于硫化钼的cmos反相器的制备方法,包括如下步骤:

26.(s1)在cvd管式炉前端温区中放入硫粉并加热至第一预设温度;

27.(s2)将moo3放置于钼片上后,将上表面带有二氧化硅介质层的硅片倒扣于该钼片上,并将钼片和硅片一同放入cvd管式炉的后端温区,通入惰性气体并加热到第二预设温度并保温,以在介质层上表面形成n型掺杂硫化钼薄膜,得到第一中间产物;

28.(s3)利用光刻胶在第一中间产物上表面制作遮挡层,以对n型掺杂硫化钼薄膜进行部分遮挡;

29.(s4)对制作有遮挡层的第一中间产物上表面进行等离子体掺杂,使n型掺杂硫化钼薄膜未被遮挡的部分被掺杂成p型掺杂硫化钼薄膜,之后去除光刻胶,得到第二中间产物;

30.(s5)在第二中间产物中的n型掺杂硫化钼薄膜上表面、p型硫化钼薄膜上表面以及两薄膜连接处的上表面制备互不接触的三个电极,得到基于硫化钼的cmos反相器。

31.本发明通过在同一n型掺杂硫化钼薄膜的部分进行等离子体掺杂,将该部分掺杂成p型掺杂硫化钼薄膜,即可制备得到由p型掺杂硫化钼薄膜和n型掺杂硫化钼薄膜横向连接而成的薄膜层,无需定向转移,由此能够到达减小制备过程对薄膜的损伤;化学掺杂、表面电荷转移等掺杂方式所构建的同质结cmos的输入输出电压范围并不相同,在逻辑电路上属于无效应用,而且使用化学掺杂和表面电荷转移等方式掺杂使得器件可靠性不高,器件工作中在空气环境下非常容易受水蒸气、氧气等影响,本发明使用等离子体掺杂完成p型掺杂硫化钼薄膜的制备,能够进一步减小对薄膜的损伤,并且保证所制备得到的cmos反相器具有较高的稳定性。最终薄膜受损较小,cmos反相器整体性能较好。

32.进一步地,步骤(s4)中,进行等离子体掺杂时,所使用的掺杂气体为氮气。

33.本发明使用氮气完成等离子体掺杂,能够通过氮原子原位替换硫化钼中的硫原子,快速有效完成掺杂。

34.进一步地,步骤(s4)中,进行等离子体掺杂时,通过磁场控制进行掺杂。

35.进一步地,磁场控制包括磁场功率的控制,和/或轰击时间的控制。

36.本发明通过磁场控制进行等离子体掺杂,使得整个掺杂过程可控;具体通过控制磁场功率和/或轰击时间,能够进一步实现低损伤掺杂。

37.总体而言,通过本发明所构思的以上技术方案,能够取得以下有益效果:

38.(1)本发明所提供的基于硫化钼的cmos反相器,使用二维材料硫化钼作为沟道材料,载流子迁移率高,免疫短沟道效应,且制备工艺简单可控;由于p型掺杂硫化钼薄膜由n型掺杂硫化钼薄膜经等离子掺杂后制备而成,因此在器件制备过程中,无需进行转移,界面态少,对薄膜损伤小,并且等离子体掺杂进一步减小了掺杂过程中对薄膜的损伤。最终,薄膜受损较小,cmos反相器整体性能较好。

39.(2)本发明所提供的基于硫化钼的cmos反相器,其中的电极为双层结构;直接与mos2薄膜接触的一层为ti金属层,由于钛的功函数与硫化钼(mos2)相近,可以实现较好的欧姆接触;ti金属层之上的一层为保护层,在导电的同时防止ti金属层被氧化;该电极结构保证了良好的导电性能,并且性能稳定。

40.(3)本发明所提供的的基于硫化钼的cmos反相器的制备方法,使用化学气相沉积的方法制备硫化钼薄膜,采用等离子体掺杂的方式进行掺杂,并且使用磁场控制的方式对掺杂过程进行控制,能够最大程度上减小对薄膜的损伤,最终制备的薄膜尺寸更大,结晶性更好,结构更稳定。

41.(4)本发明所提供的制备方法,其制备过程中对薄膜损伤小,易于制备较大的薄膜,便于在实际应用中连接引脚;实验表明,本发明所制备得到的bjt中,薄膜边长最长可达600μm~800μm。

附图说明

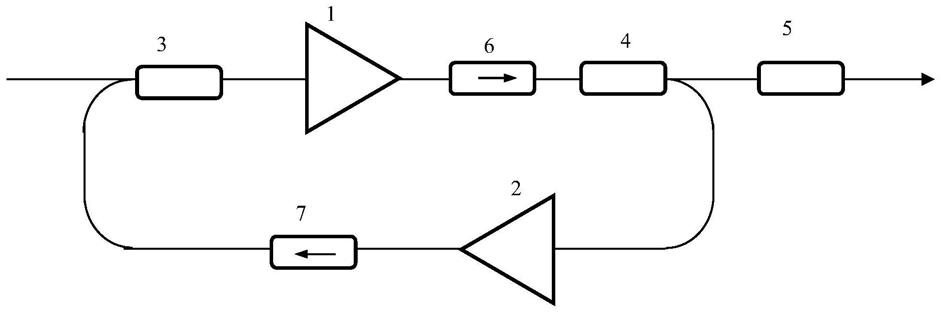

42.图1为本发明实施例提供的基于硫化钼的cmos反相器的结构示意图;

43.图2为本发明实施例提供的基于硫化钼的cmos反相器的制备方法示意图。

具体实施方式

44.为了使本发明的目的、技术方案及优点更加清楚明白,以下结合附图及实施例,对本发明进行进一步详细说明。应当理解,此处所描述的具体实施例仅仅用以解释本发明,并不用于限定本发明。此外,下面所描述的本发明各个实施方式中所涉及到的技术特征只要彼此之间未构成冲突就可以相互组合。

45.在本发明中,本发明及附图中的术语“第一”、“第二”等(如果存在)是用于区别类似的对象,而不必用于描述特定的顺序或先后次序。

46.为了降低功耗、提高增益、提高噪声容限,同时提高载流子迁移率,减小对薄膜的损伤,本发明提供了一种基于硫化钼的cmos反相器及其制备方法,其整体思路在于:提供一种同质cmos反相器,从而仅利用掺杂的方式即可在n型掺杂硫化钼薄膜的基础上完成p型薄膜的制备,无需定向转移,有效降低对薄膜的损害,保证cmos反相器的性能;相应地,在其制备方法中,通过在n型掺杂硫化钼薄膜的基础上,利用掺杂的方式,将部分n型掺杂硫化钼薄膜掺杂成p型掺杂硫化钼薄膜,即可完成薄膜层的制备,无需定向转移,制备工艺可控易操作,并且对薄膜的损伤小,制备所得的cmos反相器性能良好且稳定。

47.本发明所提供的基于硫化钼的cmos反相器,如图1所示,包括:

48.上表面带有介质层的硅衬底;

49.位于介质层上表面的薄膜层;薄膜层包括横向连接的p型掺杂硫化钼薄膜和n型掺杂硫化钼薄膜;p型掺杂硫化钼薄膜由n型掺杂硫化钼薄膜经等离子体掺杂后制备而成;

50.沉积在薄膜层上表面且互不接触的3个电极,依次为位于n型掺杂硫化钼薄膜上表面的第一电极、位于p型掺杂硫化钼薄膜上表面的第二电极以及位于p型掺杂硫化钼薄膜上表面和n型硫化钼薄膜连接处上表面的第三电极;

51.工作时,第一电极用于接地;第二电极用于接工作电压vdd;硅衬底作为输入端,用于连接输入电压vin;第三电极作为输出端,用于输出电压vout。

52.本发明所提供的基于硫化钼的cmos反相器,由于其中的n型沟道材料和p型沟道材料材料相同,都是硫化钼,因此,该cmos反相器是一种同质的cmos反相器;其中,第一电极和第三电极之间的n型掺杂硫化钼薄膜为n型沟道,第二电极和第三电极之间的p型掺杂硫化钼薄膜为p型沟道。

53.本发明所提供的上述基于硫化钼的cmos反相器,其工作原理如下:当vin输入高电平时,硅衬底、介质层及p型掺杂硫化钼薄膜构成的pmos管处于截止状态,硅衬底、介质层及n型掺杂硫化钼薄膜nmos处于导通状态,输出vout为低电平,由于mos管截止状态下等效电阻很高,此时流过两管的电流idd≈0,这也就意味着功耗接近于零;当vin输入低电平时,nmos管处于截止状态,pmos管处于导通状态,输出vout为高电平,此时功耗同样接近于零。

54.由于二氧化硅介质层相对于其他类型的介质层较为致密,悬挂键少,且容易获得,器件制备性能较好,不会受到介质层的影响;在本发明优选的实施例中,介质层为二氧化硅(sio2)介质层。

55.为了保证薄膜层具有较好的光性能和电性能,在本发明优选的一些实施例中,mos2薄膜层的厚度为0.5nm

‑

2nm。

56.为了进一步提高cmos反相器的性能,如图1所示,在本发明优选的一些实施例中,电极为双层结构,包括:与薄膜层直接接触的ti金属层,以及位于ti金属层上表面的保护层;ti金属层用于与薄膜层形成欧姆接触;保护层用于导电并防止ti金属层被氧化;由于钛的功函数与硫化钼(mos2)相近,可以实现较好的欧姆接触;ti金属层之上的一层为保护层,在导电的同时防止ti金属层被氧化;该电极结构保证了良好的导电性能,并且性能稳定。

57.为了进一步提高cmos反相器的性能,在本发明进一步优选的一些实施例中,ti金属层的厚度为10~30nm,由此能够实现良好的欧姆接触;保护层为au金属层,au的导电性和稳定性较好,在提供导电性的同时,能够有效保护底层的ti金属层不被氧化;au金属层的优选厚度为50~100nm,由此能够保证较好的导电性,并有效起到防止ti金属层被氧化的保护作用。

58.为了实现沟道匹配,保证较高的载流子迁移率,在本发明优选的一些实施例中,n型沟道的长度,即第一电极和第三电极之间的n型掺杂硫化钼薄膜的长度,为5~100μm,并且,p型沟道的长度,及第二电极和第三电极之间的p型掺杂硫化钼薄膜的长度,为5~100μm。

59.本发明所提供的基于硫化钼的cmos反相器,其中的薄膜层由二维材料硫化钼制备而成,能够实现低功耗;本发明中,p型掺杂硫化钼薄膜和n型掺杂薄膜含同样的半导体材料mos2,相应地,该cmos反相器为同质cmos反相器,由于p型掺杂硫化钼薄膜由同一n型掺杂硫化钼薄膜经等离子体掺杂后制备而成,因此,在制备过程中,无需定向转移,避免了制备过程中,因转移而导致的薄膜受损;此外,相比于化学掺杂、表面电荷转移等掺杂方式,使用等离子体掺杂能够进一步较小对薄膜的损伤;最终薄膜受损较小,cmos反相器整体性能较好。

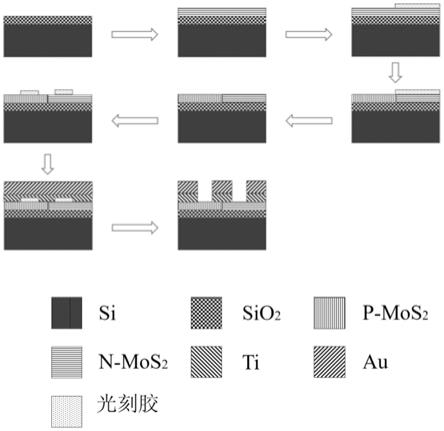

60.本发明还提供了上述基于硫化钼的cmos反相器的制备方法,如图2所示,包括如下步骤:

61.(s1)在cvd管式炉前端温区中放入硫粉并加热至第一预设温度;

62.(s2)将moo3放置于钼片上后,将上表面带有二氧化硅介质层的硅片倒扣于该钼片上,并将钼片和硅片一同放入cvd管式炉的后端温区,通入惰性气体并加热到第二预设温度并保温,以在介质层上表面形成n型掺杂硫化钼薄膜,得到第一中间产物;

63.通过步骤(s2),能能够利用化学气相沉积方法在带有介质层的硅衬底上表面制备得到n型硫化钼薄膜;

64.(s3)利用光刻胶在第一中间产物上表面制作遮挡层,以对n型掺杂硫化钼薄膜进行部分遮挡;

65.制作遮挡层的具体步骤包括:旋涂光刻胶、前曝、前烘、后曝、后烘、显影;

66.(s4)对制作有遮挡层的第一中间产物上表面进行等离子体掺杂,使n型掺杂硫化钼薄膜未被遮挡的部分被掺杂成p型掺杂硫化钼薄膜,之后去除光刻胶,得到第二中间产物;

67.(s5)在第二中间产物中的n型掺杂硫化钼薄膜上表面、p型硫化钼薄膜上表面以及两薄膜连接处的上表面制备互不接触的三个电极,得到基于硫化钼的cmos反相器;

68.在本发明优选的一些实施例中,制备电极的过程包括两个部分,先利用光刻胶在

薄膜层上制备电极图案,具体包括旋涂光刻胶、前曝、前烘、后曝、后烘、显影,之后利用电子束蒸发制备电极。

69.本发明通过在同一n型掺杂硫化钼薄膜的部分进行等离子体掺杂,将该部分掺杂成p型掺杂硫化钼薄膜,即可制备得到由p型掺杂硫化钼薄膜和n型掺杂硫化钼薄膜横向连接而成的薄膜层,无需定向转移,由此能够到达减小制备过程对薄膜的损伤;化学掺杂、表面电荷转移等掺杂方式所构建的同质结cmos的输入输出电压范围并不相同,在逻辑电路上属于无效应用,而且使用化学掺杂和表面电荷转移等方式掺杂使得器件可靠性不高,器件工作中在空气环境下非常容易受水蒸气、氧气等影响,本发明使用等离子体掺杂完成p型掺杂硫化钼薄膜的制备,能够进一步减小对薄膜的损伤,并且保证所制备得到的cmos反相器具有较高的稳定性。最终薄膜受损较小,cmos反相器整体性能较好。

70.在本发明优选的一些实施例中,步骤(s4)中,进行等离子体掺杂时,所使用的掺杂气体为氮气,能够通过氮原子原位替换硫化钼中的硫原子,快速有效完成掺杂;在本发明其他的一些实施例中,也可以使用氧气、氨气等作为掺杂气体;

71.为了进一步减小掺杂过程中对薄膜的损伤,在本发明优选的一些实施例中,步骤(s4)中,进行等离子体掺杂时,通过磁场控制进行掺杂,磁场控制包括磁场功率的控制,和/或轰击时间的控制。

72.以下为制备方法实施例。

73.实施例1:

74.基于硫化钼的cmos反相器的制备方法,包括如下步骤:

75.(1)准备一片有氧化层的单晶硅片和钼片;硅片厚度为380μm,上表面氧化层厚度为50nm,钼片厚度为0.5mm,将钼片表面打磨干净。清洗硅片与钼片并干燥,具体操作为:将硅片与钼片置入丙酮中,进行超声振荡5min,去除表面的有机杂质;再将其置入酒精中超声振荡5min,以去除表面的丙酮;之后在离子水中超声振荡5min;最后用氮气枪吹干。其中硅片、钼片的尺寸分别为20mm

×

30mm、(8~12)mm

×

30mm。

76.(2)清洗干燥两片半圆形石英舟,记为一号石英舟与二号石英舟。石英舟内径为30mm。制备硫化钼薄膜的过程中,需要用到cvd管式炉的两个温区,两温区分别位于前端进气口附近与后端出气口附近。在一号石英舟中央铺上高纯度的硫粉400~800mg,并将其置于前端温区;在钼片上,铺上moo3粉末3~8mg,将钼片放在二号石英舟中央,在钼片正上方放置硅片,硅片氧化层朝下,将二号石英舟置于后端温区。向cvd管式炉内通入氩气,气流量为40~120sccm,令整个石英管内保持氩气气氛。设置cvd管式炉的升温曲线,使前端温区达到120~200℃,后端温区达到790~850℃。两温区同时保持此温度5~15min,硅片的氧化层上会生长出n型硫化钼薄膜,等待温区自然冷却至室温得到样品a。

77.(3)将样品a置于匀胶机中,在样品a的上表面滴上适量型号az5214的负性光刻胶,设置匀胶机旋转参数,先以转速1500r/min旋涂10~20s,再以转速4000r/min旋涂20~40s;将上述旋涂好光刻胶的样品a放置在90~100℃的加热板上进行前烘1~3min。将上述样品a放在ma8紫外光刻机上进行前曝光,时长为0.8~2s,光源功率为20~30w。将前曝完成的样品a置于110~120℃的加热板上进行后烘1~3min。将后烘后的样品a放在ma8紫外光刻机上进行后曝,时间为8~20s。以显影液与去离子水比例为1:4配置溶液,将后曝完成的样品a放置于配置好的溶液中进行显影20~40s,显影后将样品a放于水中清洗5~15s,利用氮气枪

将其吹干,得到样品b。

78.(4)将样品b放进磁控溅射机真空腔内,将腔体抽至高真空状态,再向腔体内通入氮气,气体流速设置为40~80sccm。设置掺杂功率为10w~20w,观察到启辉后,立即将功率降低至3~8w进行掺杂,掺杂时间为20~40s,

79.通过磁场调控,达到低损伤的p型等离子体掺杂,得到样品c。

80.(5)将样品c置于丙酮中进行浸泡,去除样品上的光刻胶,再利用异丙醇去除掉残留的丙酮,利用氮气枪吹干,得到样品d。

81.(6)将样品a置于匀胶机中,在样品a的上表面滴上适量型号az5214的负性光刻胶,设置匀胶机旋转参数,先以转速1500r/min旋涂10~20s,再以转速4000r/min旋涂20~40s;将上述旋涂好光刻胶的样品a放置在90~100℃的加热板上进行前烘1~3min。将上述样品a放在ma8紫外光刻机上进行前曝光,时长为0.8~2s,光源功率为20~30w。将前曝完成的样品a置于110~120℃的加热板上进行后烘1~3min。将后烘后的样品a放在ma8紫外光刻机上进行后曝,时间为8~20s。以显影液与去离子水比例为1:4配置溶液,将后曝完成的样品a放置于配置好的溶液中进行显影20~40s,显影后将样品a放于水中清洗5~15s,利用氮气枪将其吹干,得到样品e。

82.(7)利用电子束蒸发技术将样品e蒸镀上电极,电极1与电极3之间的距离为n区沟道长度,n沟长为5~100μm,电极2与电极3之间的距离为p区沟道长度,p沟长为5~100μm,电极底层为金属ti,厚度为10~30nm,电极顶层为金属au,厚度为50~100nm,得到样品f。

83.(8)将样品f置于丙酮中进行浸泡,去除样品上的光刻胶,再利用异丙醇去除掉残留的丙酮,利用氮气枪吹干,得到基于硫化钼的cmos反相器。

84.实施例2:

85.基于硫化钼的cmos反相器的制备方法,包括如下步骤:

86.(1)准备一片有氧化层的单晶硅片和钼片;硅片厚度为380μm,上表面氧化层厚度为50nm,钼片厚度为0.5mm,将钼片表面打磨干净。清洗硅片与钼片并干燥,具体操作为:将硅片与钼片置入丙酮中,进行超声振荡5min,去除表面的有机杂质;再将其置入酒精中超声振荡5min,以去除表面的丙酮;之后在离子水中超声振荡5min;最后用氮气枪吹干。其中硅片、钼片的尺寸分别为20mm

×

30mm、10mm

×

30mm。

87.(2)清洗干燥两片半圆形石英舟,记为一号石英舟与二号石英舟。石英舟内径为30mm。制备硫化钼薄膜的过程中,需要用到cvd管式炉的两个温区,两温区分别位于前端进气口附近与后端出气口附近。在一号石英舟中央铺上高纯度的硫粉800mg,并将其置于前端温区;在钼片上,铺上moo3粉末3mg,将钼片放在二号石英舟中央,在钼片正上方放置硅片,硅片氧化层朝下,将二号石英舟置于后端温区。向cvd管式炉内通入氩气,气流量为50sccm,令整个石英管内保持氩气气氛。设置cvd管式炉的升温曲线,使前端温区达到140℃,后端温区达到810℃。两温区同时保持此温度10min,硅片的氧化层上会生长出n型硫化钼薄膜,等待温区自然冷却至室温得到样品a。

88.(3)将样品a置于匀胶机中,在样品a的上表面滴上适量型号az5214的负性光刻胶,设置匀胶机旋转参数,先以转速1500r/min旋涂15s,再以转速4000r/min旋涂30s;将上述旋涂好光刻胶的样品a放置在97℃的加热板上进行前烘2min。将上述样品a放在ma8紫外光刻机上进行前曝光,时长为1.1s,光源功率为21w。将前曝完成的样品a置于115℃的加热板上

进行后烘2min。将后烘后的样品a放在ma8紫外光刻机上进行后曝,时间为11s。以显影液与去离子水比例为1:4配置溶液,将后曝完成的样品a放置于配置好的溶液中进行显影35s,显影后将样品a放于水中清洗10s,利用氮气枪将其吹干,得到样品b。

89.(4)将样品b放进磁控溅射机真空腔内,将腔体抽至高真空状态,再向腔体内通入氮气,气体流速设置为60sccm。设置溅射功率为15w,观察到启辉后,立即将功率降低至5w进行掺杂,掺杂时间为20s,通过磁场调控,达到低损伤的p型等离子体掺杂,得到样品c。

90.(5)将样品c置于丙酮中进行浸泡,去除样品上的光刻胶,再利用异丙醇去除掉残留的丙酮,利用氮气枪吹干,得到样品d。

91.(6)将样品a置于匀胶机中,在样品a的上表面滴上适量型号az5214的负性光刻胶,设置匀胶机旋转参数,先以转速1500r/min旋涂15s,再以转速4000r/min旋涂30s;将上述旋涂好光刻胶的样品a放置在97℃的加热板上进行前烘2min。将上述样品a放在ma8紫外光刻机上进行前曝光,时长为1.1s,光源功率为21w。将前曝完成的样品a置于115℃的加热板上进行后烘2min。将后烘后的样品a放在ma8紫外光刻机上进行后曝,时间为11s。以显影液与去离子水比例为1:4配置溶液,将后曝完成的样品a放置于配置好的溶液中进行显影35s,显影后将样品a放于水中清洗10s,利用氮气枪将其吹干,得到样品e。

92.(7)利用电子束蒸发技术将样品e蒸镀上电极,电极1与电极3之间的距离为n区沟道长度,n沟长为40μm,电极2与电极3之间的距离为p区沟道长度,p沟长为10μm,电极底层为金属ti,厚度为10nm,电极顶层为金属au,厚度为70nm,得到样品f。

93.(8)将样品f置于丙酮中进行浸泡,去除样品上的光刻胶,再利用异丙醇去除掉残留的丙酮,利用氮气枪吹干,得到基于硫化钼的cmos反相器。

94.实施例3:

95.基于硫化钼的cmos反相器的制备方法,包括如下步骤:

96.(1)准备一片有氧化层的单晶硅片和钼片;硅片厚度为380μm,上表面氧化层厚度为50nm,钼片厚度为0.5mm,将钼片表面打磨干净。清洗硅片与钼片并干燥,具体操作为:将硅片与钼片置入丙酮中,进行超声振荡5min,去除表面的有机杂质;再将其置入酒精中超声振荡5min,以去除表面的丙酮;之后在离子水中超声振荡5min;最后用氮气枪吹干。其中硅片、钼片的尺寸分别为20mm

×

30mm、8mm

×

30mm。

97.(2)清洗干燥两片半圆形石英舟,记为一号石英舟与二号石英舟。石英舟内径为30mm。制备硫化钼薄膜的过程中,需要用到cvd管式炉的两个温区,两温区分别位于前端进气口附近与后端出气口附近。在一号石英舟中央铺上高纯度的硫粉600mg,并将其置于前端温区;在钼片上,铺上moo3粉末4mg,将钼片放在二号石英舟中央,在钼片正上方放置硅片,硅片氧化层朝下,将二号石英舟置于后端温区。向cvd管式炉内通入氩气,气流量为60sccm,令整个石英管内保持氩气气氛。设置cvd管式炉的升温曲线,使前端温区达到160℃,后端温区达到830℃。两温区同时保持此温度15min,硅片的氧化层上会生长出n型硫化钼薄膜,等待温区自然冷却至室温得到样品a。

98.(3)将样品a置于匀胶机中,在样品a的上表面滴上适量型号az5214的负性光刻胶,设置匀胶机旋转参数,先以转速1500r/min旋涂15s,再以转速4000r/min旋涂30s;将上述旋涂好光刻胶的样品a放置在97℃的加热板上进行前烘2min。将上述样品a放在ma8紫外光刻机上进行前曝光,时长为1.2s,光源功率为21w。将前曝完成的样品a置于115℃的加热板上

进行后烘2min。将后烘后的样品a放在ma8紫外光刻机上进行后曝,时间为12s。以显影液与去离子水比例为1:4配置溶液,将后曝完成的样品a放置于配置好的溶液中进行显影30s,显影后将样品a放于水中清洗10s,利用氮气枪将其吹干,得到样品b。

99.(4)将样品b放进磁控溅射机真空腔内,将腔体抽至高真空状态,再向腔体内通入氮气,气体流速设置为60sccm。设置溅射功率为15w,观察到启辉后,立即将功率降低至8w进行掺杂,掺杂时间为20s,通过磁场调控,达到低损伤的p型等离子体掺杂,得到样品c。

100.(5)将样品c置于丙酮中进行浸泡,去除样品上的光刻胶,再利用异丙醇去除掉残留的丙酮,利用氮气枪吹干,得到样品d。

101.(6)将样品a置于匀胶机中,在样品a的上表面滴上适量型号az5214的负性光刻胶,设置匀胶机旋转参数,先以转速1500r/min旋涂15s,再以转速4000r/min旋涂30s;将上述旋涂好光刻胶的样品a放置在97℃的加热板上进行前烘2min。将上述样品a放在ma8紫外光刻机上进行前曝光,时长为1.2s,光源功率为21w。将前曝完成的样品a置于115℃的加热板上进行后烘3min。将后烘后的样品a放在ma8紫外光刻机上进行后曝,时间为12s。以显影液与去离子水比例为1:4配置溶液,将后曝完成的样品a放置于配置好的溶液中进行显影30s,显影后将样品a放于水中清洗10s,利用氮气枪将其吹干,得到样品e。

102.(7)利用电子束蒸发技术将样品e蒸镀上电极,电极1与电极3之间的距离为n区沟道长度,n沟长为40μm,电极2与电极3之间的距离为p区沟道长度,p沟长为10μm,电极底层为金属ti,厚度为10nm,电极顶层为金属au,厚度为80nm,得到样品f。

103.(8)将样品f置于丙酮中进行浸泡,去除样品上的光刻胶,再利用异丙醇去除掉残留的丙酮,利用氮气枪吹干,得到基于硫化钼的cmos反相器。

104.本发明还以不同的参数组合实现了多个实施例,各实施例的关键参数设置如表1所示,步骤同上述实施例实施例1~3,在此将不作一一复述。

105.以下实施例均可制备得到性能稳定的cmos反相器,这说明了在合理范围内,制备过程可重复。

106.表1实施例3~12的关键参数

[0107][0108]

总体而言,在本发明公开的一种基于硫化钼的cmos逻辑器件反相器及制备方法,以硫化钼作为沟道材料,可以提高载流子的迁移率;采用磁场调控等离子体掺杂技术,可以有选择性地、低损耗地掺杂n型硫化钼薄膜;cmos器件的n,p区采用同种材料,无需转移;且制备方法简单、工艺可控。在集成电路领域具有广阔的应用前景。

[0109]

本领域的技术人员容易理解,以上所述仅为本发明的较佳实施例而已,并不用以限制本发明,凡在本发明的精神和原则之内所作的任何修改、等同替换和改进等,均应包含在本发明的保护范围之内。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。