1.本发明涉及一种电阻式存储装置,尤其是涉及一种具有铜接触洞导体(viaconductor)结构的电阻式存储装置。

背景技术:

2.半导体存储器为计算机或电子产品中用于存储数据的半导体元件,其可大概分为挥发性存储器(volatile)与非挥发性(non

‑

volatile)存储器。挥发性存储器是指当操作的电源中断后,所存储的数据便会消失的计算机存储器,而相对地,非挥发性存储器则具有不因电源供应中断而造成存储数据遗失的特性。电阻式随机存取存储器(resistiveram,rram)为一种非挥发性存储器,其具有低操作电压、低耗电以及高写入速度等特性而被视为可被应用于许多电子装置中的存储器结构。

技术实现要素:

3.本发明提供了一种电阻式存储装置,使用铜接触洞导体结构来改善接触洞导体的品质或/及相关制作工艺问题,并使堆叠结构中的第一电极具有氮化钽层与铜接触洞导体结构直接相连,由此改善使用铜接触洞导体结构的负面影响。

4.本发明的一实施例提供一种电阻式存储装置,其包括一堆叠结构以及一铜接触洞导体结构。堆叠结构包括一第一电极、一第二电极以及一可变电阻层。第二电极在一垂直方向上设置在第一电极之上,而可变电阻层在垂直方向上设置于第一电极与第二电极之间。铜接触洞导体结构设置在堆叠结构之下,第一电极包括一氮化钽层,且氮化钽层与铜接触洞导体结构直接相连。

附图说明

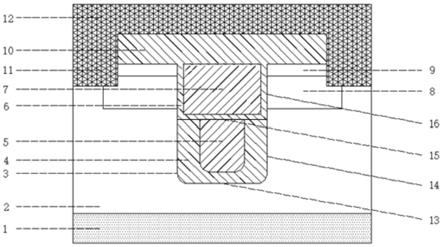

5.图1为本发明第一实施例的电阻式存储装置的示意图;

6.图2为本发明第二实施例的电阻式存储装置的示意图;

7.图3为本发明第三实施例的电阻式存储装置的示意图;

8.图4为本发明第四实施例的电阻式存储装置的示意图。

9.主要元件符号说明

10.12层间介电层

11.14金属线

12.16介电层

13.18介电层

14.20铜接触洞导体结构

15.22第一阻障层

16.22a第一层

17.22b第二层

18.24第一铜层

19.30堆叠结构

20.32氮化钽层

21.34导电层

22.36可变电阻层

23.42掩模层

24.44间隙壁

25.46层间介电层

26.50金属线

27.52第二阻障层

28.52a第一层

29.52b第二层

30.54第二铜层

31.101电阻式存储装置

32.102电阻式存储装置

33.103电阻式存储装置

34.104电阻式存储装置

35.be第一电极

36.d1第一方向

37.d2第二方向

38.l1长度

39.l2长度

40.te第二电极

41.tk1厚度

42.tk2厚度

43.tk3厚度

44.tk4厚度

45.tk5厚度

46.tk6厚度

具体实施方式

47.以下本发明的详细描述已披露足够的细节以使本领域的技术人员能够实践本发明。以下阐述的实施例应被认为是说明性的而非限制性的。对于本领域的一般技术人员而言显而易见的是,在不脱离本发明的精神和范围的情况下,可以进行形式及细节上的各种改变与修改。

48.在进一步的描述各实施例之前,以下先针对全文中使用的特定用语进行说明。

49.用语“在

…

上”、“在

…

上方”和“在

…

之上”的含义应当以最宽方式被解读,以使得“在

…

上”不仅表示“直接在”某物上而且还包括在某物上且其间有其他居间特征或层的含义,并且“在

…

上方”或“在

…

之上”不仅表示在某物“上方”或“之上”的含义,而且还可以包

括其在某物“上方”或“之上”且其间没有其他居间特征或层(即,直接在某物上)的含义。

50.说明书与权利要求中所使用的序数例如“第一”、“第二”等用词,是用以修饰权利要求的元件,除非特别说明,其本身并不意含及代表该请求元件有任何之前的序数,也不代表某一请求元件与另一请求元件的顺序、或是制造方法上的顺序,该些序数的使用仅用来使具有某命名的一请求元件得以和另一具有相同命名的请求元件能作出清楚区分。

51.在下文中使用术语“形成”或“设置”来描述将材料层施加到基底的行为。这些术语旨在描述任何可行的层形成技术,包括但不限于热生长、溅射、蒸发、化学气相沉积、外延生长、电镀等。

52.请参阅图1。图1所绘示为本发明第一实施例的电阻式存储装置101的示意图。如图1所示,电阻式存储装置101包括一堆叠结构30以及一铜接触洞导体(via conductor)结构20。堆叠结构30包括一第一电极be、一第二电极te以及一可变电阻层36。第二电极te,在一垂直方向(例如图1中所示的第一方向d1)上设置在第一电极be之上,而可变电阻层36在第一方向d1上设置于第一电极be与第二电极te之间。铜接触洞导体结构20设置在堆叠结构30之下,第一电极be包括一氮化钽层32,且氮化钽层32与铜接触洞导体结构20直接相连。使用铜接触洞导体结构20可改善接触洞导体的品质(例如降低电阻值)或/及相关制作工艺问题(例如改善填隙效果而降低在接触洞导体中产生空隙缺陷的机会),而使堆叠结构30中的第一电极be具有氮化钽层32与铜接触洞导体结构20直接相连则可改善使用铜接触洞导体结构的负面影响,例如可提升第一电极be阻挡铜接触洞导体结构20中的铜扩散至可变电阻层36的能力,避免可变电阻层36的材料品质受到铜扩散影响而导致在存储装置操作上的问题(例如电阻改变状况不符合设计值等)。

53.在一些实施例中,堆叠结构30可被视为具有可变电阻层36的电阻式存储单元,而可变电阻层36可被视为电阻式存储单元中的开关介质(switching medium),通过对堆叠结构中的上下电极(例如第一电极be与第二电极te)施加适合的电压,可改变电阻式存储单元的电阻值,使电阻式存储单元可于高电阻状态(high resistance state,hrs)与低电阻状态(low resistance state,lrs)之间进行切换,从而实现存储数据、读取数据以及重置等存储装置的操作模式。

54.在一些实施例中,电阻式存储装置101可还包括一层间介电层12、一金属线14、一介电层16以及一介电层18。金属线14可设置在层间介电层12中,介电层16可在第一方向d1上设置在层间介电层12与金属线14上,介电层18可在第一方向d1上设置在介电层16上,而堆叠结构30可在第一方向d1上设置在介电层18上。在一些实施例中,金属线14可被视为一沟槽导体(trench conductor)而主要沿水平方向(例如与图1中所示的第一方向d1以及第二方向d2正交的一水平方向)延伸,而铜接触洞导体结构20可主要沿第一方向d1延伸而贯穿金属线14上的介电层18与介电层16,由此与金属线14接触而形成电连接。

55.在一些实施例中,铜接触洞导体结构20可包括一第一阻障层22以及一第一铜层24,而第一铜层24可设置在第一阻障层22上。在一些实施例中,可先形成贯穿介电层18与介电层16的接触洞,然后再依序形成第一阻障层22与第一铜层24,接触洞可被第一阻障层22与第一铜层24填满,且第一阻障层22与第一铜层24可部分形成在接触洞之外的区域。然后,可利用一平坦化制作工艺(例如化学机械研磨制作工艺,cmp)将形成在接触洞之外的第一阻障层22与第一铜层24移除而形成铜接触洞导体结构20,故在铜接触洞导体结构20的剖视

图中,第一阻障层22可具有一u字型结构,但并不以此为限。

56.相较于其他导电材料(例如钨)所形成的接触洞导体结构,铜接触洞导体结构20中的第一铜层24可具有较佳的填隙(gap

‑

filling)能力,故可改善填隙效果而降低在接触洞导体中产生空隙缺陷的机会。然而,为了避免第一铜层24中的铜向外扩散至其他材料层而造成负面影响,第一铜层24可被第一阻障层22以及第一电极be中的氮化钽层32完全包围而达到阻止或/及降低铜扩散的效果。因此,在一些实施例中,第一电极be中的氮化钽层32在水平方向(例如但并不限于第二方向d2)上的长度(例如图1中所示的长度l2)可大于铜接触洞导体结构20在此水平方向上的长度(例如图1中所示的长度l1),由此降低因为制作工艺变异(例如对位偏移)造成铜接触洞导体结构20中的第一铜层24在第一方向d1上未被第一电极be中的氮化钽层32完全覆盖的机会,但并不以此为限。

57.此外,第一阻障层22的材料组成可与第一电极be中的氮化钽层32的材料组成相同(例如均为氮化钽)或不同。在一些实施例中,第一阻障层22可包括一第一层22a以及一第二层22b,第二层22b可设置在第一层22a上,且第二层22b的材料组成可不同于第一层22a的材料组成。举例来说,第一层22a可为阻障能力相对较佳但导电率相对较低的材料,而第二层22b可为阻障能力相对较差但导电率相对较高的材料,故第二层22b的导电率可高于第一层22a的导电率,但并不以此为限。在一些实施例中,第一层22a可为氮化钽层,而第二层22b可为钽层,故第一层22a的材料组成可与第一电极be中的氮化钽层32的材料组成相同。此外,在上述的状况下,第二层22b的厚度tk2可大于第一层22a的厚度tk1,而第一铜层24的厚度tk3可大于第二层22b的厚度tk2,由此在维持所需的阻障效果的状况下降低铜接触洞导体结构20的整体电阻值。举例来说,第一层22a的厚度tk1可约为16埃米(angstrom),第二层22b的厚度tk2可约为60埃米,而第一铜层24的厚度tk3可约为300埃米,但并不以此为限。此外,第一铜层24可被第一阻障层22以及第一电极be中的氮化钽层32完全包围,故第一阻障层22中的第一层22a与第二层22b可分别与第一电极be中的氮化钽层32直接连接。

58.在一些实施例中,第一电极be可还包括一导电层34在第一方向d1上设置在氮化钽层32与可变电阻层36之间,且导电层34的材料组成可不同于氮化钽层32的材料组成。在一些实施例中,可变电阻层36可包括金属氧化物例如过渡金属氧化物(transition metal oxide)、钙钛矿氧化物(perovskite oxide)或其他适合的可变电阻材料,而第二电极te与导电层34可分别包括铝、铂、钌、铱、镍、钴、铬、钨、铜、铪、锆、锌、金、钛、上述材料的合金、上述材料的混和物或其他适合的金属导电材料或非金属导电材料。在一些实施例中,导电层34的材料组成可与第二电极te的材料组成相同,例如第二电极te与导电层34可为与可变电阻层36之间接触状况较佳(例如接触阻抗较低)的材料。举例来说,第二电极te与导电层34可均为氮化钛,但并不以此为限。在一些实施例中,第一电极be中的氮化钽层32可为对铜的阻障能力相对较佳的材料,而第一电极be中的导电层34可为与可变电阻层36之间接触状况较佳或/及导电率相对较高的材料,而第一电极be中的氮化钽层32的厚度tk4与导电层34的厚度tk5可视产品的需要而进行搭配调整,故氮化钽层32的厚度tk4与导电层34的厚度tk5可大体上相等或不同。举例来说,氮化钽层32的厚度tk4与导电层34的厚度tk5可分别约为150埃米,但并不以此为限。

59.在一些实施例中,电阻式存储装置101可还包括一掩模层42、一间隙壁44、一层间介电层46以及一金属线50。掩模层42可在第一方向d1上设置在堆叠结构30上,间隙壁44可

设置在堆叠结构30的侧壁上,而层间介电层46可设置在介电层18上且覆盖堆叠结构30、掩模层42以及间隙壁44。金属线50可在第一方向d1上设置在堆叠结构30上且与第二电极te电连接。在一些实施例中,金属线50可被视为一沟槽导体而主要沿水平方向延伸,且金属线50可在第一方向d1上贯穿层间介电层46与掩模层42,由此与堆叠结构30中的第二电极te接触而形成电连接。此外,在一些实施例中,金属线50可包括一第二阻障层52与一第二铜层54,而第二铜层54可设置在第二阻障层52上。金属线50可被视为铜沟槽导体结构,第二铜层54的材料组成可与第一铜层22的材料组成相同,而第二阻障层52的材料组成可与第一阻障层22的材料组成相同,但并不以此为限。

60.在一些实施例中,第二阻障层52可包括一第一层52a以及一第二层52b,第二层52b可设置在第一层52a上,且第二层52b的材料组成可不同于第一层52a的材料组成。举例来说,第一层52a可为阻障能力相对较佳但导电率相对较低的材料,而第二层52b可为阻障能力相对较差但导电率相对较高的材料,但并不以此为限。在一些实施例中,第一层52a可为氮化钽层,而第二层52b可为钽层,第二层52b的厚度可大于第一层52a的厚度,而第二铜层54的厚度可大于第二层52b的厚度,由此在维持所需的阻障效果的状况下降低金属线50的整体电阻值。换句话说,金属线50的材料组成以及结构设计可与铜接触洞导体结构20相似,但并不以此为限。

61.在一些实施例中,层间介电层12与层间介电层46可包括超低介电常数(ultra low dielectric constant,ulk)介电材料(例如介电常数低于2.7的介电材料),例如苯并环丁烯(benzocyclclobutene,bcb)、hsq(hydrogen silsesquioxane)、msq(methyl silesquioxane)、硅氧碳氢化物(sioc

‑

h)、多孔性介电材料或其他适合的介电材料。金属线14可包括一低电阻材料以及一阻障层,低电阻材料可包括电阻率相对较低的材料例如铜、铝、钨等,而阻障层可包括氮化钛、氮化钽或其他适合的导电性阻障材料,但并不以此为限。在一些实施例中,介电层16可当作一蚀刻停止层,而介电层16的材料可包括氮掺杂碳化物(nitrogen doped carbide,ndc)、氮化硅、氮碳化硅(silicon carbon nitride,sicn)或其他适合的介电材料。介电层18可包括氧化硅、低介电常数介电材料或其他适合的介电材料。掩模层42与间隙壁44可分别包括单层或多层的介电材料,例如氮化硅、氮碳化硅或其他适合的介电材料。

62.在一些实施例中,层间介电层12可设置于一基底(未绘示)上,而此基底可包括半导体基底例如硅基底、硅锗半导体基底、硅覆绝缘(silicon

‑

on

‑

insulator,soi)基底或其他适合材料所形成的基底,但并不以此为限。此外,在形成层间介电层12之前,可于上述的基底上形成元件(例如晶体管)或/及电路(未绘示),而金属线14可向下电连接至基底上的元件或/及电路,但并不以此为限。在一些实施例中,电阻式存储装置101的制作方法可与半导体制作工艺中的后段(back end of line,beol)制作工艺整合,上述的层间介电层12、介电层16、介电层18以及层间介电层46可被视为于后段制作工艺中形成的层间介电层,而上述的金属14、铜接触洞导体结构20以及金属线50可被视为后段制作工艺中形成的互连结构的一部分,但并不以此为限。

63.下文将针对本发明的不同实施例进行说明,且为简化说明,以下说明主要针对各实施例不同之处进行详述,而不再对相同之处作重复赘述。此外,本发明的各实施例中相同的元件是以相同的标号进行标示,以利于各实施例间互相对照。

64.请参阅图2。图2所绘示为本发明第二实施例的电阻式存储装置102的示意图。如图2所示,在一些实施例中,铜接触洞导体结构20中的第一阻障层22可由单一材料形成,例如氮化钽、钽或其他适合的阻障材料,而第一阻障层22的厚度tk6可小于第一铜层22的厚度tk3。此外,在一些实施例中,导电层50中的第二阻障层52亦可由单一材料形成,例如氮化钽、钽或其他适合的阻障材料,而第一阻障层22的材料组成可与第二阻障层52的材料组成,由此达到简化相关制造方法的效果,但并不以此为限。

65.请参阅图3。图3所绘示为本发明第三实施例的电阻式存储装置103的示意图。如图3所示,在一些实施例中,导电层34的厚度tk5可大于氮化钽层32的厚度tk4。举例来说,当第一电极be中的导电层34的导电率明显高于氮化钽层32时,通过使导电层34的厚度tk5大于氮化钽层32的厚度tk4可降低第一电极be的整体电阻值,进而可有助于电阻式存储单元的操作表现,但并不以此为限。

66.请参阅图4。图4所绘示为本发明第四实施例的电阻式存储装置104的示意图。如图4所示,在一些实施例中,氮化钽层32的厚度tk4可大于导电层34的厚度tk5。举例来说,在一些实施例中,当可变电阻层36的材料品质较容易受到铜扩散影响时,可相对增加氮化钽层32的厚度tk4,由此提升阻挡铜接触洞导体结构20中的铜扩散至可变电阻层36的能力,且氮化钽层32的厚度tk4可大于第一阻障层22的厚度,但并不以此为限。

67.综上所述,在本发明的电阻式存储装置中,可使用铜接触洞导体结构来改善接触洞导体的品质或/及相关制作工艺问题,并使堆叠结构中的第一电极具有氮化钽层与铜接触洞导体结构直接相连,由此提升第一电极阻挡铜接触洞导体结构中的铜扩散至可变电阻层的能力,进而可改善电阻式存储装置的制作工艺良率或/及操作表现。

68.以上所述仅为本发明的优选实施例,凡依本发明权利要求所做的均等变化与修饰,都应属本发明的涵盖范围。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。