1.实施例涉及一种基座和一种半导体制造设备。

背景技术:

2.外延晶片是在用作衬底的抛光晶片上通过化学气相沉积(cvd,chemical vapor deposition)在加热到1100度或更高温度的反应器中形成的薄单晶层的晶片。即,外延晶片是通过在掺杂有例如硼(b)的杂质且电阻率低的硅晶片上,气相生长掺杂较少杂质且具有高电阻率的硅外延层来制造。

3.外延晶片具有高聚集能力、低闩锁特性和在高温下的强抗滑移性,因此近年来被广泛用作用于制造lsi器件以及mos器件的晶片。

4.这种外延晶片所需的质量项目是作为包括基底衬底和外延层的外延晶片表面项目的平坦度和颗粒污染水平,并且是外延层厚度均匀性、电阻率及电阻率均匀性、金属污染、堆垛层错、滑移位错等作为外延本身的项目。

5.其中,在外延晶片上制造半导体器件的过程中,平坦度对绝缘体上硅(soi,silicon on insulator)晶片的光刻工艺、化学机械抛光(cmp,chemical mechanical polishing)工艺和键合工艺有很大影响。特别是边缘滚降(ero,edge roll

‑

off)(其中晶片的边缘被向上或向下推动)对光刻工艺中的散焦、cmp工艺中的抛光均匀性和soi键合工艺中的键合缺陷有很大影响。随着晶片直径增大到300mm或更大,晶片边缘的平坦度在外延晶片的质量项目中越来越重要,因此有必要研究外延晶片的边缘平坦度畸变的原因。

6.特别地,当使用气体在晶片上形成外延层时,该气体不仅沉积在晶片的上表面上,而且沉积在晶片的下表面上,问题是沉积在晶片下表面上的薄膜进一步增加了外延晶片的bs zdd(背面z轴线二阶导数,backside z

‑

axis double derivative)的偏差。

技术实现要素:

7.【技术问题】

8.实施例旨在解决上述及其他问题。

9.实施例的另一目的是提供一种具有新颖结构的基座和半导体制造设备。

10.实施例的另一目的是提供一种能够使外延晶片的bs zdd的偏差最小化的基座和半导体制造设备。

11.实施例的另一目的是提供一种能够长时间制造无缺陷的半导体晶片的基座和半导体制造设备。

12.【技术解决方案】

13.根据实施例的一个方面,为了实现上述或其他目的,基座包括主体,主体包括具有边缘形状的上表面;凹部,凹部低于上表面并且包括下表面,下表面被上表面包围;以及壁架,壁架在上表面和下表面之间延伸以支撑晶片。壁架可以具有朝向下表面的中心倾斜的形状。壁架的表面的平坦度可以具有介于10μm到50μm之间的偏差。

14.根据实施例的另一方面,用于在晶片上生长薄膜的半导体制造设备包括:腔室,腔室具有内部空间;可旋转的支撑件,可旋转的支撑件定位在腔体内;以及基座,基座设置在支撑件上。基座可以包括:主体,主体包括具有边缘形状的上表面;凹部,凹部低于上表面并且包括下表面,下表面被上表面包围;以及壁架,壁架在上表面和下表面之间延伸以支撑晶片。壁架可以具有朝向下表面的中心倾斜的形状。壁架的表面的平坦度可以具有介于10μm到50μm之间的偏差。

15.【有益效果】

16.下面将描述根据实施例的基座和半导体制造设备的效果。

17.根据实施例中的至少一个实施例,通过加工基座的形状,使得壁架的表面的平坦度具有介于10μm到50μm之间的偏差,能够使外延晶片的bs zdd的偏差最小化。

18.根据实施例中的至少一个实施例,通过加工基座的形状,使得壁架的表面的平坦度具有介于10μm到50μm之间的偏差,外延晶片的bs zdd的偏差被保持在缺陷发生的范围内。优点在于能够长时间制造大量没有缺陷的外延晶片。

19.根据以下的详细描述,实施例的进一步的适用范围将变得显而易见。然而,应当理解,详细描述和例如优选实施例的特定实施例仅作为示例给出,因为本领域技术人员可以清楚地理解在实施例的精神和范围内的不同变化和修改。

附图说明

20.图1示出了晶片的晶体取向。

21.图2示出了外延晶片的bs zdd根据晶片的晶体取向的变化。

22.图3示出了根据实施例的半导体制造设备的横截面视图。

23.图4示出了根据实施例的半导体制造设备的基座的平面视图。

24.图5示出了根据实施例的半导体制造设备的基座的后视图。

25.图6示出了根据实施例的半导体制造设备的的基座的横截面视图。

26.图7示出了比较示例和实施例中的外延晶片的bs zdd的偏差。

27.图8示出了外延晶片的bs zdd根据比较示例和实施例中的晶片的晶体取向的变化。

具体实施方式

28.在下文中,将参考附图详细地描述本发明的优选实施例。

29.然而,本发明的技术精神不限于所描述的一些实施例,而是可以以各种不同的形式来实施,并且在本发明的技术精神的范围内,可以在实施例之间选择组件中一个或多个。组件中的一个或多个可以组合使用,也可以替代的使用。此外,除非特别定义和明确描述,本发明的示例中所使用的术语(包括技术术语和科学术语)可以被本发明所属领域的普通技术人员普遍理解。本发明的示例中所使用的术语可以被解释为某一含义,并且可以考虑相关技术的上下文含义来解释通用术语(例如预先定义的术语)。此外,在本发明的实施例中使用的术语是用于描述实施例,而不是旨在限制本发明。在该说明书中,单数形式也可以包括复数形式,除非在措辞中特别说明,并且当术语被描述为“b和(和)c中的至少一个(或一个以上)”时,术语可以与a、b和c组合。此外,在描述本发明实施例的组件时,可以使用例

如第一、第二、a、b、(a)、(b)等术语。这些术语仅用于区分组件与其他组件,并不通过术语限制本质、顺序或组件的顺序等。并且,当组件被描述为“连接”、“耦接”或“组合”到另一组件时,组件不仅直接连接、耦接或组合到另一组件,而且连接、耦接或组合到组件和另一组件之间的又一组件。可能因此包括“连接”、“耦接”或“组合”的情况。此外,当术语被描述为形成或布置在每个组件的“上(上方)或下(下方)”时,上(上方)或下(下方)不仅包括两个组件彼此直接接触的情况,而且还包括又一个组件形成或布置在两个组件之间的情况。此外,当表示为“上(上方)或下(下方)”时,不仅是基于一个分量的上方向,而且是基于一个分量的下方向,术语也可以包含方向的意思。

30.图1示出了晶片的晶体取向,并且图2示出了外延晶片的bs zdd根据晶片的晶体取向的变化。图2中的外延晶片可以是如下晶片:在该晶片中,薄膜(例如,外延层)形成在图1所示的晶片上。图1所示的晶片可以具有300mm的直径(150mm的半径)。在图2中,bs zdd的值为(

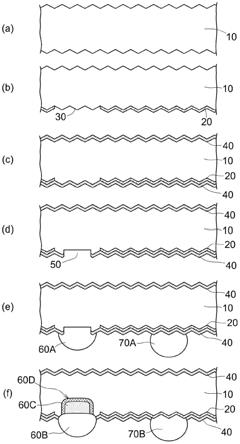

‑

)可以意味着外延晶片向下凸出弯曲。虽然未示出,但bs zdd的值为( )可以意味着外延晶片向上凸出弯曲。bs zdd的值为0可以意味着外延晶片相对于水平面精确地对齐而没有偏差。

31.在图1的晶片的晶体取向中,缺口所在的晶体取向为270

°

,基于该缺口,逆时针间隔90

°

的晶体取向为0

°

,沿顺时针方向间隔90

°

的晶体取向为180

°

。此外,从0

°

的晶体取向顺时针或逆时针间隔90

°

的晶体取向可以是90

°

。因此,从0

°

的晶体取向逆时针旋转一圈,经过0

°

到360

°

的晶体取向。

32.bs zdd根据相对于如下外延晶片的角度的变化如图2所示:在该外延晶片中,外延层形成在图1所示的晶片上。图2示出了在145.2mm、147.2mm、147.6mm和148mm处的bs zdd的变化。145.2mm、147.2mm、147.6mm和148mm中的每一个可以表示从晶片的中心向外间隔的距离。例如,148mm表示与晶片的中心间隔148mm的点,在148mm的点处可以看到bs zdd从0

°

到360

°

的变化。

33.例如,在145.2mm处,bs zdd从0

°

到360

°

几乎没有变化,而在148mm处,bs zdd从0

°

到360

°

变化非常显著。

34.例如,在148mm处晶体取向为140

°

时,bs zdd为

‑

60mm,而在晶体取向为250

°

时,bs zdd为

‑

22mm,在同一148mm处bs zdd在140

°

的晶体取向和250

°

的晶体取向之间的偏差可以是38mm(

‑

22mm

‑

(

‑

60mm))。

35.由此,可以看出,越靠近外延晶片的外端,bs zdd沿从0

°

的晶体取向到360

°

的晶体取向的偏差越大。

36.此外,如图2所示,即使在同一晶体取向下,例如在140

°

的晶体取向下,在离晶片的中心145.2mm的点处,bs zdd接近于零,但随着从145.2mm向外移动(goes)到外延晶片,bs zdd的值会迅速增加。

37.本发明人进行了一项研究,以解决bs zdd的偏差随着向外延晶片的外侧移动而增加,以及bs zdd的偏差沿从0

°

的晶体取向到360

°

的晶体取向而增加的现象。通过这些研究,本发明人确认了用于制造外延晶片的半导体制造设备的形状非常敏感地受bs zdd的偏差影响的事实。因此,本发明人深入研究了半导体制造设备的形状,以使bs zdd的偏差最小化,并获得了以下发明结果。

38.在下文中,为了使bs zdd的偏差最小化,将详细描述基座和半导体制造设备。

39.图3示出了根据实施例的半导体制造设备的横截面视图。

40.参照图3,根据实施例的半导体制造设备10包括:腔室20,腔室具有内部空间;支撑部件22,支撑部件定位在腔室20中并且是可旋转的;以及基座100,基座设置在支撑部件22上。

41.晶片w可以位于基座100上以形成半导体工艺,即,外延层。晶片w可以例如包括硅晶片。例如,晶片w具有300mm的直径和775μm的厚度,并且可以具有5mωcm到10mωcm(米

‑

欧姆

‑

厘米)的电阻率。晶片w可以具有表面平面取向。晶片w可以是p型单晶硅晶片,其中,上表面和下表面被镜面加工。

42.基座100可以通过将例如碳化硅(sic)或石墨的碳基材料附着到基座表面来形成。替代地,基座100本身可以由例如碳化硅(sic)或石墨的碳基材料来形成。

43.根据实施例的半导体制造设备10可以包括上圆顶50和下圆顶55。上圆顶50和下圆顶55可以包括透射材料(例如,高纯度石英),透射材料能够使光穿过以用于对晶片w进行辐射加热。石英具有高结构强度并且对半导体制造设备10的工艺环境是化学惰性的。

44.根据实施例的半导体制造设备10可以包括加热器件11。加热器件11可以对基座100和位于基座100上的晶片w进行辐射加热。

45.根据实施例的半导体制造设备10可以包括气体供应开口60和气体排放开口65。例如,气体供应开口60和气体排放开口65可以安装在基座100的两侧。例如,气体供应开口60可以安装在基座100的左侧,气体排放开口65可以安装在基座100的右侧。气体供应开口60和气体排放开口65可以被安装为彼此面对,并且基座100插入气体供应开口和气体排放开口之间。从气体供应开口60注入的氢气和用于外延生长的运载气体可以穿过基座100,然后通过气体排放开口65排出。

46.根据实施例的半导体制造设备10可以包括旋转轴70。旋转轴70可以通过支撑部件22连接到基座100。基座100也可以通过旋转轴70的旋转而旋转。

47.图4示出了根据实施例的半导体制造设备的基座的平面视图,图5示出了根据实施例的半导体制造设备的基座的后视图,以及图6示出了根据实施例的半导体制造设备的基座的横截面视图。

48.参照图4到图6,基座100可包括主体102、凹部108和壁架106,壁架位于主体102和凹部108之间。

49.彼此间隔开的孔118可以设置在基座100的下方。支撑件22的上部区域的一部分被紧固到孔118,使得基座100被固定到支撑件22,使得即使当旋转轴在工艺期间旋转时,基座100也不会在支撑件22上滑动。

50.凹部108可以位于基座100的中心区域中。壁架106和主体102可以围绕凹部108。主体102可以围绕壁架106。

51.主体102可包括边缘区域104。边缘区域104可以具有边缘形状。边缘形状例如可以是圆形形状,但不限于此。

52.主体102可包括上表面110。上表面110可以是边缘区域104的上表面。

53.凹部108可以定位为低于主体102的上表面110。凹部108可具有下表面126。下表面126可以具有向下凹的圆形形状,但不限于此。凹部108的下表面126可以被主体102的上表面110包围。凹部108可以具有与晶片的形状相对应的形状。例如,凹部108可以具有圆形形

状。

54.壁架106可以定位在凹部108和主体102之间。壁架106可以是从凹部108延伸到主体102中的区域。壁架106的表面116可以定位为低于主体102的上表面110。壁架106可以具有与晶片的边缘相对应的形状。例如,壁架106可以具有圆形边缘形状。晶片的边缘可以接触壁架106。

55.壁架106的表面116低于主体102的上表面110,使得第一侧壁124可以定位在壁架106的表面116和主体102的上表面110之间。凹部108的下表面126定位为低于壁架106的表面116,使得第二侧壁125可以定位在凹部108的下表面126和壁架106的表面116之间。第二侧壁125的高度可以小于第一侧壁124的高度。

56.例如,第一侧壁124的高度可以大于晶片的厚度。当晶片位于壁架106的表面116上时,晶片的上表面低于主体102的上表面110,使得氢气或运载气体更容易沉积到晶片的上表面上。

57.壁架106可以具有朝向下表面126的中心倾斜的形状。壁架106可以具有朝向下表面126的中心倾斜的表面。因此,晶片的边缘可以作为点与壁架106的表面116相切。

58.在实施例中,壁架106的表面116的平坦度具有介于10μm到50μm之间的偏差。当壁架106的表面116的平坦度具有介于10μm到50μm之间的偏差时,外延晶片的bs zdd的偏差可以最小化。

59.如图7所示,当壁架106的表面116的平坦度为75μm时(比较示例),外延晶片的bs zdd偏差可以为8mm。另一方面,当壁架106的表面116的平坦度如实施例中的一样为40μm时,外延晶片的bs zdd的偏差为2mm,并且与比较示例相比,该偏差至少减小4倍或更多。

60.如图8所示,在与外延晶片的中心间隔148nm的点处,测量了比较示例和实施例中的bs zdd根据从0

°

的晶体取向到360

°

的晶体取向的变化。

61.在比较示例中,从0

°

的晶体取向到360

°

的晶体取向,bs zdd值的范围从最小

‑

22mm到最大

‑

60mm,示出了

‑

38mm的偏差。特别地,在比较示例中,由于bs zdd值至少为

‑

22mm或更多,外延晶片的翘曲非常大。

62.在实施例中,从0

°

的晶体取向到360

°

的晶体取向,bs zdd值的范围从最小

‑

8mm到最大的

‑

32mm,示出了

‑

24mm的偏差。因此,在实施例中,沿从0

°

的晶体取向到360

°

的晶体取向,bs zdd的偏差也小于比较示例中的bs zdd的偏差,以及翘曲也小得多,从而显著地减少了缺陷的发生。

63.通常地,当bs zdd值变为

‑

50mm或更大时,相应的外延晶片是有缺陷的。因此,在比较示例中,在晶片的一些晶体取向中bs zdd的值超过

‑

50mm,因此晶片被视为有缺陷。在实施例中,由于在晶片的所有晶体取向中bs zdd的值都在

‑

32mm内,因此可以获得优异质量的外延晶片。

64.在实施例中,沿晶片的圆周方向接触晶片的壁架106的外围区域可以被定义为接触区域114。在此情况下,接触区域114的表面116的平坦度可以具有介于10μm到50μm之间的偏差。优选地,接触区域114的表面116的平坦度可以具有介于10μm到45μm之间的偏差。

65.同时,壁架106的表面116的平坦度的偏差可以由相对于参考点122的( )偏差和(

‑

)偏差来确定。例如,壁架106的表面116的平坦度的偏差可以是相对于参考点122的正偏差和负偏差之和。例如,参考点122可以是壁架106的表面116的平坦度的偏差的二分之一。

例如,参考点122可以是从凹部108的下表面126的最低点起具有第一高度h1的点。例如,参考点122可以是从基座100的下表面112的最低点起具有由第二高度h2设定的高度的点。

66.例如,( )偏差可以比参考点122高5μm到25μm。例如,(

‑

)偏差可以比参考点122低5μm到25μm。

67.根据实施例,通过加工基座100的形状,使得壁架106的表面116的平坦度具有介于10μm到50μm之间的偏差,外延晶片的bs zdd的偏差可以被最小化。

68.根据实施例,通过加工基座100的形状,使得壁架106的表面116的平坦度具有介于10μm到50μm之间的偏差,外延晶片的bs zdd的偏差被保持在缺陷发生的范围内。因此,能够长时间制造大量没有缺陷的外延晶片。

69.【工业适用性】

70.实施例可以应用于半导体制造的领域。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。