包括电荷存储区的像素电路

1.优先权声明

2.本技术要求于2020年4月30日提交的法国专利申请no.2004324的优先权权益,该申请的内容在法律允许的最大范围内通过引用整体合并于此。

技术领域

3.本公开总体上涉及电子器件或电路。本公开更具体地涉及传感器像素电路,并且具体地,涉及以测量飞行时间的原理工作的距离传感器、或tof传感器,以及用于控制该像素电路的方法。

背景技术:

4.在tof传感器中,光源向场景发射光,传感器的飞行时间检测像素电路、或tof像素电路接收由与该像素电路相关联的场景的点返回的光。飞行时间的测量,即由光从光源行进到与像素电路相关联的场景的点、并且从该点到像素电路所花费的时间,使得能够计算将像素电路与该点分离的距离。

5.在希望获得场景的浮雕图像的场景中,tof传感器包括tof像素电路的矩阵,以测量将每个像素电路和与该像素电路相关联的场景的点分离的距离。这使得能够获得将传感器与场景的不同点分离的距离的地图,该场景与该像素电路相关联,并且场景的浮雕图像然后可以由该距离的地图来重建。

6.tof传感器的像素电路包括电荷存储区,在该电荷存储区中,已在像素电路的光敏区或光转化区中光生的电荷在被读取之前接下来被临时存储。

7.在tof传感器的像素电路与关联于该像素电路的场景的点之间的距离的测量精度至少部分地取决于光生电荷从像素电路的光转化区向临时电荷存储区的转移。

8.其他像素电路包括电荷存储区,例如全局快门类型的图像传感器的像素电路。在全局快门类型的传感器的像素电路中,利用传感器而获得的图像的质量也至少部分地取决于光生电荷从像素电路的光转化区向临时电荷存储区的转移。

9.本领域需要利用包括至少一个电荷存储区的像素电路来解决已知问题的至少一些问题,具体地,已知像素电路属于tof传感器或属于全局快门图像传感器。

技术实现要素:

10.一个实施例解决包括至少一个电荷存储区的已知像素电路的缺点的全部或一些,特别是tof传感器的已知像素电路或全局快门图像传感器的已知像素电路。

11.一个实施例提供一种像素电路,包括:光转化区、绝缘的垂直电极、以及至少一个电荷存储区,光转化区属于半导体衬底的第一部分,以及每个电荷存储区属于衬底的第二部分,衬底的第二部分通过电极与衬底的第一部分物理分离。

12.根据一个实施例,电极从衬底的第一面穿过衬底,针对每个电荷存储区,像素电路还包括:第一掺杂区,与所述电荷存储区接触;第二掺杂区;栅极,放置在光转化区与所述第

二区之间的第一面上;以及电连接,在第一区与第二区之间;电极被配置为针对每个存储区将包括光转化区和第二区的衬底的第一部分与包括电荷存储区和第一区的衬底的第二部分电绝缘以及光学绝缘。

13.根据一个实施例,针对每个电荷存储区,所述连接被布置在衬底外侧、第一面上方。

14.根据一个实施例,每个电荷存储区在宽度方向上通过彼此平行并且面对的电极的两个部分来横向界定,与电荷存储区接触的第一区被布置在电荷存储区沿长度方向上的一端处。

15.根据一个实施例:衬底被掺杂有第一导电类型;光转化区包括被掺杂有第二导电类型的层并且被布置在面的第一侧上的衬底中;针对每个电荷存储区,第一区和第二区被布置在第一面的侧上的衬底中,并且电荷存储区被掺杂有第二导电类型;以及每个电荷存储区包括被掺杂有第二导电类型的盒,该盒被布置在第一面的侧上的衬底中。

16.根据一个实施例,针对每个电荷存储区:第一区和第二区具有相同的掺杂水平;和/或第一区和第二区具有与光转化区的层相同的掺杂水平;和/或电荷存储区的盒比第一区更重地掺杂。

17.根据一个实施例,针对每个电荷存储区,所述栅极放置在从第二区向光转化区的层延伸的沟道区域上,沟道区域比光转化区的层和第二区被更轻地掺杂有第二导电类型。

18.根据一个实施例,针对每个电荷存储区,沟道区域包括第一部分和第二部分,该第二部分比第一部分被更轻地掺杂,第二部分从光转化区的层向第一部分延伸,并且第一部分从第二部分向第二区延伸。

19.根据一个实施例,针对每个电荷存储区,第二区通过沟道区域和半导体衬底被掺杂有第一导电类型的半导体衬底的区域与光转化区的层分离。

20.根据一个实施例,针对每个电荷存储区,像素电路包括:掺杂读取区,被布置在包括电荷存储区的衬底的第二部分中的第一面的侧上的衬底中;以及附加的栅极,放置衬底的部分上,该衬底的部分在电荷存储区与读取区之间延伸,优选地,附加的栅极分布到电荷存储区。

21.根据一个实施例,至少两个电荷存储区属于衬底的相同第二部分。

22.另一实施例提供一种传感器,包括如所描述的多个像素电路。

23.根据一个实施例,两个相邻的像素电路共享衬底的相同第二部分或衬底的相同第一部分。

24.根据一个实施例,传感器包括电路,被配置为向每个像素电路的衬底的第一部分施加第一极化电势,以及针对每个像素电路的每个电荷存储区:在存储区的每个读取阶段期间,向包括存储区的衬底的第二部分施加第一极化电势;以及在所述存储区的读取阶段之外向第二部分施加第二极化电势,第一极化电势和第二极化电势优选地被配置,使得在电荷存储区中的势阱在第二极化电势被施加到衬底的第二部分时比第一极化电势被施加到衬底的第二部分时更深。

25.另一实施例提供一种用于所描述的像素电路的控制方法,包括利用第一电势的衬底的第一部分的极化;以及针对每个电荷存储区:在电荷存储区的每个读取阶段期间,利用第一电势使衬底的第二部分极化;以及在所述存储区的读取阶段之外,利用第二极化电势

使所述第二部分极化;电荷存储区在第二电势被施加到衬底的第二部分时比第一电势被施加到衬底的第二部分时更深。

附图说明

26.参考附图,前述特征和优势以及其他将在由图示而非限制的方式给定的特定实施例的以下描述中详细描述,其中:

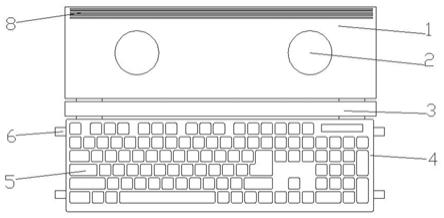

27.图1是示意地示出了示例性tof传感器的俯视图;

28.图2示出了示例性tof像素电路的电路图;

29.图3是图示图2的tof像素电路的控制方法的时序图;

30.图4在示意性俯视图中示出了图2中所示的类型的像素电路的实施例;

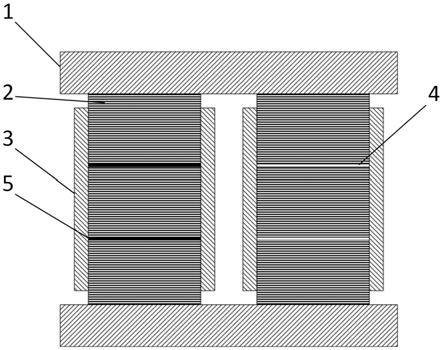

31.图5是沿图4中的虚线aa的示意性横截面图;

32.图6是沿图4中的平面bb的示意性截面图;

33.图7是沿图4中的平面cc的示意性截面图;

34.图8在示意性俯视图中示出了图4、图5、图6和图7的像素电路的变型实施例;

35.图9在示意性俯视图中示出了图4、图5、图6和图7的像素电路的另一变型实施例;

36.图10根据变型实施例在示意性俯视图中示出了图4、图5、图6和图7的像素电路的部分;

37.图11是沿图10中的虚线aa的示意性横截面图;

38.图12是图10的像素电路的部分的另一示例的示意性横截面图;以及

39.图13在示意性俯视图中示出了先前关于图4至图12所描述的类型的数个像素电路的组合的实施例。

具体实施方式

40.在各个图中,相似的特征已由相似的附图标记来指定。具体地,在各个实施例中共同的结构特征或/和功能特征可以具有相同的附图标记并且可以设置相同的结构、尺寸和材料特性。

41.为了清楚起见,仅图示和详细描述了对理解本文中所描述的实施例有用的操作和元件。

42.除非另有指示,否则当涉及连接在一起的两个元件时,这个表示除导体以外没有任何中间元件的直接连接,以及当涉及耦合在一起的两个元素时,这个表示这两个元件可以是连接的或它们可以通过一个或多个其他元件来耦合。

43.在以下公开中,除非另有指示,否则当涉及绝对位置限定词(诸如术语“前”、“后”、“顶”、“底”、“左”、“右”等)、或涉及相对位置限定词(诸如术语“之上”、“之下”、“较高”、“较低”等)、或涉及方向的限定词(诸如“垂直的”、“水平的”等)时,参考图中所示的方向。

44.除非另有规定,否则表述“约”、“近似”、“大致”和“大约”表示在10%以内,优选在5%以内。

45.图1是示例性tof传感器的示意性俯视图。传感器1包括tof像素电路的矩阵3,例如一千行乘一千列的矩阵。矩阵3与行解码器7和列解码器9相关联。行解码器7提供使得能够选择矩阵的行中的一行或另一行的信号11。列解码器9使得能够读取所选择的行的像素电

路。行解码器7和列解码器9由控制与处理电路15提供的信号13控制。控制与处理电路15例如包括与一个或数个存储器相关联的处理器。

46.在该示例中,其中传感器1是tof传感器,传感器1还与光源17相关联,以便照亮希望获得浮雕图像的场景。该光源17例如是激光器,该激光器的波长可以被包括在500nm与1000nm之间。光源17连接到控制与处理电路15,以便同步施加到矩阵3的tof像素电路与光源17的控制信号。

47.作为示例,光源17发射周期信号l

e

,例如正弦波,其频率可以被包括在20mhz与100mhz之间,例如等于25mhz。针对每个像素电路,相移在发射的光信号l

e

与由该像素电路接收的光信号l

r

之间被确定。接下来,将像素电路与其相关联的点分离的距离根据该相移来确定。

48.图2示出了tof像素电路的电路图,例如图1的传感器1的tof像素电路。

49.tof像素电路包括光敏元件或光转化元件pd,该pd的一个端子连接到节点21,并且其另一端子连接到用于施加参考电势的节点或轨,例如地。节点21借助于数个相同的组件耦合到读取节点sn,在这种情况中,两个组件s1和s2并联连接在节点21与sn之间。在该示例中,每个组件s

i

(i是等于1或2的整数)包括具有转移n沟道tmem

i

的mos晶体管、电荷存储区mem

i

和具有读取n沟道tsn

i

的mos晶体管。晶体管tmem

i

的源极连接到节点21,并且晶体管tmem

i

的漏极连接到存储区mem

i

的端子。晶体管tmem

i

由施加在其栅极上的信号vmem

i

控制。晶体管tsn

i

的源极连接到存储区mem

i

的另一端子,并且晶体管tsn

i

的漏极连接到读取节点sn。晶体管tsn

i

由施加在其栅极上的信号vsn

i

控制。存储区mem

i

的实施例将在下文中给出。

50.tof像素电路与可以由数个像素电路(例如四个像素电路)共享的读取器件相关联。读取器件包括如所示连接的预充电n沟道mos晶体管tres、作为跟随源安装的n沟道mos晶体管tsuiv、以及n沟道选择mos晶体管tsel。读取节点sn通过晶体管tres耦合到用于施加电源电势vdd(例如大于参考电势的电势)的节点或轨。晶体管tres由施加在其栅极上的信号vres控制。读取节点sn也耦合到晶体管tsuiv的栅极,该晶体管tsuiv的漏极耦合到电源轨,并且该晶体管tsuiv的源极借助于晶体管tsel耦合到像素电路的输出节点或输出轨23。晶体管tsel由施加在其栅极上的信号vsel控制。

51.在该示例中,像素电路tof还包括用于复位光敏元件pd的n沟道mos晶体管tres

pd

。晶体管tres

pd

的源极连接到节点21,并且晶体管tres

pd

的漏极连接到电源轨vdd。晶体管tres

pd

由施加在其栅极上的信号vres

pd

控制。

52.为了确定在发射的光信号l

e

与由像素电路所接收的光信号l

r

之间的相移通过向存储区mem1、然后mem2连续并且以定期间隔传输在光转化元件pd中光生的电荷而采样信号l

r

。执行这两个连续传输两者的总持续时间小于或等于信号l

e

和l

r

的周期。另外,这两次连续传输的集合被重复许多次,例如至少100000次。接下来,通过向节点sn传输区域mem1的电荷、然后区域mem2的电荷,在存储区中累积的电荷被读取。

53.现在将结合图3更详细地描述图2的tof像素电路的操作模式。

54.图3是由与传感器1(图1)相关联的光源17发射的光信号l

e

、由tof像素电路接收的光源l

r

以及数字信号vres

pd

、vres、vmem

i

、vsn

i

和vsel的时序图。默认情况下,信号vres

pd

、vmem

i

、vsn

i

和vsel处于低电平,并且信号vres处于高电平,晶体管tres

pd

、tmem

i

、tsn

i

和tsel然后处于关断状态,并且晶体管tres处于接通状态。

55.在该示例中,通过在时刻t0与t1之间将晶体管tres

pd

置于接通状态(信号vres

pd

处于高状态),光敏元件pd首先被复位。像素电路的整合循环然后在时刻t1处开始,并且与信号l

e

同步。

56.在整合循环期间,光生电荷朝着存储区mem

i

被传输到光敏区pd中。为此,传输晶体管tmem

i

依次被置于接通状态。更具体地,晶体管tmem1在时刻t2与t3之间被置于接通状态(vmem1为高),然后晶体管tmem2在时刻t4与t5之间将置于接通状态(vmem2为高)。如先前所指示的,这两次传输的集合接下来被重复许多次。贯穿整合循环的整个持续时间,信号vres处于高状态,晶体管tres接通,并且读取节点sn的电势大致等于电势vdd。

57.在整合循环的最后,从时刻t

10

,存储在存储区mem

i

中的每个存储区mem

i

的电荷被读取。为此,读取晶体管tsn

i

依次被置于接通状态,并且在存储于存储区mem

i

中的电荷的每次读取之后,在节点sn上的电势电平被测量和存储。更明确地,晶体管tsel在时刻t

10

处被置于接通状态(vsel为高),并且预充电晶体管tres在时刻t

11

处被置于关断状态(vres为低)。晶体管tsn1接下来在连续的时刻t

12

与t

13

之间被置于接通状态(vsn1为高),然后晶体管tsn2在连续的时刻t

14

与t

15

之间将置于接通状态(vsn2为高)。节点sn的第一电势电平和第二电势电平分别在时刻t

13

与t

14

之间以及在时刻t

15

与随后的时刻t

16

之间被测量和存储。在时刻t

16

,信号vsel返回到低状态,并且信号vres返回到高状态。然后,新的整合循环可以开始。

58.在该操作模式中,第一测量的电势电平和第二测量的电势电平代表分别存储在存储区mem1以及在存储区mem1和mem2中的电荷。在一个变型实施例中,在每次读取在存储区mem

i

中累积的电荷之后,通过在晶体管tres上施加具有高电势的脉冲,读取节点sn的复位被提供。在这种情况下,第一电势电平和第二电势电平代表分别存储在mem1和mem2的单个存储区中的电荷。

59.这两个电势电平使得能够确定在光信号l

e

与l

r

之间的相移并且因此由此推论出将像素电路与关联于该像素电路的场景的点分离的距离。

60.尽管已经描述了包括两个相同的组件s

i

的tof像素电路的实施例和控制,但在信号l

e

与l

r

之间的相移也可以通过使用包括多于两个组件s

i

的tof像素电路来确定,例如三个或四个组件si。

61.作为示例,传输到存储区mem

i

的持续时间被包括在5ns和30ns之间。当信号l

e

和l

r

的频率为25mhz时,分离到相同存储区mem

i

的两次传输的持续时间例如为40ns。在这种情况中,当向存储区mem

i

中的每个存储区mem

i

的电荷传输各自被完成250000次时,整合循环的持续时间可以约为10ms。从存储区mem

i

向读取节点sn的电荷传输持续时间例如被包括在1μs和10μs之间。

62.在像素电路中,当在光转化元件pd中的光生电荷以不想要的方式向电荷存储区mem

i

传输时,即这些电荷在对应的晶体管tmem

i

处于关断状态时被传输,这导致在像素电路与关联于该像素电路的场景的点之间的距离的测量上的误差。另外,如果到达光转化元件pd的光线接下来到达电荷存储区mem

i

并且通过光转化产生电荷,则这也引起在像素电路与关联于该像素电路的场景的点之间的距离的测量上的误差。

63.类似地,在全局快门传感器的像素电路中,光转化元件pd的光生电荷从像素电路向像素电路的电荷存储区mem

i

的不想要的传输、和/或通过光转化直接在像素电路的电荷存储区mem

i

中的电荷的产生导致利用传感器获得的图像质量的下降。

64.为了避免上述现象,发明人提出了一种像素电路,该像素电路包括一个或数个电荷存储区,其中当在光转化元件与该电荷存储区之间没有进行传输时,每个电荷存储区与像素电路的光转化元件光学绝缘并且电绝缘。更具体地,此处发明人提出了一种像素电路,其中像素电路的光转化区形成在半导体衬底的第一部分中,并且像素电路的每个电荷存储区形成在通过绝缘的垂直电极与衬底的第一部分物理分离的衬底的第二部分中。

65.现在将描述关于图4、图5、图6和图7的该像素电路的一个实施例。

66.图4、图5、图6和图7示意性地示出了包括至少一个存储区mem

i

的像素电路100的一个实施例。在该示例中,像素电路100是与关于图2所描述的像素电路1相对应的tof像素电路,像素电路100包括两个存储区mem1和mem2。图4是像素电路100的俯视图,图5、图6和图7分别是沿图4的虚线aa、图4的平面bb和图4的平面cc的截面图。

67.像素电路100包括例如由硅制成的半导体衬底102。衬底被掺杂有第一导电类型,在该示例中为类型p。优选地,衬底102的掺杂水平在接近衬底102的面104、图5、图6和图7中的上面时降低。

68.像素电路100还包括光敏区或光转化区pd。区pd被布置在衬底102中。区pd被布置在衬底的面104的侧上。换言之,区pd从其面104穿透衬底102。

69.区pd被配置为使得在区pd接收光时,电荷在区pd中通过将光子光转化成电子

‑

空穴对而产生,并且使得光生电子或光生空穴(在该示例中是电子)在区pd中累积,直到它们向存储区mem1或mem2传输为止。不旨在向区mem1或mem2传输的光生电荷(电子或空穴)(在该示例中是光生空穴)向施加到衬底102的极化电势释放。

70.针对每个电荷存储区mem

i

,像素电路100包括与该区mem

i

接触的掺杂区106

i

,据称该区106

i

与区mem

i

相关联。每个区域106

i

被布置在衬底102的面104的侧上的衬底102中。换言之,每个区域106

i

从衬底102的面104穿透衬底102。

71.在该示例中,像素电路100因此包括与电荷存储区mem1接触的区1061和与电荷存储区mem2接触的区1062。

72.针对每个电荷存储区mem

i

,像素电路100还包括掺杂区108

i

和栅极gmem

i

,据称掺杂区108

i

和栅极gmem

i

与该区mem

i

相关联。

73.每个区108

i

被布置在衬底102的面104的侧上的衬底102中。换言之,每个区108

i

从衬底102的面104穿透衬底102。区108

i

被掺杂有与区106

i

相同的导电类型,并且更具体地,被掺杂有与衬底102的导电类型相对的导电类型,在该示例中,区106

i

和108

i

因此被掺杂有类型n。另外,优选地,每个区108

i

具有与对应区106

i

相同的掺杂水平。

74.每个栅极gmem

i

在区pd和与栅极gmem

i

相关联的区mem

i

之间被放置在衬底102的面104上。换言之,衬底102包括区域126

i

(参见图5中的区域1261),该区域126

i

从区mem

i

延伸到区pd,该区域126

i

优选地由栅极gmem

i

完全覆盖。

75.栅极gmem

i

对应于晶体管tmem

i

的栅极,该晶体管tmem

i

的漏极和源极分别由区108

i

以及由区pd形成,并且该晶体管tmem

i

的沟道区域由区域126

i

形成。

76.在具有两个区mem1和mem2的像素电路100的该示例中,像素电路100因此包括区1081以及放置在区pd和区mem1之间的衬底102的面104上的栅极gmem1,也包括区1082以及放置在区pd和区mem2之间的衬底102的面104上的栅极gmem2。

77.针对每个区mem

i

,像素电路100包括在与区mem

i

相关联的两个掺杂区106

i

与108

i

之

间的电连接110

i

。电连接110

i

具有与区106

i

接触的端和与区108

i

接触的端。这里电连接是指由一个或数个导电元件(优选地,一个或数个金属导电元件)组成的连接。更准确地,如图5中所示,该电连接110

i

在衬底102外侧、衬底102的面104上方实现。例如,连接110

i

包括与各自的区106

i

和108

i

接触的两个过孔、以及放置在衬底102的面104上的互连结构(未示出)的金属层级的部分。该金属层级部分将两个过孔彼此电连接。

78.在这里描述的示例中,像素电路100因此包括在掺杂区1061与1081之间的电连接1101、以及在掺杂区1062与1082之间的电连接1102。

79.优选地,如在图4中所图示的,每个区106

i

和每个区108

i

包括接触恢复区112,该接触恢复区112被更重地掺杂有与其所属的区106

i

或108

i

相同的类型,在该示例中,接触恢复区因此被掺杂有类型n。每个电连接110

i

然后在其端中的每个端处与区112接触。

80.像素电路100还包括绝缘的垂直电极114。电极114从衬底102的面104穿透衬底102,电极114大致正交于面104。电极114在衬底102的整个厚度上穿过衬底102。换言之,电极114从衬底102的面104延伸到衬底102的与面104相对的另一面116(图5和图6中的下面)。尽管这在图4中未示出,以便不使附图过载,如图5中所示,电极114包括导电垂直壁或导电核心1141、以及覆盖壁1141的绝缘核心1142,并且更准确地,绝缘核心1142覆盖壁1141的所有侧分区,壁1141因此与衬底102分离并且电绝缘。导电壁1141例如由掺杂的多晶硅制成。层1142例如是氧化硅层或绝缘层的叠加(例如形成ono(氧化物氮化物氧化物)结构的氧化硅层、氮化硅层和氧化硅层的叠加)。

81.在操作期间,极化电势被施加到电极114。在该示例中,旨在传输到区mem

i

的光生电荷是光生电子,该极化电势被选择以便向电极114的分区吸引空穴。作为示例,该极化电势等于

‑

2v。

82.电极114将衬底102物理上分离成数个部分。换言之,电极114在衬底102中限定衬底102的数个部分,该衬底102的数个部分通过电极114彼此电绝缘并且光学绝缘。例如,如果衬底102的这两个部分中的一个部分由电极114的部分完全包围,则据称衬底102的两个不同部分彼此电绝缘并且光学绝缘。

83.更具体地,区pd和区108

i

属于衬底102的第一部分,并且区mem

i

和区106

i

属于衬底102的至少一个第二部分,并且与衬底102的第一部分电绝缘并且光学绝缘。换言之,属于衬底102的第二部分的每个区mem

i

与包括区pd的衬底102的第一部分电绝缘并且光学绝缘。针对每个区mem

i

,区mem

i

与接触该区mem

i

的区106

i

属于衬底102的相同第二部分。

84.在操作期间,当光由区pd接收并且电荷在区pd中被光生和累积时,只要栅极gmem1或gmem2不被控制以便将这些光生电荷从区pd分别向区1081或1082传输,这些电荷就无法到达区mem1和mem2,这是因为电绝缘通过在包括区pd的衬底102的第一部分与包括区mem1和mem2的衬底102的(一个或多个)第二部分之间的电极114来实现。

85.另外,当光线到达包括区pd的衬底102的第一部分时,该光线由电极114阻挡并且无法传播到包括区mem1和/或区mem2的衬底102的第二部分,其中该光线可以通过光转化产生了电荷。

86.在由图4、图5、图6和图7所图示的实施例中,每个区mem

i

属于衬底102的不同第二部分。换言之,在该示例中,区pd以及区1081和1082属于衬底的第一部分,区mem1和1061属于衬底102的一个第二部分,以及区mem2和1062属于衬底102的另一个第二部分。第二部分与第

一部分电绝缘并且光学绝缘,在该示例中这是因为每个第二部分由电极114的对应部分完全包围。

87.在俯视图中,换言之,在与面104和116平行的平面中,像素电路100的每个区mem

i

具有矩形形状。每个区mem

i

由电极114的平行并且彼此面对的两个部分在宽度方向上来横向界定。针对每个存储区mem

i

,在长度方向上考虑,与其相关联的区106

i

例如被布置在区mem

i

的一端。优选地,两个区106

i

和108

i

通过连接110

i

彼此连接,即与相同区mem

i

相关联的两个区106

i

和108

i

分别被布置在电极114的相同部分的每侧上,例如在电极114的该部分的每侧上彼此面对。

88.优选地,如图4中所示,区pd至少部分地由电极114横向(即在平行于面104和116的平面中)界定。换言之,电极114被布置在区pd的轮廓的至少部分上或构成区pd的轮廓的至少部分。在图4的示例中,在俯视图中,区pd具有大致正方形的形状。如图4中所示,然后电极114例如被布置在区pd的三个侧上。如图4中所示,区域108

i

然后优选地被布置在区pd的拐角处。

89.在所图示的示例中,区mem1沿区pd的第一侧布置,并且区mem2沿区pd的第二侧布置。提供沿区pd的一侧布置的区mem

i

使得能够针对电极114的部分在宽度方向上横向界定区mem

i

,也可以界定与该区mem

i

邻接的区pd的侧。这允许像素电路100特别紧凑。

90.在本实施例中,区mem

i

是固定电荷存储区或存储器区,并且区pd是固定光电二极管。因此,在每个区mem

i

和区pd中,存在电荷可以在其中存储或累积的势阱。区mem

i

或区pd的阱的深度具体取决于施加到包括该区mem

i

或区pd的衬底102的部分的极化。

91.根据一个实施例,在操作期间,第一极化电势被施加到包括区pd的衬底102的第一部分。另外,针对每个存储区mem

i

,在区mem

i

的每个读取阶段期间,并且更准确地,在该区mem

i

的每个读取阶段的整个持续时间期间,第一极化电势被施加到包括区mem

i

的衬底102的第二部分。在区mem

i

的读取阶段之外,第二极化电势被施加到包括区mem

i

的衬底102的第二部分。

92.第一极化电势和第二极化电势被选择,使得在区mem

i

中的势阱在包括该区mem

i

的衬底102的第二部分被第二电势极化时,比当其被第一电势极化时更深。因此,当区mem

i

不在被读取的过程中时,大量电荷可以在区mem

i

中存储。

93.作为示例,在p掺杂衬底102的情况中,第一电势例如是地电势,第二电势然后大于第一电势,例如大致等于1v。

94.为包括区mem

i

的衬底102的(一个或多个)第二部分提供两个极化电势是可能的,这是因为这个或这些(一个或多个)第二部分通过电极114与包括区pd的衬底的第一部分电绝缘。

95.作为示例,第一极化电势和第二极化电势由像素电路100的控制电路提供,例如通过包括数个像素电路100的传感器(例如与关于图1所述的传感器类似的传感器)由像素电路的控制电路提供。

96.针对每个区mem

i

,像素电路100还包括在衬底102的面104的侧上被布置在衬底102中的掺杂的读取区118

i

。换言之,区118

i

从衬底102的面104穿透衬底102。据称区118

i

与该区mem

i

相关联。区118

i

被掺杂有与区106

i

和区118

i

相同的导电类型,即在该示例中为类型n。

97.针对每个区mem

i

,像素电路100还包括栅极120

i

,栅极120

i

放置在衬底102的部分

121

i

上,该部分121

i

在区mem

i

与关联于该区mem

i

的读取区118

i

之间延伸。换言之,区域121

i

从区mem

i

向区118

i

延伸,该区118

i

优选地由栅极120

i

完全覆盖。据称栅极120

i

与该区mem

i

相关联。栅极120

i

对应于关于图2所述的晶体管tsn

i

的栅极,与该栅极120

i

相关联的读取区120

i

和区mem

i

形成晶体管tsn

i

的源极和漏极,并且衬底的部分121

i

形成该晶体管tsn

i

的沟道区域。

98.在这里所述的示例中,像素电路100因此包括与区mem1相关联的区1181和栅极1201、以及与区mem2相关联的区1182和栅极1202。

99.每个栅极120

i

与关联于该栅极120

i

的区mem

i

属于衬底102的相同第二部分。

100.如图4和图5中所示,与区mem

i

相关联的读取区118

i

例如被布置在区mem

i

的一端的侧上,在长度方向上考虑,该区mem

i

的一端在与区106

i

接触的区mem

i

的端的对面,该区106

i

与该区mem

i

相关联。

101.优选地,每个栅极120

i

在与其关联的电荷存储区mem

i

上分布,这有利于电荷从区mem

i

向对应的区118

i

的传输。

102.现在将更详细地描述先前描述的区mem

i

和pd的实现方式。

103.如图5、图6和图7中所图示的,区pd包括掺杂有与区106

i

、108

i

和118

i

相同的导电类型的层122,即在该示例中为类型n。优选地,层122的掺杂水平小于或等于(例如等于)区106

i

和108

i

的掺杂水平。

104.层122在在衬底102的面104的侧上被布置衬底102中。换言之,层122从衬底102的面104穿透衬底102。

105.尽管这在图中不可见,但在俯视图中,层122在区pd的整个表面上横向延伸到界定区pd的电极114的部分。

106.另外,尽管这在图4至图7中未示出,但优选地,层122在面104的侧上被覆盖有与衬底102相同类型的掺杂层,在该示例中为类型p,该层比衬底102更重地掺杂。该高p掺杂层具有与面104结合的面。优选地,在面104的侧上,层122完全被该高p掺杂层覆盖。

107.当在正交于面104的方向上时,衬底102的掺杂水平在接近表面104时降低,并且更准确地,在接近层122时降低,光生电荷旨在向区mem

i

传输,即在该示例中,光生电子更容易被汲取到层122,在向区mem

i

传输之前,它们可以在层122处累积。

108.每个区mem

i

包括被掺杂有与层122相同的导电类型的盒124,即在该示例中为类型n,该盒124被布置在面104的侧上的衬底102中。换言之,盒124从衬底102的上面104穿透衬底102。优选地,每个盒124的掺杂水平大于区106

i

和108

i

的掺杂水平。

109.尽管这在图中不可见,但在俯视图中,每个区mem

i

的盒124在区mem

i

的整个表面上延伸。盒124因此从电极114的平行部分中的一个平行部分延伸到另一平行部分,该电极114在宽度方向上横向界定区mem

i

。

110.另外,尽管这在图4至图7中未示出,但每个盒在面104的侧上被覆盖有与衬底102相同类型的掺杂层,在该示例中为类型p,该层比衬底102更重地掺杂。该高p掺杂层具有与面104结合的面。优选地,在面104的侧上,每个盒124完全由该高p掺杂层覆盖,其中由对应的栅极120

i

覆盖的盒124的任何部分除外。优选地,该高p掺杂层具有与覆盖层122的高p掺杂层相同的掺杂水平,例如,因为这些层是同时制造的。

111.在操作期间,当电极114被极化并且电荷(在该示例中为空穴)沿电极114累积时,

这引起在一方面上的电极114的绝缘层1142与在另一方面上的盒124以及n掺杂层122之间的边界的钝化。该钝化阻止光生电荷,并且更明确地,在该示例中为被捕获在该界面处的光生电子。另外,空穴沿电极114的该累积形成导电层,该导电层然后与衬底102处于相同的电势并且横向邻接盒124和层122。

112.根据一个实施例,如图5中所示,利用栅极gmem

i

覆盖并且在区pd和对应区108

i

之间延伸的衬底102的每个部分126

i

被掺杂有与层120和区106

i

相同的导电类型。即在该示例中为类型n。这使得在电荷从区pd向区mem

i

的传输期间,可以减少、甚至抵消被捕获在衬底102与栅极gmem

i

的绝缘体之间的边界处的剩余电荷数目。

113.另外,在该实施例中,该沟道区域126

i

优选地不像层122和区域108

i

一样地被强烈掺杂,沟道区域126

i

在区域108

i

与层122之间延伸。因此,在电荷经由区126

i

从区pd向对应的区mem

i

的传输之外,沟道区域126

i

形成针对电荷的势垒。

114.根据一个实施例,如图5中所图示的,针对每个区mem

i

,当区域126

i

被掺杂有与衬底102的导电类型相对的导电类型时,即在该示例中为类型n,区域126

i

包括第一部分1261

i

和第二部分1262

i

,第一部分1261

i

和第二部分1262

i

被掺杂有与衬底102的导电类型相对的导电类型,即在该示例中为n型。第二部分1262

i

比第一部分1261

i

更轻地掺杂。部分1262

i

从层122向部分1261

i

延伸,并且部分1261

i

从部分1262

i

向对应的区108

i

延伸。部分1262

i

然后在部分1261

i

与层122之间形成势垒,该势垒阻止在部分1261

i

中存在的电荷向层122返回。当施加在对应的栅极gmem

i

上的电势从用于区域126

i

在区108

i

与层122之间形成势阱的第一值切换到用于区域126

i

在区108

i

与层122之间形成势垒的第二值时,这在电荷从区pd向区mem

i

传输结束时特别有利。

115.针对每个区mem

i

,层122的任何部分都不与区108

i

直接接触,该区108

i

与该区mem

i

相关联的,具体如图4、图5和图7中所示。例如,不仅通过由对应的栅极gmem

i

覆盖的沟道区域126

i

,而且还通过被布置在栅极gmem

i

的任一侧上的衬底102的区域128

i

,将区108

i

与层122分离。

116.根据一个实施例,如关于图2所描述的,并且如图4和图6中所示,像素电路100包括晶体管tres

pd

。

117.在该示例中,晶体管tres

pd

被称为“垂直栅极”晶体管。换言之,晶体管tres

pd

包括与层122相同类型的掺杂区域129,即在该示例中为类型n,区域129比层122更重地掺杂并且由穿过衬底102的绝缘的垂直电极130或垂直栅极130包围。垂直栅极130包括导电壁1301和绝缘层1302,该绝缘层1302将壁1301与衬底102分离并且绝缘。优选地,壁1301和层1302分别与电极114的壁1141和层1142完全相同。空间e被布置在电极130的彼此面对的两端之间(在图6中以虚线表示)。在该空间e中,层122向上延伸到区域129。在操作期间,电源电势被施加到区域129。另外,取决于施加到栅极130的控制信号(图2中的vres

pd

)的电势电平,势垒在空间e中形成并且阻止光生电荷向区域129的通过(晶体管tres

pd

关断),或者势垒丢失并且在层122中光生的电荷从区pd向被施加到区域129的电势释放(晶体管tres

pd

接通)。

118.图8以示意性俯视图示出了图4、图5、图6和图7的像素电路100的变型实施例。

119.在该变型中,数个区mem

i

属于衬底102的相同第二部分,该第二部分与包括区pd的衬底102的第一部分光学绝缘并且电绝缘。仅突出示出在图4、图5、图6和图7的像素电路100与图8的像素电路100之间的差异。

120.优选地,如图8中所图示的,由数个区mem

i

共享的该衬底102的第二部分包括部分132,该部分132未由以下项占据:区mem

i

、与区mem

i

相关联的区106

i

和118

i

、以及对应的栅极120

i

。因此,晶体管(未示出)(例如关于图2所述的晶体管tres、tsuiv和tsel)可以在该部分132中形成。

121.更具体地,在该示例中,区mem1与区mem2属于衬底102的相同第二部分。优选地,衬底102的该第二部分包括如上所述的部分132。例如,区mem1沿区pd的第一侧布置,区mem2沿区pd的与第一侧相对的第二侧布置,并且部分132沿区pd的第三侧布置。因此,界定了区pd的侧的区域132的电极的部分也界定了区pd的第三侧。这允许像素电路100特别紧凑。

122.图9以示意性俯视图示出了图4、图5、图6和图7的像素电路100的另一变型实施例。仅突出示出在图4、图5、图6和图7的像素电路100与图9的像素电路100之间的差异。

123.在该变型中,针对每个区mem

i

,像素电路100包括附加电荷存储区mem

i’,该附加电荷存储区mem

i’与区mem

i

完全相同并且与区mem

i

形成在衬底102的相同第二部分中,据称区mem

i’与区mem

i

相关联。

124.不像区mem

i

,区mem

i’不与区106接触。相对地,区mem

i’与区mem

i

共享相同的栅极120

i

和相同的读取区118

i

。另外,区mem

i

的掺杂盒124(图5)包括到区mem

i’的掺杂盒(未示出)的延伸(未示出)。该延伸由栅极120

i

覆盖。因此,当被施加到栅极120

i

的电势使得晶体管tsn

i

(图2)处于关断状态时,如果已被传输到区mem

i

的光生电荷的数目变得太高,则过量的电荷扩散到区mem

i’中,它们可以在被读取之前与存储在区mem

i

中的电荷同时被存储在区mem

i’中。

125.优选地,如图9中所示,每个区mem

i’沿与其相关联的区mem

i

布置,使得在横向上和宽度方向上界定区mem

i

的电极114的两个部分中的一个部分也是在横向上和宽度方向上界定区mem

i’的电极114的两个部分中的一个部分。

126.图10以示意性俯视图示出了根据变型实施例的图4、图5、图6和图7的像素电路100的部分。图11是沿图10中的虚线aa的示意性横截面图。图12是图10的像素电路的部分的另一示例的示意性横截面图。仅突出示出图4、图5、图6和图7的像素电路100与图10、图11和图12的像素电路100之间的差异。

127.图10、图11和图12,更特别是图10,示出了区pd的部分、晶体管tres

pd

的部分、电极114的部分、区mem

i

、与该区mem

i

相关联的区106

i

、108

i

和118

i

、以及与该区mem

i

相关联的栅极gmem

i

和120

i

。区mem1在该示例中被示出,但要理解的是,这里针对区mem1描述的内容适用于所有区mem

i

。

128.在该变型中,区1061和1081各自包括接触恢复区112。

129.区1081的区域112通过绝缘沟槽134与接触区1081的电极114的部分分离。这使得能够限制在电极114与区域112之间的电容耦合。作为示例,沟槽134从衬底102的面104穿透衬底102,深度上小于区108

i

。优选地,区1081的区域112在其侧中的一侧上具有悬于栅极gmem1之上的一侧,并且在其所有其他侧上由沟槽134邻接。

130.类似地,区1061的区域112也可以通过绝缘沟槽134与接触区1061的电极114的部分分离。作为示例,沟槽134从衬底102的面穿透衬底102,深度上小于区106

i

。优选地,区1061的区域112具有与区mem1接触的一侧,并且在其所有其他侧上由沟槽134包围。

131.如图10和图12中所示,优选地,区1181也通过绝缘沟槽134与包围区118

i

的电极114

的部分分离。优选地,沟槽134完全包围区1181,除了在与对应的栅极1201的一侧对准的区1181的侧上。

132.图10、图11和图12的变型实施例与图8的变型和/或与图9的变型兼容。另外,变型8和9可以被结合。

133.当上述像素电路100是传感器(例如关于图1所述类型的tof传感器)的像素电路100的矩阵的部分时,相邻像素电路可以共享公共元件,具体是衬底102的第一部分或第二部分。

134.作为示例:像素电路100的区mem

i

可以与相邻像素电路100的区mem

i

属于衬底102的相同第二部分,或换言之,两个相邻像素电路100可以共享衬底102的相同第二部分;和/或两个相邻像素电路100可以共享相同的电极114;和/或像素电路100的区pd可以与相邻像素电路100的区pd属于衬底102的相同第一部分,或换言之,两个相邻像素电路100可以共享衬底102的相同第一部分;和/或像素电路100的区mem

i

和相邻像素电路100的区mem

i

可以与相同的读取区118

i

相关联;和/或像素电路100的所有区mem

i

可以属于衬底102的第二部分,相邻像素电路100的所有区mem

i

也属于该第二部分,该衬底的第二部分能够包括由两个相邻像素电路100共享的区域132。

135.现在将描述包括公共元件(或者换言之,由数个相邻像素电路100共享的元件)的数个像素电路100的关联的一个特定示例。

136.图13以示意性俯视图示出了包括像素电路100的矩阵的传感器(例如传感器1)的数个相邻像素电路100的结合的实施例。

137.更明确地,图13示出了像素电路100的矩阵的相同行或相同列(优选地,矩阵的相同列)的三个像素电路100,该三个像素电路100在下文中分别参考100

‑

1、100

‑

2和100

‑

3。像素电路100

‑

2例如被布置在像素电路100

‑

1与100

‑

3之间,像素电路100

‑

1和100

‑

3中的每个像素电路与像素电路100

‑

2相邻。在图13中,部分示出的像素电路100

‑

1被布置在图的顶处,完全示出的像素电路100

‑

2被布置在图的中心处,以及部分示出的像素电路100

‑

3被布置在图的底处。

138.在该示例性实施例中,如关于图8所述,每个像素电路100

‑

1、100

‑

2、100

‑

3具有两个区mem1和mem2,该两个区mem1和mem2属于衬底102的相同第二部分,该衬底102的第二部分包括区域132。另外,如关于图9所述,每个像素电路100

‑

1、100

‑

2、100

‑

3的每个区mem

i

与附加的区mem

i’相关联。最后,如关于图10、图11和图12所述,针对每个区108

i

、每个区106

i

和每个区118

i

,绝缘沟槽134被提供。

139.在该实施例中,所有像素电路100

‑

1、100

‑

2和100

‑

3共享相同的电极114。确实,尽管图13似乎示出数个分离的电极114,但后者实际上对应于相同电极114的部分。优选地,尽管这在图13中不可见,但传感器的像素电路100的矩阵的所有像素电路100共享相同的电极114。

140.在该实施例中,像素电路100

‑

2的区pd与像素电路100

‑

1的区pd属于衬底102的相同第一部分。相对地,像素电路100

‑

3的区pd属于衬底102的另一第一部分。

141.优选地,如图13中所示,共享衬底102的相同第一部分的两个像素电路100

‑

1和100

‑

2共享相同的晶体管tres

pd

。在该示例中,其中晶体管tres

pd

是垂直栅极晶体管,电极130然后包括两个分离的部分。空间e在电极130的第一部分的第一端与电极130的第二部分

的第一端之间被布置在像素电路100

‑

1的区pd的侧上,并且另一空间e在电极130的第一部分的第二端与电极130的第二部分的第二端之间被布置在像素电路100

‑

2的区pd的侧上。

142.另外,由于像素电路100

‑

1和100

‑

2共享衬底102的相同第一部分,尽管像素电路100

‑

1不与像素电路100

‑

2共享其区108

i

,但像素电路100

‑

1的区108

i

的沟槽134优选地是与像素电路100

‑

2的对应区108

i

的沟槽134相同的沟槽。

143.在该实施例中,像素电路100

‑

2的区mem

i

和mem

i’与像素电路100

‑

3的区mem

i

和mem

i’属于衬底102的相同第二部分。相对地,像素电路100

‑

1的区mem

i

和mem

i’属于衬底102的另一第二部分。

144.由于像素电路100

‑

2和100

‑

3共享衬底102的相同第二部分,其包括的区132由这两个像素电路100

‑

2和100

‑

3共享,如图13中所示。因此,晶体管形成在该公共区域132中,在该示例中,关于图2所述的晶体管tres、tsiv和tsel由两个像素电路100

‑

2和100

‑

3共享。

145.另外,由于像素电路100

‑

2和100

‑

3共享衬底102的相同第二部分,所以像素电路100

‑

2的两个区mem

i

和mem

i’可以与关联于像素电路100

‑

3的两个对应区mem

i

和mem

i’的区118

i

相同的区118

i

相关联。换言之,在此示例中,像素电路100

‑

2和100

‑

3共享相同的区1181,并且共享相同的区1182。作为示例,如图13中所示,像素电路100

‑

2的两个区mem

i

和mem

i’各自具有面对对应的区118

i

的相同第一侧而布置的端,并且像素电路100

‑

3的两个对应区mem

i

和mem

i’各自具有面对该区118

i

的相同第二侧而布置的一端,该第二侧与第一侧相对。

146.作为示例,上述三个像素电路100

‑

1、100

‑

2和100

‑

3的关联可以在像素电路100

‑

1、100

‑

2和100

‑

3彼此跟随的第一方向上重复。即在图13中竖直地例如形成一列像素电路100。该列像素电路例如在与第一方向正交的第二方向上重复以形成像素电路的矩阵。

147.当上述三个像素电路100

‑

1、100

‑

2和100

‑

3的关联也在第二方向上(在图13中水平地)重复时,像素电路100的每个区mem

i’然后优选地在宽度方向上由电极114的部分来横向界定,该电极114的部分也界定相邻像素电路100的对应区mem

i’。

148.关于图13所述的实施例可以获得像素电路100的特别紧凑的矩阵。

149.以上已描述了关于图4至图13在作为示例的像素电路100包括两个存储区mem

i

的情况中的像素电路100的实施例和变型实施例。本领域技术人员能够使该示例的描述适于仅包括一个区mem

i

或者相对地包括多于两个的区mem

i

的像素电路100的情况。作为示例,仅包括一个区mem

i

的像素电路100被用作全局快门图像传感器的像素电路。作为示例,类似于先前所描述的,包括三个区mem

i

的像素电路100可以在tof传感器中使用。

150.已描述了各种实施例和变型。本领域技术人员将理解,这些实施例的某些特征可以被组合,并且本领域技术人员将容易想到其他变型。具体地,像素电路100已在作为示例的意图被传输到区mem

i

的光生电荷是光生电子的情况中描述。本领域技术人员能够使本公开适于其中这些电荷是光生空穴的情况,具体是通过反转作为示例指示的所有导电类型并且通过适配控制和极化电势电平。

151.最后,基于在上文提供的功能描述,本文中所述的实施例和变型的实际实现在本领域技术人员的能力之内。具体地,例如使用由计算机实现的模拟工具,本领域技术人员能够选择施加到栅极gmem

i 130和120

i

的控制信号的高电平和低电平和/或施加到衬底102的(多个)极化电势电平和/或施加到电极114的极化电势的电平和/或所描述的各种层、区和盒的掺杂水平。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。