技术特征:

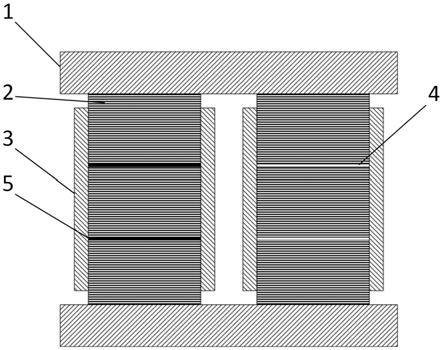

1.一种像素电路,包括:光转化区;绝缘的垂直电极;以及至少一个电荷存储区;其中所述光转化区属于半导体衬底的第一部分;以及其中每个电荷存储区属于所述半导体衬底的第二部分,所述第二部分通过所述绝缘的垂直电极与所述半导体衬底的所述第一部分物理分离。2.根据权利要求1所述的像素电路,其中所述绝缘的垂直电极从所述半导体衬底的第一面穿过所述半导体衬底,针对每个电荷存储区,所述像素电路还包括:第一掺杂区,与在所述第二部分中的所述电荷存储区接触;第二掺杂区,在所述第一部分中;栅极,放置在所述光转化区与所述第二掺杂区之间的所述半导体衬底的所述第一面上;以及电连接件,在所述第一掺杂区与所述第二掺杂区之间;其中所述绝缘的垂直电极被配置为针对每个电荷存储区,将包括所述光转化区和所述第二掺杂区的所述半导体衬底的所述第一部分与包括所述电荷存储区和所述第一掺杂区的所述半导体衬底的所述第二部分电绝缘并且光学绝缘。3.根据权利要求2所述的像素电路,其中针对每个电荷存储区,所述电连接件在所述半导体衬底的所述第一面上方被布置在所述半导体衬底外侧。4.根据权利要求2所述的像素电路,其中每个电荷存储区在宽度方向上通过彼此平行并且面对的所述绝缘的垂直电极的两个部分来横向界定,与所述电荷存储区接触的所述第一掺杂区被布置在所述电荷存储区沿长度方向上的一端处。5.根据权利要求2所述的像素电路,其中:所述半导体衬底被掺杂有第一导电类型;所述光转化区包括被掺杂有第二导电类型的层,所述第二导电类型的层在所述半导体衬底的所述第一面上被布置在所述半导体衬底中;针对每个电荷存储区,所述第一掺杂区和所述第二掺杂区在所述半导体衬底的所述第一面上被布置在所述半导体衬底中,并且所述第一掺杂区和所述第二掺杂区被掺杂有所述第二导电类型;以及每个电荷存储区包括被掺杂有所述第二导电类型的区域,所述区域在所述半导体衬底的所述第一面上被布置在所述半导体衬底中。6.根据权利要求5所述的像素电路,其中,针对每个电荷存储区,所述第一掺杂区和所述第二掺杂区具有相同的掺杂水平。7.根据权利要求5所述的像素电路,其中,针对每个电荷存储区,所述第一掺杂区和所述第二掺杂区具有与所述光转化区的层相同的掺杂水平。8.根据权利要求5所述的像素电路,其中,针对每个电荷存储区,所述电荷存储区的所述区域比所述第一掺杂区更重地掺杂。9.根据权利要求5所述的像素电路,其中,针对每个电荷存储区,所述栅极放置在从所述第二掺杂区向所述光转化区的层延伸的沟道区域上,所述沟道区域比所述光转化区的层

和所述第二掺杂区被更轻地掺杂有所述第二导电类型。10.根据权利要求9所述的像素电路,其中,针对每个电荷存储区,所述沟道区域包括第一部分和第二部分,所述第二部分比所述第一部分被更轻地掺杂,所述第二部分从所述光转化区的层向所述第一部分延伸,并且所述第一部分从所述第二部分向所述第二掺杂区延伸。11.根据权利要求9所述的像素电路,其中,针对每个电荷存储区,所述第二掺杂区通过所述沟道区域和所述半导体衬底的被掺杂有所述第一导电类型的区域与所述光转化区的层分离。12.根据权利要求2所述的像素电路,其中,针对每个电荷存储区,所述像素电路包括:掺杂读取区,在所述半导体衬底的具有所述电荷存储区的所述第二部分中、在所述第一面的侧上被布置在所述半导体衬底中;以及附加的栅极,放置在所述半导体衬底的在所述电荷存储区与所述读取区之间延伸的部分上,所述附加的栅极伸展到所述电荷存储区。13.根据权利要求1所述的像素电路,其中至少两个电荷存储区属于所述半导体衬底的相同第二部分。14.根据权利要求1所述的像素电路,包括电路,所述电路被配置为:向所述半导体衬底的所述第一部分施加第一极化电势;以及针对每个电荷存储区:在所述电荷存储区的每个读取阶段期间,向所述半导体衬底的所述第二部分施加所述第一极化电势;以及在所述电荷存储区的读取阶段之外,向所述半导体衬底的所述第二部分施加第二极化电势;其中所述第一极化电势和所述第二极化电势被配置,使得所述电荷存储区中的势阱在所述第二极化电势被施加时比所述第一极化电势被施加时更深。15.一种传感器,包括根据权利要求1的多个像素电路。16.根据权利要求15所述的传感器,其中两个相邻的像素电路共享所述半导体衬底的相同第二部分。17.根据权利要求15所述的传感器,其中两个相邻的像素电路共享所述半导体衬底的相同第一部分。18.根据权利要求15所述的传感器,还包括电路,所述电路被配置为:向所述半导体衬底的所述第一部分施加第一极化电势;以及针对每个电荷存储区:在所述电荷存储区的每个读取阶段期间,向包括所述存储区的所述半导体衬底的所述第二部分施加所述第一极化电势;以及在所述电荷存储区的读取阶段之外,向所述第二部分施加第二极化电势;其中所述第一极化电势和所述第二极化电势被配置,使得所述电荷存储区中的势阱在所述第二极化电势被施加到所述半导体衬底的所述第二部分时比所述第一极化电势被施加到所述半导体衬底的所述第二部分时更深。19.一种用于根据权利要求1所述的像素电路的控制方法,包括:

利用第一极化电势使所述半导体衬底的所述第一部分极化;以及针对每个电荷存储区:在所述电荷存储区的每个读取阶段期间,利用所述第一极化电势使所述半导体衬底的所述第二部分极化;以及在所述电荷存储区的读取阶段之外,利用第二极化电势使所述第二部分极化;其中所述第一极化电势和所述第二极化电势被配置,使得所述电荷存储区中的势阱在所述第二极化电势被施加到所述半导体衬底的所述第二部分时比所述第一极化电势被施加到所述半导体衬底的所述第二部分时更深。20.一种像素电路,包括:半导体衬底;光转化区,在半导体衬底的第一部分中;电荷存储区,在所述半导体衬底的第二部分中;绝缘的垂直电极,完全延伸穿过所述半导体衬底,并且被定位以使所述电荷存储区与所述光转化区电绝缘并且光学绝缘。21.根据权利要求20所述的像素电路,还包括:第一掺杂区,在所述半导体衬底的所述第二部分中,与所述电荷存储区接触;第二掺杂区,在所述半导体衬底的所述第一部分中;栅极结构,在所述半导体衬底之上,并且被定位在所述光转化区与所述第二掺杂区之间;以及电连接件,在所述第一掺杂区与所述第二掺杂区之间。22.根据权利要求21所述的像素电路,其中所述电连接件被布置在所述半导体衬底上方,并且在所述绝缘的垂直电极之上延伸。23.根据权利要求21所述的像素电路,其中所述绝缘的垂直电极的彼此平行延伸并且面对的两个部分在宽度上界定所述电荷存储区,以及其中所述绝缘的垂直电极的彼此平行延伸并且面对的两个其他部分在长度上界定所述电荷存储区。24.根据权利要求21所述的像素电路,还包括:掺杂读取区,在所述半导体衬底的所述第二部分中;以及附加的栅极结构,放置在所述半导体衬底的所述第二部分的一部分上,所述第二部分在在所述半导体衬底之上延伸,并且被定位在所述电荷存储区和所述掺杂读取区之间。25.根据权利要求21所述的像素电路,其中:所述半导体衬底被掺杂有第一导电类型;所述光转化区包括被掺杂有第二导电类型的层;以及所述电荷存储区被掺杂有所述第二导电类型。26.根据权利要求25所述的像素电路,其中所述第二掺杂区通过所述栅极结构在其之上延伸的沟道区域与所述光转化区的层分离。27.根据权利要求26所述的像素电路,其中所述沟道区域包括:第一掺杂部分,与所述第二掺杂区接触;以及第二掺杂部分,与所述光转化区接触。28.根据权利要求20所述的像素电路,还包括电路,所述电路被配置为:

向所述半导体衬底的所述第一部分施加第一极化电势;在所述电荷存储区的每个读取阶段期间,向所述半导体衬底的所述第二部分施加所述第一极化电势;以及在所述电荷存储区的读取阶段之外,向所述半导体衬底的所述第二部分施加不同于所述第一极化电势的第二极化电势。

技术总结

本公开的实施例涉及包括电荷存储区的像素电路。像素电路包括光转化区、绝缘的垂直电极以及至少一个电荷存储区。光转化区属于半导体衬底的第一部分,并且每个电荷存储区属于衬底的第二部分,该第二部分通过绝缘的垂直电极与衬底的第一部分物理分离。与衬底的第一部分物理分离。与衬底的第一部分物理分离。

技术研发人员:B

受保护的技术使用者:意法半导体(克洛尔2)公司

技术研发日:2021.04.29

技术公布日:2021/11/2

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。