1.本发明涉及机内自检测技术领域,一种精益的机内自检电路。

背景技术:

2.机内自检测(bit)是机载设备设计中常见的状态与故障监测方式,是机载设备能够准确地确定其状态(可工作、不可工作或性能下降),并隔离其内部故障的一种设计。其设计的核心是解决故障检测和隔离的问题。在机载设备设计中常用的机内自检测方法包括上电自检、周期自检和触发自检。无论采用哪种机内自检测方法,目前常用的bit电路设计均存在如下缺点。

3.在工程运用中,为了保证自检测的故障检测率、隔离率、虚警率指标,通常会使用多路检测通道对设备电路进行监测。bit电路需要采用激励信号发生电路为各路监测通道提供激励信号。由于各路监检测通道的监测需求不一,因此需要分别设计多种可以产生不同电气特性离散量、模拟量的激励电路,bit 自检电路也因此较为复杂。鉴于bit电路的重要性,一般设计要求bit电路的可靠性指标比被监测电路的可靠性指标高1个数量级。bit自检电路自身复杂度较高,导致其可靠性指标较难满足设计要求。

4.飞机部分关键系统的设备体积较小,电路功能较复杂,在单位体积内聚集了大量不同类型的模拟或数字电路,强电与弱电信号混合,电磁环境条件较为恶劣。bit电路由于与被监测电路存在物理上的硬连接,因此在工程实践中, bit电路常常受电磁干扰,误报设备故障,虚警率较高。bit电路误报故障可能会影响飞行员对飞机状态的判读,导致飞行员采取错误的措施,影响飞机的安全。同时,bit电路误报故障也会使飞机频繁进行不必要的停飞检修,影响签派率。

5.目前的bit电路设计中,关注点在于测试被检电路的功能在理想工作环境下是否完好。为了测试被检电路而由bit电路产生的激励信号通常是一个具有标准电气特性的信号。然而设备在实际工作中,接收与发送的各种信号由于受各类外部因素影响,信号的幅值、频率、波形往往发生偏移或畸变,与理想信号的标准电气特性不一致。所以使用传统bit电路产生的具有标准电气特性的激励信号对机内电路进行测试,常常出现:机内自检测报告被测电路正常,但被测电路却因为不能识别处在电气特性临界值附近的信号而无法正常工作的现象。

6.目前常规bit电路存在以上缺点,从而在一些对bit电路可靠性要求特别严格的应用场合,比如:飞机前轮转弯、刹车、后襟系统等,无法满足这类系统的需求,一种精益的,高可靠性的bit电路设计方法亟待被实现。

技术实现要素:

7.发明目的

8.本发明针对现有技术存在的不足,提供一种精益的机内自检电路,可以有效减少bit电路复杂度,提高bit电路抗干扰能力与余度检测能力。

9.发明技术解决方案

10.为了实现上述发明目的,本发明采用下述的技术方案:

11.一种精益的机内自检电路,包括中央处理模块、数字/模拟转换模块、通道切换模块、选通模块、叠加电路模块,中央处理模块通过数字总线控制数字/ 模拟转换模块输出要求的模拟激励信号,并通过地址总线控制通道切换模块将模拟激励信号输出至对应的输出通道,中央处理模块经过一定延时待通道切换模块输出通道信号稳定后,对选通模块输出使能信号,将模拟激励信号通过叠加电路模块传递至待测试电路,中央处理模块通过对输出的激励信号及待测试电路反馈的测量值进行对比,以判定待测电路的工作状态。

12.优选的,中央处理模块能够采用循环工作的方式控制数字/模拟转换模块输出不同的模拟激励信号,并控制通道切换模块、选通模块将模拟激励信号依次输出至各个待测试电路,以完成对各个待测电路工作状态进行检测。

13.优选的,选通模块采用能够通过离散量信号进行电气导通和关闭的电子器件。

14.优选的,选通模块采用电子继电器。

15.优选的,模拟激励信号通过加法器耦合至待测试电路,不需要对待测试电路做切换。

16.优选的,该机内自检电路在非自检状态时,不与被测电路形成任何关联。

17.本发明的优点

18.本发明的优点在于:

19.(1)简化检测电路复杂度:采用d/a数模转换器与模拟切换开关配合的方式,分时为各检测电路提供激励,优点在于d/a数模转换器可输出任何形式的信号,为各种离散量、模拟量的输入信号提供模拟激励,避免根据不同电路需求设计不同自检激励电路,同时通过软件调度分时为各电路提供激励,仅需采用1片d/a数模转换器,有效降低了bit自检电路的复杂度。

20.(2)提高bit自检电路的抗干扰能力:本发明采用继电器与加法器组合向被测电路耦合激励信号,非自检状态时,继电器触点断开,bit自检电路处于悬空状态,故bit自检电路与被测电路不形成任何关联;bit自检激励信号经继电器切换后作为加法器的1个输入信号耦合至被测电路,不需要对被测电路做切换等动作,避免了由于被测电路切换瞬间产生的强电磁辐射,有效提高bit自检电路抗干扰能力。

21.(3)增强bit自检电路的余度检测:传统的离散量检测,通过模拟开关信号实现,激励信号为固定值,无法检测被测电路的检测边界值。本发明采用d/a数模转换器可对激励信号幅值、频率、波形等参数进行模拟,能更全面的检测出被测电路的性能。

附图说明

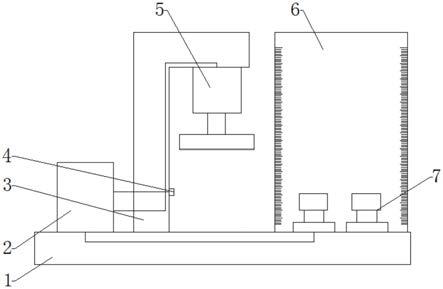

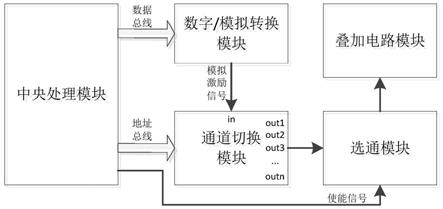

22.图1是本发明的一种精益的机内自检电路的设计框图。

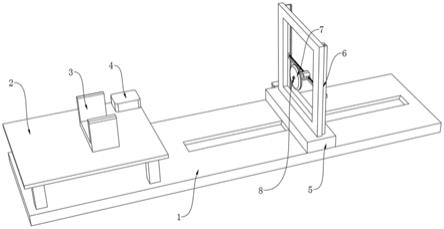

23.图2是本发明中央处理模块电路原理图。

24.图3是本发明数字/模拟转换模块电路原理图。

25.图4是本发明通道切换模块电路原理图。

26.图5是本发明选通模块电路原理图。

27.图6是本发明地/开信号检测电路叠加电路模块原理图。

28.图7是本发明模拟信号检测电路叠加电路模块原理图。

具体实施方式

29.结合附图对本发明的技术方案进行进一步描述。

30.一种精益的机内自检电路,参阅图1,包括:中央处理模块、数字/模拟转换模块、通道切换模块、选通模块、叠加电路模块,中央处理模块通过数字总线控制数字/模拟转换模块输出要求的模拟激励信号,并通过地址总线控制通道切换模块将模拟激励信号输出至对应的输出通道,中央处理模块经过一定延时待通道切换模块输出通道信号稳定后,对选通模块(选通模块指可以通过离散量信号进行电气导通和关闭电子器件,其具体器件类型可以为但不限于电子继电器)输出使能信号,将模拟激励信号通过叠加电路模块传递至待测试电路,中央处理模块通过对输出的激励信号及待测试电路反馈的测量值进行对比,以判定待测电路的工作状态。按上述控制方式,中央处理模块可以采用循环工作的方式,控制数字/模拟转换模块输出不同的模拟激励信号,并控制通道切换模块、选通模块将模拟激励信号依次输出至各个待测试电路,以完成对各个待测电路工作状态进行检测。

31.实施例一

32.参阅图2。该电路由中央处理芯片smj320f2812和dsp晶振及电阻、电容组成,用于完成图1的中央处理模块功能。smj320f2812的数字总线 d0_da~d11_da和da芯片使能线da_csa2,da_csb2,da2_wr与数字/ 模拟转换模块连接。smj320f2812通过向数字/模拟转换模块写入数字信号,使数字/模拟转换模块产生指定电压、频率的模拟电压信号;smj320f2812向通道切换模块和选通模块发送通道地址信号和选通使能信号,将指定的bit激励信号输出至叠加模块。

33.参阅图3。该电路由da芯片dac7547和四运算放大器芯片op400ay及电阻、电容组成,用于完成图1的数字/模拟转换模块功能。dac7547为电流型数字/模拟转换芯片,可以根据图2中央处理芯片的命令产生指定电流值的电流。该电流首先经op400ay的一个运放电路组成的电流/电压电路转换为bit 激励信号(电压信号);bit激励信号再经op400ay的另一个运放电路组成的放大电路进行电压放大、反向后输出到通道切换模块。

34.参阅图4。该电路由多路芯片hi1-548及电阻、电容组成,用于完成图1 的通道切换模块功能。数字/模拟转换模块产生的bit激励信号发送到hi1-548 的输入通道in1~in8,通过hi1-548的输出通道out输出。中央处理模块向 hi1-548的en,a0,a1,a2,a3端发送控制信号与地址信号,使hi1-548的 bit激励信号输入通道in1~in8中被选中的一路通道与out输出通道连通,将多路bit激励信号中的一路通过out输出通道输出到选通模块。

35.参阅图5。该电路由电子继电器芯片hi1-303及电阻组成,用于完成图1 的选通模块功能。通道切换模块将被选中的bit激励信号输出到hi1-303的输入通道s,通过hi1-303的输出通道d输出。中央处理模块向hi1-303的in端发送控制能信号,使hi1-303的bit激励信号输入通道s与输出通道d连通或断开,使bit激励信号接入叠加电路模块或与叠加电路模块断开。

36.参阅图6。该电路由电压比较器lm139及电阻、电容组成,用于完成图1 的叠加电路模块功能,实现地/开信号与待测电路叠加。来自刹车选择开关的地 /开信号经 15v电压上拉,通过1个限流电阻与1个隔离二极管1n3595后接入电压比较器lm139的正输入端。来自da

芯片的bit激励信号通过1个多路开关后,经同一个隔离二极管1n3595同样接入电压比较器lm139的正输入端。 bit激励信号电压值由da芯片输出电压值决定。lm139的负输入端与 6v参考电压连接;lm139的输出端为漏极开路,使用5v电源进行了上拉。地/开信号检测电路正常工作,未进行bit时,bit激励信号为悬空状态,lm139的正输入端电压等于刹车选择开关信号电压。地/开信号检测电路进行bit时, lm139的正输入端电压等于bit激励信号电压值。lm139的正输入端电压大于负输入端的 6v参考电压,lm139输出端输出 5v电压;lm139的正输入端电压小于负输入端的 6v参考电压,lm139输出端输出0v电压。通过lm139 输出电压的变化,可以监测地/开信号检测电路工作是否正常。

37.实施例二

38.参阅图2。该电路由中央处理芯片smj320f2812和dsp晶振及电阻、电容组成,用于完成图1的中央处理模块功能。smj320f2812的数字总线 d0_da~d11_da和da芯片使能线da_csa2,da_csb2,da2_wr与数字/ 模拟转换模块连接。smj320f2812通过向数字/模拟转换模块写入数字信号,使数字/模拟转换模块产生指定电压、频率的模拟电压信号;smj320f2812向通道切换模块和选通模块发送通道地址信号和选通使能信号,将指定的bit激励信号输出至叠加模块。

39.参阅图3。该电路由da芯片dac7547和四运算放大器芯片op400ay及电阻、电容组成,用于完成图1的数字/模拟转换模块功能。dac7547为电流型数字/模拟转换芯片,可以根据图2中央处理芯片的命令产生指定电流值的电流。该电流首先经op400ay的一个运放电路组成的电流/电压电路转换为bit激励信号(电压信号);bit激励信号再经op400ay的另一个运放电路组成的放大电路进行电压放大、反向后输出到通道切换模块。

40.参阅图4。该电路由多路芯片hi1-548及电阻、电容组成,用于完成图1的通道切换模块功能。数字/模拟转换模块产生的bit激励信号发送到hi1-548的输入通道in1~in8,通过hi1-548的输出通道out输出。中央处理模块向 hi1-548的en,a0,a1,a2,a3端发送控制信号与地址信号,使hi1-548的 bit激励信号输入通道in1~in8中被选中的一路通道与out输出通道连通,将多路bit激励信号中的一路通过out输出通道输出到选通模块。

41.参阅图5。该电路由电子继电器芯片hi1-303及电阻组成,用于完成图1 的选通模块功能。通道切换模块将被选中的bit激励信号输出到hi1-303的输入通道s,通过hi1-303的输出通道d输出。中央处理模块向hi1-303的in端发送控制能信号,使hi1-303的bit激励信号输入通道s与输出通道d连通或断开,使bit激励信号接入叠加电路模块或与叠加电路模块断开。

42.参阅图7。该电路由运算放大器op400ay及电阻、电容组成,用于完成图1的叠加电路模块功能,实现模拟信号与待测电路叠加。前舱右刹车指令模拟信号及来自da芯片的bit激励信号分别通过1个精密电阻,在运算放大器op400ay的正输入端汇聚。此时,op400ay的正输入端电压等于前舱右刹车指令模拟信号电压与bit激励信号电压的叠加。op400ay的负输入端通过电阻与地连接,因此op400ay的输出端电压等于正输入端电压。模拟信号检测电路正常工作,未进行bit时,bit激励信号通过模拟开关与地连接,op400ay 的输出端电压等于前舱右刹车指令模拟信号电压。模拟信号检测电路进行bit 时,op400ay的输出端电压等于前舱右刹车指令模拟信号电压加上bit激励信号电压之和。通过比较op400ay的输出端电压值的增量是否等于bit激励信号电压值,可以监测模拟信号检测电路工作是否正常。同

时,该电路具有开路检测功能。当前舱右刹车指令模拟信号开路时,解调电路的输出电压变为bit 激励信号的2倍,因此可以实现故障定位。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。