1.本发明是有关于一种电容串结构、存储器装置及电子装置,且特别是有关于一种在存储器装置的字线形成的电容串结构,以及基于电容结构所建构的电子装置。

背景技术:

2.在存储器技术领域中,在存储器装置中设置电荷泵电路是一个必要的选择。电荷泵电路可以用来提升字线上字线电压,以启动存储单元的编程动作。

3.基于电荷泵电路需要设置相应的多个电容。而电容在集成电路的布局中,又需耗费大量的布局面积。因此,要如何节省集成电路内的电容的布局面积,为本领域技术人员的重要课题。

技术实现要素:

4.本发明提供一种电容串结构,利用存储器装置中多条字线来形成,可减小电路布局所需的面积。

5.本发明提供一种存储器装置及电子装置,配合上述的电容串结构,可减小电路布局所需的面积。

6.本发明的电容串结构包括多个导电板。导电板设置在存储器装置中。导电板相互堆叠,分别形成存储器装置中的多条字线,其中导电板中相邻的二者间形成电容。

7.本发明的电子装置包括核心电路以及多个第一电容。核心电路耦接至第一电容。第一电容形成一电容串结构。电容串结构由多个导电板形成。导电板设置在存储器装置中。导电板相互堆叠,分别形成存储器装置中的多条字线,其中导电板中相邻的二者间形成各第一电容。

8.本发明的存储器装置包括多条字线以及电荷泵电路。各字线耦接至多个存储单元。字线分别由多个导电板所形成,导电板形成电容串结构。电荷泵电路耦接至电容串结构,根据多个时钟脉冲信号以针对该电容结构中的多个第一电容进行电荷泵操作以产生输出电压。

9.基于上述,本发明的电容串结构通过存储器装置中的相互堆叠的多条字线来形成。本发明的电容串结构可提供存储器装置以及电子装置来进行电荷存储以及转移的媒介。基于电容串结构是通过存储器装置中的相互堆叠的多条字线来形成,电容串结构不需占去额外的电路布局面积,有效降低电路成本。

附图说明

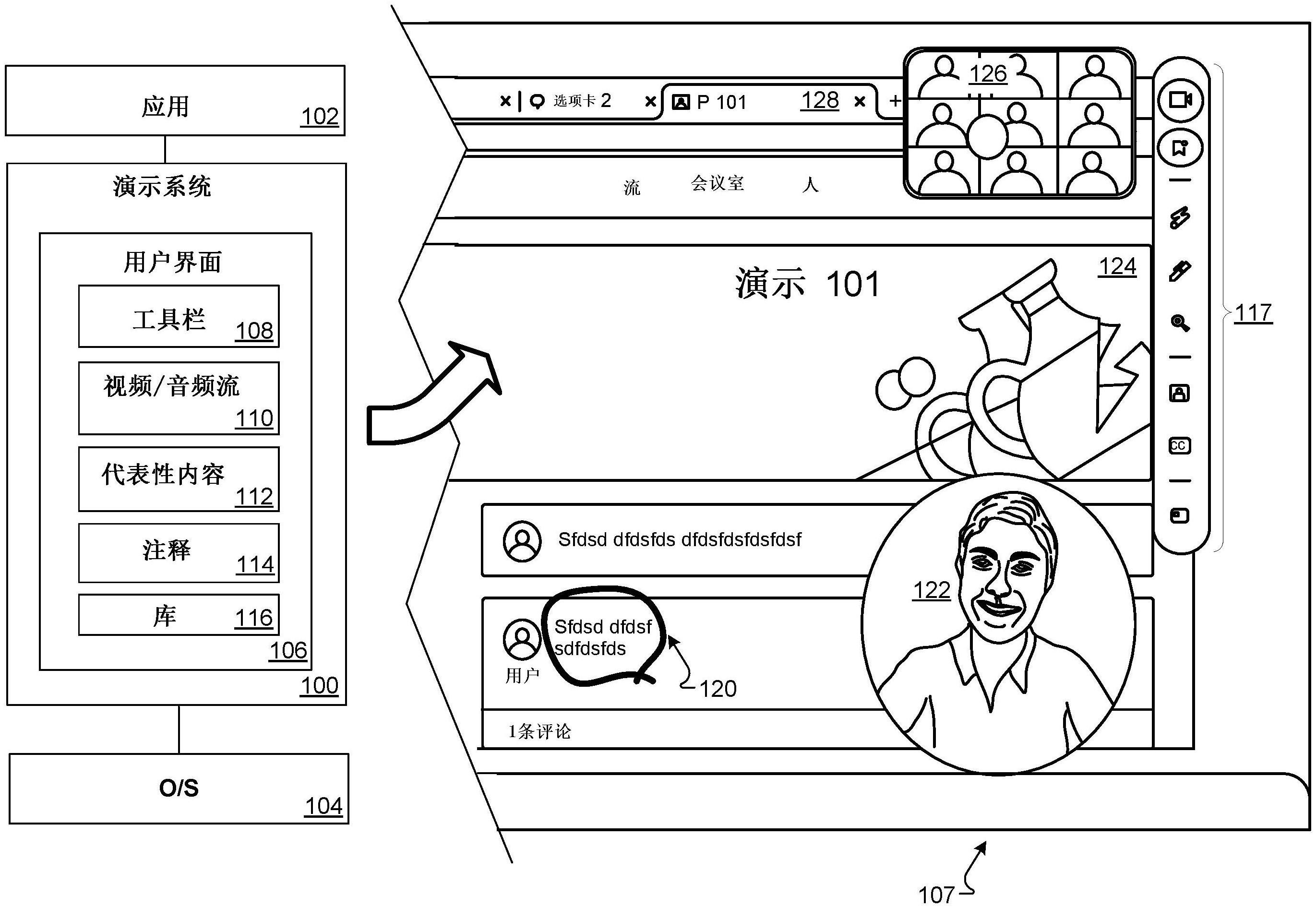

10.图1绘示本发明一实施例的电容串结构的示意图。

11.图2绘示本发明一实施例的电容串结构的示意图。

12.图3a至图3c分别绘示本发明实施例的电容串结构的不同实施方式的示意图。

13.图4绘示本发明一实施例的电子装置的示意图。

14.图5a至5e绘示本发明实施例的多个电子装置的示意图。

15.图6绘示本发明一实施例的存储器装置的示意图。

16.附图标记说明

17.100、600:存储器装置

18.200、310、320、420、520:电容串结构

19.331:等效电路

20.400:电荷泵电路

21.411~415、511~515:单元电路

22.500、501、502、503、504:电子装置

23.5011、5021、5031、5041:核心电路

24.52111:参考电压产生器

25.610:存储单元阵列

26.621~622:x驱动器

27.631~632:电荷泵电路

28.640:电容串结构

29.650:页缓冲器

30.660:周边电路

31.buf1、buf2:缓冲器

32.c1~c19、cg1~cg5、cout、cd、c51~c54:电容

33.c31~c34:等效电容

34.clk:时钟脉冲信号

35.gsl:共同源极线

36.isp1~isp4:介电层

37.iv1~iv4:反向器

38.n1~n5、m1~m5:端点

39.np1~np5:裸露部

40.p1~p4:时钟脉冲信号

41.pp1~pp10:突出部

42.r51、r52、r53:电阻

43.ssl:存储串选择线

44.t1~t10、ti1~ti8、m51~m55、mp1、mb1~mb5:晶体管

45.vcc、vb:基准电压

46.vout:输出电压

47.vss:参考接地端

48.wl、wl1~wln、wl(n)~wl(n 7):字线

49.wl1~wl8:字线

50.wlp1~wlp5:导电板

51.wr1~wr8:传输导线

具体实施方式

52.请参照图1,图1绘示本发明一实施例的电容串结构的示意图。电容串结构中包括串联耦接的电容c1~c8。电容c1~c8由多个形成存储器装置100的字线wl1~wl8的导电板所形成。其中,在本实施例中,形成字线wl1~wl8的导电板依序堆叠。相邻的字线wl1以及wl2的二导电板形成电容c1;相邻的字线wl2以及wl3的二导电板形成电容c2;

…

;相邻的字线wl7以及wl8的二导电板形成电容c8。

53.本实施例中,存储器装置100可以为非易失式存储器(例如快闪存储器)或易失式存储器,没有一定的限制。

54.在本实施例中,存储器装置100为三维架构的存储器装置。存储器装置100中具有形成存储串选择线ssl以及共同源极线gsl的导电板。形成字线wl1~wl8的导电板依序设置在存储串选择线ssl以及共同源极线gsl的二导电板间。值得一提的,本发明实施例通过利用存储器装置100中形成字线wl1~wl8的导电板来形成包括电容c1~c8的电容串结构,可在不需要额外的布局面积下,产生电路中所需要的电容。

55.值得一提的,在存储器装置100中,形成字线wl1~wl8的导电板可以为具有孔串(string holes)的导电板或不具有孔串的导电板。本发明实施例中,用以形成字线wl1~wl8的导电板可以为不具有孔串的导电板,或也可以为具有孔串的导电板,没有固定的限制。

56.以下请参照图2,图2绘示本发明一实施例的电容串结构的示意图。电容串结构200由多个形成字线wl1~wl20的导电板所形成。其中字线wl1~wl20中,相邻的二的导电板分别形成电容c1~c19。在本实施例中,形成字线wl1、wl3以及wl5的第一导电板可通过传输导线wr1相互耦接至端点n1,形成字线wl2以及wl4的第二导电板则可通过传输导线wr2相互耦接至端点m1。如此一来,电容c1~c4可并联耦接在端点n1以及m1间。

57.另外,形成字线wl6、wl8以及wl10的第一导电板可通过传输导线wr3相互耦接至端点n3;形成字线wl7以及wl9的第二导电板则可通过传输导线wr4相互耦接至端点m3;形成字线wl11、wl13以及wl15的第一导电板可通过传输导线wr5相互耦接至端点n2;形成字线wl12以及wl14的第二导电板则可通过传输导线wr6相互耦接至端点m2;形成字线wl16、wl18以及wl20的第一导电板可通过传输导线wr7相互耦接至端点n4;形成字线wl17以及wl19的第二导电板则可通过传输导线wr8相互耦接至端点m4。上述的多个第一导电板彼此不直接相邻,多个第二导电板彼此也不直接相邻。

58.通过上述的耦接关系,可以使电容c6~c10并连耦接在端点m3以及n3间,使电容c11~c14并连耦接在端点m2以及n2间,以及使电容c15~c19并连耦接在端点m4以及n4间。而上述的端点m1、n1间的电容、端点m3、n3间的电容、端点m2、n2间的电容以及端点m4、n4间的电容则依序串联耦接。

59.附带一提的,本实施例中的字线wl1~wl20的数量仅只是说明用的范例,不用以限制本发明的范畴。本领域普通技术人员可根据存储器装置中所具有的实际的字线的个数来产生不同数量的电容,没有特定的限制。

60.此外,本实施例中,任二端点间并联的电容的数量是可以根据设计上的需求来进行调整的,并不限于本实施例中的四个。而通过调整二端点间并联的电容的数量,可以调整二端点间所提供的等效电容的大小。

61.以下请参照图3a至图3c,图3a至图3c分别绘示本发明实施例的电容串结构的不同实施方式的示意图。在图3a中,电容串结构310包括多个形成存储器装置的字线的导电板wlp1~wlp5以及多个介电层isp1~isp4。导电板wlp1~wlp5分别与介电层isp1~ip4交错设置。其中,导电板wlp1、wlp2间、导电板wlp2、wlp3间、wlp3、wlp4间以及导电板wlp4、wlp5间可分形成电容。在本实施例中,导电板wlp1~wlp5相互堆叠成阶梯状,且导电板wlp1~wlp5分别具有裸露部np1~np5。

62.此外,电容串结构310并包括传输导线wr1以及wr2。传输导线wr1耦接至导电板wlp1、wlp3以及wlp5所分别具有的裸露部np1、np3以及np5上。传输导线wr1并可耦接至端点m1。传输导线wr2则耦接至导电板wlp2以及wlp4所分别具有的裸露部np2以及np4上。传输导线wr2并可耦接至端点n1。通过传输导线wr1以及wr2,导电板wlp1~wlp5间所形成的电容可并联耦接在端点m1以及n1间。

63.在图3b中,电容串结构320包括导电板wlp1~wlp8。导电板wlp1~wlp8分别用以形成存储器装置中的字线wl(n)~wl(n 7)。导电板wlp1~wlp8相互交叠配置,相邻的二导电板wlp1~wlp8间并分别形成多个电容。导电板wlp1、wlp3、wlp5以及wlp7分别具有相互重叠的突出部pp1、pp3、pp5以及pp7,导电板wlp2、wlp4、wlp6以及wlp8则分别具有相互重叠的突出部pp2、pp4、pp6以及pp8。各个突出部pp1、pp3、pp5以及pp7与各个突出部pp2、pp4、pp6以及pp8则不相重叠。电容串结构320并包括传输导线wr1以及wr2。其中传输导线wr1耦接至突出部pp1、pp3、pp5以及pp7,而传输导线wr2则耦接至突出部pp2、pp4、pp6以及pp8。导电板wlp1~wlp8监所形成的多个电容可相互并联耦接。

64.在图3c中,电容串结构330包括形成存储器装置的字线的多个导电板wlp1~wlp5。导电板wlp1~wlp5可以阶梯状相互堆叠。在本实施方式中,传输导线wr1耦接至导电板wlp1以及导电板wlp5,且不直接连接至导电板wlp2以及wlp4(第三导电板),且传输导线wr2则耦接至导电板wlp3,以形成等效电路331。其中,传输导线wr1另耦接至端点n1,传输导线wr2则另耦接至端点m1。

65.在等效电路331中,导电板wlp1、wlp2间形成的等效电容c31与导电板wlp2、wlp3间形成的等效电容c32相互串联耦接在端点n1以及m1间。导电板wlp3、wlp4间形成的等效电容c33与导电板wlp4、wlp5间形成的等效电容c34相互串联耦接在端点m1以及n1间。

66.通过图3c实施方式的耦接组态,端点n1以及m1间可具有相对多的电容相互串接。因此,可提升端点n1以及m1间的耐电压能力。

67.当然,图3c中使二端点n1以及m1间具有两个相互串连的电容的实施方式只是一个说明用的范例。设计者也可使二端点n1以及m1间具有三个或三个以上相互串连的电容。其中,二端点n1以及m1具有串接电容的数量,可以由设计者自行决定,没有特别的限制。

68.以下请参照图4,图4绘示本发明一实施例的电子装置的示意图。电子装置可以是电荷泵电路400。电荷泵电路400包括具有多个单元电路411~415的核心电路以及电容串结构420,其中电容串结构420系由多个字线wl的导电板间的电容所组成。单元电路411~415依序串联耦接,其中第一级的单元电路411接收基准电压vcc。单元电路411~415的输出端分别耦接至端点m1~m5。端点m5可以为电荷泵电路400的输出端并产生输出电压vout。单元电路411~414的输出端并分别耦接至次一级的单元电路412~415的输入端。

69.电容串结构420中,多个电容的另一端点n1、n3用以接收时钟脉冲信号p2;端点n2、

n4用以接收时钟脉冲信号p3;端点n5则耦接至参考接地端vss。时钟脉冲信号p3与时钟脉冲信号p2可具有不同的相位。时钟脉冲信号p3与时钟脉冲信号p2交错的使对应联接的电容的端点n1~n4,交错的在不相同的第一电压与第二电压间进行切换。

70.对应于电容串结构420中的多个电容的电压交错切换动作,单元电路411~415可进行电荷转移动作。电荷泵电路400可基于基准电压vcc,通过电压泵升动作,来产生数倍于基准电压vcc的输出电压vout。

71.值得一提的,在本实施例中,单元电路411~415可应用本领域普通技术人员熟知的多级形式的电荷泵电路中的电荷泵单元电路来实施,没有固定的限制。

72.关于电容串结构420的实施细节,在前述的多个实施例以及实施方式中已有详细的说明,在此恕不多赘述。

73.以下请参照图5a,图5a绘示本发明另一实施例的电子装置的示意图。电子装置可以为电荷泵电路500。电荷泵电路500包括具有多个单元电路511~515以及多个反向器iv1~iv4的核心电路,以及电容串结构520,其中电容串结构520系由多个字线wl的导电板间的电容所组成。在本实施例中,单元电路511包括晶体管t1、t2以及电容cg1;单元电路512包括晶体管t3、t4以及电容cg2;单元电路513包括晶体管t5、t6以及电容cg3;单元电路511包括晶体管t7、t8以及电容cg4;单元电路514包括晶体管t9、t10以及电容cg5。其中,第一级的单元电路511中,晶体管t1的第一端接收基准电压vcc,晶体管t1的控制端耦接至单元电路511的输出端并耦接至端点m1。晶体管t1的第二端耦接至晶体管t2的控制端。晶体管t2的第一端耦接至晶体管t1的第一端,晶体管t2的第二端则耦接至晶体管t1的控制端。此外,电容cg1的一端接收时钟脉冲信号p4,电容cg1的另一端耦接至晶体管t2的控制端。在第二级至最后一级的单元电路512~515中,其中的晶体管t3、t5、t7以及t9的第一端是耦接至前级单元电路511~514的输出端,而最后一级的单元电路515的输出端则用以产生输出电压vout。在第二级至最后一级的单元电路512~515中,电容cg2、cg4接收时钟脉冲信号p1,电容cg3、cg5则接收时钟脉冲信号p4。

74.此外,反向器iv1由晶体管ti1、ti2串接而成;反向器iv2由晶体管ti3、ti4串接而成;反向器iv3由晶体管ti5、ti6串接而成;以及,反向器iv4由晶体管t17、ti8串接而成。反向器iv1接收时钟脉冲信号p2并提供时钟脉冲信号p2的反向信号至端点n1;反向器iv2接收时钟脉冲信号p3并提供时钟脉冲信号p3的反向信号至端点n2;反向器iv3接收时钟脉冲信号p2并提供时钟脉冲信号p2的反向信号至端点n3;反向器iv4接收时钟脉冲信号p3并提供时钟脉冲信号p3的反向信号至端点n4。其中,时钟脉冲信号p1~p4分别具有不同的相位。

75.在本实施例中,晶体管t1~t10以及晶体管ti2、ti4、ti6、ti8可以均为n型晶体管。晶体管ti1、ti3、ti5、ti7可以为p型晶体管。

76.在图5b中,电子装置可以为双相位电荷泵电路501。双相位电荷泵电路501包括核心电路5011以及电容cout,其中电容cout为由存储器中的多个形成字线的导电板所形成的电容串结构。电容cout耦接至核心电路5011的输出端。电容cout的细节可参见图5a实施例的电容串结构520。核心电路5011包括相互串联的晶体管m51~m55。各晶体管m51~m55耦接成二极体的组态。晶体管m51接收基准电压vb,晶体管m52、m54通过电容c51、c53接收时钟脉冲信号clk,晶体管m53、m55通过电容c52、c54接收反向时钟脉冲信号。核心电路5011泵升基准电压vb以核心电路5011的输出端产生输出电压vout。

77.图5c中,电子装置可以为电压调整器502。电压调整器502包括核心电路5021以及电容cout,其中电容cout为由存储器中的多个形成字线的导电板所形成的电容串结构。电容cout耦接至核心电路5021的输出端。电容cout的细节可参见图5a实施例的电容串结构520。核心电路5021包括参考电压产生器50211、放大器op1、功率晶体管mp5以及电阻r51、r52。参考电压产生器50211可以是能带隙电压产生器,并用以提供参考电压至放大器op1。电阻r51、r52用以分压输出电压vout以产生回授电压至放大器op1。电压调整器502是低压降电压调整器。

78.图5d中,电子装置可以为时间延迟器503。时间延迟器503包括核心电路5031以及电容cd,其中电容cd为由存储器中的多个形成字线的导电板所形成的电容串结构。电容cd的细节可参见图5a实施例的电容串结构520。核心电路5031包括缓冲器buf1、buf2以及电阻r53。缓冲器buf1、buf2相互串联耦接,用以接收输入信号in,并通过延迟输入信号in以产生输出信号out。电阻r53耦接在缓冲器buf1、buf2间,电容cd则耦接在电阻r53与接地端间。时间延迟器503的时间延迟可由电阻r53以及电容cd来决定。

79.图5e中,电子装置可以为电压升压器504。电压升压器504包括核心电路5041以及电容cout,其中电容cout为由存储器中的多个形成字线的导电板所形成的电容串结构。电容cout耦接至核心电路5041的输出端。电容cout的细节可参见图5a实施例的电容串结构520。核心电路5041包括晶体管mb1~mb5以及电容cb1。晶体管mb1及mb2形成一反相器以接收时钟脉冲信号clk并产生反相时钟脉冲信号。晶体管mb3~mb5形成多个开关,并用以通过升压基准电压vcc以产生输出电压vout。

80.在此请注意,由存储器中的多个形成字线的导电板所形成的电容串结构也可应用在其他任意的电路架构中。图5a至图5e的实施例仅只是说明用的范例,不用以限制本发明的范畴。

81.以下请参照图6,图6绘示本发明一实施例的存储器装置的示意图。存储器装置600为三维结构的存储器装置。存储器装置600包括存储单元阵列610、x驱动器621~622、电荷泵电路631~632、电容串结构640、页缓冲器650以及周边电路660。存储单元阵列610可以具有三维方式堆叠排列的多个存储单元。x驱动器621则可设置在存储单元阵列610的侧边。

82.此外,基于存储单元阵列610中的字线wl1~wln的布局方向,电容串结构640可以形成在存储单元阵列610的另一侧边上。相对应电容串结构640的位置,全部的或部分的电荷泵电路631的元件可以被设置在相邻于电容串结构640的位置,并电容串结构640相耦接。在一些实施例中,电荷泵电路631也可设置在存储单元阵列610的下方。

83.在本实施例中,x驱动器621~622可以堆叠的方式,多层次的被堆叠在存储器装置600中。相对应的,电荷泵电路631~632也可多层次的被堆叠在存储器装置600中,并分别设置在x驱动器621~622的侧边。如此一来,电荷泵电路631~632可以不需要被设置在周边电路660的布局范围中,有效减低布局面积的需求。

84.附带一提的,本实施例中的页缓冲器650以及周边电路660可布局在存储器装置600的底部,并为存储单元阵列610所覆盖。此外,本实施例中的x驱动器621~622、页缓冲器650以及周边电路660皆可应用本领域普通技术人员所熟知的电路架构来实施,没有固定的限制。

85.关于电荷泵电路631以及电容串结构640的实施细节,在前述的实施例以及实施方

式中已有详细的说明,在此恕不多赘述。

86.综上所述,本发明利用存储器装置中形成的字线导电板来形成电容串结构。在不额外占去三维的存储器装置中的布局面积的前提下,形成电容串结构。并且,本发明的存储器装置与电子装置可搭配上述的电容串结构来操作,以达到减小存储器装置的布局面积,与降低电路成本的目的。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。