1.本技术实施例涉及集成电路领域,具体而言,涉及一种存储地址传输电路、方法、装置、存储介质及电子设备。

背景技术:

2.随着近代制造技术的进步,集成电路进入了深层次的微米制造阶段,单一芯片上能够容纳的晶体管产品的数量达到了20,000,000至40,000,000个,并且由于微处理机的制造,集成电路工业还诞生了系统单芯片(soc),随着芯片技术的发展,一些存储芯片上开始具备一定的测试和修复功能。

3.相关技术中为了实现存储芯片上的测试和修复功能一般通过比较器确定内存单元能否完成使能操作,在接收到内存单元的地址的情况下,通过比较器将内存单元的地址与错误内存缓存中的错误内存的地址进行比较,在发现错误内存的情况下,使用备用的内存完成使能操作。这种在存储地址传输的过程中引入地址比较器的方式会增加存储地址传输链路的长度和操作逻辑,严重影响存储地址的传输效率。

4.针对相关技术中,存储地址的传输效率较低等问题,尚未提出有效的解决方案。

技术实现要素:

5.本技术实施例提供了一种存储地址传输电路、方法、装置、存储介质及电子设备,以至少解决相关技术中电路测试的效率较低的问题。

6.根据本技术的一个实施例,提供了一种存储地址传输电路,包括:n个存储使能链路,所述n个存储使能链路的n个输入端用于与地址译码器的n个存储使能端连接,所述地址译码器还具有地址输入端,所述地址输入端用于接收存储地址;每个存储使能链路用于将所述n个存储使能端中的一个存储使能端连接至存储模块所包括的m个存储单元中的一个目标存储单元上,所述目标存储单元是处于正常工作状态的存储单元,所述n个存储使能链路是在所述存储模块的内建自我测试阶段形成的,n和m均为大于1的正整数,n小于m。

7.在一个示例性实施例中,每个所述存储使能端通过所述存储地址传输电路连接了所述m个存储单元中的q个存储单元,其中,所述m个存储单元中包括n个主用存储单元和p个备用存储单元,其中,p为m-n;每个所述存储使能端连接所述n个主用存储单元中的一个所述主用存储单元以及所述p个备用存储单元,形成所述存储使能端对应的q个存储链路,其中,p为q-1,所述q个存储链路中的一个存储链路作为一个所述存储使能链路处于连通状态,所述q个存储链路中除所述一个存储链路之外的其他存储链路处于断开状态。

8.在一个示例性实施例中,所述存储地址传输电路包括:r层的交换器数组,其中,所述r层的交换器数组形成n

×

q个存储链路。

9.在一个示例性实施例中,r层的所述交换器数组包括s个一对t交换器组件,t大于2,r以及每层的一对t交换器组件数量是根据n,p和t确定的。

10.在一个示例性实施例中,所述存储地址传输电路包括:n组单路半交换器数组,其

中,每组所述单路半交换器数组包括p个单路半交换器形成每个所述存储使能端对应的q个存储链路,其中,每个所述单路半交换器包括一个三态逻辑缓冲器和一个数据拴锁,所述三态逻辑缓冲器的输入端旁路连接在所述存储使能端与对应的所述主用存储单元之间的存储链路上,所述三态逻辑缓冲器的输出端连接在一个所述备用存储单元上,所述数据拴锁与所述三态逻辑缓冲器的控制端连接。

11.在一个示例性实施例中,所述存储地址传输电路,还包括:连接控制电路,其中,所述连接控制电路与所述存储地址传输电路中的每条存储链路连接;所述连接控制电路,用于在所述内建自我测试阶段根据测试结果生成控制信号;向所述存储地址传输电路中的每条存储链路发送所述控制信号,其中,所述控制信号用于连通所述n个存储使能链路,并断开除所述n个存储使能链路之外的其他存储链路。

12.在一个示例性实施例中,在所述存储地址传输电路包括r层的交换器数组的情况下,所述连接控制电路,包括:错误地址缓存器和第一链路控制器,其中,所述错误地址缓存器与所述第一链路控制器连接,所述第一链路控制器与每个所述一对t交换器组件的控制端连接;所述错误地址缓存器,用于在所述内建自我测试阶段获取错误存储地址作为所述测试结果;所述第一链路控制器,用于根据所述错误存储地址生成每个所述一对t交换器组件对应的所述控制信号;向每个所述一对t交换器组件发送对应的所述控制信号。

13.在一个示例性实施例中,在所述存储地址传输电路包括n组单路半交换器数组的情况下,所述连接控制电路,包括:第二链路控制器,其中,所述第二链路控制器与每个所述数据拴锁连接;所述第二链路控制器,用于根据在所述内建自我测试阶段获取到的错误存储地址生成每个所述单路半交换器对应的所述控制信号;向每个所述单路半交换器发送对应的所述控制信号。

14.根据本技术的另一个实施例,提供了一种存储设备,包括:地址译码器,存储模块和存储地址传输模块,其中,所述地址译码器包括地址输入端和n个存储使能端,所述存储模块包括m个存储单元,所述地址输入端用于接收存储地址,所述n个存储使能端通过所述存储地址传输模块与所述存储模块连接,n和m均为大于1的正整数,n小于m;所述存储地址传输模块包括n个存储使能链路,每个存储使能链路用于将所述n个存储使能端中的一个存储使能端连接至所述m个存储单元中的一个目标存储单元上,所述目标存储单元是处于正常工作状态的存储单元,所述n个存储使能链路是在所述存储模块的内建自我测试阶段形成的。

15.在一个示例性实施例中,所述m个存储单元中包括n个主用存储单元和p个备用存储单元,其中,p为m-n;每个所述存储使能端通过所述存储地址传输模块连接所述n个主用存储单元中的一个所述主用存储单元以及所述p个备用存储单元,形成所述存储使能端对应的q个存储链路,其中,q为1 p,所述q个存储链路中的一个存储链路作为一个所述存储使能链路处于连通状态,所述q个存储链路中除所述一个存储链路之外的其他存储链路处于断开状态。

16.在一个示例性实施例中,所述存储地址传输模块通过r层的交换器数组形成n

×

q个存储链路,其中,r层的所述交换器数组包括s个一对t交换器组件,t大于2,r以及每层的一对t交换器组件数量是根据n,p和t确定的。

17.在一个示例性实施例中,所述存储地址传输模块通过p个单路半交换器形成每个

所述存储使能端对应的q个存储链路,其中,每个所述单路半交换器包括一个三态逻辑缓冲器和一个数据拴锁,所述三态逻辑缓冲器的输入端旁路连接在所述存储使能端与对应的所述主用存储单元之间的存储链路上,所述三态逻辑缓冲器的输出端连接在一个所述备用存储单元上,所述数据拴锁与所述三态逻辑缓冲器的控制端连接。

18.在一个示例性实施例中,所述存储设备,还包括:连接控制模块,其中,所述连接控制模块与所述存储地址传输模块连接;所述连接控制模块,用于在所述内建自我测试阶段根据测试结果生成控制信号;向所述存储地址传输模块发送所述控制信号,其中,所述控制信号用于连通所述n个存储使能链路,并断开所述存储地址传输模块中除所述n个存储使能链路之外的其他存储链路。

19.在一个示例性实施例中,在所述存储地址传输模块包括r层的交换器数组的情况下,所述连接控制电路,包括:错误地址缓存器和第一链路控制器,其中,所述错误地址缓存器与所述第一链路控制器连接,所述第一链路控制器与每个所述一对t交换器组件的控制端连接;所述错误地址缓存器,用于在所述内建自我测试阶段获取错误存储地址作为所述测试结果;所述第一链路控制器,用于根据所述错误存储地址生成每个所述一对t交换器组件对应的所述控制信号;向每个所述一对t交换器组件发送对应的所述控制信号。

20.在一个示例性实施例中,在所述存储地址传输模块包括n组单路半交换器数组的情况下,所述连接控制电路,包括:第二链路控制器,其中,所述第二链路控制器与每个所述数据拴锁连接;所述第二链路控制器,用于根据在所述内建自我测试阶段获取到的错误存储地址生成每个所述单路半交换器对应的所述控制信号;向每个所述单路半交换器发送对应的所述控制信号。

21.根据本技术的另一个实施例,提供了一种存储地址传输方法,应用于存储地址传输电路,所述存储地址传输电路包括n个存储使能链路,所述方法包括:通过目标输入端接收存储地址,其中,所述n个存储使能链路的n个输入端用于与地址译码器的n个存储使能端连接,所述地址译码器还具有地址输入端,所述地址输入端用于获取所述存储地址,所述n个输入端包括所述目标输入端;通过所述n个存储使能链路中所述目标输入端对应的目标存储使能链路将所述存储地址传输至所述目标输入端所对应的目标存储单元,其中,每个存储使能链路用于将所述n个存储使能端中的一个存储使能端连接至存储模块所包括的m个存储单元中的一个所述目标存储单元上,所述目标存储单元是处于正常工作状态的存储单元,所述n个存储使能链路是在所述存储模块的内建自我测试阶段形成的,n和m均为大于1的正整数,n小于m。

22.在一个示例性实施例中,在所述通过所述n个存储使能链路中所述目标输入端对应的目标存储使能链路将所述存储地址传输至所述目标输入端所对应的目标存储单元之前,所述方法还包括:在所述内建自我测试阶段根据测试结果生成控制信号;向所述存储地址传输电路中的每条存储链路发送所述控制信号,其中,所述控制信号用于连通所述n个存储使能链路,并断开除所述n个存储使能链路之外的其他存储链路。

23.在一个示例性实施例中,所述在所述内建自我测试阶段根据测试结果生成控制信号,包括:在所述内建自我测试阶段获取错误存储地址作为所述测试结果;根据所述错误存储地址生成所述控制信号。

24.在一个示例性实施例中,所述在所述内建自我测试阶段获取错误存储地址作为所

述测试结果,包括:对所述存储模块中的每个存储单元执行内建自我测试;将未内建自我测试的存储单元的目标存储地址确定为所述错误存储地址。

25.根据本技术的另一个实施例,提供了一种存储地址传输装置,应用于存储地址传输电路,所述存储地址传输电路包括n个存储使能链路,所述装置包括:

26.接收模块,用于通过目标输入端接收存储地址,其中,所述n个存储使能链路的n个输入端用于与地址译码器的n个存储使能端连接,所述地址译码器还具有地址输入端,所述地址输入端用于获取所述存储地址,所述n个输入端包括所述目标输入端;

27.传输模块,用于通过所述n个存储使能链路中所述目标输入端对应的目标存储使能链路将所述存储地址传输至所述目标输入端所对应的目标存储单元,其中,每个存储使能链路用于将所述n个存储使能端中的一个存储使能端连接至存储模块所包括的m个存储单元中的一个所述目标存储单元上,所述目标存储单元是处于正常工作状态的存储单元,所述n个存储使能链路是在所述存储模块的内建自我测试阶段形成的,n和m均为大于1的正整数,n小于m。

28.根据本技术的又一个实施例,还提供了一种计算机可读存储介质,所述计算机可读存储介质中存储有计算机程序,其中,所述计算机程序被设置为运行时执行上述任一项方法实施例中的步骤。

29.根据本技术的又一个实施例,还提供了一种电子设备,包括存储器和处理器,所述存储器中存储有计算机程序,所述处理器被设置为运行所述计算机程序以执行上述任一项方法实施例中的步骤。

30.通过本技术,使用包括输入端与地址译码器的n个存储使能端连接的n个存储使能链路的存储地址传输电路,地址译码器还有用于接收存储地址的地址输入端;每个存储使能链路用于将在存储模块的内建自我测试阶段形成的n个存储使能端中的一个存储使能端连接至存储模块所包括的m个存储单元中的一个处于正常工作状态的目标存储单元上,n和m均为大于1的正整数,n小于m。由于在电路的内建自我测试阶段就形成了将每个存储使能端连接至对应的处于正常工作状态的目标存储单元上的工作过程,使得电路在工作模式下存储地址传输的过程不会经过地址比较器等附加的逻辑器件,缩短了链路长度,因此可以解决存储地址的传输效率较低问题,达到提高了存储地址的传输效率的效果。

附图说明

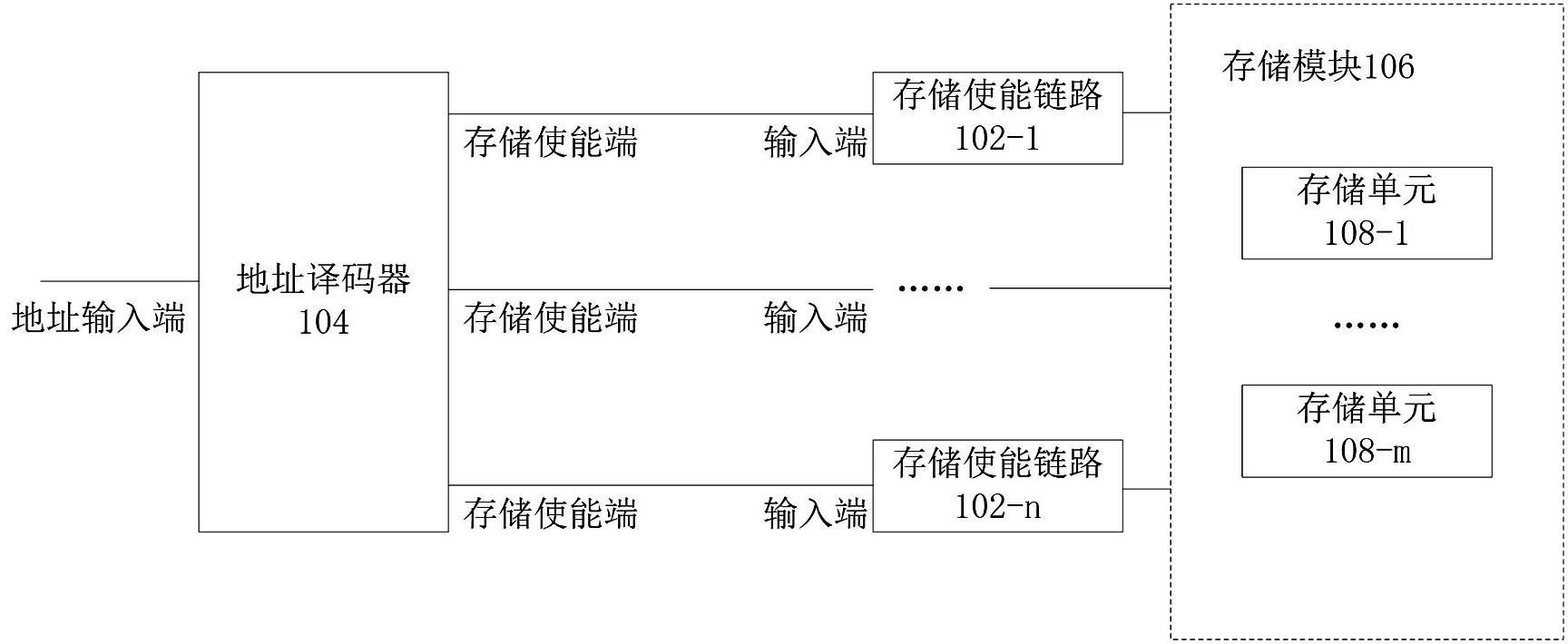

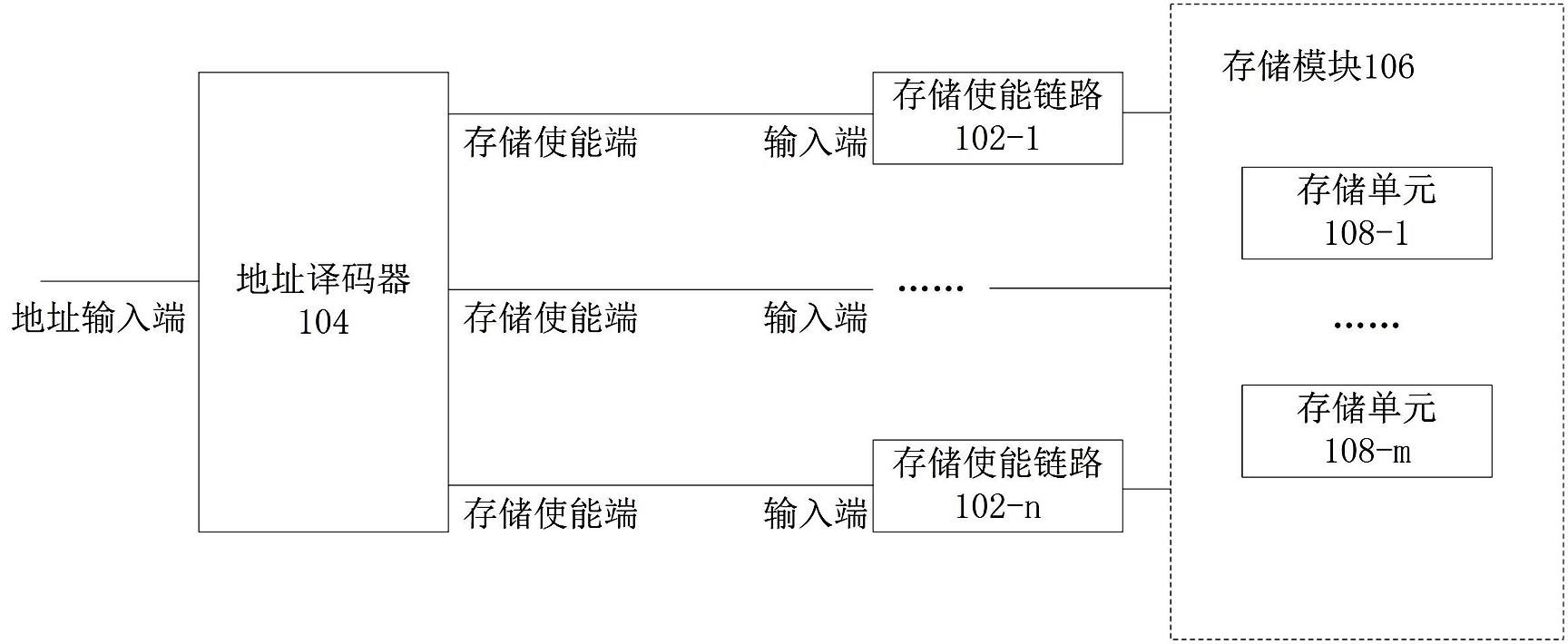

31.图1是根据本技术实施例的一种存储地址传输电路的示意图;

32.图2是根据本技术实施例的一种地址译码器的工作过程的示意图;

33.图3是根据本技术实施例的一种内建自我测试的示意图;

34.图4是根据本技术实施例的一种存储使能链路的示意图;

35.图5是根据本技术实施例的一种交换器数组的示意图;

36.图6是根据本技术实施例的一种一对二交换器组件的示意图;

37.图7是根据本技术实施例的一种包括一对二交换器组件的交换器数组的示意图;

38.图8是根据本技术实施例的一种单路半交换器的示意图;

39.图9是根据本技术实施例的一种包括单路半交换器数组的存储地址传输电路的示意图;

40.图10是根据本技术实施例的一种内建自我测试和内建自我修复电路的示意图一;

41.图11是根据本技术实施例的一种内建自我测试和内建自我修复电路的示意图二;

42.图12是根据本技术实施例的一种存储设备的示意图;

43.图13是根据本技术实施例的一种内建自我测试阶段的工作过程的示意图;

44.图14是根据本技术实施例的一种内建自我测试和内建自我修复电路的示意图三;

45.图15是根据本技术实施例的一种控制信号的生成过程的示意图;

46.图16是根据本技术实施例的一种内建自我测试和内建自我修复电路的示意图四;

47.图17是根据本技术实施例的一种存储地址传输方法的移动终端的硬件结构框图;

48.图18是根据本技术实施例的一种内建自我修复电路的工作过程的流程图;

49.图19是根据本技术实施例的一种内建自我修复电路与内建自我测试电路的工作过程的流程图;

50.图20是根据本技术实施例的存储地址传输方法的流程图;

51.图21是根据本技术实施例的一种存储地址传输电路的工作过程的示意图一;

52.图22是根据本技术实施例的一种存储地址传输电路的工作过程的示意图二;

53.图23是根据本技术实施例的一种存储地址传输电路的工作过程的示意图三;

54.图24是根据本技术实施例的存储地址传输装置的结构框图。

具体实施方式

55.下文中将参考附图并结合实施例来详细说明本技术的实施例。

56.需要说明的是,本技术的说明书和权利要求书及上述附图中的术语“第一”、“第二”等是用于区别类似的对象,而不必用于描述特定的顺序或先后次序。

57.需要说明的是,在系统单一芯片或者整合型集成电路(integrated circuit,ic)的发展过程中,可能会遇到一个棘手的问题:是否需要将动态随机存取存储器(random access memory,ram)或者只读存储器(read-only memory,rom)整合进来。在整合了动态随机存取存储器或者只读存储器的情况下,可能导致原本很轻易就能被测试并修改的动态随机存取存储器或者只读存储器,因为部署在极复杂的电路而变得不易测试与修复,并且测试成本也随之升高,甚至超过整体成本的50%及以上。此时可测试性电路设计(design for testability,dft)成为了电路设计者降低测试成本的一项重要方式。常用的dft方式包括:加入test point(测试点)、scan-based design(基于扫描的设计)、boundary scan(边界扫描)、bist(built-in self test,内建自我测试)等等。

58.需要说明的是,在系统单一芯片的趋势下,可以但不限于将动态随机存取存储器内建在复杂的电路中,但由于电路的测试信号很难到达电路内部需要进行测试的节点,就会导致电路中某些节点的错误(fault)无法直接由外部设备检测到。内建自我测试(bist)是一种通过增加测试电路在芯片(chip)、电路板(board)或者系统(system)上,实现自己对自己进行测试的电路。根据测试的时间,内建自我测试主要分为两种:在线自我测试(on-line bist)与脱机自我测试(off-line bist)。

59.在线自我测试是在电路正常运作的模式下进行测试的工作,在线自我测试可以但不限于包括:电路执行正常功能的同时进行测试(侦错)工作的在线自我测试(concurrent on-line bist),以及在电路执行正常功能的情况下,测试工作处于停止状态,在系统处于

停滞(idle)状态时,进行测试的异步在线自我测试(nonconcurrent on-line bist)。

60.在脱机自我测试中,电路的运作模式包括一般模式(normal mode)和测试模式(test mode)。在测试模式下,测试电路执行自我测试动作;在正常模式下,测试电路关闭,待测电路执行正常功能。脱机自我测试无法实时检测电路发生的错误,电路在执行期(runtime)出现的错误需要在系统重置(system reset)之后才能被脱机自我测试电路找到。

61.一般的脱机自我测试架构可以但不限于采用以下方式工作:在测试模式下,bist控制单元统筹控制整个测试流程,将测试向量产生器(test-pattern generator,tpg)作为待测电路(circuit under test,cut)的输入端,使用结果分析器(output response analyzer,ora)作为待测电路的输出端,可以但不限于使用线性回授移位寄存器(linear feedback shift register,lfsr)作为待测电路的测试向量产生器以及使用结果分析器。

62.需要说明的是,本技术提供的一种存储地址传输电路可以但不限于应用于多种内建动态随机存取存储器或者只读存储器的电路中,比如:系统单一芯片,整合型集成电路等等。可以但不限于使用存储地址传输电路检测并修复多种内建动态随机存取存储器或者只读存储器的电路中发生的动态随机存取存储器或者只读存储器的故障。

63.在本实施例中提供了一种存储地址传输电路,图1是根据本技术实施例的一种存储地址传输电路的示意图,如图1所示,上述存储地址传输电路可以包括:n个存储使能链路(102-1至102-n),所述n个存储使能链路(102-1至102-n)的n个输入端用于与地址译码器104的n个存储使能端连接,所述地址译码器104还具有地址输入端,所述地址输入端用于接收存储地址;每个存储使能链路用于将所述n个存储使能端中的一个存储使能端连接至存储模块106所包括的m个存储单元(108-1至108-m)中的一个目标存储单元上,所述目标存储单元是处于正常工作状态的存储单元,所述n个存储使能链路(102-1至102-n)是在所述存储模块106的内建自我测试阶段形成的,n和m均为大于1的正整数,n小于m。

64.通过上述电路,使用包括输入端与地址译码器的n个存储使能端连接的n个存储使能链路的存储地址传输电路,地址译码器还有用于接收存储地址的地址输入端;每个存储使能链路用于将在存储模块的内建自我测试阶段形成的n个存储使能端中的一个存储使能端连接至存储模块所包括的m个存储单元中的一个处于正常工作状态的目标存储单元上,n和m均为大于1的正整数,n小于m。由于在电路的内建自我测试阶段就形成了将每个存储使能端连接至对应的处于正常工作状态的目标存储单元上的工作过程,使得电路在工作模式下存储地址传输的过程不会经过地址比较器等附加的逻辑器件,缩短了链路长度,因此可以解决存储地址的传输效率较低问题,达到提高了存储地址的传输效率的效果。

65.可选地,在本实施例中,上述地址译码器可以但不限于用于接收存储模块的存储单元的存储地址,并将存储单元的存储地址编译为对应的使能信号。

66.可选地,在本实施例中,上述地址译码器可以但不限于包括一个或者多个地址输入端和一个或者多个存储设备的选择信号的输出端,存储设备的选择信号的输出端可以但不限于为地址译码器的n个存储使能端。地址译码器可以但不限于通过以下过程工作:当特定存储设备的地址从地址译码器的地址输入端输入时,地址译码器输出该设备的选择输出。

67.可选地,在本实施例中,可以但不限于将存储使能链路作为存储地址传输电路中

的重导器(re-mapper)。n个存储使能链路可以但不限于用于将从地址译码器的n个存储使能端接受到的使能信号重新排列后输出至存储模块对应的目标存储单元上,使得使能信号不会被传输至发生错误的存储单元,也就是说,不会将发生错误的存储单元使能(enable)。

68.可选地,在本实施例中,上述存储模块可以但不限于包括多个内存单元,存储模块可以但不限于根据存储使能端发出的使能信号使得目标存储单元被使能。可以但不限于将存储使能端发出的使能信号传输至处于正常工作状态的目标存储单元,使得目标存储单元执行存储使能端发出的使能信号指示的操作,达到电路正常运行的目的。

69.在一个示例性实施例中,提供了一种可选的地址译码器的工作过程的示例,图2是根据本技术实施例的一种地址译码器的工作过程的示意图,如图2所示,以地址译码器在内建自我测试中工作为例,在内建自我测试中可以但不限于使用bist控制单元(bist control unit)统筹包括测试向量产生器(test pattern genetator),待测电路(circuit under test),地址译码器和只读存储器rom等等的模块。可以但不限于采用以下方法检测待测电路中的错误情况:

70.测试向量产生器输入测试序列(test sequence)至待测电路;待测电路将测试序列的输出响应(output response)传输至地址译码器,地址译码器用于将接收到的测试序列的输出响应进行编译。

71.在一个示例性实施例中,提供了一种可选的内建自我测试的过程的示例,图3是根据本技术实施例的一种内建自我测试的示意图,如图3所示,以电路中包括在内建自我测试电路和内建自我修复电路为例,由内建自我测试电路和内建自我修复电路组成的电路的工作模式包括内建自我测试和内建自我修复模式(bist and bisr mode)与一般模式(normal mode),可以但不限于采用以下方式使能电路中的存储模块中的目标存储单元:

72.在电路处于内建自我测试模式(bist mode)中,可以但不限于采用以下方式工作:内建自我测试模块(bist module)的数据输入端(data input)输入数据,通过检测存储模块在数据输出端(data output)输出的数据与输入数据是否相同确定存储模块中每个存储单元的使能状态(能否被使能)。

73.在内建自我测试模块的数据输入端的输入数据,与数据输出端(data output)的输出数据相同的情况下,认为存储模块的存储单元正常工作;在内建自我测试模块的数据输入端的输入数据,与数据输出端(data output)的输出数据不同的情况下,认为存储模块的存储单元处于异常状态。

74.在内建自我测试模块(bist module)检测到电路中的错误内存单元(包括不能被使能的存储单元)的情况下,内建自我修复模块(bisr module)将错误内存单元的地址存放至错误地址缓存器(fail-address buffers)中,具体的,内建自我修复模块(bisr module)使用错误地址缓存器的首个未使用的缓存单元存放错误内存单元的地址;内建自我测试和内建自我修复模式重复上述检测动作,直到完成对存储模块(ram array module)中每个存储单元的测试与修复,电路进入一般模式(normal mode)。

75.在一个示例性实施例中,每个所述存储使能端通过所述存储地址传输电路连接了所述m个存储单元中的q个存储单元,其中,所述m个存储单元中包括n个主用存储单元和p个备用存储单元,其中,p为m-n;每个所述存储使能端连接所述n个主用存储单元中的一个所述主用存储单元以及所述p个备用存储单元形成所述存储使能端对应的q个存储链路,其

中,p为q-1,所述q个存储链路中的一个存储链路作为一个所述存储使能链路处于连通状态,所述q个存储链路中除所述一个存储链路之外的其他存储链路处于断开状态。

76.可选地,在本实施例中,上述存储使能端可以但不限于通过包括n个存储使能链路的存储地址传输电路连接了存储模块中的多个存储单元。每个存储使能端可以但不限于连接了多个存储单元,每个存储使能端连接的多个存储单元可以但不限于包括一个主用存储单元以及多个备用存储单元。

77.可选地,在本实施例中,上述每个存储使能端可以但不限于有其对应的主用存储单元,每个存储使能端的主用存储单元可以但不限于是预先确定的,比如:在需要对存储模块中的存储单元进行使能的情况下,可以但不限于将存储单元中首个空闲的存储单元确定为主用存储单元。

78.可选地,在本实施例中,每个存储使能端可以但不限于有相同数量的多个备用存储单元,比如:以包括存储使能端a,存储使能端b以及存储使能端c为例,存储使能端a可以但不限于有p1个备用存储单元,存储使能端b可以但不限于有p2个备用存储单元,存储使能端c可以但不限于有p3个备用存储单元,其中,p1=p2=p3。

79.可选地,在本实施例中,可以但不限于根据存储模块中存储单元的数量以及与存储单元连接的存储使能链路的数量确定存储单元中包括的主用存储单元的数量和备用存储单元的数量,比如:以存储地址传输电路包括n个存储使能链路,存储模块包括m个存储单元为例,n个存储使能链路可以但不限于与存储模块中的n个主用存储单元连接,备用存储单元的数量为存储模块中包括的全部的存储单元的数量m与存储模块中包括的主用存储单元的数量n的差值(m-n)。

80.可选地,在本实施例中,每个存储使能端可以但不限于连接了多个存储单元,可以但不限于将存储使能端与与其连接的每个存储单元之间的连接链路确定为一条存储链路,每个存储使能端可以但不限于有多条存储链路,每个存储使能端的存储链路的个数可以但不限于是根据与存储使能端连接的存储单元的个数确定的,比如:在存储使能端连接了p个备用存储单元,1个主用存储单元的情况下,可以但不限于将p 1确定为存储使能端的存储链路的个数。

81.可选地,在本实施例中,可以但不限于将用于传输用于使能存储单元的使能信号的存储链路确定为存储使能链路。对于一个存储使能端可以但不限于具有一个存储使能链路使得使能存储单元的使能信号能够到达目标存储单元。

82.在一个示例性实施例中,提供了一种存储使能链路的示例,图4是根据本技术实施例的一种存储使能链路的示意图,如图4所示,以地址译码器的三个存储使能端分别通过存储地址传输电路连接了4个存储单元中的3个存储单元为例,每个存储使能端可以但不限于通过以下方式确定存储使能链路:

83.存储模块包括4个存储单元,其中,存储单元包括3个主用存储单元和1个备用存储单元,每个存储使能端分别连接了与其对应的1个主用存储单元以及1个备用存储单元,每个存储使能端具有2个存储链路。

84.可以但不限于在每个存储使能端的2个存储链路中选择1个存储链路作为处于连通状态的存储使能链路,可以但不限于控制2个存储链路中另1个存储链路保持断开状态。

85.在一个示例性实施例中,所述存储地址传输电路包括:r层的交换器数组,其中,所

述r层的交换器数组形成n

×

q个存储链路。

86.可选地,在本实施例中,上述交换器数组可以但不限于用于连接地址译码器的存储使能端与存储使能端对应的存储单元,可以但不限于使用交连网络作为交换器数组的基础架构。

87.可选地,在本实施例中,上述交换器数组可以但不限于包括r层,比如:2层的交换器数组,3层的交换器数组等等。

88.可选地,在本实施例中,上述交换器数组可以但不限于根据主用存储单元的个数n与每个存储使能端的存储链路q个存储链路的网络,可以但不限于根据主用存储单元的个数n以及每个存储使能端的存储链路q确定交换器数组的层数r。

89.在一个示例性实施例中,提供了一种交换器数组的示例,图5是根据本技术实施例的一种交换器数组的示意图,如图5所示,对于包括m个存储单元的存储模块,可以但不限于使用2m至2m p的交连网络组成交换器数组,p为备用存储单元的个数,以存储地址传输电路连接了n=4个存储使能端,每个存储使能端连接了内存模块中的q=4个存储单元,交换器数组的层数r=2为例,交换器数组中存储链路的个数为n

×

q=4

×

4=16,从上至下依次为交换器数组的第一层和第二层,第一层包括与4个存储使能端连接的4个第一层交换器组件,第一层交换器组件依次连接6个第二层交换器组件,第二层交换器组件依次与7个存储单元连接,其中,交换器数组从输入端到输出端的路径(path)都不会也不允许与其他路径相交于同一个节点(note)。

90.在一个示例性实施例中,r层的所述交换器数组包括s个一对t交换器组件,t大于2,r以及每层的一对t交换器组件数量是根据n,p和t确定的。

91.可选地,在本实施例中,可以但不限于根据存储地址传输电路连接的存储使能端的个数n,备用存储单元的个数p和一对t交换器组件的输出个数t确定r层的交换器数组中一对t交换器组件的数量s,比如:以存储模块包括m个存储单元、交换器数组的层数为r为例,根据公式计算一对t交换器组件的数量。

92.可选地,在本实施例中,上述一对t交换器组件可以但不限于用于接收地址译码器的n个存储使能端发出的使能信号。

93.可选地,在本实施例中,可以但不限于连接t个三态逻辑缓冲器得到一对t交换器组件,一个一对t交换器组件中三态逻辑缓冲器的个数可以但不限于等于一对t交换器组件的输出个数t。

94.在一个示例性实施例中,提供了一种一对二交换器组件的示例,图6是根据本技术实施例的一种一对二交换器组件的示意图,如图6所示,每个一对二交换器组件包括两个三态逻辑缓冲器(tri-state-buffer),可以但不限于通过一条选择线(sel)控制一对二交换器组件选择对应的线路(out0或者out1)进行输出。

95.在一个示例性实施例中,提供了一种包括了交换器组件的交换器数组的示例,图7是根据本技术实施例的一种包括一对二交换器组件的交换器数组的示意图,如图7所示,以存储模块包括sram(static random-access memory,静态随机存取存储器)0、sram1、sram2、sram3、sram4、sram5以及sram6,r=2层的交换器数组包括s=10个一对二交换器组件

(t=2),地址译码器包括4个存储使能端为例,交换器数组可以但不限于通过以下方式工作:

96.以地址译码器的4个存储使能端传输了4个使能信号(sram0_en,sram1_en,sram2_en和sram3_en)为例,交换器数组中包括第一层和第二层,每层的节点通过一对二交换器组件实现向多条存储链路中对应的存储链路输出,每个使能信号可以但不限于有其对应的1个主用存储单元以及3个备用存储单元(q-1=3),每个使能信号可以但不限于有4条不同的存储链路,r=2层的交换器数组形成了4

×

4=16条存储链路。

97.对于sram0_en,sram0_en有主用存储单元sram0以及3个备用存储单元(sram1,sram2和sram3),形成的4条存储链路分别为:sram0_en经过第一层交换器数组中的一对二交换器组件sw1-0,到达第二层交换器数组中一对二交换器组件sw0-0将sram0使能;或者,sram0_en经过第一层交换器数组中的一对二交换器组件sw1-0,到达第二层交换器数组中一对二交换器组件sw0-0将sram1使能;或者,sram0_en经过第一层交换器数组中的一对二交换器组件sw1-0,到达第二层交换器数组中一对二交换器组件sw0-2将sram2使能;或者,sram0_en经过第一层交换器数组中的一对二交换器组件sw1-0,到达第二层交换器数组中一对二交换器组件sw0-2将sram3使能。

98.对于sram1_en,sram1_en有主用存储单元sram1以及3个备用存储单元(sram2,sram3和sram4),形成的4条存储链路分别为:sram1_en经过第一层交换器数组中的一对二交换器组件sw1-1,到达第二层交换器数组中一对二交换器组件sw0-1将sram1使能;或者,sram1_en经过第一层交换器数组中的一对二交换器组件sw1-1,到达第二层交换器数组中一对二交换器组件sw0-1将sram2使能;或者,sram1_en经过第一层交换器数组中的一对二交换器组件sw1-1,到达第二层交换器数组中一对二交换器组件sw0-3将sram3使能;或者,sram1_en经过第一层交换器数组中的一对二交换器组件sw1-1,到达第二层交换器数组中一对二交换器组件sw0-3将sram4使能。

99.对于sram2_en,sram2_en有主用存储单元sram2以及3个备用存储单元(sram3,sram4和sram5),形成的4条存储链路分别为:sram2_en经过第一层交换器数组中的一对二交换器组件sw1-2,到达第二层交换器数组中一对二交换器组件sw0-2将sram2使能;或者,sram2_en经过第一层交换器数组中的一对二交换器组件sw1-2,到达第二层交换器数组中一对二交换器组件sw0-2将sram3使能;或者,sram2_en经过第一层交换器数组中的一对二交换器组件sw1-2,到达第二层交换器数组中一对二交换器组件sw0-4将sram4使能;或者,sram2_en经过第一层交换器数组中的一对二交换器组件sw1-2,到达第二层交换器数组中一对二交换器组件sw0-4将sram5使能。

100.对于sram3_en,sram3_en有主用存储单元sram3以及3个备用存储单元(sram4,sram5和sram6),形成的4条存储链路分别为:sram3_en经过第一层交换器数组中的一对二交换器组件sw1-3,到达第二层交换器数组中一对二交换器组件sw0-3将sram3使能;或者,sram3_en经过第一层交换器数组中的一对二交换器组件sw1-3,到达第二层交换器数组中一对二交换器组件sw0-3将sram4使能;或者,sram3_en经过第一层交换器数组中的一对二交换器组件sw1-3,到达第二层交换器数组中一对二交换器组件sw0-5将sram5使能;或者,sram3_en经过第一层交换器数组中的一对二交换器组件sw1-3,到达第二层交换器数组中一对二交换器组件sw0-5将sram6使能。

101.使用r层的交换器数组作为存储地址传输电路,使得电路的扩充较为容易。

102.在一个示例性实施例中,所述存储地址传输电路包括:n组单路半交换器数组,其中,每组所述单路半交换器数组包括p个单路半交换器形成每个所述存储使能端对应的q个存储链路,其中,每个所述单路半交换器包括一个三态逻辑缓冲器和一个数据拴锁,所述三态逻辑缓冲器的输入端旁路连接在所述存储使能端与对应的所述主用存储单元之间的存储链路上,所述三态逻辑缓冲器的输出端连接在一个所述备用存储单元上,所述数据拴锁与所述三态逻辑缓冲器的控制端连接。

103.可选地,在本实施例中,存储地址传输电路可以但不限于通过n组单路半交换器数组接收地址译码器的n个存储使能端发出的使能信号。

104.可选地,在本实施例中,n组单路半交换器数组可以但不限于用于将地址译码器的n个存储使能端发出的使能信号重新排列后传输至目标存储单元,并使能目标存储单元。

105.可选地,在本实施例中,每组单路半交换器数组包括p个单路半交换器,单路半交换器可以但不限于包括一个三态逻辑缓冲器和一个数据拴锁。数据拴锁连接三态逻辑缓冲器的控制端,可以但不限于通过数据拴锁确定三态逻辑缓冲器的输出。

106.可选地,在本实施例中,三态逻辑缓冲器的输入端旁路连接在地址译码器的存储使能端与对应的主用存储单元之间的存储链路上,三态逻辑缓冲器的输出端连接在一个备用存储单元上,三态逻辑缓冲器可以但不限于根据数据拴锁中存储的信号确定使能的目标存储单元。

107.可选地,在本实施例中,数据拴锁可以但不限于用于存储一个字节(bit)的错误内存单元的地址,数据栓锁可以但不限于根据预先存储的错误内存单元的地址控制三态逻辑缓冲器接收到的使能信号的传输。

108.在一个示例性实施例中,提供了一种单路半交换器的示例,图8是根据本技术实施例的一种单路半交换器的示意图,如图8所示,单路半交换器可以但不限于包括一个三态逻辑缓冲器和一个数据拴锁(latch),以使用单路半交换器组成n组单路半交换器数组作为存储地址传输电路为例,当内存模块(ram module)包括n个主用存储单元,可以但不限于根据主用存储单元的个数n以及备用存储单元的个数p确定单路半交换器数组的个数m以及单路半交换器数组的个数p。

109.在一个示例性实施例中,提供了一种包括单路半交换器数组的存储地址传输电路的示例,图9是根据本技术实施例的一种包括单路半交换器数组的存储地址传输电路的示意图,如图9所示,以存储模块包括sram0、sram1、sram2、sram3和sram4,存储地址传输电路包括4组单路半交换器数组,每组单路半交换器数组包括1个单路半交换器形成每个存储使能端对应的2个存储链路,每个单路半交换器包括一个三态逻辑缓冲器和一个数据拴锁为例,单路半交换器数组可以但不限于通过以下方式工作:

110.以地址译码器的4个存储使能端传输了4个使能信号为例,每个单路半交换器可以但不限于通过一个三态逻辑缓冲器和一个数据拴锁实现输出两条存储链路,每个使能信号可以但不限于有其对应的1个主用存储单元以及1个备用存储单元,每个使能信号可以但不限于有2条不同的存储链路。

111.对于写使能信号wen0和读使能信号ren0,可以但不限于有主用存储单元sram0以及备用存储单元sram4,形成的2条存储链路分别为:写使能信号wen0和读使能信号ren0通过三态逻辑缓冲器的输入端旁路到达主用存储单元sram0;或者,写使能信号wen0和读使能

信号ren0通过连接在三态逻辑缓冲器的控制端的数据拴锁到达备用存储单元sram4。

112.对于写使能信号wen1和读使能信号ren1,可以但不限于有主用存储单元sram1以及备用存储单元sram4,形成的2条存储链路分别为:写使能信号wen1和读使能信号ren1通过三态逻辑缓冲器的输入端旁路到达主用存储单元sram1;或者,写使能信号wen1和读使能信号ren1通过连接在三态逻辑缓冲器的控制端的数据拴锁到达备用存储单元sram4。

113.对于写使能信号wen2和读使能信号ren2,可以但不限于有主用存储单元sram2以及备用存储单元sram4,形成的2条存储链路分别为:写使能信号wen2和读使能信号ren2通过三态逻辑缓冲器的输入端旁路到达主用存储单元sram2;或者,写使能信号wen2和读使能信号ren2通过连接在三态逻辑缓冲器的控制端的数据拴锁到达备用存储单元sram4。

114.对于写使能信号wen3和读使能信号ren3,可以但不限于有主用存储单元sram3以及备用存储单元sram4,形成的2条存储链路分别为:写使能信号wen3和读使能信号ren3通过三态逻辑缓冲器的输入端旁路到达主用存储单元sram3;或者,写使能信号wen3和读使能信号ren3通过连接在三态逻辑缓冲器的控制端的数据拴锁到达备用存储单元sram4。

115.相比于图6可知,在使用r层的交换器数组作为存储地址传输电路中,每个交换器数组包括s个一对t交换器组件,每个一对t交换器组件中至少包括t个三态逻辑缓冲器缩;使用n组单路半交换器数组作为存储地址传输电路,每组单路半交换器数组包括p个单路半交换器,每个单路半交换器包括一个三态逻辑缓冲器和一个数据拴锁,因此相比于使用r层的交换器数组作为存储地址传输电路,使用n组单路半交换器数组作为存储地址传输电路减少了电路中三态逻辑缓冲器的数量,存储地址传输电路的面积可以但不限于减小了50%。

116.因为制程技术的进步、良率的提升,在某些情况下,只需要少数(1至3个)备用存储单元,就能大幅的提升存储模块的利用率,其中以增加一个备用存储单元的效果最大。因此在需要增加的备用存储单元的数量较少的情况下,可以但不限于使用n组单路半交换器数组作为存储地址传输电路,减少了电路内三态逻辑缓冲器的数量,有效的降低了内建自我修复电路面积的需求。可以但不限于包括以下优势:

117.在一般模式下,使能信号在电路中经过的路径更短,在存储地址传输电路中使能信号所经过的路径长度于与交换器数组的层数成正比(也就是与三态逻辑缓冲器的数量有关),对于r层的交换器数组使能信号需要经过t

×

r个三态逻辑缓冲器;而在n组单路半交换器数组中只经过1个三态逻辑缓冲器,并且不会随着备用存储单元的增加而增加。

118.存储地址传输电路的面积减小,虽然n组单路半交换器数组中的每个单路半交换器中包括了一个数据拴锁latch,但在r层的交换器数组中也有同样包括数据拴锁latch功能的器件,只是它并不直接与交换器数组连接。

119.在一个示例性实施例中,所述存储地址传输电路,还包括:连接控制电路,其中,所述连接控制电路与所述存储地址传输电路中的每条存储链路连接;所述连接控制电路,用于在所述内建自我测试阶段根据测试结果生成控制信号;向所述存储地址传输电路中的每条存储链路发送所述控制信号,其中,所述控制信号用于连通所述n个存储使能链路,并断开除所述n个存储使能链路之外的其他存储链路。

120.可选地,在本实施例中,可以但不限于在内建自我测试阶段通过存储地址传输电路中的连接控制电路生成控制信号。内建自我测试阶段可以但不限于用于测试存储模块中

每个存储单元的使能情况,可以但不限于根据内建自我测试阶段得到的对每个存储单元的测试结果确定内建自我修复阶段生成的控制信号。

121.可选地,在本实施例中,可以但不限于根据控制信号从存储地址传输电路中每条存储链路中选择存储使能链路,可以但不限于通过存储使能链路传输信号。可以但不限于通过控制信号连通n个存储使能链路并断开除n个存储使能链路之外的其他存储链路。

122.在一个示例性实施例中,在所述存储地址传输电路包括r层的交换器数组的情况下,所述连接控制电路,包括:错误地址缓存器和第一链路控制器,其中,所述错误地址缓存器与所述第一链路控制器连接,所述第一链路控制器与每个所述一对t交换器组件的控制端连接;所述错误地址缓存器,用于在所述内建自我测试阶段获取错误存储地址作为所述测试结果;所述第一链路控制器,用于根据所述错误存储地址生成每个所述一对t交换器组件对应的所述控制信号;向每个所述一对t交换器组件发送对应的所述控制信号。

123.可选地,在本实施例中,上述错误地址缓存器可以但不下限于用于在内建自我测试阶段获取错误存储地址作为测试结果进行存储。在一般阶段,错误地址缓存器可以但不下限于是存储了存储模块中错误内存的错误存储地址。

124.可选地,在本实施例中,上述第一链路控制器可以但不限于包括多个输出端,每个输出端都连接了一个一对t交换器组件的控制端。第一链路控制器可以但不限于用于根据错误地址缓存器中的错误存储地址生成每个一对t交换器组件对应的控制信号。

125.可选地,在本实施例中,上述第一链路控制器可以但不限于将每个一对t交换器组件对应的控制信号发送至对应的一对t交换器组件,上述一对t交换器组件可以但不限于根据第一链路控制器的控制信号进行存储使能链路的选择。

126.在一个示例性实施例中,提供了一种内建自我测试和内建自我修复电路的示例,图10是根据本技术实施例的一种内建自我测试和内建自我修复电路的示意图一,如图10所示,内建自我测试和内建自我修复电路包括:连接控制电路(bist/bisr control unit)、内建自我测试模块(bist module)、地址译码器(ram decoder)、r层的交换器数组(switch array)以及内存模块(ram array module)。

127.连接控制电路可以但不限于包括:地址缓存器(address buffers)用于在内建自我测试阶段中存放上一次读出或写入的地址。在进入内建自我测试和内建自我修复模式(bist and bisr mode)的情况下,在内建自我测试模块根据数据输入端(data input)与数据输出端(data output)的数据情况检测到错误内存地址时,可以但不限于通过缓存器控制模块(bisr buffer control)控制错误地址缓存器(fail address buffers)会将地址缓存器中的地址,存入错误地址缓存器中的第一个空位置。可以但不限于通过连接控制电路中的握手器(bist/bisr handshaker)保持电路中的信号同步。

128.在电路处于一般模式的情况下,地址译码器从地址输入端(address input)接收并编译存储单元的地址,并转换为信号ram_en传输至交换器数组。

129.在连接控制电路中还包括:连接控制电路(switch array controller),无论是电路处于bist and bisr mode或是normal mode,都会根据错误地址缓存器中所存放的发生错误的内存的地址产生r层的交换器数组所需要的控制信号(select)。

130.在一个示例性实施例中,在所述存储地址传输电路包括n组单路半交换器数组的情况下,所述连接控制电路,包括:第二链路控制器,其中,所述第二链路控制器与每个所述

数据拴锁连接;所述第二链路控制器,用于根据在所述内建自我测试阶段获取到的错误存储地址生成每个所述单路半交换器对应的所述控制信号;向每个所述单路半交换器发送对应的所述控制信号。

131.可选地,在本实施例中,上述数据拴锁可以但不下限于用于在内建自我测试阶段获取错误存储地址作为测试结果进行存储。在一般阶段,数据拴锁可以但不下限于是存储了存储模块中错误内存的错误存储地址。

132.可选地,在本实施例中,上述第二链路控制器可以但不限于包括多个输出端,每个输出端都连接了一个单路半交换器的控制端。第二链路控制器可以但不限于用于根据数据拴锁中的错误存储地址生成每个单路半交换器对应的控制信号。

133.可选地,在本实施例中,上述单路半交换器可以但不限于将每个单路半交换器对应的控制信号发送至对应的单路半交换器,上述单路半交换器可以但不限于根据单路半交换器的控制信号进行存储使能链路的选择。

134.在一个示例性实施例中,提供了一种内建自我测试和内建自我修复电路的示例,图11是根据本技术实施例的一种内建自我测试和内建自我修复电路的示意图二,如图11所示,内建自我测试和内建自我修复电路包括:连接控制电路(bist/bisr control unit)、内建自我测试模块(bist module)、地址译码器(ram rol decoder)、r层的交换器数组(switch array)以及内存模块(ram array module)。

135.连接控制电路可以但不限于包括:地址缓存器(address buffers)用于在内建自我测试阶段中存放上一次读出或写入的地址。在进入内建自我测试和内建自我修复模式(bist and bisr mode)的情况下,在内建自我测试模块根据数据输入端(data input)与数据输出端(data output)的数据情况检测到错误内存地址时,可以但不限于通过缓存器控制模块(bisr buffer control)控制地址缓存器将错误内存地址发送至数据拴锁(fail address buffers)进行存储。可以但不限于通过连接控制电路中的握手器(bist/bisr handshaker)保持电路中的信号同步。

136.在电路处于一般模式的情况下,地址译码器从地址输入端(address input)接收并编译存储单元的地址,并转换为信号ram_en传输至交换器数组。

137.在连接控制电路中还包括:连接控制电路(switch array controller),无论是电路处于bist and bisr mode或是normal mode,都会根据数据拴锁中所存放的发生错误的内存的地址产生r层的交换器数组所需要的控制信号(select)。

138.在本实施例中提供了一种存储设备,图12是根据本技术实施例的一种存储设备的示意图,如图12所示,上述存储设备包括:地址译码器1202,存储模块1204和存储地址传输模块1206,其中,所述地址译码器1202包括地址输入端和n个存储使能端,所述存储模块1204包括m个存储单元(1208-1至1208-m),所述地址输入端用于接收存储地址,所述n个存储使能端通过所述存储地址传输模块与所述存储模块1204连接,n和m均为大于1的正整数,n小于m;所述存储地址传输模块1206包括n个存储使能链路,每个存储使能链路用于将所述n个存储使能端中的一个存储使能端连接至所述m个存储单元中的一个目标存储单元上,所述目标存储单元是处于正常工作状态的存储单元,所述n个存储使能链路是在所述存储模块的内建自我测试阶段形成的。

139.通过上述设备,使用包括输入端与地址译码器的n个存储使能端连接的n个存储使

能链路的存储地址传输电路,地址译码器还有用于接收存储地址的地址输入端;每个存储使能链路用于将在存储模块的内建自我测试阶段形成的n个存储使能端中的一个存储使能端连接至存储模块所包括的m个存储单元中的一个处于正常工作状态的目标存储单元上,n和m均为大于1的正整数,n小于m。由于在电路的内建自我测试阶段就形成了将每个存储使能端连接至对应的处于正常工作状态的目标存储单元上的工作过程,使得电路在工作模式下存储地址传输的过程不会经过地址比较器等附加的逻辑器件,缩短了链路长度,因此可以解决存储地址的传输效率较低问题,达到提高了存储地址的传输效率的效果。

140.可选地,在本实施例中,上述地址译码器可以但不限于用于接收存储模块的存储单元的存储地址,并将存储单元的存储地址编译为对应的使能信号。

141.可选地,在本实施例中,上述地址译码器可以但不限于包括一个或者多个地址输入端和一个或者多个存储设备的选择信号的输出端,存储设备的选择信号的输出端可以但不限于为地址译码器的n个存储使能端。地址译码器可以但不限于通过以下过程工作:当特定存储设备的地址从地址译码器的地址输入端输入时,地址译码器输出该设备的选择输出。

142.可选地,在本实施例中,可以但不限于将存储使能链路作为存储地址传输电路中的重导器(re-mapper)。n个存储使能链路可以但不限于用于将从地址译码器的n个存储使能端接受到的使能信号重新排列后输出至存储模块对应的目标存储单元上,使得使能信号不会被传输至发生错误的存储单元,也就是说,不会将发生错误的存储单元使能(enable)。

143.可选地,在本实施例中,上述存储模块可以但不限于包括多个内存单元,存储模块可以但不限于根据存储使能端发出的使能信号使得目标存储单元被使能。可以但不限于将存储使能端发出的使能信号传输至处于正常工作状态的目标存储单元,使得目标存储单元执行存储使能端发出的使能信号指示的操作,达到电路正常运行的目的。

144.在一个示例性实施例中,提供了一种可选的内建自我测试阶段的工作过程的示例,图13是根据本技术实施例的一种内建自我测试阶段的工作过程的示意图,如图13所示,待测电路可以但不限包括只读存储器或动态随机存取存储器,可以但不限于通过比较电路将写入(write)的数据与读出(read)的数据做对比,检测数据的写入与读出是否有错误产生,从而确定该地址的内存单元是否有错误产生。内建自我测试阶段的工作过程可以但不限于包括以下步骤:

145.步骤s1302:输入数据data以及存储模块中的存储单元的地址address;

146.步骤s1304:获取需要存储单元执行的使能动作(可以但不限于包括读出和写入等等);

147.步骤s1306:检测输入与输出的数据是否相同(存储单元能否完成使能动作);

148.步骤s1308:在输入与输出的数据不相同的情况下,发送用于指示错误内存单元的信号(bist fail);在输入与输出的数据相同的情况下,检测下一个内存单元的使能情况,直至完成全部内存单元的检测。

149.在一个示例性实施例中,提供了一种可选的内建自我测试和内建自我修复电路的示例,图14是根据本技术实施例的一种内建自我测试和内建自我修复电路的示意图三,如图14所示,内建自我测试和内建自我修复电路包括:内建自我修复模块(bisr module)、内建自我测试模块(bist module)、错误地址缓存器(fail address buffers)、地址译码器

(ram decoder)、存储地址传输模块(switch array)以及存储模块(ram array module)。存储地址传输模块可以但不限于包括交换器数组,可以但不限于将交换器数组放在地址译码器与内存模块之间。

150.在进入内建自我测试和内建自我修复模式(bist and bisr mode)的情况下,内建自我测试模块找到一个错误内存地址时,错误地址缓存器会将地址存入。无论是电路处于bist and bisr mode或是normal mode,bisr模块都会根据错误地址缓存器中所存放的发生错误的内存的地址产生控制信号(select)。

151.在一个示例性实施例中,所述m个存储单元中包括n个主用存储单元和p个备用存储单元,其中,p为m-n;每个所述存储使能端通过所述存储地址传输模块连接所述n个主用存储单元中的一个所述主用存储单元以及所述p个备用存储单元,形成所述存储使能端对应的q个存储链路,其中,q为1 p,所述q个存储链路中的一个存储链路作为一个所述存储使能链路处于连通状态,所述q个存储链路中除所述一个存储链路之外的其他存储链路处于断开状态。

152.可选地,在本实施例中,上述存储使能端可以但不限于通过包括n个存储使能链路的存储地址传输电路连接了存储模块中的多个存储单元。每个存储使能端可以但不限于连接了多个存储单元,每个存储使能端连接的多个存储单元可以但不限于包括一个主用存储单元以及多个备用存储单元。

153.可选地,在本实施例中,上述每个存储使能端可以但不限于有其对应的主用存储单元,每个存储使能端的主用存储单元可以但不限于是预先确定的,比如:在需要对存储模块中的存储单元进行使能的情况下,可以但不限于将存储单元中首个空闲的存储单元确定为主用存储单元。

154.可选地,在本实施例中,每个存储使能端可以但不限于有相同数量的多个备用存储单元,比如:以包括存储使能端a,存储使能端b以及存储使能端c为例,存储使能端a与存储使能端b以及存储使能端c的备用存储单元的数量相同。

155.可选地,在本实施例中,可以但不限于将存储模块中存储单元的数量与存储单元连接的主用存储单元的数量的差值确定为存储单元中包括的备用存储单元的数量。

156.可选地,在本实施例中,可以但不限于根据存储地址传输电路包括n个存储使能链路,确定n个存储使能链路可以但不限于与存储模块中的n个主用存储单元连接,从而得到备用存储单元的数量为存储模块中包括的全部的存储单元的数量m与存储模块中包括的主用存储单元的数量n的差值(m-n)。

157.可选地,在本实施例中,每个存储使能端可以但不限于连接了多个存储单元,可以但不限于将存储使能端与与其连接的每个存储单元之间的连接链路确定为一条存储链路,每个存储使能端可以但不限于有多条存储链路,每个存储使能端的存储链路的个数可以但不限于是根据与存储使能端连接的存储单元的个数确定的,比如:在存储使能端连接了p个备用存储单元,1个主用存储单元的情况下,可以但不限于将p 1确定为存储使能端的存储链路的个数。

158.可选地,在本实施例中,可以但不限于将用于传输用于使能存储单元的使能信号的存储链路确定为存储使能链路。对于一个存储使能端可以但不限于具有一个存储使能链路使得使能存储单元的使能信号能够到达目标存储单元。

159.在一个示例性实施例中,所述存储地址传输模块通过r层的交换器数组形成n

×

q个存储链路,其中,r层的所述交换器数组包括s个一对t交换器组件,t大于2,r以及每层的一对t交换器组件数量是根据n,p和t确定的。

160.可选地,在本实施例中,上述交换器数组可以但不限于使用交连网络作为交换器数组的基础架构。交换器数组可以但不限于包括多个层级,比如:2层的交换器数组,3层的交换器数组等等。

161.可选地,在本实施例中,上述交换器数组可以但不限于是根据主用存储单元的个数n与每个存储使能端的存储链路q个存储链路得到的网络,可以但不限于根据主用存储单元的个数n以及每个存储使能端的存储链路q确定交换器数组的层数r。

162.在一个示例性实施例中,所述存储地址传输模块通过p个单路半交换器形成每个所述存储使能端对应的q个存储链路,其中,每个所述单路半交换器包括一个三态逻辑缓冲器和一个数据拴锁,所述三态逻辑缓冲器的输入端旁路连接在所述存储使能端与对应的所述主用存储单元之间的存储链路上,所述三态逻辑缓冲器的输出端连接在一个所述备用存储单元上,所述数据拴锁与所述三态逻辑缓冲器的控制端连接。

163.可选地,在本实施例中,存储地址传输电路可以但不限于通过n组单路半交换器数组接收地址译码器的n个存储使能端发出的使能信号。

164.可选地,在本实施例中,n组单路半交换器数组可以但不限于用于将地址译码器的n个存储使能端发出的使能信号重新排列后传输至目标存储单元,并使能目标存储单元。

165.可选地,在本实施例中,每组单路半交换器数组包括p个单路半交换器,单路半交换器可以但不限于包括一个三态逻辑缓冲器和一个数据拴锁。数据拴锁连接三态逻辑缓冲器的控制端,可以但不限于通过数据拴锁确定三态逻辑缓冲器的输出。

166.可选地,在本实施例中,三态逻辑缓冲器的输入端旁路连接在地址译码器的存储使能端与对应的主用存储单元之间的存储链路上,三态逻辑缓冲器的输出端连接在一个备用存储单元上,三态逻辑缓冲器可以但不限于根据数据拴锁中存储的信号确定使能的目标存储单元。

167.可选地,在本实施例中,数据拴锁可以但不限于用于存储一个字节(bit)的错误内存单元的地址,数据栓锁可以但不限于根据预先存储的错误内存单元的地址控制三态逻辑缓冲器接收到的使能信号的传输。

168.在一个示例性实施例中,所述存储设备,还包括:连接控制模块,其中,所述连接控制模块与所述存储地址传输模块连接;所述连接控制模块,用于在所述内建自我测试阶段根据测试结果生成控制信号;向所述存储地址传输模块发送所述控制信号,其中,所述控制信号用于连通所述n个存储使能链路,并断开所述存储地址传输模块中除所述n个存储使能链路之外的其他存储链路。

169.可选地,在本实施例中,可以但不限于在内建自我测试阶段通过存储地址传输电路中的连接控制电路生成控制信号。内建自我测试阶段可以但不限于用于测试存储模块中每个存储单元的使能情况,可以但不限于根据内建自我测试阶段得到的对每个存储单元的测试结果确定内建自我修复阶段生成的控制信号。

170.可选地,在本实施例中,可以但不限于根据控制信号从存储地址传输电路中每条存储链路中选择存储使能链路,可以但不限于通过存储使能链路传输信号。可以但不限于

通过控制信号连通n个存储使能链路并断开除n个存储使能链路之外的其他存储链路。

171.在一个示例性实施例中,在所述存储地址传输模块包括r层的交换器数组的情况下,所述连接控制电路,包括:错误地址缓存器和第一链路控制器,其中,所述错误地址缓存器与所述第一链路控制器连接,所述第一链路控制器与每个所述一对t交换器组件的控制端连接;所述错误地址缓存器,用于在所述内建自我测试阶段获取错误存储地址作为所述测试结果;所述第一链路控制器,用于根据所述错误存储地址生成每个所述一对t交换器组件对应的所述控制信号;向每个所述一对t交换器组件发送对应的所述控制信号。

172.可选地,在本实施例中,上述错误地址缓存器可以但不下限于用于在内建自我测试阶段获取错误存储地址作为测试结果进行存储。在一般阶段,错误地址缓存器可以但不下限于是存储了存储模块中错误内存的错误存储地址。

173.可选地,在本实施例中,上述第一链路控制器可以但不限于包括多个输出端,每个输出端都连接了一个一对t交换器组件的控制端。第一链路控制器可以但不限于用于根据错误地址缓存器中的错误存储地址生成每个一对t交换器组件对应的控制信号。

174.可选地,在本实施例中,上述第一链路控制器可以但不限于将每个一对t交换器组件对应的控制信号发送至对应的一对t交换器组件,上述一对t交换器组件可以但不限于根据第一链路控制器的控制信号进行存储使能链路的选择。

175.在一个示例性实施例中,在所述存储地址传输模块包括n组单路半交换器数组的情况下,所述连接控制电路,包括:第二链路控制器,其中,所述第二链路控制器与每个所述数据拴锁连接;所述第二链路控制器,用于根据在所述内建自我测试阶段获取到的错误存储地址生成每个所述单路半交换器对应的所述控制信号;向每个所述单路半交换器发送对应的所述控制信号。

176.可选地,在本实施例中,上述数据拴锁可以但不下限于用于在内建自我测试阶段获取错误存储地址作为测试结果进行存储。在一般阶段,数据拴锁可以但不下限于是存储了存储模块中错误内存的错误存储地址。

177.可选地,在本实施例中,上述第二链路控制器可以但不限于包括多个输出端,每个输出端都连接了一个单路半交换器的控制端。第二链路控制器可以但不限于用于根据数据拴锁中的错误存储地址生成每个单路半交换器对应的控制信号。

178.可选地,在本实施例中,上述单路半交换器可以但不限于将每个单路半交换器对应的控制信号发送至对应的单路半交换器,上述单路半交换器可以但不限于根据单路半交换器的控制信号进行存储使能链路的选择。

179.在一个示例性实施例中,提供了一种可选的控制信号的生成过程的示例,图15是根据本技术实施例的一种控制信号的生成过程的示意图,如图15所示,连接控制电路包括r=2层的交换器数组、连接控制模块、错误地址缓存器和第一链路控制器,交换器数组中可以但不限于通过第0层与存储模块连接,通过第r层连接地址译码器的存储使能端。

180.以将交换器数组看作一个二进制的数值为例,可以但不限于通过20表示第0层交换器(sw0_x),通过21表示第1层交换器(sw1_x)以此类推得到第r层交换器(swr_x)。每个一对t交换器组件的选择线信号为该二进制数的值(value)。

181.当检测到错误内存单元的情况下,可以但不限于将错误内存单元对应的错误地址缓存器(fail-address register,farx)设定为1,可以但不限于根据公式

计算第0层交换器(sw0_x)中首个一对t交换器组件sw0_0的选择线信号sel0_0;可以但不限于根据公式计算第0层交换器(sw0_x)中每个sw0_x的选择线信号sel0_x。

182.对于第二层的选择线信号sel1_x,可以但不限于在sel0_x有进位,或者前1个sel1_x-1为1时,将设定误地址缓存器设定为1,可以但不限于通过公式计算第1层交换器(sw1_x)中首个一对t交换器组件sw1_0的选择线信号sel1_0;可以但不限于根据公式计算第1层交换器(sw1_x)中每个sw1_x的选择线信号sel1_x。

183.得到交换器数组(switch array)的控制信号(select)产生电路(switch array control unit):在交换器数组输入错误地址缓存器(fail address register)的设定值的情况下,可以但不限于对错误地址缓存器(far0、far1、far2、far3、far4、far5)的值进行设定,与确定的首个0进行计算,产生选择线信号sel0_x(可以但不限于包括sel0_0、sel0_1、sel0_2、sel0_3、sel0_4、sel0_5),再根据选择线信号sel0_x产生选择线信号sel1_x(可以但不限于包括sel1_0、sel1_1、sel1_2、sel1_3),得到控制信号。

184.在一个示例性实施例中,提供了一种可选的内建自我测试和内建自我修复电路的示例,图16是根据本技术实施例的一种内建自我测试和内建自我修复电路的示意图四,如图16所示,可以但不限于在图15的基础上,为交换器数组以及控制信号增加连接控制模块(control unit),得到完整的内建自我测试和内建自我修复电路,bistctrl_hswsram是内建自我测试模块,hswsram是内建自我修复模块与存储模块。

185.内建自我测试模块可以但不限于包括输入数据(datain),内存地址(address),重置信号(reset),时钟信号(clock),以及控制电路进入自我测试模式,并接收使能信号(读使能信号ren、写使能信号wen),并将错误错误内存信号或者通过的内存信号传输至内建自我修复模块以及内存模块。

186.内建自我修复模块以及内存模块可以但不限于包括接收bist模块发出的错误内存信号,以及从输出端(dataout)输出数据,重启内建自我测试模块。

187.本技术实施例中所提供的方法实施例可以在移动终端、计算机终端或者类似的运算装置中执行。以运行在移动终端上为例,图17是根据本技术实施例的一种存储地址传输方法的移动终端的硬件结构框图。如图17所示,移动终端可以包括一个或多个(图17中仅示出一个)处理器1702(处理器1702可以包括但不限于微处理器mcu或可编程逻辑器件fpga等的处理装置)和用于存储数据的存储器1704,其中,上述移动终端还可以包括用于通信功能的传输设备1706以及输入输出设备1708。本领域普通技术人员可以理解,图1所示的结构仅为示意,其并不对上述移动终端的结构造成限定。例如,移动终端还可包括比图1中所示更多或者更少的组件,或者具有与图1所示不同的配置。

188.存储器1704可用于存储计算机程序,例如,应用软件的软件程序以及模块,如本技术实施例中的存储地址传输方法对应的计算机程序,处理器1702通过运行存储在存储器1704内的计算机程序,从而执行各种功能应用以及数据处理,即实现上述的方法。存储器1704可包括高速随机存储器,还可包括非易失性存储器,如一个或者多个磁性存储装置、闪

存、或者其他非易失性固态存储器。在一些实例中,存储器1704可进一步包括相对于处理器1702远程设置的存储器,这些远程存储器可以通过网络连接至移动终端。上述网络的实例包括但不限于互联网、企业内部网、局域网、移动通信网及其组合。

189.传输设备1706用于经由一个网络接收或者发送数据。上述的网络具体实例可包括移动终端的通信供应商提供的无线网络。在一个实例中,传输设备1706包括一个网络适配器(network interface controller,简称为nic),其可通过基站与其他网络设备相连从而可与互联网进行通讯。在一个实例中,传输设备1706可以为射频(radio frequency,简称为rf)模块,其用于通过无线方式与互联网进行通讯。

190.需要说明的是,内建自我修复是将内建自我测试进行了进一步的提升,将内建自我测试在待测电路中检测到的错误存储单元,进行适当的处理,使得该错误不会对待测电路的正常工作产生影响。在有规律比如:构造相同并且重复出现的电路中,内建自我修复电路可以但不限于使用预留的存储单元取代(repair)发生错误的存储单元,例如:复杂可程序逻辑组件(complex programmable logic device,cpld)、现场可程序门阵列(field-programmable gate array,fpga)、ram、rom等等。

191.内建自我修复可以但不限于通过以下方式对错误存储单元进行修复:激光可编程熔断器(laser programmable fuses),即通过雷射烧掉电路上的一部分保险丝,使得电路能够避开有错误产生的存储单元,实现通过预留的存储单元取代有错误产生的存储单元。非易失性存储器元件(non-volatile memory element),即通过程序来实现“烧掉”保险丝的动作,使得电路能够避开有错误产生的存储单元,实现通过预留的存储单元取代有错误产生的存储单。在电路中增加缓存器(buffer)与地址比较器(compare module)等等。

192.在一个示例性实施例中,提供了一种可选的内建自我修复电路的工作过程的示例,图18是根据本技术实施例的一种内建自我修复电路的工作过程的流程图,如图18所示,在构造相同并且重复出现的电路中内建自我修复电路可以但不限于通过以下方法工作:

193.在进行内建自我测试的过程中,在发现了错误存储单元的情况下,内建自我修复检测存储模块中是否有预留的备用存储单元,在存储模块中有预留的备用存储单元的情况下,使用预留的备用存储单元替换错误存储单元进行使能工作;在存储模块中没有预留的备用存储单元的情况下,发送失败信号(bist失败信号)至控制端。

194.在未发现错误存储单元的情况下,检测存储模块中的下一个存储单元,直至完成对存储模块的检测。

195.在一个示例性实施例中,提供了一种可选的内建自我修复电路与内建自我测试电路的工作过程的示例,图19是根据本技术实施例的一种内建自我修复电路与内建自我测试电路的工作过程的流程图,如图19所示,内建自我修复电路与内建自我测试电路可以但不限于通过以下方法工作:

196.在待测电路进入测试模式的情况下,内建自我测试电路检测到发生错误的错误内存单元的情况下,内建自我修复电路可以但不限于将错误内存单元的地址发送至缓存器进行存储。

197.在待测电路进入一般模式的情况下,地址比较器可以但不限将每个存储单元的地址,与存放在缓存器内的全部的错误内存单元的地址进行比较:在存储单元的地址与缓存器内全部的错误内存单元的地址都不同的情况下,认为存储单元正常运行,将该地址传输

至地址译码器;在存储单元的地址与缓存器内某一的错误内存单元的地址相同的情况下,认为存储单元为错误内存单元,可以但不限于将该错误内存单元的地址替换为预留的备用存储单元的地址,再备用存储单元的地址传输至地址译码器。

198.在本实施例中提供了一种运行于上述移动终端的存储地址传输方法,图20是根据本技术实施例的存储地址传输方法的流程图,如图20所示,该流程包括如下步骤:

199.步骤s2002,通过目标输入端接收存储地址,其中,所述n个存储使能链路的n个输入端用于与地址译码器的n个存储使能端连接,所述地址译码器还具有地址输入端,所述地址输入端用于获取所述存储地址,所述n个输入端包括所述目标输入端;

200.步骤s2004,通过所述n个存储使能链路中所述目标输入端对应的目标存储使能链路将所述存储地址传输至所述目标输入端所对应的目标存储单元,其中,每个存储使能链路用于将所述n个存储使能端中的一个存储使能端连接至存储模块所包括的m个存储单元中的一个所述目标存储单元上,所述目标存储单元是处于正常工作状态的存储单元,所述n个存储使能链路是在所述存储模块的内建自我测试阶段形成的,n和m均为大于1的正整数,n小于m。

201.通过上述步骤,使用包括输入端与地址译码器的n个存储使能端连接的n个存储使能链路的存储地址传输电路,地址译码器还有用于接收存储地址的地址输入端;每个存储使能链路用于将在存储模块的内建自我测试阶段形成的n个存储使能端中的一个存储使能端连接至存储模块所包括的m个存储单元中的一个处于正常工作状态的目标存储单元上,n和m均为大于1的正整数,n小于m。由于在电路的内建自我测试阶段就形成了将每个存储使能端连接至对应的处于正常工作状态的目标存储单元上的工作过程,使得电路在工作模式下存储地址传输的过程不会经过地址比较器等附加的逻辑器件,缩短了链路长度,因此可以解决存储地址的传输效率较低问题,达到提高了存储地址的传输效率的效果。

202.可选地,在本实施例中,上述存储地址传输方法可以但不限于应用于存储地址传输电路,存储地址传输电路可以但不限于包括n个存储使能链路。

203.在上述步骤s2002提供的技术方案中,可以但不限于从地址译码器的n个存储使能端接收经过地址译码器编译的存储地址,上述存储地址可以但不限于用于指示在存储模块中需要使能的存储单元的地址信息。

204.可选地,在本实施例中,上述地址译码器可以但不限于包括一个或者多个地址输入端和一个或者多个存储设备的选择信号的输出端,存储设备的选择信号的输出端可以但不限于为地址译码器的n个存储使能端。地址译码器可以但不限于通过以下过程工作:当特定存储设备的地址从地址译码器的地址输入端输入时,地址译码器输出该设备的选择输出。

205.可选地,在本实施例中,可以但不限于将存储使能链路作为存储地址传输电路中的重导器(re-mapper)。n个存储使能链路可以但不限于用于将从地址译码器的n个存储使能端接受到的使能信号重新排列后输出至存储模块对应的目标存储单元上,使得使能信号不会被传输至发生错误的存储单元,也就是说,不会将发生错误的存储单元使能(enable)。

206.可选地,在本实施例中,上述存储模块可以但不限于包括多个内存单元,存储模块可以但不限于根据存储使能端发出的使能信号使得目标存储单元被使能。可以但不限于将存储使能端发出的使能信号传输至处于正常工作状态的目标存储单元,使得目标存储单元

执行存储使能端发出的使能信号指示的操作,达到电路正常运行的目的。

207.在上述步骤s2004提供的技术方案中,上述存储使能端可以但不限于通过包括n个存储使能链路的存储地址传输电路连接了存储模块中的多个存储单元。每个存储使能端可以但不限于连接了多个存储单元,每个存储使能端连接的多个存储单元可以但不限于包括一个主用存储单元以及多个备用存储单元,可以但不限于将n个存储使能链路中的存储地址传输至目标输入端所对应的目标存储单元,使得目标存储单元被使能。

208.可选地,在本实施例中,上述每个存储使能端可以但不限于有其对应的主用存储单元,每个存储使能端的主用存储单元可以但不限于是预先确定的,比如:在需要对存储模块中的存储单元进行使能的情况下,可以但不限于将存储单元中首个空闲的存储单元确定为主用存储单元。

209.可选地,在本实施例中,可以但不限于根据存储模块中存储单元的数量以及与存储单元连接的存储使能链路的数量确定存储单元中包括的主用存储单元的数量和备用存储单元的数量,比如:以存储地址传输电路包括n个存储使能链路,存储模块包括m个存储单元为例,n个存储使能链路可以但不限于与存储模块中的n个主用存储单元连接,备用存储单元的数量为存储模块中包括的全部的存储单元的数量m与存储模块中包括的主用存储单元的数量n的差值(m-n)。

210.在一个可选的实施方式中,在所述通过所述n个存储使能链路中所述目标输入端对应的目标存储使能链路将所述存储地址传输至所述目标输入端所对应的目标存储单元之前,可以但不限于包括以下方法:在所述内建自我测试阶段根据测试结果生成控制信号;向所述存储地址传输电路中的每条存储链路发送所述控制信号,其中,所述控制信号用于连通所述n个存储使能链路,并断开除所述n个存储使能链路之外的其他存储链路。

211.可选地,在本实施例中,每个存储使能端可以但不限于连接了多个存储单元,可以但不限于将存储使能端与与其连接的每个存储单元之间的连接链路确定为一条存储链路,每个存储使能端可以但不限于有多条存储链路,每个存储使能端的存储链路的个数可以但不限于是根据与存储使能端连接的存储单元的个数确定的,比如:在存储使能端连接了p个备用存储单元,1个主用存储单元的情况下,可以但不限于将p 1确定为存储使能端的存储链路的个数。

212.可选地,在本实施例中,可以但不限于将用于传输用于使能存储单元的使能信号的存储链路确定为存储使能链路。对于一个存储使能端可以但不限于具有一个存储使能链路使得使能存储单元的使能信号能够到达目标存储单元。

213.可选地,在本实施例中,可以但不限于在内建自我测试阶段通过存储地址传输电路中的连接控制电路生成控制信号。内建自我测试阶段可以但不限于用于测试存储模块中每个存储单元的使能情况,可以但不限于根据内建自我测试阶段得到的对每个存储单元的测试结果确定内建自我修复阶段生成的控制信号。

214.可选地,在本实施例中,可以但不限于根据控制信号从存储地址传输电路中每条存储链路中选择存储使能链路,可以但不限于通过存储使能链路传输信号。可以但不限于通过控制信号连通n个存储使能链路并断开除n个存储使能链路之外的其他存储链路。

215.在一个可选的实施方式中,可以但不限于采用以下方式在所述内建自我测试阶段根据测试结果生成控制信号:在所述内建自我测试阶段获取错误存储地址作为所述测试结

果;根据所述错误存储地址生成所述控制信号。

216.可选地,在本实施例中,内建自我测试阶段可以但不限于通过检测存储模块中每个存储单元的输入与输出情况,确定每个存储单元的使能情况。可以但不限于根据存储模块中每个存储单元的输入与输出确定测试结果,比如:在存储单元的输入与输出相同的情况下,可以但不限于将测试结果确定为存储单元正常工作;在存储单元的输入与输出不同的情况下,可以但不限于将测试结果确定为存储单元异常工作,并根据异常存储单元的地址生成控制信号。

217.可选地,在本实施例中,上述控制信号可以但不限于用将异常存储单元的使能信号传输至用于替代异常存储单元工作的备用存储单元,从而使得电路保持正常工作。

218.存储单元在一个可选的实施方式中,可以但不限于采用以下方式在所述内建自我测试阶段获取错误存储地址作为所述测试结果:对所述存储模块中的每个存储单元执行内建自我测试;将未内建自我测试的存储单元的目标存储地址确定为所述错误存储地址。

219.可选地,在本实施例中,可以但不限于通过向每个存储单元输入数据,检测每个存储单元的输入数据实现对每个存储单元的内建自我测试。

220.可选地,在本实施例中,可以但不限于根据每个存储单元输入数据与输入数据,确定每个存储单元是否为错误存储地址,比如:在存储单元的输入数据与输入数据不同的情况下,确定存储单元的目标存储地址是错误存储地址。

221.在一个示例性实施例中,提供了一种存储地址传输电路的工作过程的示例,图21是根据本技术实施例的一种存储地址传输电路的工作过程的示意图一,如图21所示,以存储模块包括ram0、ram1、ram2、ram3、ram4、ram5以及ram6,r=2层的交换器数组包括s=10个一对二交换器组件(t=2),地址译码器包括4个存储使能端(sram0_en、sram1_en、sram2_en、sram3_en)为例,存储地址传输电路可以但不限于通过以下方式工作:

222.对于存储地址传输电路包括r层的交换器数组,可以但不限于根据公式计算存储地址传输电路中能容纳的备用存储单元的个数。以交换器数组包括两层为例,存储地址传输电路最多能够修正:2

r-1=3个有错误的存储单元(ram4、ram5和ram6)。

223.可以但不限于通过一对t交换器组件的选择线控制sram_en使能的目标存储单元。可以但不限于根据发生错误的存储单元的个数确定一对t交换器组件的选择线,以交换器数组包括一对二交换器组件,发生错误的存储单元的为ram2为例,在bist and bisr mode时,bisr模块可以但不限于控制交换器数组通过以下链路将sram_en输出至对应的ram,具体如下:

224.发生错误的存储单元的为ram2,可以但不限于将ram2对应错误地址缓存far2设定为1,根据公式确定 ,再根据公式,得到如表1所示交换器数组第0层中每个一对二交换器组件的选择线:

225.表1

[0226][0227]

由表1可知,交换器数组第0层中一对二交换器组件sw0-0的选择线为0;

[0228]

交换器数组第0层中一对二交换器组件sw0-1的选择线为0;

[0229]

交换器数组第0层中一对二交换器组件sw0-2的选择线为1;

[0230]

交换器数组第0层中一对二交换器组件sw0-3的选择线为1;

[0231]

交换器数组第0层中一对二交换器组件sw0-4的选择线为0;

[0232]

交换器数组第0层中一对二交换器组件sw0-5的选择线为0。

[0233]

可以但不限于根据公式确定 ,根据公式得到如表2所示交换器数组第1层中每个一对二交换器组件的选择线:

[0234]

表2

[0235][0236]

由表2可知,交换器数组第1层中一对二交换器组件sw1-0的选择线为1;

[0237]

交换器数组第1层中一对二交换器组件sw1-1的选择线为1;

[0238]

交换器数组第1层中一对二交换器组件sw1-2的选择线为1;

[0239]

交换器数组第1层中一对二交换器组件sw1-3的选择线为1。

[0240]

综上所述,每个sram_en的存储使能链路为:

[0241]

sram0_en经过一对二交换器组件sw1-0,到达一对二交换器组件sw0-0将ram0使能。

[0242]

sram1_en经过一对二交换器组件sw1-1,到达一对二交换器组件sw0-1将ram1使能。

[0243]

sram2_en经过一对二交换器组件sw1-2,到达一对二交换器组件sw0-2将ram3使能。

[0244]

sram3_en经过一对二交换器组件sw1-3,到达一对二交换器组件sw0-2将sram4使

能。

[0245]

在一个示例性实施例中,提供了一种存储地址传输电路的工作过程的示例,图22是根据本技术实施例的一种存储地址传输电路的工作过程的示意图二,如图22所示,以存储模块包括ram0、ram1、ram2、ram3、ram4、ram5以及ram6,r=2层的交换器数组包括s=10个一对二交换器组件(t=2),地址译码器包括4个存储使能端(sram0_en、sram1_en、sram2_en、sram3_en)为例,存储地址传输电路可以但不限于通过以下方式工作:

[0246]

以交换器数组包括一对二交换器组件,发生错误的存储单元的为ram1和ram2为例,在bist and bisr mode时,bisr模块可以但不限于控制交换器数组通过以下链路将sram_en输出至对应的ram,具体如下:

[0247]

发生错误的存储单元的为ram1和ram2,可以但不限于将ram1和ram2对应错误地址缓存far1和far2设定为1,每个sram_en的存储使能链路为:

[0248]

sram0_en经过一对二交换器组件sw1-0,到达一对二交换器组件sw0-0将ram0使能。

[0249]

sram1_en经过一对二交换器组件sw1-1,到达一对二交换器组件sw0-3将ram3使能。

[0250]

sram2_en经过一对二交换器组件sw1-2,到达一对二交换器组件sw0-4将ram4使能。

[0251]

sram3_en经过一对二交换器组件sw1-3,到达一对二交换器组件sw0-5将sram5使能。

[0252]

在一个示例性实施例中,提供了一种存储地址传输电路的工作过程的示例,图23是根据本技术实施例的一种存储地址传输电路的工作过程的示意图三,如图23所示,以存储模块包括ram0、ram1、ram2、ram3、ram4、ram5以及ram6,r=2层的交换器数组包括s=10个一对二交换器组件(t=2),地址译码器包括4个存储使能端(sram0_en、sram1_en、sram2_en、sram3_en)为例,存储地址传输电路可以但不限于通过以下方式工作:

[0253]

以交换器数组包括一对二交换器组件,发生错误的存储单元的为ram1、ram2和ram3为例,在bist and bisr mode时,bisr模块可以但不限于控制交换器数组通过以下链路将sram_en输出至对应的ram,具体如下:

[0254]

发生错误的存储单元的为ram1、ram2和ram3,可以但不限于将ram1、ram2和ram3对应错误地址缓存far1、far2和far3设定为1,每个sram_en的存储使能链路为:

[0255]

sram0_en经过一对二交换器组件sw1-0,到达一对二交换器组件sw0-0将ram1使能。

[0256]

sram1_en经过一对二交换器组件sw1-1,到达一对二交换器组件sw0-2将ram4使能。

[0257]

sram2_en经过一对二交换器组件sw1-2,到达一对二交换器组件sw0-4将ram5使能。

[0258]

sram3_en经过一对二交换器组件sw1-3,到达一对二交换器组件sw0-5将sram6使能。

[0259]

通过以上的实施方式的描述,本领域的技术人员可以清楚地了解到根据上述实施例的方法可借助软件加必需的通用硬件平台的方式来实现,当然也可以通过硬件,但很多

情况下前者是更佳的实施方式。基于这样的理解,本技术的技术方案本质上或者说对现有技术做出贡献的部分可以以软件产品的形式体现出来,该计算机软件产品存储在一个存储介质(如rom/ram、磁碟、光盘)中,包括若干指令用以使得一台终端设备(可以是手机,计算机,服务器,或者网络设备等)执行本技术各个实施例所述的方法。

[0260]

在本实施例中还提供了一种存储地址传输装置,应用于存储地址传输电路,所述存储地址传输电路包括n个存储使能链路,该装置用于实现上述实施例及优选实施方式,已经进行过说明的不再赘述。如以下所使用的,术语“模块”可以实现预定功能的软件和/或硬件的组合。尽管以下实施例所描述的装置较佳地以软件来实现,但是硬件,或者软件和硬件的组合的实现也是可能并被构想的。

[0261]

图24是根据本技术实施例的存储地址传输装置的结构框图,如图2所示,该装置包括:

[0262]

接收模块2402,用于通过目标输入端接收存储地址,其中,所述n个存储使能链路的n个输入端用于与地址译码器的n个存储使能端连接,所述地址译码器还具有地址输入端,所述地址输入端用于获取所述存储地址,所述n个输入端包括所述目标输入端;

[0263]

传输模块2404,用于通过所述n个存储使能链路中所述目标输入端对应的目标存储使能链路将所述存储地址传输至所述目标输入端所对应的目标存储单元,其中,每个存储使能链路用于将所述n个存储使能端中的一个存储使能端连接至存储模块所包括的m个存储单元中的一个所述目标存储单元上,所述目标存储单元是处于正常工作状态的存储单元,所述n个存储使能链路是在所述存储模块的内建自我测试阶段形成的,n和m均为大于1的正整数,n小于m。

[0264]

通过上述装置,使用包括输入端与地址译码器的n个存储使能端连接的n个存储使能链路的存储地址传输电路,地址译码器还有用于接收存储地址的地址输入端;每个存储使能链路用于将在存储模块的内建自我测试阶段形成的n个存储使能端中的一个存储使能端连接至存储模块所包括的m个存储单元中的一个处于正常工作状态的目标存储单元上,n和m均为大于1的正整数,n小于m。由于在电路的内建自我测试阶段就形成了将每个存储使能端连接至对应的处于正常工作状态的目标存储单元上的工作过程,使得电路在工作模式下存储地址传输的过程不会经过地址比较器等附加的逻辑器件,缩短了链路长度,因此可以解决存储地址的传输效率较低问题,达到提高了存储地址的传输效率的效果。

[0265]

在一个示例性实施例中,所述存储地址传输装置,还包括:

[0266]

生成模块,用于在所述内建自我测试阶段根据测试结果生成控制信号;

[0267]

发送模块,用于向所述存储地址传输电路中的每条存储链路发送所述控制信号,其中,所述控制信号用于连通所述n个存储使能链路,并断开除所述n个存储使能链路之外的其他存储链路。

[0268]

在一个示例性实施例中,所述生成模块,包括:

[0269]

获取单元,用于在所述内建自我测试阶段获取错误存储地址作为所述测试结果;

[0270]

生成单元,用于根据所述错误存储地址生成所述控制信号。

[0271]

在一个示例性实施例中,所述获取单元,用于:对所述存储模块中的每个存储单元执行内建自我测试;将未内建自我测试的存储单元的目标存储地址确定为所述错误存储地址。

[0272]

需要说明的是,上述各个模块是可以通过软件或硬件来实现的,对于后者,可以通过以下方式实现,但不限于此:上述模块均位于同一处理器中;或者,上述各个模块以任意组合的形式分别位于不同的处理器中。

[0273]

本技术的实施例还提供了一种计算机可读存储介质,该计算机可读存储介质中存储有计算机程序,其中,该计算机程序被设置为运行时执行上述任一项方法实施例中的步骤。

[0274]

在一个示例性实施例中,上述计算机可读存储介质可以包括但不限于:u盘、只读存储器(read-only memory,简称为rom)、随机存取存储器(random access memory,简称为ram)、移动硬盘、磁碟或者光盘等各种可以存储计算机程序的介质。

[0275]

本技术的实施例还提供了一种电子设备,包括存储器和处理器,该存储器中存储有计算机程序,该处理器被设置为运行计算机程序以执行上述任一项方法实施例中的步骤。

[0276]

在一个示例性实施例中,上述电子设备还可以包括传输设备以及输入输出设备,其中,该传输设备和上述处理器连接,该输入输出设备和上述处理器连接。

[0277]

本实施例中的具体示例可以参考上述实施例及示例性实施方式中所描述的示例,本实施例在此不再赘述。

[0278]

显然,本领域的技术人员应该明白,上述的本技术的各模块或各步骤可以用通用的计算装置来实现,它们可以集中在单个的计算装置上,或者分布在多个计算装置所组成的网络上,它们可以用计算装置可执行的程序代码来实现,从而,可以将它们存储在存储装置中由计算装置来执行,并且在某些情况下,可以以不同于此处的顺序执行所示出或描述的步骤,或者将它们分别制作成各个集成电路模块,或者将它们中的多个模块或步骤制作成单个集成电路模块来实现。这样,本技术不限制于任何特定的硬件和软件结合。

[0279]

以上所述仅为本技术的优选实施例而已,并不用于限制本技术,对于本领域的技术人员来说,本技术可以有各种更改和变化。凡在本技术的原则之内,所作的任何修改、等同替换、改进等,均应包含在本技术的保护范围之内。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。