1.本实用新型涉及一种半导体元件,特别是一种包括互连结构及对准结构的半导体元件。

背景技术:

2.微影工艺(photolithography)是制造半导体元件的重要步骤,其利用曝光和显影将光掩模上的设计图案转移至光刻胶层,然后用光刻胶层为蚀刻遮罩对其下方的材料层进行蚀刻,从而将设计图案再往下转移至材料层中,制造出一层电路结构。

3.半导体制造工艺即由重复进行沉积、微影和蚀刻工艺,逐层架构出半导体元件的积体电路结构。随着电路图案设计越来越细致紧密,上下层电路结构之间的对准(alignment)规范也越来越严苛,因为稍微的对准偏移即可能导致接触异常、短路或断线等缺陷。在一些情况下,还需在叠层结构中另制作零层标记(zero mark)以协助对准。

技术实现要素:

4.本实用新型目的在于提供一种半导体元件,在省略了零层标记的前提下,可提高上层和下层互连结构之间的对准精确度。相较于传统工艺需要制作零层标记(zero mark)以协助对准,本实用新型省略了此步骤不仅可节省零层标记的光罩花费,还具有较简化的制程。

5.本实用新型实施例提供了一种半导体元件,包括衬底,第一介质层位于所述衬底上,第一互连结构及对准结构位于所述第一介质层中,第二介质层位于所述第一介质层上并覆盖所述对准结构的顶面,以及第二互连结构位于所述第二介质层中并直接接触所述第一互连结构的顶面。所述对准结构的所述顶面低于所述第一互连结构的顶面。

6.本实用新型又一实施例提供了一种半导体元件,包括衬底,第一介质层位于所述衬底上,第一互连结构及对准结构位于所述第一介质层中;第二介质层位于所述第一介质层上并覆盖所述对准结构的顶面,以及第二互连结构位于所述第二介质层中且底面直接接触所述第一互连结构的顶面。所述对准结构的所述顶面低于所述第二互连结构的所述底面。

附图说明

7.所附图示提供对于本实用新型实施例更深入的了解,并纳入此说明书成为其中一部分。这些图示与描述,用来说明一些实施例的原理。需注意的是所有图示均为示意图,以说明和制图方便为目的,相对尺寸及比例都经过调整。相同的符号在不同的实施例中代表相对应或类似的特征。

8.图1至图12所绘示为根据本实用新型一实施例的半导体元件的制造方法的过程中的步骤所涉及到的结构示意图。

9.其中,附图标记说明如下:

10.r1

ꢀꢀꢀꢀꢀꢀꢀꢀꢀ

电路区

11.r2

ꢀꢀꢀꢀꢀꢀꢀꢀꢀ

对准标记区

12.10

ꢀꢀꢀꢀꢀꢀꢀꢀꢀ

衬底

13.12

ꢀꢀꢀꢀꢀꢀꢀꢀꢀ

层间介质层

14.14

ꢀꢀꢀꢀꢀꢀꢀꢀꢀ

导电结构

15.16

ꢀꢀꢀꢀꢀꢀꢀꢀꢀ

蚀刻停止层

16.18

ꢀꢀꢀꢀꢀꢀꢀꢀꢀ

第一介质层

17.22

ꢀꢀꢀꢀꢀꢀꢀꢀꢀ

互连开口

18.26

ꢀꢀꢀꢀꢀꢀꢀꢀꢀ

第一互连结构

19.32

ꢀꢀꢀꢀꢀꢀꢀꢀꢀ

第一光刻胶层

20.34

ꢀꢀꢀꢀꢀꢀꢀꢀꢀ

盖层

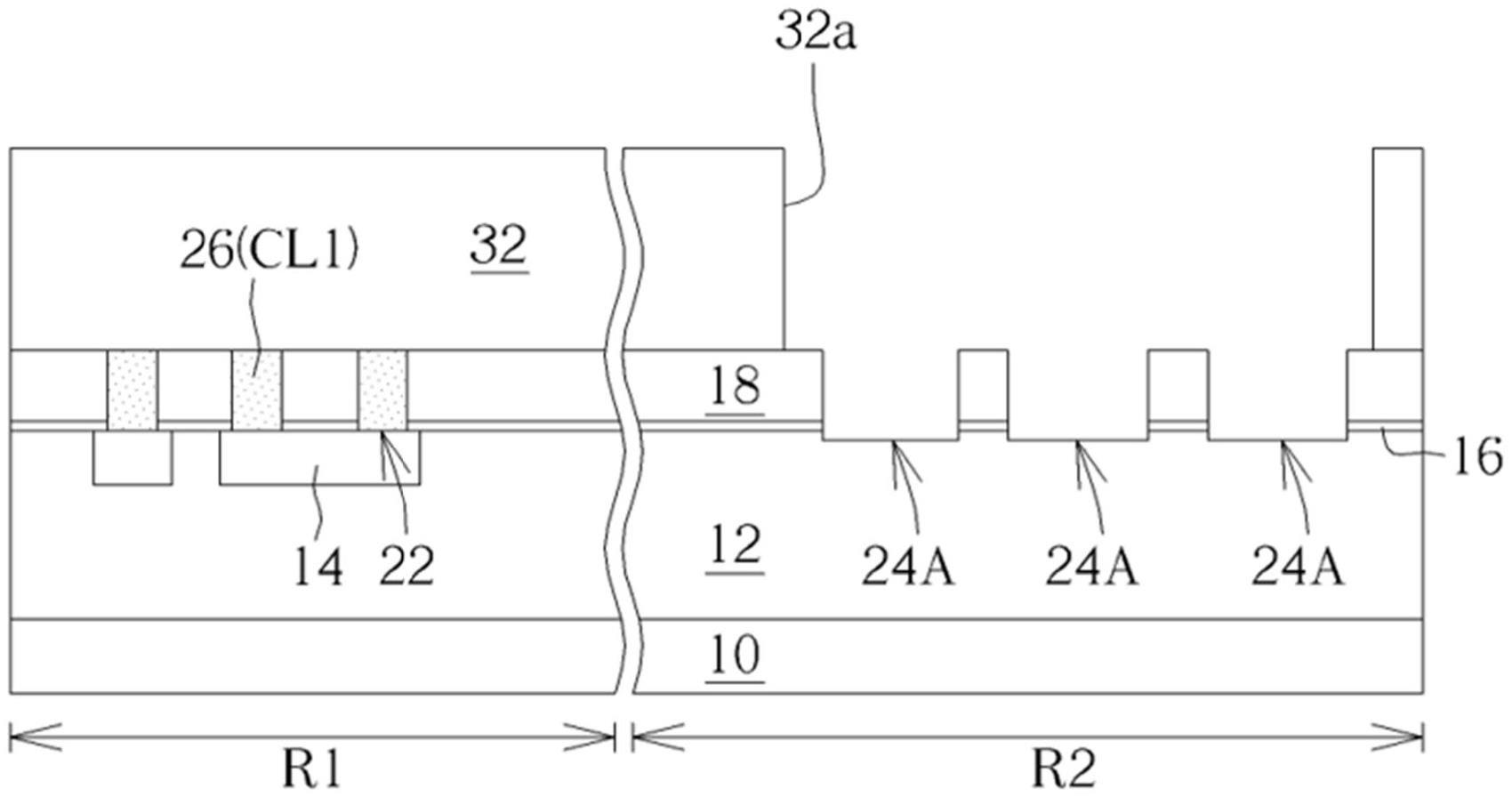

21.36

ꢀꢀꢀꢀꢀꢀꢀꢀꢀ

第二光刻胶层

22.38

ꢀꢀꢀꢀꢀꢀꢀꢀꢀ

平坦化层

23.40

ꢀꢀꢀꢀꢀꢀꢀꢀꢀ

抗反射层

24.42

ꢀꢀꢀꢀꢀꢀꢀꢀꢀ

第三光刻胶层

25.44

ꢀꢀꢀꢀꢀꢀꢀꢀꢀ

第二互连结构

26.18a

ꢀꢀꢀꢀꢀꢀꢀꢀ

顶面

27.18b

ꢀꢀꢀꢀꢀꢀꢀꢀ

顶面

28.18c

ꢀꢀꢀꢀꢀꢀꢀꢀ

顶面

29.18d

ꢀꢀꢀꢀꢀꢀꢀꢀ

顶面

30.24a

ꢀꢀꢀꢀꢀꢀꢀꢀ

第一对准沟槽

31.24b

ꢀꢀꢀꢀꢀꢀꢀꢀ

第二对准沟槽

32.32a

ꢀꢀꢀꢀꢀꢀꢀꢀ

第一标记开口

33.36a

ꢀꢀꢀꢀꢀꢀꢀꢀ

第二标记开口

34.a1

ꢀꢀꢀꢀꢀꢀꢀꢀꢀ

第一对准结构

35.a2

ꢀꢀꢀꢀꢀꢀꢀꢀꢀ

第二对准结构

36.a2a

ꢀꢀꢀꢀꢀꢀꢀꢀ

下部

37.a2b

ꢀꢀꢀꢀꢀꢀꢀꢀ

上部

38.cl1

ꢀꢀꢀꢀꢀꢀꢀꢀ

第一导电层

39.cl2

ꢀꢀꢀꢀꢀꢀꢀꢀ

第二导电层

40.s1

ꢀꢀꢀꢀꢀꢀꢀꢀꢀ

阶梯差

41.s2

ꢀꢀꢀꢀꢀꢀꢀꢀꢀ

阶梯差

42.s3

ꢀꢀꢀꢀꢀꢀꢀꢀꢀ

阶梯差

具体实施方式

43.为使熟悉本实用新型所属技术领域的一般技术者能进一步了解本实用新型,下文特列举本实用新型的数个优选实施例,并配合所附的图示,详细说明本实用新型的技术方案以及所欲达成的功效。本实用新型所属领域的技术人员能在不脱离本实用新型的精神下,参考以下所举实施例,而将数个不同实施例中的特征进行替换、重组、混合以完成其他

实施例。

44.本揭露中的多张图式只绘出显示装置的一部分,图中各元件的数量及尺寸仅作为示意,并非用来限制本揭露的范围。文中所描述对于图形中相对元件之上下关系,在本领域之人皆应能理解其系指物件之相对位置而言,因此皆可以翻转而呈现相同之构件,此皆应同属本说明书所揭露之范围。

45.图1至图12所绘示为根据本实用新型一实施例的半导体元件的制造方法的过程中的步骤所涉及到的结构示意图。请参考图1,首先提供一衬底10,包括一电路区r1以及一对准标记区r2。接着,于衬底10上形成一层间介质层12,然后于层间介质层12上形成一蚀刻停止层16以及一第一介质层18。

46.如图1所示,衬底10例如是硅(si)衬底、磊晶硅(epi-si)衬底、硅锗(sige)衬底、碳化硅(sic)衬底或硅覆绝缘(silicon-on-insulator,soi)衬底,但不限于此。衬底10可以是已经完成部分半导体制程的衬底,包括已制作于其中或其上的结构物和电路元件(图未示)。层间介质层12、蚀刻停止层16和第一介质层18均可以是由电介质材料构成,适用的电介质材料例如包括氧化硅(sio2)、氮化硅(sin)、氮氧化硅(sion)、氮碳化硅(sicn)、氮掺杂碳化硅(ndc)、低介电常数(low-k)电介质材料例如氟硅玻璃(fluorinated silica glass,fsg)、碳硅氧化物(sicoh)、旋涂硅玻璃(spin-on glass)、多孔性低介电常数电介质材料(porous low-k dielectric material)、有机高分子电介质材料,或者上述材料之组合,但不限于此。

47.根据本实用新型一实施例,请参考图1所示,层间介质层12和第一介质层18主要包括氧化硅(sio2),蚀刻停止层16则包括不同于层间介质层12和第一介质层18的材料,例如氮化硅(sin)。根据本实用新型一些实施例,电路区r1的层间介质层12中可设有导电结构14,其中导电结构14主要是由导电材料构成,适用的导电材料例如包括铝(al)、钛(ti)、钽(ta)、钨(w)、铌(nb)、钼(mo)、铜(cu)、氮化钛(tin)、碳化钛(tic)、氮化钽(tan)、钛钨(ti/w)、钛与氮化钛(ti/tin)、多晶硅(poly silicon)、掺杂硅(doped silicon)、硅化物(silicide)等金属或非金属导电材料或其任何组合,但不限于此。导电结构14的顶面大致上与层间介质层12的上表面齐平,并且与蚀刻停止层16直接接触。

48.请参考图2。接着,进行一微影暨蚀刻工艺,以在电路区r1的第一介质层18中形成多个互连开口22,同时在对准标记区r2的第一介质层18中形成多个第一对准沟槽24a。根据本实用新型一些实施例,微影暨蚀刻工艺包括利用光刻设备(例如扫描光刻机或步进光刻机)将一光掩模(photomask)上的互连开口22和第一对准沟槽24a的设计图案转移至设置在该第一介质层18上的一光刻胶层(图未示)中,接着再以光刻胶层作为蚀刻遮罩来蚀刻移除第一介质层18被显露出来的部分,从而将互连开口22和第一对准沟槽24a的设计图案再往下转移至第一介质层18中。根据本实用新型一些实施例,光刻设备是利用形成在衬底10中或者形成在层间介质层12中的一对准结构(图未示)作为对准标记(alignment mark)来对准光掩模和衬底10,以使互连开口22和第一对准沟槽24a形成在预计的位置。根据本实用新型一些实施例,互连开口22的底部贯穿蚀刻停止层16,大致上停止在导电结构14上,显露出部分导电结构14。第一对准沟槽24a的底部贯穿蚀刻停止层16并且再往下延伸至层间介质层12的上部中,因而第一对准沟槽24a的底部低于互连开口22的底部。

49.请参考图3,接着形成一第一导电层cl1,全面性地覆盖第一介质层18并且填满互

连开口22和第一对准沟槽24a。第一导电层cl1主要包括金属材料,例如钨(w)、铜(cu)、铝(al)、钛(ti)、钽(ta)等金属,或前述金属材料之化合物、合金,及/或复合层,但不限于此。

50.请参考图4,接着可进行回蚀刻工艺或化学机械抛光(cmp)工艺,移除位于互连开口22和第一对准沟槽24a之外的多余的第一导电层cl1,从而获得位于互连开口22中的第一互连结构26以及位于第一对准沟槽24a中的第一对准结构a1。如图4所示,第一对准结构a1的顶面和第一互连结构26的顶面大致上互相齐平,第一对准结构a1的底面低于第一互连结构26的底面。

51.请参考图4至图6,接着,进行第一微影暨蚀刻工艺,移除第一对准结构a1,显露出第一对准沟槽24a。具体地,第一微影暨蚀刻工艺包括先在第一介质层18上形成第一光刻胶层32,然后使用光刻设备(例如扫描光刻机或步进光刻机)将一光掩模(图未示)上的标记开口图案转移至第一光刻胶层32中,形成第一标记开口32a以显露出第一对准结构a1。接着,再用第一光刻胶层32作为蚀刻遮罩,通过第一标记开口32a蚀刻移除第一对准结构a1,显露出第一对准沟槽24a。根据本实用新型一些实施例,第一微影暨蚀刻工艺是使用第一对准结构a1作为对准标记来对准光掩模和衬底10,以使第一标记开口32a形成在预计的位置。

52.请参考图7。移除第一光刻胶层32后,接着形成一第二导电层cl2,全面性地覆盖第一介质层18和第一互连结构26并填入第一对准沟槽24a,形成第二对准结构a2。第二导电层cl2主要包括金属材料,例如钨(w)、铜(cu)、铝(al)、钛(ti)、钽(ta)等金属,或前述金属材料之化合物、合金,及/或复合层,但不限于此。根据本实用新型一些实施例,第一导电层cl1与第二导电层cl2可包括选自前述群组的相同材料,例如钨(w)。根据本实用新型另一些实施例,第一导电层cl1与第二导电层cl2可包括选自前述群组的不同材料,例如第一导电层cl1主要包括钛(ti),第二导电层cl2主要包括钨(w)。如图7所示,第二对准结构a2可区分成填充在第一对准沟槽24a内的下部a2a,以及位于第一对准沟槽24a以外的上部a2b,其中上部a2b具有对应于第一对准沟槽24a的轮廓的第二对准沟槽24b。根据本实用新型一些实施例,可再形成一盖层34,共型地覆盖第二导电层cl2和第二对准沟槽24b。盖层34可包括电介质材料,例如氧化硅(sio2)。

53.请参考图8和图9。接着进行第二微影暨蚀刻工艺,移除第二对准结构a2的上部a2b以及部分第一介质层18,显露出位于第一对准沟槽24a中的下部a2a。具体地,第二微影暨蚀刻工艺包括先在盖层34上形成第二光刻胶层36,然后使用光刻设备(例如扫描光刻机或步进光刻机)将一光掩模(图未示)上的标记开口图案转移至第二光刻胶层36中,形成第二标记开口36a以显露出第二对准结构a2。接着,再用第二光刻胶层36作为蚀刻遮罩,通过第二标记开口36a蚀刻显露出来的盖层34、第二导电层cl2和第一介质层18。根据本实用新型一些实施例,第二微影暨蚀刻工艺是使用第二对准结构a2的第二对准沟槽24b作为对准标记来对准光掩模和衬底10,以使第二标记开口36a形成在预计的位置。根据本实用新型一实施例,图5至图6的第一微影暨蚀刻工艺和图8至图9的第二微影暨蚀刻工艺使用同一个光掩模。第二对准结构a2的下部a2a的顶面可齐平或略低于自第二标记开口36a中显露出来的第一介质层18的顶面18b,并且都低于未被蚀刻、仍被第二导电层cl2覆盖住的第一介质层18的顶面18a。根据本实用新型一实施例,第一介质层18的顶面18a和顶面18b之间包括阶梯差s1。

54.请参考图10和图11。移除剩余的第二光刻胶层36(在图9中示出)后,接着形成一平

坦化层38全面性地覆盖电路区r1和对准标记区r2,然后进行第三微影暨蚀刻工艺,移除第二导电层cl2多余的部分,获得第二互连结构44。具体地,第三微影暨蚀刻工艺包括先在平坦化层38上形成第三光刻胶层42,然后使用光刻设备(例如扫描光刻机或步进光刻机)将一光掩模(图未示)上的互连结构图案转移至第三光刻胶层42中,接着再用第三光刻胶层42作为蚀刻遮罩,蚀刻显露出来的平坦化层38、盖层34和部分第二导电层cl2,从而将剩余的第二导电层cl2图案化成第二互连结构44。根据本实用新型一些实施例,第三微影暨蚀刻工艺是使用第二对准结构a2(在图8中示出)的下部a2a作为对准标记来对准光掩模和衬底10,其中下部a2a和第一介质层18之间明显的边界轮廓使光刻设备较容易对准光掩模和衬底10,获得较佳的对准精确度,使第二互连结构44较准确地形成在预计的位置。平坦化层38可包括电介质材料,例如有机高分子电介质材料。可选择性地在平坦化层38和第三光刻胶层42之间设置一抗反射层40,例如一氮化硅(sin)层或一氮氧化硅(sion)层。

55.如图11所示,为了确保各第二互连结构44之间无残留的第二导电层cl2,以避免各第二互连结构44之间短接,蚀刻第二导电层cl2的步骤可包括对第一介质层18进行过蚀刻,因此电路区r1上位于第二互连结构44附近被过蚀刻而显露出来的第一介质层18的顶面18c会低于被第二互连结构44覆盖住的第一介质层18的顶面18a。对准标记区r2上的第一介质层18的顶面18b(在图9中示出)也会再被过蚀刻至更低的顶面18d,且顶面18d低于顶面18c。根据本实用新型一实施例,顶面18c和顶面18d之间的阶梯差s3,大于顶面18a和顶面18c之间的阶梯差s2。根据本实用新型一实施例,由于材料的蚀刻选择比不同,在第三微影暨蚀刻工艺后,第二对准结构a2的下部a2a的顶面可略高于第一介质层18的顶面18d,但仍然低于第一介质层18的顶面18c。根据本实用新型一实施例,第三微影暨蚀刻工艺后,第二对准结构a2的下部a2a的顶面与顶面18d之间的阶梯差小于第二对准结构a2的下部a2a的顶面与顶面18c之间的阶梯差。

56.请参考图11和图12。接着,移除剩余的第三光刻胶层42、抗反射层40和平坦化层38,然后形成第二介质层46,第二介质层46全面性地覆盖第一介质层18、第二互连结构44(以及其上的盖层34)和第二对准结构a2的下部a2a,并填满第二互连结构44之间的间隙。然后,进行回蚀刻工艺或化学机械抛光(cmp)工艺,移除第二互连结构44上的第二介质层46和盖层34直到显露出第二互连结构44的顶面,获得本实用新型之半导体元件。第二介质层46是由电介质材料构成,适用的电介质材料例如包括氧化硅(sio2)、氮化硅(sin)、氮氧化硅(sion)、氮碳化硅(sicn)、氮掺杂碳化硅(ndc)、低介电常数(low-k)电介质材料例如氟硅玻璃(fluorinated silica glass,fsg)、碳硅氧化物(sicoh)、旋涂硅玻璃(spin-on glass)、多孔性低介电常数电介质材料(porous low-k dielectric material)、有机高分子电介质材料,或者上述材料之组合,但不限于此。根据本实用新型一实施例,第二介质层46主要包括氧化硅(sio2)。

57.如图12所示,本实用新型提供之半导体元件,包括衬底10、设置在衬底10上的层间介质层12、设置在层间介质层12上的第一介质层18、设置在第一介质层18中的第一互连结构26及对准结构(即第二对准结构a2的下部a2a)、设置在第一介质层18上并直接覆盖对准结构(即第二对准结构a2的下部a2a)的顶面的第二介质层46,以及设置在第二介质层46中的第二互连结构44。第一互连结构26的顶面与第二互连结构44的底面直接接触并电连接。对准结构(即第二对准结构a2的下部a2a)的顶面和底面则分别被第二介质层46和层间介质

层12完全包覆,未与其他电路结构直接接触或电连接。也就是说对准结构(即第二对准结构a2的下部a2a)为电性浮置(electrical floating)。具体地,对准结构(即第二对准结构a2的下部a2a)的顶面低于第一互连结构26的顶面和第二互连结构44的底面,对准结构(即第二对准结构a2的下部a2a)的底面则低于第一互连结构26的底面。

58.参考图12,第二互连结构44和对准结构(即第二对准结构a2的下部a2a)是由相同一层金属材料(即第二导电层cl2)制造而成,具有相同材质,并且与第一互连结构26的材质(即第一导电层cl1)可相同或不同。

59.在一些实施例中,参考图12,第二互连结构44和对准结构(即第二对准结构a2的下部a2a)包括相同材料,例如分别可选自由钨(w)、铜(cu)、铝(al)、钛(ti)、钽(ta)等金属,或前述金属材料之化合物、合金,及/或复合层所构成的群组。

60.在一些实施例中,参考图12,第二互连结构44和对准结构(即第二对准结构a2的下部a2a)包括不同材料,例如分别可选自由钨(w)、铜(cu)、铝(al)、钛(ti)、钽(ta)等金属,或前述金属材料之化合物、合金,及/或复合层所构成的群组。

61.在一些实施例中,参考图12,半导体元件还包括设置在衬底10以及第一介质层18之间的层间介质层12、设置在层间介质层12中的导电结构14,以及设置在层间介质层12和第一介质层18之间的蚀刻停止层16。蚀刻停止层16直接接触导电结构14的顶面。第一互连结构26的底部贯穿蚀刻停止层16,与导电结构14直接接触。

62.在一些实施例中,参考图12,对准结构(即第二对准结构a2的下部a2a)贯穿蚀刻停止层16并延伸至层间介质层12的上部。对准结构(即第二对准结构a2的下部a2a)的底面低于第一互连结构26的底面。

63.在一些实施例中,参考图12,第一介质层18包括与第二互连结构44的底面直接接触的顶面18a(第一顶面)、邻近第二互连结构44并且与第二介质层46的底面直接接触的顶面18c(第二顶面),以及邻近对准结构(即第二对准结构a2的下部a2a)并且与第二介质层46的底面直接接触的顶面18d(第三顶面),其中顶面18d低于对准结构(即第二对准结构a2的下部a2a)的顶面,对准结构(即第二对准结构a2的下部a2a)的顶面低于顶面18c,顶面18c再低于顶面18a。

64.在一些实施例中,参考图11,顶面18c和顶面18d之间的阶梯差s3大于顶面18a和顶面18c之间的阶梯差s2。

65.综合以上,参考图12,本实用新型利用填充在第一对准沟槽24a中的第二导电层cl2(在图10中示出)所形成的对准结构(即第二对准结构a2的下部a2a)作为对准标记来图案化第二导电层cl2,形成第二互连结构44,如此可在没有零层标记的前提下,提高第一互连结构26和第二互连结构44之间的对准精确度。

66.以上所述仅为本实用新型的优选实施例而已,并不用于限制本实用新型,对于本领域的技术人员来说,本实用新型可以有各种更改和变化。凡在本实用新型的精神和原则之内,所作的任何修改、等同替换、改进等,均应包含在本实用新型的保护范围之内。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。