技术特征:

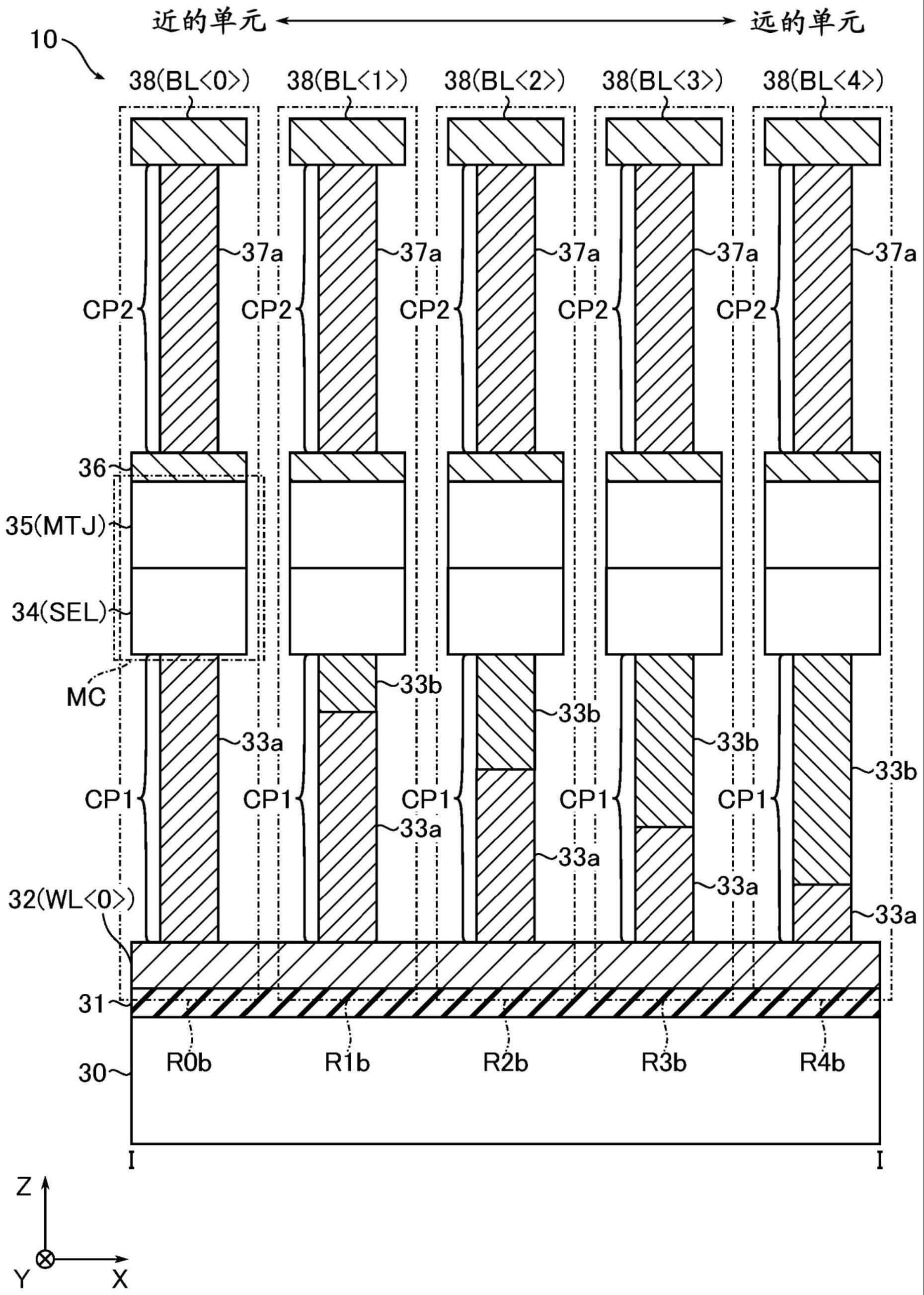

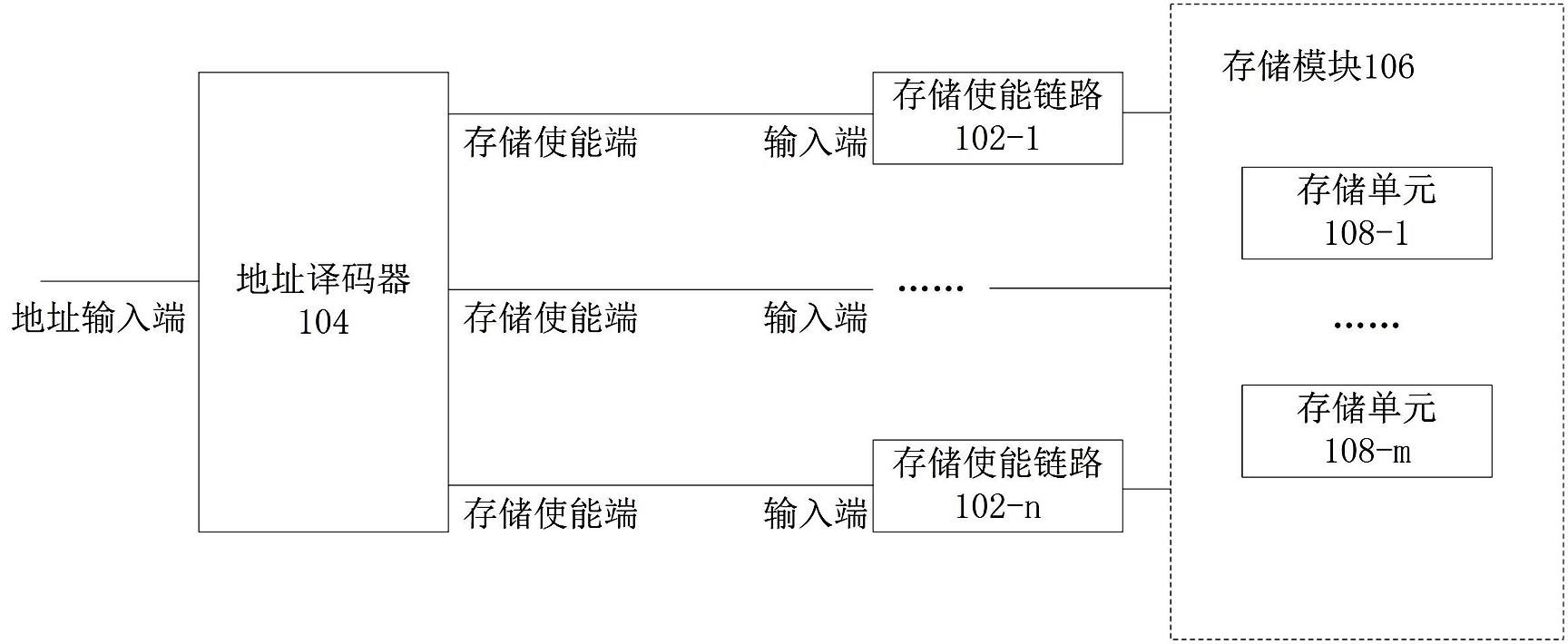

1.一种存储装置,具备:第1存储单元;第2存储单元;第1电路,其向所述第1存储单元和所述第2存储单元供给写入电流;第1布线,其连接于所述第1电路;第1插塞,其将所述第1存储单元和所述第1布线电连接;以及第2插塞,其将所述第2存储单元和所述第1布线电连接,从所述第1电路到所述第1插塞为止的所述第1布线的长度比从所述第1电路到所述第2插塞为止的所述第1布线的长度短,所述第1插塞的电阻值比所述第2插塞的电阻值高。2.根据权利要求1所述的存储装置,所述第1插塞包括第1导电体和第2导电体,所述第2插塞包括第3导电体和第4导电体,所述第2导电体的电阻率比所述第1导电体的电阻率低,所述第4导电体的电阻率比所述第3导电体的电阻率低,所述第1插塞所包括的所述第2导电体的比率比所述第2插塞所包括的所述第4导电体的比率低。3.根据权利要求2所述的存储装置,所述第1导电体和所述第3导电体包含钨、氮化钨、钛、氮化钛、碳和多晶硅中的至少一种,所述第2导电体和所述第4导电体包含铜和铝中的至少一种。4.根据权利要求2所述的存储装置,所述第1导电体和所述第3导电体包含碳和多晶硅中的至少一种,所述第2导电体和所述第4导电体包含钨、氮化钨、钛和氮化钛中的至少一种。5.根据权利要求2所述的存储装置,所述第1导电体和所述第3导电体包含第1半导体,所述第2导电体和所述第4导电体包含第2半导体,所述第1半导体的杂质浓度比所述第2半导体的杂质浓度低。6.根据权利要求2所述的存储装置,所述第2导电体设置在所述第1导电体上,所述第4导电体设置在所述第3导电体上。7.根据权利要求1所述的存储装置,所述第1插塞包含第1半导体,所述第2插塞包含第2半导体,所述第1半导体的杂质浓度比所述第2半导体的杂质浓度低。8.根据权利要求1所述的存储装置,所述第1插塞与所述第1布线接触的面积比所述第2插塞与所述第1布线接触的面积小。9.根据权利要求8所述的存储装置,所述第1插塞和所述第2插塞的截面形状为圆形。

10.根据权利要求9所述的存储装置,所述第1插塞的直径比所述第2插塞的直径小。11.根据权利要求1所述的存储装置,所述第1存储单元和所述第2存储单元配置在所述第1布线的上方。12.根据权利要求1所述的存储装置,所述第1布线配置在所述第1存储单元和所述第2存储单元的上方。13.根据权利要求1所述的存储装置,还具备:第3存储单元;第4存储单元;第3插塞,其将所述第3存储单元和所述第1布线电连接;以及第4插塞,其将所述第4存储单元和所述第1布线电连接,从所述第1电路到所述第3插塞为止的所述第1布线的长度比从所述第1电路到所述第1插塞为止的所述第1布线的长度长、并且比从所述第1电路到所述第2插塞为止的所述第1布线的长度短,从所述第1电路到所述第4插塞为止的所述第1布线的长度比从所述第1电路到所述第2插塞为止的所述第1布线的长度长,所述第3插塞的电阻值与所述第1插塞的电阻值相等,所述第4插塞的电阻值与所述第2插塞的电阻值相等。14.根据权利要求13所述的存储装置,所述第1插塞包括第1导电体和第2导电体,所述第2插塞包括第3导电体和第4导电体,所述第3插塞包括第5导电体和第6导电体,所述第4插塞包括第7导电体和第8导电体,所述第2导电体的电阻率比所述第1导电体的电阻率低,所述第4导电体的电阻率比所述第3导电体的电阻率低,所述第1插塞所包括的所述第2导电体的比率比所述第2插塞所包括的所述第4导电体的比率低,所述第5导电体的电阻率与所述第1导电体的电阻率相等,所述第6导电体的电阻率与所述第2导电体的电阻率相等,所述第7导电体的电阻率与所述第3导电体的电阻率相等,所述第8导电体的电阻率与所述第4导电体的电阻率相等,所述第3插塞所包括的所述第6导电体的比率与所述第1插塞所包括的所述第2导电体的比率相等,所述第4插塞所包括的所述第8导电体的比率与所述第2插塞所包括的所述第4导电体的比率相等。15.根据权利要求13所述的存储装置,所述第1插塞与所述第1布线接触的面积比所述第2插塞与所述第1布线接触的面积小,所述第3插塞与所述第1布线接触的面积、和所述第1插塞与所述第1布线接触的面积相等,

所述第4插塞与所述第1布线接触的面积、和所述第2插塞与所述第1布线接触的面积相等。16.根据权利要求1所述的存储装置,还具备:第5存储单元;第6存储单元;第2电路,其向所述第5存储单元和所述第6存储单元供给写入电流;第2布线,其连接于所述第2电路;第5插塞,其将所述第5存储单元和所述第2布线电连接;以及第6插塞,其将所述第6存储单元和所述第2布线电连接,从所述第2电路到所述第5插塞为止的所述第2布线的长度比从所述第2电路到所述第6插塞为止的所述第2布线的长度短,所述第5插塞的电阻值比所述第6插塞的电阻值高。17.根据权利要求16所述的存储装置,所述第2布线配置在所述第5存储单元和所述第6存储单元的上方。18.根据权利要求16所述的存储装置,所述第5存储单元和所述第6存储单元配置在所述第2布线的上方。19.根据权利要求1所述的存储装置,所述第1存储单元和所述第2存储单元包括可变电阻元件。20.根据权利要求19所述的存储装置,所述可变电阻元件为磁阻效应元件。

技术总结

实施方式提供能够减少误读出的存储装置。实施方式的存储装置具备:第1存储单元;第2存储单元;第1电路,其向第1存储单元和第2存储单元供给写入电流;第1布线,其连接于第1电路;第1插塞,其将第1存储单元和第1布线电连接;以及第2插塞,其将第2存储单元和第1布线电连接。从第1电路到第1插塞为止的第1布线的长度比从第1电路到第2插塞为止的第1布线的长度短。第1插塞的电阻值比第2插塞的电阻值高。塞的电阻值比第2插塞的电阻值高。塞的电阻值比第2插塞的电阻值高。

技术研发人员:杉浦邦晃 五十岚太一

受保护的技术使用者:铠侠股份有限公司

技术研发日:2023.02.27

技术公布日:2023/9/18

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。