1.本发明构思涉及三维半导体存储器件和包括该三维半导体存储器件的电子系统,具体地,涉及包括垂直沟道结构的非易失性三维半导体存储器件、制造该非易失性三维半导体存储器件的方法和包括该非易失性三维半导体存储器件的电子系统。

背景技术:

2.能够存储大量数据的半导体器件作为电子系统的数据存储器是理想的。半导体器件的越来越高的集成度可以为消费者提供增大的数据存储容量、提高的性能和降低的价格。在二维或平面半导体器件的情况下,由于它们的集成主要由单位存储单元所占据的面积决定,所以集成受到精细图案形成技术水平的极大影响。然而,增加图案精细度所需的极其昂贵的工艺设备对增加二维或平面半导体器件的集成度设置了实际限制。因此,包括三维排列的存储单元的三维半导体存储器件已经在开发中。

技术实现要素:

3.本发明构思的一示例实施方式提供了一种具有改善的电特性和提高的可靠性的三维半导体存储器件及其制造方法。

4.本发明构思的一示例实施方式提供了一种包括三维半导体存储器件的电子系统。

5.根据本发明构思的一示例实施方式,一种三维半导体存储器件包括:堆叠结构,包括顺序堆叠在衬底上的接地选择线、第一字线、第二字线和串选择线;垂直沟道结构,穿透堆叠结构并被排列以形成多列;下分离结构,在第一方向上与堆叠结构的下部交叉,并沿与第一方向相交的第二方向划分接地选择线;以及第一上分离结构和第二上分离结构,在第一方向上与堆叠结构的上部交叉,并沿第二方向划分串选择线,其中下分离结构和第一上分离结构与垂直沟道结构的所述列之一垂直重叠,以及第二上分离结构提供在垂直沟道结构之间。

6.根据本发明构思的一示例实施方式,一种三维半导体存储器件包括:第一衬底,包括第一区域和在第一方向上邻近第一区域的第二区域;外围电路结构,包括设置在第一衬底上的外围电路晶体管;第二衬底,设置在外围电路结构上;堆叠结构,包括顺序堆叠在第二衬底上的接地选择线、第一字线、第二字线和串选择线,并在第二区域上具有阶梯结构;垂直沟道结构,穿透堆叠结构并被排列以形成多列;字线分离结构,覆盖堆叠结构的相反侧表面并在第一方向上延伸;下分离结构,在第一方向上与堆叠结构的下部交叉,并沿与第一方向交叉的第二方向划分接地选择线;第一上分离结构和第二上分离结构,在第一方向上与堆叠结构的上部交叉,并沿第二方向划分串选择线;接触插塞,穿透堆叠结构的阶梯结构,并分别电连接到第一字线和第二字线;位线,分别电连接到垂直沟道结构;以及导电线,分别电连接到接触插塞,其中下分离结构和第一上分离结构与垂直沟道结构的所述列之一垂直重叠,以及从平面图看,第二上分离结构具有不平坦的侧表面,并且在第二方向上与垂直沟道结构间隔开。

7.根据本发明构思的一示例实施方式,一种电子系统包括:三维半导体存储器件;以及控制器,电连接到三维半导体存储器件并被配置为控制三维半导体存储器件,其中三维半导体存储器件包括:衬底,具有第一区域和在第一方向上邻近第一区域的第二区域;堆叠结构,包括顺序堆叠在衬底上的接地选择线、第一字线、第二字线和串选择线,并在第二区域上具有阶梯结构;垂直沟道结构,穿透堆叠结构并被排列以形成多列;下分离结构,在第一方向上与堆叠结构的下部交叉,并沿与第一方向相交的第二方向划分接地选择线;第一上分离结构和第二上分离结构,在第一方向上与堆叠结构的上部交叉,并沿第二方向划分串选择线;绝缘层,覆盖堆叠结构的阶梯结构;接触插塞,穿透堆叠结构和绝缘层;以及输入/输出焊盘,连接到接触插塞之一,其中控制器通过输入/输出焊盘电连接到三维半导体存储器件,其中下分离结构和第一上分离结构与垂直沟道结构的所述列之一垂直重叠,其中第二上分离结构提供在垂直沟道结构的所述列中的两列之间。

附图说明

8.图1是示出根据本发明构思的一示例实施方式的包括三维半导体存储器件的电子系统的示意图。

9.图2是示意性示出根据本发明构思的一示例实施方式的包括三维半导体存储器件的电子系统的透视图。

10.图3和图4是截面图,其分别沿图2的线i-i'和ii-ii'截取以示出根据本发明构思的一示例实施方式的包括三维半导体存储器件的半导体封装。

11.图5a和图5b是根据本发明构思的一示例实施方式的三维半导体存储器件的平面图。

12.图6a和图6b是截面图,其分别沿图5a或图5b的线i-i'和ii-ii'截取以示出根据本发明构思的一示例实施方式的三维半导体存储器件的一部分。

13.图7是根据本发明构思的一示例实施方式的三维半导体存储器件的一部分(例如,图6a的“a”)的放大截面图。

14.图8a和图8b是示出根据本发明构思的一示例实施方式的三维半导体存储器件的平面图。

15.图9a、图10a和图11a是截面图,其各自沿图5a或图5b的线i-i'截取以示出根据本发明构思的一示例实施方式的制造三维半导体存储器件的方法。

16.图9b、图10b、图11b和图12是截面图,其各自沿图5a或图5b的ii-ii'线截取以示出根据本发明构思的一示例实施方式的制造三维半导体存储器件的方法。

具体实施方式

17.现在将参照附图更全面地描述本发明构思的示例实施方式。

18.图1是示出根据本发明构思的一示例实施方式的包括三维半导体存储器件的电子系统的示意图。

19.参照图1,电子系统1000可以包括三维半导体存储器件1100和电连接到三维半导体存储器件1100的控制器1200。电子系统1000可以是包括一个或更多个三维半导体存储器件1100的存储器装置,或者可以是包括例如存储器装置的电子设备。例如,电子系统1000可

以是在其中提供至少一个三维半导体存储器件1100的固态驱动器(ssd)装置、通用串行总线(usb)、计算系统、医疗系统或通信系统。

20.三维半导体存储器件1100可以是非易失性存储器件(例如,将在下面描述的三维nand快闪存储器件)。三维半导体存储器件1100可以包括第一区域1100f和设置在第一区域1100f上的第二区域1100s。在本发明构思的一示例实施方式中,第一区域1100f可以与第二区域1100s相邻地设置。第一区域1100f可以是外围电路区域,其包括解码器电路1110、页缓冲器1120和逻辑电路1130。第二区域1100s可以是存储单元区域,其包括位线bl、公共源极线csl、字线wl、第一线ll1和ll2、第二线ul1和ul2以及在位线bl和公共源极线csl之间的存储单元串cstr。

21.在第二区域1100s中,每个存储单元串cstr可以包括与公共源极线csl相邻的第一晶体管lt1和lt2、与位线bl相邻的第二晶体管ut1和ut2、以及设置在第一晶体管lt1和lt2与第二晶体管ut1和ut2之间的多个存储单元晶体管mct。根据本发明构思的一示例实施方式,第一晶体管lt1和lt2的数量以及第二晶体管ut1和ut2的数量可以被各种各样地改变。

22.在本发明构思的一示例实施方式中,第一晶体管lt1和lt2可以包括例如接地选择晶体管,第二晶体管ut1和ut2可以包括例如串选择晶体管。第一线ll1和ll2可以分别用作第一晶体管lt1和lt2的栅电极。字线wl可以用作存储单元晶体管mct的栅电极。第二线ul1和ul2可以分别用作第二晶体管ut1和ut2的栅电极。

23.在本发明构思的一示例实施方式中,第一晶体管lt1和lt2可以包括例如彼此串联连接的第一擦除控制晶体管lt1和接地选择晶体管lt2。第二晶体管ut1和ut2可以包括例如彼此串联连接的串选择晶体管ut1和第二擦除控制晶体管ut2。第一擦除控制晶体管lt1和第二擦除控制晶体管ut2中的至少一个可以用于使用栅极诱导漏极泄漏(gidl)现象擦除存储在存储单元晶体管mct中的数据的擦除操作。

24.公共源极线csl、第一线ll1和ll2、字线wl以及第二线ul1和ul2可以通过从第一区域1100f延伸至第二区域1100s的第一互连线1115电连接到解码器电路1110。位线bl可以通过从第一区域1100f延伸到第二区域1100s的第二互连线1125电连接到页缓冲器1120。

25.在第一区域1100f中,解码器电路1110和页缓冲器1120可以配置为执行控制操作,该控制操作对选自存储单元晶体管mct的至少一个存储单元晶体管执行。解码器电路1110和页缓冲器1120可以由逻辑电路1130控制。三维半导体存储器件1100可以通过电连接到逻辑电路1130的输入/输出焊盘1101与控制器1200通信。输入/输出焊盘1101可以通过从第一区域1100f延伸到第二区域1100s的输入/输出互连线1135电连接到逻辑电路1130。

26.控制器1200可以包括处理器1210、nand控制器1220和主机接口1230。例如,电子系统1000可以包括多个三维半导体存储器件1100,在这种情况下,控制器1200可以控制所述多个三维半导体存储器件1100。

27.处理器1210可以控制包括控制器1200的电子系统1000的整体操作。基于特定的固件,处理器1210可以执行控制nand控制器1220和访问三维半导体存储器件1100的操作。nand控制器1220可以包括nand接口1221,其用于与三维半导体存储器件1100通信。nand接口1221可以用于发送和接收用于控制三维半导体存储器件1100的控制命令、将被写入三维半导体存储器件1100的存储单元晶体管mct或从其读取的数据等。主机接口1230可以被配置为允许电子系统1000和外部主机之间的通信。如果通过主机接口1230从外部主机提供控

制命令,则处理器1210可以控制三维半导体存储器件1100。

28.图2是示意性示出根据本发明构思的一示例实施方式的包括三维半导体存储器件的电子系统的透视图。

29.参照图2,电子系统2000可以包括主衬底2001以及安装在主衬底2001上的控制器2002、至少一个半导体封装2003和dram 2004。半导体封装2003和dram 2004可以通过提供在主衬底2001中的互连图案2005连接到控制器2002并彼此连接。

30.主衬底2001可以包括连接器2006,该连接器2006包括多个联接至外部主机的引脚。在连接器2006中,引脚的数量和布置可以根据电子系统2000和外部主机之间的通信接口而变化。在本发明构思的一示例实施方式中,电子系统2000可以根据诸如通用串行总线(usb)、快速外围组件互连(pci-express)、串行高级技术附件(sata)、通用闪存(ufs)m-phy等的接口与外部主机通信。在本发明构思的一示例实施方式中,电子系统2000可以由通过连接器2006从外部主机供应的电力驱动。电子系统2000可以进一步包括电力管理集成电路(pmic),其用于将从外部主机提供的电力单独供应给控制器2002和半导体封装2003。

31.控制器2002可以被配置为控制半导体封装2003上的写入或读取操作并提高电子系统2000的操作速度。

32.dram 2004可以是缓冲存储器,其被配置为减轻由用作数据存储器装置的半导体封装2003与外部主机之间的速度差异所引起的技术困难。在本发明构思的一示例实施方式中,电子系统2000中的dram 2004可以用作高速缓冲存储器,并且可以用作存储空间,该存储空间用于在控制操作期间临时在半导体封装2003上存储数据。在电子系统2000包括dram 2004的情况下,除了用于控制半导体封装2003的nand控制器之外,控制器2002可以进一步包括用于控制dram 2004的dram控制器。

33.半导体封装2003可以包括彼此间隔开的第一半导体封装2003a和第二半导体封装2003b。第一半导体封装2003a和第二半导体封装2003b中的每个可以是包括多个半导体芯片2200的半导体封装。第一半导体封装2003a和第二半导体封装2003b中的每个可以包括封装衬底2100、在封装衬底2100上的半导体芯片2200、分别设置在半导体芯片2200的底表面上的粘合层2300、将半导体芯片2200电连接到封装衬底2100的连接结构2400、以及设置在封装衬底2100上以覆盖半导体芯片2200和连接结构2400的模层2500。

34.封装衬底2100可以是包括封装上焊盘2130的印刷电路板。每个半导体芯片2200可以包括输入/输出焊盘2210。每个输入/输出焊盘2210可以对应于图1的输入/输出焊盘1101。每个半导体芯片2200可以包括栅极堆叠结构3210和垂直沟道结构3220。每个半导体芯片2200可以包括将在下面描述的三维半导体存储器件。

35.在本发明构思的一示例实施方式中,连接结构2400可以是将输入/输出焊盘2210电连接到封装上焊盘2130的接合线。在第一半导体封装2003a和第二半导体封装2003b的每个中,半导体芯片2200可以通过接合线彼此电连接,并且可以电连接到封装衬底2100的封装上焊盘2130。在本发明构思的一示例实施方式中,第一半导体封装2003a和第二半导体封装2003b的每个中的半导体芯片2200可以通过贯通硅通路(tsv)而不是通过以接合线形式提供的连接结构2400彼此电连接。

36.在本发明构思的一示例实施方式中,控制器2002和半导体芯片2200可以包括在单个封装中。例如,控制器2002和半导体芯片2200可以安装在独立于主衬底2001制备的中介

衬底上,并且可以通过提供在中介衬底中的互连线彼此连接。

37.图3和图4是截面图,其分别沿图2的线i-i'和ii-ii'截取以示出包括根据本发明构思的一示例实施方式的三维半导体存储器件的半导体封装。

38.参照图3和图4,半导体封装2003可以包括封装衬底2100、在封装衬底2100上的多个半导体芯片2200、以及覆盖封装衬底2100和半导体芯片2200的模层2500。

39.封装衬底2100可以包括封装衬底主体部分2120、封装上焊盘2130、下焊盘2125和内部线2135。封装上焊盘2130可以设置在封装衬底主体部分2120的顶表面上。下焊盘2125可以设置在封装衬底主体部分2120的底表面上或者通过该底表面暴露,并且内部线2135可以提供在封装衬底主体部分2120中以将上焊盘2130电连接到下焊盘2125。上焊盘2130可以电连接到连接结构2400。下焊盘2125可以通过导电连接部分2800连接到图2的电子系统2000的主衬底2001的互连图案2005。

40.每个半导体芯片2200可以包括半导体衬底3010以及顺序堆叠在半导体衬底3010上的第一结构3100和第二结构3200。第一结构3100可以包括在其中提供外围线3110的外围电路区域。第二结构3200可以包括公共源极线3205、栅极堆叠结构3210、垂直沟道结构3220、分离结构3230、位线3240、栅极互连线3235和导电线3250。栅极堆叠结构3210可以设置在公共源极线3205上。垂直沟道结构3220和分离结构3230可以穿透栅极堆叠结构3210。位线3240可以电连接到垂直沟道结构3220。栅极互连线3235可以电连接到栅极堆叠结构3210的字线(例如,图1的wl)。每条栅极互连线3235可以电连接到字线wl中的相应一条。栅极互连线3235中的至少一条可以电连接到公共源极线3205。

41.每个半导体芯片2200可以包括穿透线3245,该穿透线3245电连接到第一结构3100的外围线3110并从第一结构3100延伸到第二结构3200中。穿透线3245可以提供为穿透栅极堆叠结构3210,并且在本发明构思的一示例实施方式中,穿透线3245可以设置在栅极堆叠结构3210的外部。每个半导体芯片2200可以包括从第一结构3100延伸到第二结构3200中并且电连接到第一结构3100的外围线3110的输入/输出互连线3265以及电连接到输入/输出互连线3265的输入/输出焊盘2210。

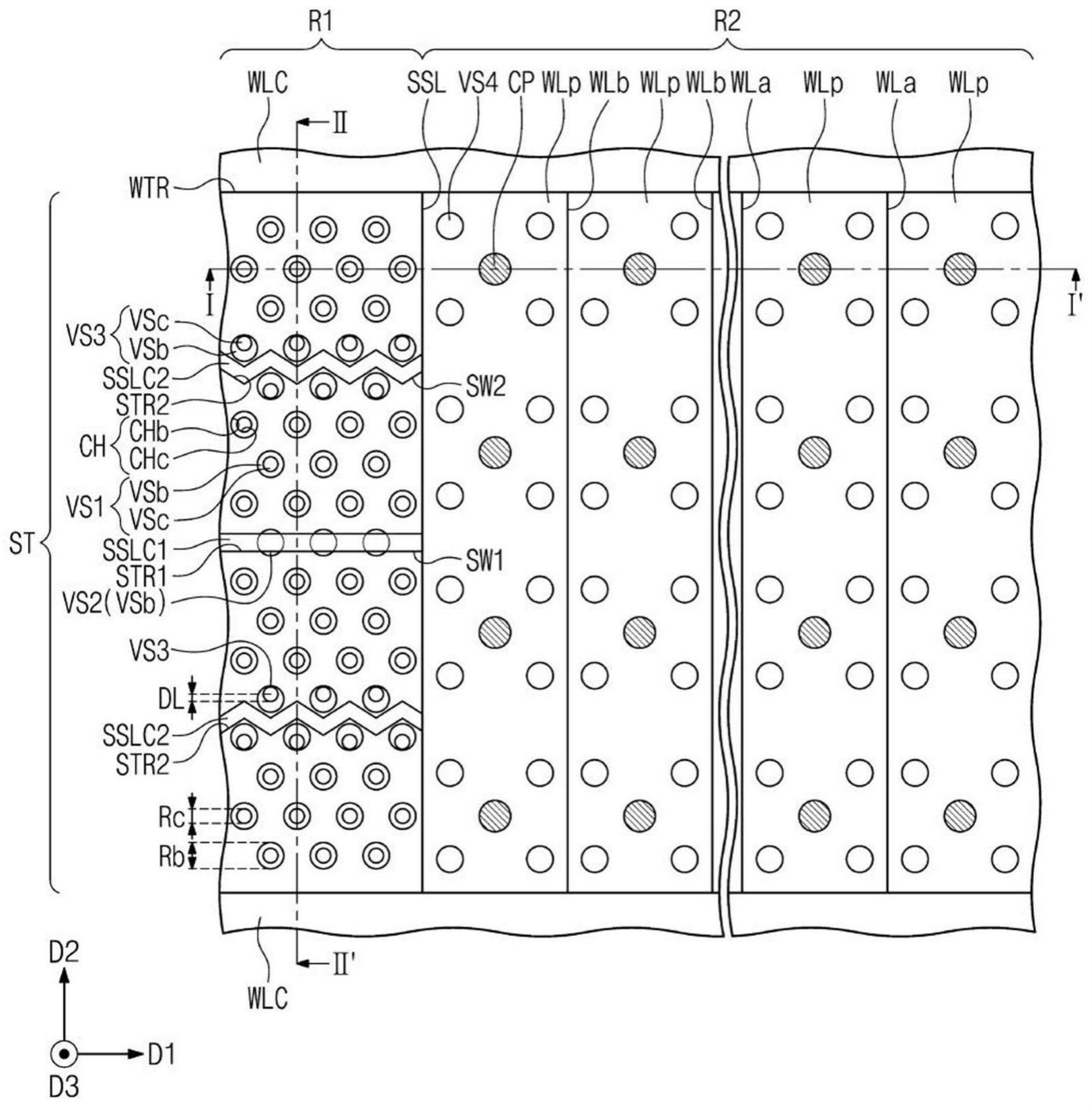

42.图5a和图5b是示出根据本发明构思的一示例实施方式的三维半导体存储器件的平面图。例如,图5b可以是不同于图5a的层的顶表面的平面图。图6a和图6b是截面图,其分别沿图5a或图5b的线i-i'和ii-ii'截取以示出根据本发明构思的一示例实施方式的三维半导体存储器件的一部分。

43.参照图5a、图5b、图6a和图6b,可以提供包括第一区域r1和第二区域r2的第一衬底10。第一衬底10可以在从第一区域r1朝向第二区域r2取向的第一方向d1上和在与第一方向d1交叉的第二方向d2上延伸。第一衬底10的顶表面可以面向基本上垂直于第一方向d1和第二方向d2的第三方向d3。例如,第一、第二和第三方向d1、d2和d3可以彼此正交。

44.第二区域r2和第一区域r1可以沿第一方向d1排列。第一区域r1可以是在其中提供参照图3和图4描述的垂直沟道结构3220、分离结构3230和位线3240的区域。第二区域r2可以是在其中提供包括将在下面描述的焊盘部分wlp的阶梯结构的区域。

45.在本发明构思的一示例实施方式中,第一衬底10可以是例如硅衬底、硅锗衬底、锗衬底或包括单晶硅衬底及从其生长的单晶外延层的结构。器件隔离层11可以提供在第一衬底10中。器件隔离层11可以提供为形成第一衬底10的有源区。器件隔离层11可以由例如硅

氧化物形成或者包括例如硅氧化物。

46.外围电路结构ps可以提供在第一衬底10上。外围电路结构ps可以包括外围电路晶体管ptr、外围电路接触插塞31、外围电路互连线33和第一绝缘层30。外围电路晶体管ptr可以设置在第一衬底10的有源区上,外围电路互连线33可以通过外围电路接触插塞31电连接到外围电路晶体管ptr。第一绝缘层30可以包围它们。外围电路结构ps可以对应于图1的第一区域1100f,外围电路互连线33可以对应于图3和图4的外围线3110。

47.外围电路晶体管ptr、外围电路接触插塞31和外围电路互连线33可以构成外围电路。例如,外围电路晶体管ptr可以构成图1的解码器电路1110、页缓冲器1120和逻辑电路1130。例如,每个外围电路晶体管ptr可以包括外围栅极绝缘层21、外围栅电极23、外围盖图案25、外围栅极间隔物27和外围源极/漏极区29。

48.外围栅极绝缘层21可以提供在外围栅电极23和第一衬底10之间。外围盖图案25可以提供在外围栅电极23上。外围栅极间隔物27可以提供在外围栅极绝缘层21、外围栅电极23和外围盖图案25的侧表面上。外围源极/漏极区29可以提供在第一衬底10的部分中且在外围栅电极23的相反侧。

49.外围电路互连线33可以通过外围电路接触插塞31电连接到外围电路晶体管ptr。例如,外围电路接触插塞31连接到外围电路晶体管ptr。每个外围电路晶体管ptr可以是nmos晶体管或pmos晶体管,并且在本发明构思的一示例实施方式中,它可以是栅极全环绕型晶体管。例如,随着距第一衬底10的距离增加,外围电路接触插塞31的宽度可以增加。外围电路接触插塞31和外围电路互连线33可以由导电材料和金属材料中的至少一种形成,或者可以包括导电材料和金属材料中的至少一种。

50.第一绝缘层30可以提供在第一衬底10的顶表面上。第一绝缘层30可以覆盖外围电路晶体管ptr、外围电路接触插塞31和外围电路互连线33。第一绝缘层30可以是包括多个绝缘层的多层结构。例如,第一绝缘层30可以由硅氧化物、硅氮化物、硅氮氧化物和低k电介质材料中的至少一种形成,或者包括硅氧化物、硅氮化物、硅氮氧化物和低k电介质材料中的至少一种。

51.单元阵列结构cs可以提供在外围电路结构ps上,在本发明构思的一示例实施方式中,单元阵列结构cs可以包括第二衬底100、堆叠结构st、下分离结构gslc、第一上分离结构sslc1和第二上分离结构sslc2、字线分离结构wlc、第一至第四垂直沟道结构vs1、vs2、vs3和vs4以及接触插塞cp。在下文,将更详细地描述单元阵列结构cs。

52.第二衬底100可以提供在第一区域r1和第二区域r2上以及第一绝缘层30上。第二衬底100可以在第一方向d1和第二方向d2上延伸。第二衬底100可以是包括半导体材料的半导体衬底。第二衬底100可以由例如硅(si)、锗(ge)、硅锗(sige)、镓砷化物(gaas)、铟镓砷化物(ingaas)和铝镓砷化物(algaas)中的至少一种形成,或者包括例如硅(si)、锗(ge)、硅锗(sige)、镓砷化物(gaas)、铟镓砷化物(ingaas)和铝镓砷化物(algaas)中的至少一种。

53.堆叠结构st可以提供在第二衬底100上。堆叠结构st可以从第一区域r1向第二区域r2和/或在第一方向d1上延伸。堆叠结构st可以对应于图3和图4的堆叠结构3210。

54.可以提供多个堆叠结构st,且在本发明构思的一示例实施方式中,堆叠结构st可以沿第二方向d2排列。当在平面图中观察时,字线分离结构wlc可以提供在字线分离沟槽wtr中,该字线分离沟槽wtr提供在堆叠结构st之间以在第一方向d1上与堆叠结构st交叉。

字线分离结构wlc可以从第一区域r1延伸到第二区域r2。字线分离结构wlc可以提供在堆叠结构st之一的相反侧表面上。堆叠结构st可以在第二方向d2上彼此间隔开,其中字线分离结构wlc之一插置在其间。每个字线分离结构wlc在第三方向d3上的长度可以大于第一上分离结构sslc1和第二上分离结构sslc2中的每个在第三方向d3上的长度。每个字线分离结构wlc在第二方向d2上的宽度可以大于第一上分离结构sslc1和第二上分离结构sslc2中的每个在第二方向d2上的宽度。字线分离结构wlc可以由例如硅氧化物、硅氮化物和硅氮氧化物中的至少一种形成,或者包括例如硅氧化物、硅氮化物和硅氮氧化物中的至少一种。在下文,为了描述方便,下面将描述堆叠结构st之一,但是剩余的堆叠结构st也可以具有与下面描述的那些基本相同或相同的特征。

55.堆叠结构st可以包括堆叠在第二衬底100上的层间电介质层ilda、ildb和ildc、以及提供在层间电介质层ilda、ildb和ildc之间的接地选择线gsl、字线wla和wlb以及串选择线ssl。字线wla和wlb可以对应于图1的字线wl。接地选择线gsl可以对应于图1的第一线ll1和ll2,串选择线ssl可以对应于图1的第二线ul1和ul2。

56.例如,堆叠结构st可以包括在第二衬底100上的第一堆叠结构sta、在第一堆叠结构sta上的第二堆叠结构stb和在第二堆叠结构stb上的第三堆叠结构stc。第一堆叠结构sta可以包括交替且重复地堆叠在第二衬底100上的第一层间电介质层ilda和第一字线wla(或接地选择线gsl)。第二堆叠结构stb可以包括交替并重复堆叠在第一堆叠结构sta上的第二层间电介质层ildb和第二字线wlb。第三堆叠结构stc可以包括交替并重复堆叠在第二堆叠结构stb上的第三层间电介质层ildc和串选择线ssl。

57.随着在第三方向d3上距第二衬底100的距离增加,第一字线wla和第二字线wlb可以在第一方向d1上具有减小的长度。换句话说,第一字线wla和第二字线wlb中的每条在第一方向d1上的长度可以大于其上的另一条字线在第一方向d1上的长度。在第一字线wla和第二字线wlb中,第一堆叠结构sta的第一字线wla中最下面的一条可以在第一方向d1上具有最大长度,第二堆叠结构stb的第二字线wlb中最上面的一条可以在第一方向d1上具有最小长度。第二堆叠结构stb的第二字线wlb中最上面的一条在第一方向d1上的长度可以大于串选择线ssl在第一方向d1上的长度。

58.参照图5a和图6a,第一字线wla和第二字线wlb可以在第二区域r2上具有焊盘部分wlp。第一字线wla和第二字线wlb的焊盘部分wlp可以设置在彼此水平和垂直不同的位置处。焊盘部分wlp可以提供为在第一方向d1上形成阶梯结构。

59.由于阶梯结构,当在平面图中观察时,随着距第一至第三垂直沟道结构vs1、vs2和vs3的距离增加,第一堆叠结构sta和第二堆叠结构stb中的每个可以具有减小的厚度,并且第一字线wla和第二字线wlb的侧表面可以在第一方向d1上彼此间隔开特定或预定的距离。例如,第一堆叠结构sta的更靠近第一至第三垂直沟道结构vs1、vs2和vs3的部分可以具有比第一堆叠结构sta的更远离第一至第三垂直沟道结构vs1、vs2和vs3的部分的厚度大的厚度。

60.接地选择线gsl、第一字线wla和第二字线wlb以及串选择线ssl可以由例如掺杂的半导体材料(例如,掺杂的硅等等)、金属材料(例如,钨、铜、铝等等)、导电的金属氮化物(例如,钛氮化物、钽氮化物等等)和过渡金属(例如,钛、钽等等)中的至少一种形成,或者包括例如掺杂的半导体材料(例如,掺杂的硅等等)、金属材料(例如,钨、铜、铝等等)、导电的金

属氮化物(例如,钛氮化物、钽氮化物等等)和过渡金属(例如,钛、钽等等)中的至少一种。

61.第一至第三层间电介质层ilda、ildb和ildc可以提供在接地选择线gsl之间、接地选择线gsl和第一字线wla之间、第一字线wla之间、第一字线wla和第二字线wlb之间、第二字线wlb之间、第二字线wlb和串选择线ssl之间以及串选择线ssl之间。随着距第二衬底100的距离增加,第一层间电介质层ilda和第二层间电介质层ildb可以在第一方向d1上具有减小的长度,类似于第一字线wla和第二字线wlb的长度。

62.第二层间电介质层ildb中的最下面的第二层间电介质层可以设置在第一层间电介质层ilda中的最上面的第一层间电介质层上。例如,第二层间电介质层ildb中的最下面的第二层间电介质层可以与第一层间电介质层ilda中的最上面的第一层间电介质层接触。在本发明构思的一示例实施方式中,第一层间电介质层ilda和第二层间电介质层ildb中的每个的厚度可以小于接地选择线gsl、第一字线wla和第二字线wlb以及串选择线ssl中的每个的厚度。在本说明书中,元件的厚度可以指在第三方向d3上测量的元件的长度。例如,第一层间电介质层ilda中的最下面的第一层间电介质层的厚度可以小于层间电介质层ilda、ildb和ildc中的每个其它层间电介质层的厚度。例如,第三层间电介质层ildc中的最上面的第三层间电介质层的厚度可以大于层间电介质层ilda、ildb和ildc中的每个其它层间电介质层的厚度。然而,第一至第三层间电介质层ilda、ildb和ildc的厚度不限于该示例,并且可以根据半导体器件的技术特性而改变。

63.第一至第三层间电介质层ilda、ildb和ildc可以由例如硅氧化物、硅氮化物、硅氮氧化物和低k电介质材料中的至少一种形成,或者包括例如硅氧化物、硅氮化物、硅氮氧化物和低k电介质材料中的至少一种。例如,第一至第三层间电介质层ilda、ildb和ildc可以由高密度等离子体(hdp)氧化物和原硅酸四乙酯(teos)中的至少一种形成,或者包括高密度等离子体(hdp)氧化物和原硅酸四乙酯(teos)中的至少一种。

64.参照图5b和图6b,下分离结构gslc可以提供在下分离沟槽gtr中,该下分离沟槽gtr形成在第一区域r1上以在第一方向d1上与第一堆叠结构sta的下部交叉。下分离结构gslc可以在第三方向d3上与将在下面描述的第一上分离结构sslc1和第二垂直沟道结构vs2重叠。下分离结构gslc可以在第二方向d2上与字线分离结构wlc间隔开。当在图5b的平面图中观察时,下分离结构gslc可以提供成与堆叠结构st的中心部分或中央部分交叉。下分离结构gslc可以在第二方向d2上与接地选择线gsl重叠,并且可以在第二方向d2上将接地选择线gsl彼此分离。例如,下分离结构gslc的顶表面可以位于接地选择线gsl中的最上面一条的顶表面与第一字线wla中的最下面一条的底表面之间。例如,下分离结构gslc的顶表面可以与接地选择线gsl中的最上面一条的顶表面共面。当在图6b的截面图中观察时,下分离结构gslc可以提供成穿透接地选择线gsl和一些第一层间电介质层ilda。下分离结构gslc可以由例如硅氧化物、硅氮化物和硅氮氧化物中的至少一种形成,或者包括例如硅氧化物、硅氮化物和硅氮氧化物中的至少一种。

65.参照图5a和图6b,第一上分离结构sslc1和第二上分离结构sslc2可以提供在第一上分离沟槽str1和第二上分离沟槽str2中,其形成在第一区域r1上以在第一方向d1上与第三堆叠结构stc交叉。

66.第一上分离沟槽str1中的第一上分离结构sslc1可以在第三方向d3上与下分离结构gslc和第二垂直沟道结构vs2重叠。第一上分离结构sslc1可以在第二方向d2上与字线分

离结构wlc间隔开。当在图5a的平面图中观察时,第一上分离结构sslc1可以提供成与堆叠结构st的中心部分或中央部分交叉。第一上分离结构sslc1可以在第二方向d2上与串选择线ssl重叠,并且可以在第二方向d2上将串选择线ssl彼此分离。第一上分离结构sslc1的底表面可以位于串选择线ssl中的最下面一条的底表面和第二字线wlb中的最上面一条的顶表面之间。例如,第一上分离结构sslc1的底表面可以与第三层间电介质层ildc中的最低的第三层间电介质层ildc的底表面共面。

67.第二上分离沟槽str2中的第二上分离结构sslc2可以提供在字线分离结构wlc和第一上分离结构sslc1之间。例如,第二上分离结构sslc2之一可以提供在每个字线分离结构wlc和第一上分离结构sslc1之间。第二上分离结构sslc2可以与第三垂直沟道结构vs3相邻。在本发明构思的一示例实施方式中,第二上分离结构sslc2可以与第三垂直沟道结构vs3间隔开。例如,第二上分离结构sslc2可以在第二方向d2上与每个第三垂直沟道结构vs3的第三部分vsc间隔开。

68.第二上分离结构sslc2可以在第二方向d2上与字线分离结构wlc和第一上分离结构sslc1间隔开。第二上分离结构sslc2可以在第二方向d2上与串选择线ssl重叠,并且可以在第二方向d2上将串选择线ssl彼此分离。每个第二上分离结构sslc2的底表面可以位于串选择线ssl中的最下面一条的底表面和第二字线wlb中的最上面一条的顶表面之间。例如,第二上分离结构sslc2在第三方向d3上的长度可以与第一上分离结构sslc1在第三方向d3上的长度基本相同。例如,第二上分离结构sslc2的底表面可以与第一上分离结构sslc1的底表面共面。

69.第一上分离结构sslc1的侧表面sw1可以具有平行于第一方向d1的线形状。第一上分离结构sslc1在第二方向d2上的宽度可以在第一方向d1上是恒定的。另外,当在图5a的平面图中观察时,每个第二上分离结构sslc2的侧表面sw2可以是不平坦的表面。例如,每个第二上分离结构sslc2的侧表面sw2可以具有浮雕线形状或锯齿线形状。

70.当在图6b的截面图中观察时,第一上分离结构sslc1和第二上分离结构sslc2中的每个可以提供成穿透串选择线ssl和第三层间电介质层ildc。在本发明构思的一示例实施方式中,第一上分离结构sslc1和第二上分离结构sslc2中的每个在第二方向d2上的宽度可以在大约20nm到大约70nm的范围内。第一上分离结构sslc1和第二上分离结构sslc2可以由例如硅氧化物、硅氮化物和硅氮氧化物中的至少一种形成,或者包括例如硅氧化物、硅氮化物和硅氮氧化物中的至少一种。

71.源极结构sc可以提供在第二衬底100和堆叠结构st之间。第二衬底100和源极结构sc可以对应于图1的公共源极线csl和图3和图4的公共源极线3205。

72.源极结构sc可以平行于堆叠结构st的接地选择线gsl、第一字线wla和第二字线wlb以及串选择线ssl中的每条并沿第一方向d1和第二方向d2延伸。源极结构sc可以包括顺序堆叠在第二衬底100上的第一源极导电图案scp1和第二源极导电图案scp2。第二源极导电图案scp2可以提供在第一源极导电图案scp1和第一层间电介质层ilda中的最下面的第一层间电介质层ilda之间。第一源极导电图案scp1的厚度可以不同于第二源极导电图案scp2的厚度。例如,第一源极导电图案scp1的厚度可以大于第二源极导电图案scp2的厚度。第一源极导电图案scp1和第二源极导电图案scp2中的每个可以包括掺杂的半导体材料。在本发明构思的一示例实施方式中,第一源极导电图案scp1的杂质浓度可以高于第二源极导

电图案scp2的杂质浓度。

73.第一至第三垂直沟道结构vs1、vs2和vs3可以提供在第一区域r1上,以穿透堆叠结构st和源极结构sc,并且可以与第二衬底100接触。第一至第三垂直沟道结构vs1、vs2和vs3中的每个可以提供为穿透第二衬底100的至少一部分,并且可以具有位于低于第二衬底100的顶表面和源极结构sc的底表面的水平处的底表面。

74.当在平面图中观察时,第一至第三垂直沟道结构vs1、vs2和vs3可以布置成在第一方向d1或第二方向d2上形成锯齿形。例如,第一至第三垂直沟道结构vs1、vs2和vs3可以排列成彼此未对准的行,并且可以排列成彼此未对准的列。第一至第三垂直沟道结构vs1、vs2和vs3可以不提供在第二区域r2上。第一至第三垂直沟道结构vs1、vs2和vs3可以对应于图2至图4的垂直沟道结构3220。第一至第三垂直沟道结构vs1、vs2和vs3可以对应于图1的第一晶体管lt1和lt2的沟道区、存储单元晶体管mct的沟道区以及第二晶体管ut1和ut2的沟道区。

75.第一垂直沟道结构vs1和第三垂直沟道结构vs3可以提供在第一上分离结构sslc1和第二上分离结构sslc2之间。第三垂直沟道结构vs3可以与每个第二上分离结构sslc2的侧表面sw2相邻。例如,在第一垂直沟道结构vs1和第三垂直沟道结构vs3中,第三垂直沟道结构vs3可以更靠近第二上分离结构sslc2的侧表面sw2。第二垂直沟道结构vs2可以在第二方向d2上与下分离结构gslc和第一上分离结构sslc1重叠。第二垂直沟道结构vs2可以是虚设沟道结构,其不用作存储单元的一部分。

76.在本发明构思的一示例实施方式中,穿透一个堆叠结构st的第一至第三垂直沟道结构vs1、vs2和vs3可以布置成在字线分离结构wlc之间形成17列,并且所述列可以沿第二方向d2排列。然而,本发明构思不限于该示例,并且在本发明构思的一示例实施方式中,穿透堆叠结构st的第一至第三垂直沟道结构vs1、vs2和vs3可以布置成在字线分离结构wlc之间形成(4n 1)或(8n 1)列,其中n是自然数。在本说明书中,列可以意指一组垂直沟道结构,其排列成一行或者在第一方向d1上布置以在第一方向d1上延伸。

77.第一垂直沟道结构vs1可以布置成在第一上分离结构sslc1和每个第二上分离结构sslc2之间形成三列;然而,本发明构思不限于此。此外,第一垂直沟道结构vs1可以布置成在每个第二上分离结构sslc2和与其相邻的字线分离结构wlc之间形成三列;然而,本发明构思不限于此。第二垂直沟道结构vs2可以布置成在下分离结构gslc和第一上分离结构sslc1之间形成一列。第三垂直沟道结构vs3可以布置成形成两列,所述两列通过插置在其间的第二上分离结构sslc2彼此间隔开。布置在第一上分离结构sslc1和字线分离结构wlc中的一个之间的第一垂直沟道结构vs1和第三垂直沟道结构vs3的列数可以等于布置在第一上分离结构sslc1和字线分离结构wlc中的另一个之间的第一垂直沟道结构vs1和第三垂直沟道结构vs3的列数。

78.第一至第三垂直沟道结构vs1、vs2和vs3可以提供在垂直沟道孔ch中,其形成为穿透堆叠结构st。第一垂直沟道结构vs1和第三垂直沟道结构vs3中的每个可以包括第一部分vsa,其提供在穿透第一堆叠结构sta的每个第一垂直沟道孔cha的内部空间中;第二部分vsb,其提供在穿透第二堆叠结构stb的每个第二垂直沟道孔chb的内部空间中;以及第三部分vsc,其提供在穿透第三堆叠结构stc的每个第三垂直沟道孔chc的内部空间中。每个第一垂直沟道孔cha可以在第三方向d3上连接到第二垂直沟道孔chb中的相应一个和第三垂直

沟道孔chc中的相应一个,以形成垂直沟道孔ch。例如,第一垂直沟道结构vs1和第三垂直沟道结构vs3中的每个的第一至第三部分vsa、vsb和vsc可以在第三方向d3上彼此连接。

79.在第一垂直沟道结构vs1和第三垂直沟道结构vs3的每个中,第一至第三部分vsa、vsb和vsc中的每个的宽度可以随着在第三方向d3上距第二衬底100的距离增加而增大。第一部分vsa的最上宽度可以大于第二部分vsb的最下宽度,第二部分vsb的最上宽度rb可以大于第三部分vsc的最下宽度。例如,第一垂直沟道结构vs1和第三垂直沟道结构vs3中的每个的侧表面可以在第一部分vsa和第二部分vsb之间的界面以及第二部分vsb和第三部分vsc之间的界面附近具有台阶形状。然而,本发明构思不限于该示例,第一垂直沟道结构vs1和第三垂直沟道结构vs3中的每个的侧表面可以具有位于不同水平的三个或更多台阶部分,或者可以具有平坦形状而没有阶梯部分。

80.在第一垂直沟道结构vs1和第三垂直沟道结构vs3的每个中,第二部分vsb的最上宽度rb可以大于第三部分vsc的最上宽度rc。当在图5a的平面图中观察时,第一垂直沟道结构vs1和第三垂直沟道结构vs3中的每个的第三部分vsc的轮廓可以位于第一垂直沟道结构vs1和第三垂直沟道结构vs3中的每个的第二部分vsb的轮廓内。在本发明构思的一示例实施方式中,第一垂直沟道结构vs1和第三垂直沟道结构vs3中的每个的第二部分vsb的最上宽度rb可以在大约100nm到大约140nm的范围内。第一垂直沟道结构vs1和第三垂直沟道结构vs3中的每个的第三部分vsc的最上宽度rc可以在大约50nm到大约90nm的范围内。

81.在每个第三垂直沟道结构vs3中,第三部分vsc的中心轴(例如,每个第三垂直沟道孔chc的中心轴)可以偏离第二部分vsb的中心轴(例如,每个第二垂直沟道孔chb的中心轴)。在本发明构思的一示例实施方式中,每个第三垂直沟道结构vs3的第三部分vsc的中心轴和每个第三垂直沟道结构vs3的第二部分vsb的中心轴之间的距离dl可以在大约20nm到大约30nm的范围内。

82.每个第二垂直沟道结构vs2可以包括第一部分vsa和第二部分vsb,第一部分vsa提供在穿透第一堆叠结构sta的每个第一垂直沟道孔cha的内部空间中,第二部分vsb提供在穿透第二堆叠结构stb的每个第二垂直沟道孔chb的内部空间中。每个第一垂直沟道孔cha可以在第三方向d3上连接到第二垂直沟道孔chb中的相应一个。例如,在每个第二垂直沟道结构vs2中,第一部分vsa和第二部分vsb可以在第三方向d3上彼此连接。每个第二垂直沟道结构vs2的顶表面可以位于比第一垂直沟道结构vs1和第三垂直沟道结构vs3中的每个的顶表面低的水平处。每个第二垂直沟道结构vs2可以提供在下分离结构gslc和第一上分离结构sslc1之间,并且可以在第三方向d3上延伸。

83.第一至第三垂直沟道结构vs1、vs2和vs3中的每个可以包括:数据存储图案dsp,其与堆叠结构st相邻和/或覆盖每个垂直沟道孔ch的内侧表面;垂直半导体图案vsp,其共形地覆盖数据存储图案dsp的内侧表面;间隙填充绝缘图案vi,其填充由垂直半导体图案vsp包围的内部空间;以及导电焊盘pad,其提供在由间隙填充绝缘图案vi和数据存储图案dsp包围的空间中。例如,导电焊盘pad可以设置在间隙填充绝缘图案vi的顶表面上。第一至第三垂直沟道结构vs1、vs2和vs3中的每个的顶表面可以具有圆形、椭圆形或多边形形状(例如,正方形形状)。

84.垂直半导体图案vsp可以提供在数据存储图案dsp和间隙填充绝缘图案vi之间。垂直半导体图案vsp可以像中空圆柱体一样地成形。在本发明构思的一示例实施方式中,垂直

半导体图案vsp可以与源极结构sc的一部分接触。例如,垂直半导体图案vsp可以由多晶硅形成或者包括多晶硅。

85.数据存储图案dsp可以像底部敞开的中空圆柱体一样地成形。数据存储图案dsp可以包括顺序堆叠的多个绝缘层。间隙填充绝缘图案vi可以由例如硅氧化物形成或者包括例如硅氧化物。在本发明构思的一示例实施方式中,导电焊盘pad可以由掺杂的半导体材料或导电材料中的至少一种形成,或者包括掺杂半导体材料或导电材料中的至少一种。

86.多个第四垂直沟道结构vs4可以提供在第二区域r2上,以穿透将在下面描述的第二绝缘层110、堆叠结构st和源极结构sc。例如,第四垂直沟道结构vs4可以提供为穿透第一字线wla和第二字线wlb的焊盘部分wlp。第四垂直沟道结构vs4可以提供在下面将要描述的接触插塞cp周围或附近。第四垂直沟道结构vs4可以不提供在第一区域r1上。第四垂直沟道结构vs4可以是虚设沟道结构,其不用作存储单元的一部分。

87.第四垂直沟道结构vs4可以与第一至第三垂直沟道结构vs1、vs2和vs3同时形成。第四垂直沟道结构vs4可以具有与第一垂直沟道结构vs1和第三垂直沟道结构vs3的结构基本相同的结构。然而,在本发明构思的一示例实施方式中,可以不提供第四垂直沟道结构vs4。

88.第二绝缘层110可以提供在第二区域r2上,以覆盖堆叠结构st的阶梯结构。第二绝缘层110可以具有基本平坦的顶表面。第二绝缘层110的顶表面可以与堆叠结构st的最高顶表面(例如,第三层间电介质层ildc中的最上面一个的顶表面)基本共面。

89.第三绝缘层130可以提供在堆叠结构st和第二绝缘层110上。第二绝缘层110和第三绝缘层130中的每个可以由例如绝缘材料(例如,硅氧化物、硅氮化物、硅氮氧化物和/或低k电介质材料)中的至少一种形成,或者包括例如绝缘材料(例如,硅氧化物、硅氮化物、硅氮氧化物和/或低k电介质材料)中的至少一种。

90.在第一区域r1上,位线接触插塞bp可以提供为穿透第三绝缘层130。每个位线接触插塞bp可以电连接到第一垂直沟道结构vs1和第三垂直沟道结构vs3中的每个的导电焊盘pad。

91.接触插塞cp可以提供在第二区域r2上,以穿透第二绝缘层110和第三绝缘层130。每个接触插塞cp可以进一步穿透堆叠结构st的第一层间电介质层ilda或第二层间电介质层ildb中的一个,并且可以以接触方式电连接到第一字线wla或第二字线wlb中的相应一条。接触插塞cp可以提供在第一字线wla和第二字线wlb的焊盘部分wlp上。接触插塞cp可以与第四垂直沟道结构vs4间隔开。随着距第一区域r1的距离增加,每个接触插塞cp的高度可以增加。接触插塞cp可以对应于图4的栅极连接线3235。

92.随着在第三方向d3上距第二衬底100的距离增加,位线接触插塞bp和接触插塞cp中的每个可以具有增加的宽度。位线接触插塞bp和接触插塞cp可以由导电材料和金属材料中的至少一种形成,或者包括导电材料和金属材料中的至少一种。

93.分别电连接到位线接触插塞bp和接触插塞cp的位线bl和导电线cl可以提供在第三绝缘层130上。第一至第三垂直沟道结构vs1、vs2和vs3中的每个可以在第三方向d3上与一对位线bl重叠,并且可以电连接到它们中的一条。位线bl和导电线cl可以由导电材料和金属材料中的至少一种形成,或者包括导电材料和金属材料中的至少一种。位线bl可以对应于图1的位线bl以及图3和图4的位线3240,导电线cl可以对应于图4的导电线3250。

94.在堆叠结构st的外部区域中(例如,在沿第一方向d1与堆叠结构st和第二衬底100间隔开的区域上),接触插塞cp中的一个可以提供为穿透第二绝缘层110并电连接到外围电路晶体管ptr中的相应一个。这里,连接到外围电路晶体管ptr的接触插塞cp上的导电线cl可以电连接到对应于图1的输入/输出焊盘1101或图2和图3的输入/输出焊盘2210的元件。

95.在本发明构思的一示例实施方式中,附加绝缘层可以提供在第三绝缘层130上以覆盖位线bl和导电线cl,并且附加互连线可以提供在附加绝缘层中。

96.图7是示出根据本发明构思的一示例实施方式的三维半导体存储器件的一部分(例如,图6a的“a”)的放大截面图。

97.参照图6a和图7,源极结构sc可以包括第一源极导电图案scp1和第二源极导电图案scp2,第一垂直沟道结构vs1之一的第一部分vsa可以包括数据存储图案dsp、垂直半导体图案vsp、间隙填充绝缘图案vi和下数据存储图案dspr。为了描述方便,下面将描述堆叠结构st之一和第一垂直沟道结构vs1之一,但是堆叠结构st中的剩余堆叠结构以及第一垂直沟道结构vs1和第三垂直沟道结构vs3中的剩余垂直沟道结构的第一部分vsa可以被配置为具有基本相同的特征。

98.数据存储图案dsp可以包括顺序堆叠在第二衬底100上的阻挡绝缘层blk、电荷存储层cil和隧穿绝缘层til。阻挡绝缘层blk可以与堆叠结构st或源极结构sc相邻,隧穿绝缘层til可以与垂直半导体图案vsp相邻。电荷存储层cil可以插置在阻挡绝缘层blk和隧穿绝缘层til之间。阻挡绝缘层blk可以覆盖每个垂直沟道孔ch的内侧壁(例如,第一垂直沟道孔的内侧壁)。

99.阻挡绝缘层blk、电荷存储层cil和隧穿绝缘层til可以在堆叠结构st和垂直半导体图案vsp之间的区域中沿第三方向d3延伸。在本发明构思的一示例实施方式中,由垂直半导体图案vsp与第一栅电极和第二栅电极之间的电压差引起的福勒-诺德海姆(fowler-nordheim(fn))隧穿现象可以用于在数据存储图案dsp中存储或改变数据。在本发明构思的一示例实施方式中,阻挡绝缘层blk和隧穿绝缘层til可以由硅氧化物形成或者包括硅氧化物,电荷存储层cil可以由硅氮化物或硅氮氧化物形成,或者包括硅氮化物或硅氮氧化物。

100.源极结构sc的第一源极导电图案scp1可以与垂直半导体图案vsp接触,第二源极导电图案scp2可以与垂直半导体图案vsp间隔开,且数据存储图案dsp插置在其间。第一源极导电图案scp1可以与间隙填充绝缘图案vi间隔开,且垂直半导体图案vsp插置在其间。

101.例如,第一源极导电图案scp1可以包括突出部分scp1bt,该突出部分scp1bt位于比第二源极导电图案scp2的底表面scp2b高或比第一源极导电图案scp1的底表面scp1b低的水平处。突出部分scp1bt可以位于比第二源极导电图案scp2的顶表面scp2a低的水平处。突出部分scp1bt的与数据存储图案dsp或下数据存储图案dspr接触的表面可以具有弯曲的形状。

102.尽管图7显示出每个第一源极导电图案scp1包括两个突出部分scp1bt,但本发明构思不限于此。例如,第一源极导电图案scp1可以具有多于两个的突出部分scp1bt,或者可以仅具有一个突出部分scp1bt。

103.图8a和图8b是示出根据本发明构思的一示例实施方式的三维半导体存储器件的平面图。在下面的描述中,为了简明描述,先前参照图5a和图5b描述的元件可以由相同的附图标记来标识,而不重复其重复描述。

104.参照图8a和图8b,一对第二上分离结构sslc2可以提供在每个字线分离结构wlc和第一上分离结构sslc1之间。例如,一对第二上分离结构sslc2可以提供在多个字线分离结构wlc中的第一字线分离结构wlc和第一上分离结构sslc1之间。在每个字线分离结构wlc和第一上分离结构sslc1之间,所述一对第二上分离结构sslc2可以在第二方向d2上彼此间隔开。

105.在本发明构思的一示例实施方式中,穿透一个堆叠结构st的第一至第三垂直沟道结构vs1、vs2和vs3可以排列成在字线分离结构wlc之间形成25列。然而,本发明构思不限于该示例。

106.第一垂直沟道结构vs1可以排列成在第一上分离结构sslc1和每个第二上分离结构sslc2之间形成三列。此外,第一垂直沟道结构vs1可以排列成在每个第二上分离结构sslc2和与其相邻的字线分离结构wlc之间形成三列。此外,第一垂直沟道结构vs1可以排列成在沿第二方向d2彼此相邻的一对第二上分离结构sslc2之间形成两列。

107.图9a、图10a和图11a是截面图,其分别沿图5a或图5b的线i-i'截取以示出根据本发明构思的一示例实施方式的制造三维半导体存储器件的方法。图9b、图10b、图11b和图12是截面图,其分别沿图5a或图5b的线ii-ii'截取以示出根据本发明构思的一示例实施方式的制造三维半导体存储器件的方法。

108.下文中,将参照图9a至图12、图5a、图5b、图6a和图6b更详细地描述根据本发明构思的一示例实施方式的制造三维半导体存储器件的方法。

109.参照图9a和图9b,可以提供包括第一区域r1和第二区域r2的第一衬底10。可以在第一衬底10中形成器件隔离层11以限定有源区。器件隔离层11的形成可以包括在第一衬底10的上部形成沟槽以及用硅氧化物填充该沟槽。

110.可以在由器件隔离层11限定的有源区上形成外围电路晶体管ptr。可以在第一衬底10上形成连接到外围电路晶体管ptr的外围源极/漏极区29的外围电路接触插塞31和外围电路互连线33。可以形成第一绝缘层30以覆盖外围电路晶体管ptr、外围电路接触插塞31和外围电路互连线33。

111.可以在第一绝缘层30上依次形成第二衬底100、下牺牲层101和下半导体层103。在本发明构思的一示例实施方式中,下牺牲层101可以由硅氮化物形成或者包括硅氮化物。在本发明构思的一示例实施方式中,下牺牲层101可以通过顺序堆叠多个绝缘层形成。下半导体层103可以由与第二衬底100的材料相同的材料形成,或者包括与第二衬底100的材料相同的材料。

112.可以在下半导体层103上形成下模制结构105。下模制结构105的形成可以包括在下半导体层103上交替且重复地形成第一层间电介质层ilda和第一牺牲层sla。

113.可以形成下分离沟槽gtr以穿透下模制结构105。可以形成下分离结构gslc以填充下分离沟槽gtr。下分离结构gslc的顶表面可以与下模制结构105的顶表面基本共面。在下面的描述中,“两个元件基本上彼此共面”的表述可以意指可对所述元件执行平坦化工艺。平坦化工艺可以使用例如化学机械抛光(cmp)工艺或回蚀工艺执行。

114.参照图10a和图10b,可以在下半导体层103上形成第一模制结构msa。图9a和图9b的下模制结构105可以是第一模制结构msa的下部,并且在下文中可以被称为第一模制结构msa。

115.第一模制结构msa的形成可以包括交替并重复地在下半导体层103上形成第一层间电介质层ilda和第一牺牲层sla以及对第一层间电介质层ilda和第一牺牲层sla执行第一修整工艺。

116.第一修整工艺可以包括:在第一层间电介质层ilda中的最上面一个的顶表面上形成掩模图案,使用掩模图案部分地蚀刻第一层间电介质层ilda和第一牺牲层sla,减小掩模图案的面积,以及使用减小的掩模图案部分地蚀刻第一层间电介质层ilda和第一牺牲层sla。减小掩模图案的面积的步骤和图案化步骤可以交替地重复。作为第一修整工艺的结果,第一模制结构msa可以具有阶梯结构。

117.可以在第一模制结构msa上形成第二模制结构msb。第二模制结构msb的形成可以包括:在第一模制结构msa的第一层间电介质层ilda中的最上面的一个上交替并重复地形成第二层间电介质层ildb和第二牺牲层slb,以及对第二层间电介质层ildb和第二牺牲层slb执行第二修整工艺。第二修整工艺可以以与上述第一修整工艺相同的方式执行。作为第二修整工艺的结果,第二模制结构msb可以具有阶梯结构。

118.第一牺牲层sla和第二牺牲层slb可以由与第一层间电介质层ilda和第二层间电介质层ildb的绝缘材料不同的绝缘材料形成。第一牺牲层sla和第二牺牲层slb可以由相对于第一层间电介质层ilda和第二层间电介质层ildb具有蚀刻选择性的材料形成,或者包括相对于第一层间电介质层ilda和第二层间电介质层ildb具有蚀刻选择性的材料。例如,第一牺牲层sla和第二牺牲层slb可以由硅氮化物形成,第一层间电介质层ilda和第二层间电介质层ildb可以由硅氧化物形成。第一牺牲层sla和第二牺牲层slb可以形成为具有彼此基本相同的厚度,并且第一层间电介质层ilda和第二层间电介质层ildb可以根据它们的垂直位置具有至少两种彼此不同的厚度。例如,第一层间电介质层ilda可以具有彼此不同的厚度,第二层间电介质层ildb可以具有彼此不同的厚度。然而,本发明构思不限于此。在本发明构思的一示例实施方式中,第一牺牲层sla和第二牺牲层slb可以形成为具有彼此不同的厚度。

119.在形成第一模制结构msa和第二模制结构msb之后,可以形成第二绝缘层110以覆盖第一模制结构msa和第二模制结构msb的阶梯结构。第二绝缘层110的顶表面可以与第二模制结构msb的顶表面基本共面。

120.可以在第一垂直沟道孔cha和第二垂直沟道孔chb中形成牺牲柱sp。第一垂直沟道孔cha形成为穿透第一模制结构msa、下半导体层103和下牺牲层101,第二垂直沟道孔chb通过穿透第二模制结构msb形成。牺牲柱sp可以由例如多晶硅形成或者包括例如多晶硅。

121.参照图11a和图11b,可以在第二模制结构msb上形成第三模制结构msc。第三模制结构msc的形成可以包括在第二模制结构msb的第二层间电介质层ildb中的最上面一个上交替并重复地形成第三层间电介质层ildc和第三牺牲层slc以及图案化第三层间电介质层ildc和第三牺牲层slc以减小其在第一方向d1上的长度。第三模制结构msc在第一方向d1上的长度可以小于第二模制结构msb的第二牺牲层slb中的最上面一个在第一方向d1上的长度。此后,可以形成第二绝缘层110以覆盖第三模制结构msc的侧表面。第二绝缘层110的顶表面可以位于比图10a和图10b中更高的水平;例如,它可以基本上与第三模制结构msc的顶表面共面。

122.第三牺牲层slc可以由与第一牺牲层sla和第二牺牲层slb的绝缘材料相同的绝缘

材料形成,第三层间电介质层ildc可以由与第一层间电介质层ilda和第二层间电介质层ildb的绝缘材料相同的绝缘材料形成。例如,第三牺牲层slc可以由硅氮化物形成,第三层间电介质层ildc可以由硅氧化物形成。

123.接下来,可以形成第三垂直沟道孔chc以穿透第三模制结构msc。第三垂直沟道孔chc可以形成在对应于第二垂直沟道孔chb的位置处。在本发明构思的一示例实施方式中,第三垂直沟道孔chc中的一些可以形成为使得其中心轴偏离第二垂直沟道孔chb中的相应第二垂直沟道孔chb的中心轴。

124.可以去除由第三垂直沟道孔chc暴露的牺牲柱sp(例如,图10a和图10b)。可以形成第一至第三垂直沟道结构vs1、vs2和vs3以填充通过去除牺牲柱sp而形成的第一、第二和第三垂直沟道孔cha、chb和chc的内部空间。尽管在图11b中没有示出第二垂直沟道结构vs2,但是第二垂直沟道结构vs2可以形成于在第三方向d3上与下分离结构gslc重叠的位置处。

125.第一至第三垂直沟道结构vs1、vs2和vs3的形成可以包括顺序形成数据存储图案dsp、垂直半导体图案vsp、间隙填充绝缘图案vi和导电焊盘pad,以填充第一至第三垂直沟道孔cha、chb和chc。

126.参照图12,可以形成第一上分离沟槽str1和第二上分离沟槽str2以沿第一方向d1与第三模制结构msc交叉。第一上分离沟槽str1和第二上分离沟槽str2中的每个的底表面可以位于比第三牺牲层slc中的最下面一个的底表面低并且比第二牺牲层slb中的最上面一个的顶表面高的水平。

127.可以形成字线分离沟槽wtr以穿透第一至第三模制结构msa、msb和msc(例如,第一至第三层间电介质层ilda、ildb和ildc以及第一至第三牺牲层sla、slb和slc)和下半导体层103,并沿第一方向d1与第一至第三模制结构msa、msb和msc交叉。每个字线分离沟槽wtr的底表面可以位于比下半导体层103的顶表面低的水平,并且下牺牲层101可以被字线分离沟槽wtr暴露。

128.结合图12再次参照图5a、图5b、图6a和图6b,可以选择性地去除由字线分离沟槽wtr暴露的第一至第三牺牲层sla、slb和slc和下牺牲层101以及由第一上分离沟槽str1和第二上分离沟槽str2暴露的第三牺牲层slc。牺牲层101、sla、slb和slc的选择性去除可以通过例如使用蚀刻溶液的湿法蚀刻工艺执行。在选择性地去除牺牲层101、sla、slb和slc的过程期间,可以不去除第一至第三层间电介质层ilda、ildb和ildc。

129.作为选择性去除牺牲层101、sla、slb和slc的结果,通过去除下牺牲层101形成第一间隙区(其可以是空的空间),并且通过去除第一至第三牺牲层sla、slb和slc形成第二间隙区(其可以是空的空间)。第一垂直沟道结构vs1的侧表面和第三垂直沟道结构vs3的侧表面可以被第一间隙区和第二间隙区部分地暴露。例如,第一垂直沟道结构vs1和第三垂直沟道结构vs3中的每个的垂直半导体图案vsp的侧表面可以通过第一间隙区被部分地暴露。

130.可以形成第一源极导电图案scp1以填充第一间隙区。第一源极导电图案scp1上的下半导体层103可以被称为第二源极导电图案scp2。结果,可以形成包括第一源极导电图案scp1和第二源极导电图案scp2的源极结构sc。

131.可以形成接地选择线gsl、第一字线wla、第二字线wlb和串选择线ssl以填充第二间隙区。结果,可以形成堆叠结构st,该堆叠结构st包括接地选择线gsl、第一字线wla、第二字线wlb、串选择线ssl以及插置在接地选择线gsl、第一字线wla、第二字线wlb和串选择线

ssl之间的第一至第三层间电介质层ilda、ildb和ildc。

132.此后,可以形成第一上分离结构sslc1以填充第一上分离沟槽str1,可以形成第二上分离结构sslc2以填充第二上分离沟槽str2,可以形成字线分离结构wlc以填充字线分离沟槽wtr。第一上分离结构sslc1和第二上分离结构sslc2和字线分离结构wlc中的每个被示出为具有位于与第一至第三垂直沟道结构vs1、vs2和vs3的顶表面相同水平的顶表面,但是本发明构思不限于该示例;例如,第一上分离结构sslc1和第二上分离结构sslc2以及字线分离结构wlc中的每个的顶表面可以位于比第一至第三垂直沟道结构vs1、vs2和vs3的顶表面高的水平。

133.可以在第一上分离结构sslc1和第二上分离结构sslc2的顶表面、字线分离结构wlc的顶表面和堆叠结构st的顶表面上形成第三绝缘层130。

134.可以在第一区域r1上形成位线接触插塞bp,并且每个位线接触插塞bp可以提供成穿透第三绝缘层130,并且可以连接到第一垂直沟道结构vs1和第三垂直沟道结构vs3中的相应一个的导电焊盘pad。可以在第三绝缘层130上形成通过位线接触插塞bp电连接到第一垂直沟道结构vs1和第三垂直沟道结构vs3的位线bl。

135.在第二区域r2上,接触插塞cp可以形成为穿透第二绝缘层110和第三绝缘层130。每个接触插塞cp可以提供成进一步穿透堆叠结构st的第一层间电介质层ilda或第二层间电介质层ildb之一,并且可以电连接到第一字线wla或第二字线wlb中的相应一条。可以在第三绝缘层130上形成通过接触插塞cp连接到第一字线wla和第二字线wlb的导电线cl。

136.在根据本发明构思的一示例实施方式的三维半导体存储器件中,通过在垂直沟道结构之间添加一列虚设沟道结构,可以确保划分接地选择线的下分离结构和划分串选择线的上分离结构的空间,同时防止用作存储单元的一部分的垂直沟道结构被电影响。因此,可以改善三维半导体存储器件的电特性并增加其可靠性。

137.虽然已参照本发明构思的示例实施方式对本发明构思进行了具体展示和描述,但是对于本领域普通技术人员将明显的,在不脱离本发明构思的精神和范围的情况下,可以对其进行形式和细节上的各种变化。

138.本技术要求享有2021年12月14日在韩国知识产权局提交的第10-2021-0179136号韩国专利申请的优先权,其公开内容通过引用整体合并于此。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。