技术特征:

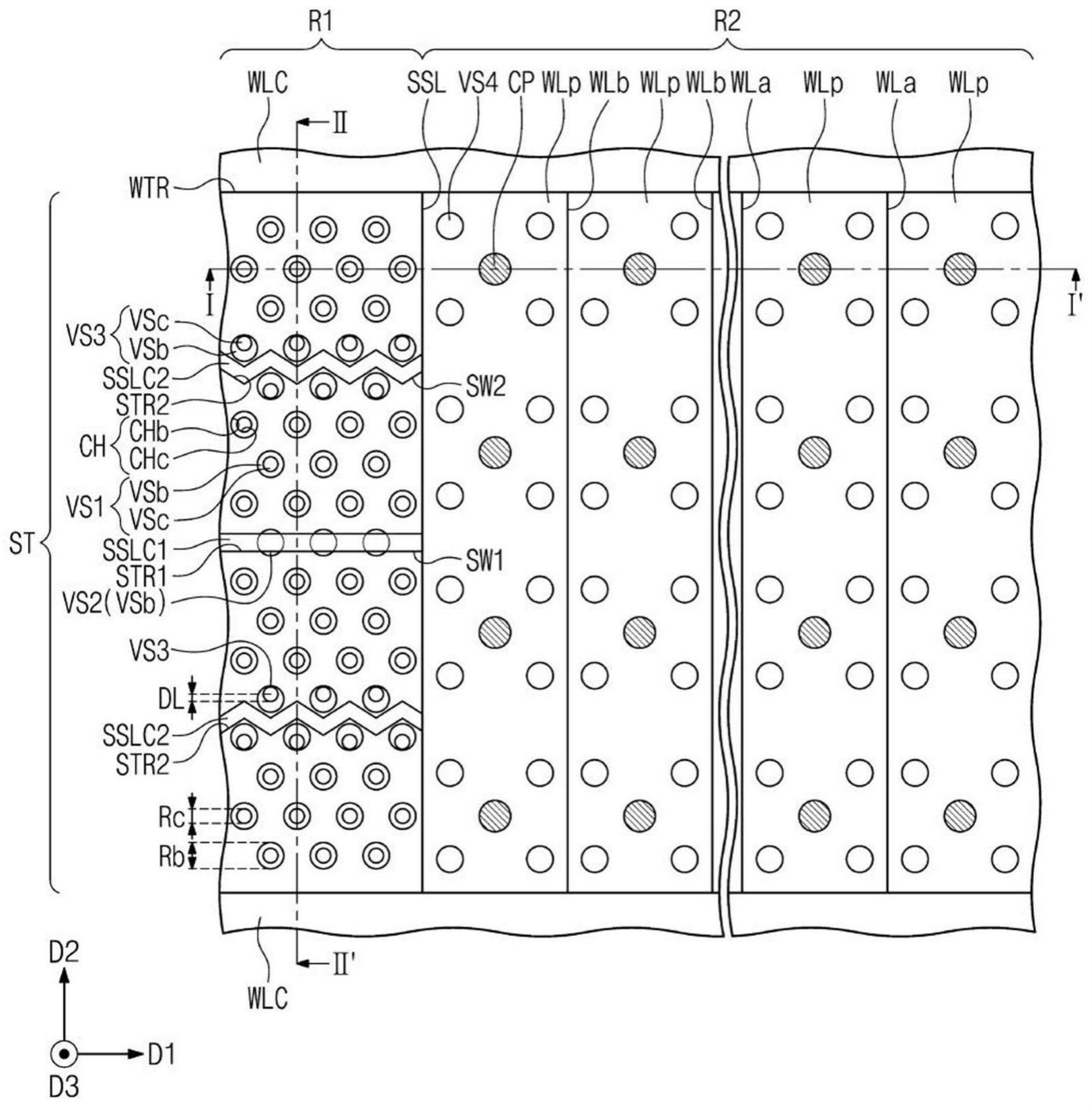

1.一种三维半导体存储器件,包括:堆叠结构,包括顺序堆叠在衬底上的接地选择线、第一字线、第二字线和串选择线;垂直沟道结构,穿透所述堆叠结构并被排列以形成多列;下分离结构,在第一方向上与所述堆叠结构的下部交叉,并沿着与所述第一方向相交的第二方向划分所述接地选择线;以及第一上分离结构和第二上分离结构,在所述第一方向上与所述堆叠结构的上部交叉,并沿着所述第二方向划分所述串选择线,其中所述下分离结构和所述第一上分离结构与所述垂直沟道结构的所述列中的一个垂直重叠,以及所述第二上分离结构提供在所述垂直沟道结构之间。2.根据权利要求1所述的半导体存储器件,其中所述第一上分离结构的侧表面具有平行于所述第一方向的线形状,以及从平面图看,每个所述第二上分离结构的侧表面是不平坦的。3.根据权利要求1所述的半导体存储器件,其中所述垂直沟道结构的所述列的数量是4n 1,其中n是自然数。4.根据权利要求1所述的半导体存储器件,其中所述堆叠结构被提供为多个,以及所述半导体存储器件进一步包括提供在所述堆叠结构之间的字线分离结构,其中所述字线分离结构在所述第一方向上与所述堆叠结构交叉,并覆盖每个所述堆叠结构的侧表面。5.根据权利要求4所述的半导体存储器件,其中每个所述字线分离结构的垂直长度大于所述第一上分离结构和所述第二上分离结构中的每个的垂直长度。6.根据权利要求4所述的半导体存储器件,其中所述垂直沟道结构包括:第一垂直沟道结构,提供在所述第一上分离结构和每个所述第二上分离结构之间以及在每个所述字线分离结构和每个所述第二上分离结构之间;第二垂直沟道结构,与所述下分离结构和所述第一上分离结构垂直重叠;以及第三垂直沟道结构,比所述第一垂直沟道结构更靠近所述第二上分离结构,其中所述第一垂直沟道结构和所述第三垂直沟道结构中的每个包括:第一部分,提供在穿透所述接地选择线和所述第一字线的第一垂直沟道孔中;第二部分,提供在穿透所述第二字线的第二垂直沟道孔中;以及第三部分,提供在穿透所述串选择线的第三垂直沟道孔中。7.根据权利要求6所述的半导体存储器件,其中所述第一部分的最上宽度大于所述第二部分的最下宽度,以及所述第二部分的最上宽度大于所述第三部分的最下宽度。8.根据权利要求6所述的半导体存储器件,其中所述第二部分的最上宽度大于所述第三部分的最上宽度。9.根据权利要求6所述的半导体存储器件,其中每个所述第三垂直沟道结构的所述第三部分的中心轴偏离每个所述第三垂直沟道结构的所述第二部分的中心轴。10.根据权利要求9所述的半导体存储器件,其中每个所述第三垂直沟道结构的所述第三部分的所述中心轴和每个所述第三垂直沟道结构的所述第二部分的所述中心轴之间的

距离在20nm到30nm的范围内。11.根据权利要求1所述的半导体存储器件,其中所述第一上分离结构和所述第二上分离结构中的每个在所述第二方向上的宽度在20nm到70nm的范围内。12.根据权利要求1所述的半导体存储器件,其中每个所述第二上分离结构的侧表面在所述第二方向上与所述垂直沟道结构间隔开。13.根据权利要求1所述的半导体存储器件,其中所述下分离结构的顶表面位于所述接地选择线的顶表面和所述第一字线中的最下面一条的底表面之间。14.一种三维半导体存储器件,包括:第一衬底,包括第一区域和在第一方向上邻近所述第一区域的第二区域;外围电路结构,包括设置在所述第一衬底上的外围电路晶体管;第二衬底,设置在所述外围电路结构上;堆叠结构,包括顺序堆叠在所述第二衬底上的接地选择线、第一字线、第二字线和串选择线,并在所述第二区域上具有阶梯结构;垂直沟道结构,穿透所述堆叠结构并被排列以形成多列;字线分离结构,覆盖所述堆叠结构的相反侧表面并在所述第一方向上延伸;下分离结构,在所述第一方向上与所述堆叠结构的下部交叉,并沿与所述第一方向相交的第二方向划分所述接地选择线;第一上分离结构和第二上分离结构,在所述第一方向上与所述堆叠结构的上部交叉,并沿所述第二方向划分所述串选择线;接触插塞,穿透所述堆叠结构的所述阶梯结构,并分别电连接到所述第一字线和所述第二字线;位线,分别电连接到所述垂直沟道结构;以及导电线,分别电连接到所述接触插塞,其中所述下分离结构和所述第一上分离结构与所述垂直沟道结构的所述列中的一个垂直重叠,以及从平面图看,所述第二上分离结构具有不平坦的侧表面,并且在所述第二方向上与所述垂直沟道结构间隔开。15.根据权利要求14所述的半导体存储器件,进一步包括位于所述第二衬底和所述堆叠结构之间的源极结构,其中每个所述垂直沟道结构包括数据存储图案、垂直半导体图案和导电焊盘,其中所述数据存储图案邻近所述堆叠结构,其中所述垂直半导体图案共形地覆盖所述数据存储图案的内侧壁,并且所述导电焊盘设置在所述垂直半导体图案上,以及所述源极结构与每个所述垂直沟道结构的所述垂直半导体图案接触。16.根据权利要求14所述的半导体存储器件,其中所述垂直沟道结构的所述列的数量是8n 1,其中n是自然数。17.根据权利要求14所述的半导体存储器件,其中每个所述垂直沟道结构的侧表面在所述串选择线中的最下面一条与所述第二字线中的最上面一条之间具有台阶部分。18.根据权利要求14所述的半导体存储器件,其中所述下分离结构的顶表面位于所述接地选择线的顶表面和所述第一字线中的最下面一条的底表面之间。

19.一种电子系统,包括:三维半导体存储器件;以及控制器,电连接到所述三维半导体存储器件并被配置为控制所述三维半导体存储器件,其中所述三维半导体存储器件包括:衬底,具有第一区域和在第一方向上邻近所述第一区域的第二区域;堆叠结构,包括顺序堆叠在所述衬底上的接地选择线、第一字线、第二字线和串选择线,并在所述第二区域上具有阶梯结构;垂直沟道结构,穿透所述堆叠结构并被排列以形成多列;下分离结构,在所述第一方向上与所述堆叠结构的下部交叉,并沿与所述第一方向相交的第二方向划分所述接地选择线;第一上分离结构和第二上分离结构,在所述第一方向上与所述堆叠结构的上部交叉,并沿所述第二方向划分所述串选择线;绝缘层,覆盖所述堆叠结构的所述阶梯结构;接触插塞,穿透所述堆叠结构和所述绝缘层;以及输入/输出焊盘,连接到所述接触插塞中的一个,其中所述控制器通过所述输入/输出焊盘电连接到所述三维半导体存储器件,其中所述下分离结构和所述第一上分离结构与所述垂直沟道结构的所述列中的一个垂直重叠,以及其中所述第二上分离结构提供在所述垂直沟道结构的所述列中的两列之间。20.根据权利要求19所述的电子系统,其中所述三维半导体存储器件进一步包括设置在所述衬底上的外围电路结构,以及其中所述输入/输出焊盘通过所述接触插塞中的一个电连接到所述外围电路结构。

技术总结

本发明构思涉及三维半导体存储器件和包括其的电子系统。该三维半导体存储器件包括:堆叠结构,包括顺序堆叠在衬底上的接地选择线、第一字线、第二字线和串选择线;垂直沟道结构,穿透堆叠结构并被排列以形成多列;下分离结构,在第一方向上与堆叠结构的下部交叉,并沿与第一方向交叉的第二方向划分接地选择线;以及第一上分离结构和第二上分离结构,在第一方向上与堆叠结构的上部交叉,并沿第二方向划分串选择线,其中下分离结构和第一上分离结构与垂直沟道结构的所述列之一垂直重叠,并且第二上分离结构提供在垂直沟道结构之间。二上分离结构提供在垂直沟道结构之间。二上分离结构提供在垂直沟道结构之间。

技术研发人员:金承允 金森宏治 韩智勋

受保护的技术使用者:三星电子株式会社

技术研发日:2022.12.06

技术公布日:2023/6/16

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。