半导体系统及接线缺陷检测方法

1.相关申请案的交叉参考

2.本技术案是基于且主张来自2021年9月6日申请的第2021-144898号日本专利申请案及2022年2月24日申请的第17/679857号美国专利申请案的优先权权益,所述申请案的全部内容以引用的方式并入本文中。

技术领域

3.本文中描述的实施例大体上涉及半导体系统及接线缺陷检测方法。

背景技术:

4.半导体芯片通过其堆叠、使用接合线彼此连接并封装的堆叠技术已变得广泛使用。在其中在通过接合线从控制器传送的信号中检测到缺陷的情况中,需要在不分离封装的情况下容易且准确地检测所述信号中的缺陷的原因。

技术实现要素:

5.实施例提供一种半导体系统及一种接线缺陷检测方法,通过所述方法,可在不分离所述半导体系统的封装的情况下容易且准确地检测信号中的缺陷的原因。

6.一般来说,根据一个实施例,一种半导体系统包含:第一半导体芯片;第二半导体芯片,其堆叠于所述第一半导体芯片上方;控制器,其经配置以控制所述第一及第二半导体芯片;第一接线,其连接于所述控制器与所述第一及第二半导体芯片中的每一者之间,且第一信号将要通过其从所述控制器传输到所述第一及第二半导体芯片中的每一者;第二接线,其连接于所述控制器与所述第一半导体芯片之间,且流过所述第一接线到所述第一半导体芯片的所述第一信号的电流将要通过其返回到所述控制器;及第三接线,其连接于所述控制器与所述第二半导体芯片之间,且流过所述第一接线到所述第二半导体芯片的所述第一信号的电流将要通过其返回到所述控制器。

附图说明

7.图1是示意性地说明根据第一实施例的半导体系统的主要组件的平面图。

8.图2是示意性地说明根据第二实施例的半导体系统的主要组件的平面图。

9.图3是说明存储器系统的轮廓的框图,所述存储器系统是根据第一及第二实施例的半导体系统的特定实例。

10.图4是说明具有三维结构的nand快闪存储器单元阵列的实例的电路图。

具体实施方式

11.在下文中,半导体系统及接线缺陷检测方法的实施例将参考附图来描述。虽然将集中于半导体系统的主要组件进行描述,但半导体系统可具有本文中未说明或描述的组件或功能。本文在下文中的描述不希望排除本文中未说明或描述的组件或功能。

12.(第一实施例)

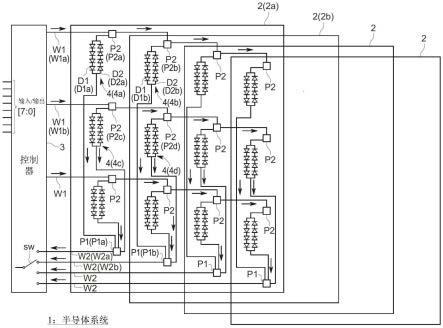

13.图1是示意性地说明根据第一实施例的半导体系统1的主要组件的平面图。图1的半导体系统1具备多个堆叠的半导体芯片2及控制多个半导体芯片2的控制器3。

14.多个半导体芯片2中的每一者是未封装的裸芯片。半导体芯片2可为任何类型。举例来说,半导体芯片2可为快闪存储器芯片。

15.多个堆叠的半导体芯片2中的每一者具备多个垫p1及p2。在图1中,假设多个半导体芯片2具有相同功能,且设置于每一半导体芯片2上的垫p1及p2的位置、大小及数目在全部半导体芯片2中是共同的。每一半导体芯片2通过垫p1及p2及接合线w1及w2将信号传输到控制器3/从控制器3接收信号。如稍后描述,每一半导体芯片2包含两种类型的垫p1及p2。有关垫的数目,每一半导体芯片2具备一个垫p1及一或多个垫p2。图1表示其中每一半导体芯片2具备多个垫p2的实例。

16.每一半导体芯片2的多个垫p2包含用于从控制器3接收信号的垫、用于将信号传输到控制器3的垫、用于双向地将信号传输到控制器3/从控制器3接收信号的垫及用于供应电力的垫。此外,单独设置于每一半导体芯片2上的垫p1是用于检测缺陷的垫,如稍后描述。

17.如图1中说明,多个半导体芯片2堆叠于支撑衬底(未说明)上同时稍微移位。移位原因是要促进接合线w1及w2连接到每一半导体芯片2上的垫p1及p2。当接合线w1及w2连接到多个半导体芯片2中的每一者上的垫p1及p2时,随着堆叠的半导体芯片2的数目增加,变得难以确保用于布置接合线w1及w2的空间。因此,在一些实施例中,多个堆叠的半导体芯片2上的相同类型的垫通过使用穿硅通路(tsv)、凸块、cu-cu连接或类似物在堆叠方向上彼此接合,且接合线w1连接到任一半导体芯片2的垫以将信号传输到控制器3/从控制器3接收信号。因此,无需增加接合线w1的数目,信号可在控制器3与多个半导体芯片2之间传输/接收。因此,堆叠的半导体芯片2的数目可根据需要增加。

18.在图1中,多个堆叠的半导体芯片2的对应垫p1(或p2)通过导线彼此电导通。然而,对角线是示意性的,且实际上由例如通路、cu-cu连接、接线模式及其它的组合来实施。

19.虽然图1表示其中每一半导体芯片2包含三个垫p2的实例。然而,垫p2的数目、垫p1及p2的布置位置及通过垫p2传输/接收的信号的类型是任意的。举例来说,当半导体芯片2是快闪存储器芯片时,除了与电力相关的垫外,所有垫基本上都将信号传输到控制器3/从控制器3接收信号。快闪存储器芯片中典型的垫包含用于芯片启用信号cen的垫、用于写入启用信号wen的垫、用于读取启用信号ren的垫、用于地址锁存启用信号ale的垫、用于命令锁存启用信号cle的垫及其它。芯片启用信号cen是用于使快闪存储器芯片进入启用状态的信号。写入启用信号wen是用于指定将数据写入到快闪存储器芯片的时序的信号。读取启用信号ren是用于指定用于从快闪存储器芯片读取数据的时序的信号。地址锁存启用信号ale是用于指示信号dq是地址的信号。命令锁存启用信号cle是用于指示信号dq是命令的信号。

20.如上文描述,设置于多个堆叠的半导体芯片2中的每一者上的垫p2的数目及类型是任意的,且多个半导体芯片2中的任一者上的垫p2及控制器3通过接合线w1彼此连接。举例来说,安置于最上层上的半导体芯片2的多个垫p2可分别通过接合线w1连接到控制器3。另外,如图1中说明,由于多个半导体芯片2被堆叠同时被移位,因此具有接合线w1所连接到的垫p2的半导体芯片2可能不一定是安置于最上层上的半导体芯片。

21.在本文中的描述中,用于在多个半导体芯片2中的每一者与控制器3之间传输信号

的接合线w1将被称为第一接线w1,且用于将控制器3与每一半导体芯片2彼此连接以便检测第一接线w1中的缺陷的接合线w2将被称为第二接线w2。提供与设置于多个堆叠的半导体芯片2中的每一者上的多种类型的垫p2的数目一样多的第一接线w1。提供与堆叠的半导体芯片2的数目一样多的第二接线w2。

22.此外,在本文中的描述中,连接到多个第二接线w2中的每一者的半导体芯片2上的垫p1可被称为第一垫p1,且与第一接线w1电导通的垫p2可被称为第二垫p2。虽然第二垫p2是设置于半导体芯片2上的常规垫,但第一垫p1是经提供用于检测缺陷的非常规垫。第一垫p1经提供用于每一半导体芯片2,且连接到对应第二接线w2。一或多个第二垫p2设置于每一半导体芯片2上,且第一接线w1连接到半导体芯片2中的任一者的第二垫p2。

23.如上文描述,针对最小配置,除了上文描述的多个半导体芯片2及控制器3外,根据本实施例的半导体系统1具备至少一个第一接线w1及多个第二接线w2。第一接线w1是用于在控制器3与多个半导体芯片2之间传输信号的接线(接合线)。多个第二接线w2是用于将控制器3与多个半导体芯片2的第一垫p1彼此连接的接线(接合线),且当执行缺陷检测时,使流过第一接线w1到控制器3的电流返回。

24.控制器3中具备开关sw,所述开关sw选择多个第二接线w2中的一者。基于电流流过由开关sw选择的第二接线w2,控制器3检测连接到第二接线w2的第一接线w1的缺陷。更准确地说,第一接线w1的缺陷是指通过第一接线w1从控制器3侧处的第一接线w1的端到每一半导体芯片2的第二垫p2的信号路径中的缺陷。缺陷的典型实例是短路或断开连接。

25.如稍后描述,在本实施例中,当控制器3通过第一接线w1向每一半导体芯片2的第二垫p2发送信号时,对应于信号的电流通过第二接线w2从第一垫p1返回到控制器3。当每一半导体芯片2具有多个第二垫p2时,控制器3可根据到控制器3的输入信号或用于在稍后将要描述的第一模式被选择之后选择任意第一接线w1的地址信号选择任意第二垫p2,且可检测连接到所选择的第二垫p2的第一接线w1的缺陷。

26.因为单独为每一半导体芯片2提供第二接线w2,因此控制器3可从通过第二接线w2返回的电流识别具有其中出现缺陷的信号路径的半导体芯片2。

27.控制器3可通过在第一模式与第二模式之间执行切换来控制多个堆叠的半导体芯片2。第一模式是用于检测用于信号传输的第一接线w1中的缺陷的模式。当第一模式被选择时,控制器3检测通过多个第二接线w2返回的电流,且基于检测到的电流检测多个相应半导体芯片2的信号路径中是否出现缺陷。更明确来说,在第一模式中,控制器3检测经由对应于任一第二垫p2的第一垫p1从第一接线w1流到对应第二接线w2的电流。

28.当第二模式被选择时,其中电流从第一接线w1流到多个第二接线w2的信号路径被切断。因此,控制器3通过第一接线w1将信号传输到每一半导体芯片2/从每一半导体芯片2传输信号,以使每一半导体芯片2执行正常操作。

29.如上文描述,每一第一接线w1的一端连接到控制器3,且其另一端连接到半导体芯片2中的任一者的第二垫p2。设置于多个半导体芯片2中的每一者上的多个第二垫p2彼此电导通。在缺陷检测期间,从第一接线w1流到多个第二垫p2中的每一者的电流通过对应第一垫p1流到对应第二接线w2。

30.如图1中说明,多个半导体芯片2中的每一者具备安置于第一垫p1与第二垫p2之间的整流电路4。当第一接线w1的电压电平小于预定阈值时,整流电路4切断其中电流从第二

垫p2流到第一垫p1的信号路径,且当第一接线w1的电压电平等于或高于阈值时,整流电路4允许电流在信号路径中从第二垫p2流到第一垫p1。预定阈值是例如高于半导体芯片2的电源电压的电压。因此,当控制器3将第一接线w1的电压电平设置为小于预定阈值时(上文描述的第二模式),电流不通过第二垫p2从第一接线w1流到第一垫p1,且因此,也不在第二接线w2中流动,使得控制器3无需监测第二接线w2的电流。同时,在第一模式中,控制器3有意地将第一接线w1的电压电平设置为等于或高于预定阈值,使得电流通过第二垫p2及第一垫p1从第一接线w1流到第二接线w2。

31.如上文描述,在第一模式中,第一接线w1的电压电平需要被设置为预定阈值或更高。因此,例如,升压电路(未说明)可设置于控制器3内部,以在第一模式期间将通过用升压电路使控制器3的电力电压升高获得的电压供应到第一接线w1。替代地,用于第一模式的电压可提前输入到控制器3,且用于第一模式的输入电压可在第一模式期间供应到第一接线w1。

32.通过以此方式提供整流电路4,仅当控制器3增加第一接线w1的电压电平时,电流才可通过整流电路4从第一接线w1流到第二接线w2。因此,通过监测第二接线w2的电流,控制器3可对其电压电平已增加的第一接线w1执行缺陷检测。

33.整流电路4具有多个第一二极管d1,其串联连接同时将其整流方向对准。第一二极管d1的阳极在多个经连接第一二极管d1的一端处连接到第二垫p2。第一二极管d1的阴极在多个经连接第一二极管d1的另一端处连接到第一垫p1。因为正常二极管的正向电压是约0.6v,因此当半导体芯片2的电力电压例如是约1.8v时,串联连接的二极管的数目被设置为例如4。因此,上述预定阈值被设置为约2.4v,且当第一接线w1的电压电平是2.4v或更多时,电流可被允许通过二极管d1从第一接线w1流到第二接线w2。

34.已描述其中电流通过整流电路4从第一接线w1流到第二接线w2的实例。然而,根据缺陷的类型,缺陷可能无法通过简单地监测第二接线w2的电流来正确地检测,且可凭借通过整流电路4使电流从第二接线w2返回到第一接线w1来检测。因此,当多个第二接线w2的电压电平小于预定阈值时,整流电路4切断其中电流从多个第一垫p1流到对应第二垫p2的信号路径。当多个第二接线w2中的至少一者的电压电平等于或高于阈值时,整流电路4允许电流在信号路径中从多个第一垫p1中的至少一者流到对应第二垫p2。在此情况中,整流电路4具有多个第二二极管d2,其在与多个第一二极管d1的方向相反的方向上串联连接。第二二极管d2的阴极在多个经连接第二二极管d2的一端处连接到第二垫p2。第二二极管d2的阳极在多个经连接第二二极管d2的另一端处连接到第一垫p1。

35.如图1中说明,每一半导体芯片2具备多种类型的第二垫p2用于相对于控制器3传输信号。在此情况中,多个第一接线w1布置于控制器3与多个半导体芯片2之间以与多种类型的第二垫p2电导通。在缺陷检测期间,控制器3检测通过对应第二垫p2及对应第一垫p1从每一第一接线w1流到对应第二接线w2的电流。整流电路4单独连接到多个第一接线w1中的每一者。当第二接线w2的电压电平小于预定阈值时,每一整流电路4切断其中电流从对应第二垫p2流到第一垫p1的信号路径。当第二接线w2的电压电平等于或高于阈值时,每一整流电路4允许电流在信号路径中从对应第二垫p2中流到对应第一垫p1。此外,当多个第二接线w2的电压电平小于预定阈值时,每一整流电路4切断其中电流从多个第一垫p1中的每一者流到对应第二垫p2的信号路径。当多个第二接线w2中的至少一者的电压电平等于或高于阈

值时,每一整流电路4可允许电流在信号路径中从多个第一垫p1中的至少一者流到对应第二垫p2。

36.半导体芯片通过其堆叠、通过接合线彼此连接并封装的堆叠技术已变得广泛使用。在其中堆叠的半导体芯片的数目大的情况中,当接合线连接到每一堆叠的半导体芯片的垫时,封装中的导线的数目变得过大。因此,针对相同类型的信号,多个半导体芯片的垫可在堆叠方向上彼此导通,且接合线可仅连接到代表性半导体芯片的垫,借此减小导线的数目。在此情况中,当在从控制器传输到接合线的信号中检测到缺陷时,难以从封装外部识别有缺陷的位置。

37.针对最小配置,图1中说明的半导体系统1可具备控制器3及两个半导体芯片2。在下文中,两个半导体芯片2将被称为第一半导体芯片2a及第二半导体芯片2b。举例来说,第一半导体芯片2a及第二半导体芯片2b中的每一者具有一个第一垫p1及两个第二垫p2。在本文中的下文描述中,第一半导体芯片2a中的两个第二垫p2将被称为第三垫p2a及第五垫p2c,且第二半导体芯片2b中的两个第二垫p2将被称为第四垫p2b及第六垫p2d。

38.如上文描述,控制器3及每一半导体芯片2通过第一接线w1执行信号传输。在下文描述中,用于在控制器3与第一半导体芯片2a中的第三垫p2a/第二半导体芯片2b中的第四垫p2b之间传输第一信号的第一接线w1将被称为第一接线w1a,且用于在控制器3与第一半导体芯片2a中的第五垫p2c/第二半导体芯片2b中的第六垫p2d之间传输不同于第一信号的第二信号的第一接线w1将被称为第四接线w1b。

39.如上文描述,图1中说明的半导体系统1中的每一半导体芯片2具有第一垫p1及第二接线w2。在下文中,第一半导体芯片2a中的第一垫p1将被称为第一垫p1a,且连接到第一垫p1a的第二接线w2将被称为第二接线w2a。此外,第二半导体芯片2b中的第一垫p1将被称为第二垫p1b,且连接到第二垫p1b的第二接线w2将被称为第三接线w2b。

40.如上文描述,图1中说明的半导体系统中的每一半导体芯片2具有整流电路4。在下文中,安置于第一半导体芯片2a中的第一垫p1a与第三垫p2a之间的整流电路4将被称为第一整流电路4a,且安置于第二半导体芯片2b中的第二垫p1b与第四垫p2b之间的整流电路4将被称为第二整流电路4b。此外,安置于第一半导体芯片2a中的第一垫p1a与第五垫p2c之间的整流电路4将被称为第三整流电路4c,且安置于第二半导体芯片2b中的第二垫p1b与第六垫p2d之间的整流电路4将被称为第四整流电路4d。

41.如上文描述,图1的整流电路4具有多个二极管d1及多个二极管d2,其在方向上彼此不同。在下文中,第一整流电路4a中的多个二极管d1将被称为多个第一二极管d1a,且第二整流电路4b中的多个二极管d1将被称为多个第二二极管d1b。此外,在下文中,第一整流电路4a中的多个二极管d2将被称为多个第三二极管d2a,且第二整流电路4b中的多个二极管d2将被称为多个第四二极管d2b。

42.如上文描述,第一半导体芯片2a具备第一垫p1a、第三垫p2a、第五垫p2c、具有多个第一二极管d1a及多个第三二极管d2a的第一整流电路4a及具有与第一整流电路4a的配置相同的配置的第三整流电路4c。第二半导体芯片2b具备第二垫p1b、第四垫p2b、第六垫p2d、具有多个第二二极管d1b及多个第四二极管d2b的第二整流电路4b及具有与第二整流电路4b的配置相同的配置的第四整流电路4d。控制器3通过第一接线w1a向第一半导体芯片2a及第二半导体芯片2b传输第一信号。第一半导体芯片2a通过第二接线w2a使在第一接线w1a中

流动的电流返回到控制器3。第二半导体芯片2b通过第三接线w2b使在第一接线w1a中流动的电流返回到控制器3。此外,控制器3通过第四接线w1b向第一半导体芯片2a及第二半导体芯片2b传输第二信号。第一半导体芯片2a通过第二接线w2a使在第四接线w1b中流动的电流返回到控制器3。第二半导体芯片2b通过第三接线w2b使在第四接线w1b中流动的电流返回到控制器3。

43.在根据第一实施例的半导体系统1中,为了检测用于在多个堆叠的半导体芯片2与控制器3之间传输信号的第一接线w1中的缺陷,提供用于将每一半导体芯片的第一垫p1及控制器3彼此连接的第二接线w2。接着,对应于由控制器3发送到第一接线w1的信号的电流从每一第二接线w2返回到控制器3。因此,可针对每一半导体芯片2个别地检测从控制器3侧处的第一接线w1的端到每一半导体芯片2的第二垫p2的信号路径中例如短路或断开连接的缺陷。因此,根据本实施例,多个堆叠的半导体芯片2与控制器3之间的接线路径中有缺陷的位置可被容易且准确地识别。

44.此外,在本实施例中,由于多个整流电路4被设置于第一接线w1与多个第二接线w2之间,因此仅当控制器3将具有等于或高于预定阈值的电压电平的信号供应到第一接线w1时,电流才从第一接线w1流到第二接线w2。因此,通过在不提供用于切换操作模式的开关电路的情况下简单地切换第一接线w1的电压电平,可在用于检测第一接线w1的缺陷的第一模式与用于正常操作多个半导体芯片2的第二模式之间实施切换。

45.(第二实施例)

46.在第二实施例中,提供开关电路5,而非图1的整流电路4。图2是示意性地说明根据第二实施例的半导体系统1a的主要组件的平面图。类似于图1,图2的半导体系统1a具备多个堆叠的半导体芯片2及控制器3。

47.如图2中说明,多个半导体芯片2中的每一者具有多个开关电路5,所述多个开关电路5就多种类型的第二垫p2及第一垫p1是否彼此电导通进行切换。控制器3选择多个开关电路5中的一者以使对应第二垫p2及第一垫p1彼此电导通,借此检测流过第一垫p1的电流。

48.多个开关电路5基于来自控制器3的开关控制信号sc就对应第二垫p2及第一垫p1是否彼此电导通进行切换。在控制器3与多个半导体芯片2之间,多个第一接线w1及多个第二接线w2如在第一实施例的半导体系统1中那样布置,且此外,安置用于开关控制信号sc的第三接线w3。由于开关控制信号sc能够对所有开关电路5执行开关控制,因此可提供仅一个第三接线w3。通过切换开关控制信号sc的逻辑,控制器3可就对应于所有开关电路5的第二垫p2及第一垫p1是否彼此电导通进行切换。更明确来说,控制器3可将开关控制信号sc设置为例如高电平,使得通过每一开关电路5,对应第二垫p2及第一垫p1可彼此电导通。在此情况中,对应于连接到第二垫p2的第一接线w1上的信号的电流通过第二垫p2及第一垫p1流到对应第二接线w2。

49.由于控制器3可个别地控制施加到多个第一接线w1的电压,因此可个别地检测每一第一接线w1中的例如断开连接或类似物的缺陷。在第一实施例中,具有等于或高于预定阈值的电压电平的信号在第一模式中被供应到多个第一接线w1。然而,在本实施例中,在第一及第二模式期间供应到多个第一接线w1的信号的电压电平中不存在差异。因此,促进控制器3侧处的控制。

50.多个开关电路5的特定电路配置不限于任何特定配置。图2的实例具有并联连接于

第一垫p1及第二垫p2与反相器6之间的nmos晶体管q1及pmos晶体管q2。开关控制信号sc被输入到反相器6,且反相器6的输出被输入到pmos晶体管q2的栅极。开关控制信号sc被输入到nmos晶体管q1的栅极。

51.针对最小配置,图2中说明的半导体系统1a可具备控制器3及两个半导体芯片2。在下文中,两个半导体芯片2将被称为第一半导体芯片2a’及第二半导体芯片2b’。在下文中,将集中于与图1中的第一半导体芯片2a及第二半导体芯片2b的差异来进行描述。

52.第一半导体芯片2a’具有第一开关电路5a及第二开关电路5b,而非图1的第一半导体芯片2a中的第一整流电路4a及第三整流电路4c。此外,第二半导体芯片2b’具有第三开关电路5c及第四开关电路5d,而非图1的第一半导体芯片2b中的第二整流电路4b及第四整流电路4d。第一开关电路5a就第一垫p1a及第三垫p2a是否彼此电导通进行切换。第二开关电路5b就第一垫p1a及第五垫p2c是否彼此电导通进行切换。第三开关电路5c就第二垫p1b及第四垫p2b是否彼此电导通进行切换。第四开关电路5d就第二垫p1b及第六垫p2d是否彼此电导通进行切换。控制器3使第一开关电路5a进入导通状态以使第三垫p2a及第一垫p1a彼此电导通,借此检测流过第一垫p1a的电流。控制器3使第二开关电路5b进入导通状态以使第五垫p2c及第一垫p1a彼此电导通,借此检测流过第一垫p1a的电流。控制器3使第三开关电路5c进入导通状态以使第四垫p2b及第二垫p1b彼此电导通,借此检测流过第二垫p1b的电流。控制器3使第四开关电路5d进入导通状态以使第六垫p2d及第二垫p1b彼此电导通,借此检测流过第二垫p1b的电流。

53.如上文描述,在第二实施例中,多个开关电路5设置于电连接到经布置用于在控制器3与多个半导体芯片2之间进行信号传输的多个第一接线w1的多个第二垫p2与第一垫p1之间。控制器3通过开关控制信号sc选择多个开关电路5中的一者且通过所选择的开关电路5使来自对应第一接线w1的电流返回到第二接线w2。

54.在第二实施例中,由于开关电路5就第一垫p1及第二垫p2是否彼此电导通进行切换,因此在第一模式期间多个第一接线w1的电压电平无需升高到高于在第二模式中的电压电平,使得控制器3的内部配置及控制可能不会变得复杂化。

55.此外,在图2中,针对所有开关电路5的开关控制基于从控制器3输出的共同开关控制信号sc来执行。然而,单独开关控制信号sc可针对每一开关电路5形成。在此情况中,等于开关电路5的数目的数目个第三接线w3经布置于控制器3与多个半导体芯片2之间,且通过每一第三接线w3,对应开关控制信号sc被供应到每一半导体芯片2。

56.nand快闪存储器芯片可在根据上文描述的第一及第二实施例的半导体系统1及1a中用作多个堆叠的半导体芯片2。

57.图3是说明存储器系统10的轮廓的框图,所述存储器系统10是根据第一或第二实施例的半导体系统1或1a的特定实例。图3的存储器系统10具备nand快闪存储器100、控制器200及主机装置300。nand快闪存储器100是堆叠的主体,其中堆叠多个nand快闪存储器芯片。

58.组成nand快闪存储器100的多个快闪存储器芯片中的每一者具有存储器单元阵列110。存储器单元阵列110中的每一存储器单元以非易失性方式存储数据。全部多个快闪存储器芯片都具有相同的内部配置。此外,每一快闪存储器芯片具有控制器接口(i/f)电路170。如图1及2中说明,多个第二垫p2、整流电路4或开关电路5及第一垫p1设置于控制器i/f

电路170中。第二接线w2及第一垫p1经提供用于每一快闪存储器芯片。此外,在控制器i/f电路170中,可提供图2的第三垫p3,且第三接线w3可经提供为连接到第三垫p3。

59.控制器200将各种信号传输到nand快闪存储器100/从nand快闪存储器100接收各种信号。此外,控制器200通过主机总线12连接到主机装置300。

60.控制器200及nand快闪存储器100通过多个第一接线w1及多个第二接线w2彼此连接用于传输/接收各种信号。如上文描述,多个第一接线w1传输/接收芯片启用信号cen、写入启用信号wen、读取启用信号ren、地址锁存启用信号ale、命令锁存启用信号cle及其它。

61.控制器200控制nand快闪存储器100且响应于从主机装置300接收到的命令存取nand快闪存储器100。主机装置300是例如电子装置,例如个人计算机或类似物。

62.控制器200具备主机接口(i/f)电路210、内置存储器(随机存取存储器(ram))220、处理器(中央处理单元(cpu))230、缓冲器存储器240、nand接口(i/f)电路250及错误检查及校正(ecc)电路260。

63.主机i/f电路210经由主机总线12连接到主机装置300且将从主机装置300接收到的命令及数据传送到cpu 230及缓冲器存储器240中的每一者。此外,响应于来自cpu 230的命令,主机i/f电路210将缓冲器存储器240中的数据传送到主机装置300。

64.cpu 230控制整个控制器200的操作。举例来说,当从主机装置300接收到写入命令时,cpu 230作为响应向nand i/f电路250发出写入命令。这同样适用于读取命令及擦除命令。此外,cpu 230执行用于管理nand快闪存储器100的各种过程,例如损耗均衡或类似物。另外,下文描述的控制器200的操作可以cpu执行固件的方式实施,或可由硬件实施。

65.nand i/f电路250将各种信号传输到nand快闪存储器100中的控制器i/f电路170/从控制器i/f电路170接收各种信号,以便执行与nand快闪存储器100的通信。此外,基于从cpu 230接收到的命令,nand i/f电路250向nand快闪存储器100传输各种信号及从nand快闪存储器100接收各种信号。缓冲器存储器240临时存储写入或读取数据。

66.ram 220是半导体存储器,例如动态随机存取存储器(dram)、静态随机存取存储器(sram)或类似物,且用作cpu 230的工作区域。ram 220存储用于管理nand快闪存储器100的固件、各种管理表及其它。

67.ecc电路260对将要存储于nand快闪存储器100中的数据执行错误检测过程及错误校正过程。即,针对数据写入,ecc电路260产生错误校正码(ecc)并指派所产生的ecc来写入数据。针对数据读取,ecc电路260确定在读取数据中是否存在错误,且当确定在读取数据中存在错误时,ecc电路260通过使用ecc对读取的数据执行错误校正过程。

68.接着将描述nand快闪存储器100的配置。如上文描述,除了控制器i/f电路170外,nand快闪存储器100还具备存储器单元阵列110、行解码器120、驱动器电路130、列控制电路140、寄存器组150及定序器160。

69.存储器单元阵列110具备包含与行及列相关联的多个非易失性存储器单元的多个块blk。图3说明例如四个块blk0到blk3。接着,存储器单元阵列110存储从控制器200传送的数据。

70.行解码器120选择块blk0到blk3中的一者,且在所选择的块blk中进一步选择行方向。驱动器电路130经由行解码器120向所选择的块blk供应电压。

71.在数据读取期间,列控制电路140感测从存储器单元阵列110读取的数据,并执行

必要的算术运算。接着,列控制电路140将数据输出到控制器200。在数据写入期间,列控制电路140将从控制器200接收到的写入数据传送到存储器单元阵列110。

72.寄存器组150具有地址寄存器、命令寄存器及其它。地址寄存器存储从控制器200接收到的地址。命令寄存器存储从控制器200接收到的命令。

73.定序器160基于存储于寄存器组150中的各种类型的信息控制整个nand快闪存储器100的操作。

74.如图1或2中说明,图3的nand快闪存储器100经配置有多个堆叠的快闪存储器芯片。通过增加堆叠的层的数目,可增加nand快闪存储器100的存储器容量。

75.图4是说明具有三维结构的nand快闪存储器单元阵列110的实例的电路图。图4表示具有三维结构的nand快闪存储器单元阵列110中的多个块当中的一个块blk的电路配置。nand快闪存储器单元阵列110的其它块具有与图4中说明的相同的电路配置。

76.如图4中说明,块blk具有例如四个指部fng(fng0到fng3)。此外,每一指部fng包含多个nand串ns。每一nand串ns具有级联连接的例如8个存储器单元晶体管mt(mt0到mt7)、及选择晶体管st1及st2。在本文中的描述中,每一指部fng可被称为串单元su。

77.此外,nand串ns中的存储器单元晶体管mt的数目不限于8。存储器单元晶体管mt经布置使得其电流路径串联连接于选择晶体管st1与st2之间。存储器单元晶体管mt7的电流路径在串联连接的一端处连接到选择晶体管st1的电流路径的一端,且存储器单元晶体管mt0的电流路径在串联连接的另一端处连接到选择晶体管st2的电流路径的一端。

78.相应指部fng0到fng3中的选择晶体管st1的栅极分别共同连接到选择栅极线sgd0到sgd3。同时,选择晶体管st2的栅极跨多个指部fng共同连接到同一选择栅极线sgs。此外,同一块blk中的存储器单元晶体管mt0到mt7的控制栅极分别共同耦合到字线wl0到wl7。即,虽然字线wl0到wl7及选择栅极线sgs跨同一块blk中的多个指部fng0到fng3共同连接,但即使在同一块blk中,选择栅极线sgd也分别独立地用于指部fng0到fng3。

79.字线wl0到wl7分别连接到组成nand串ns的存储器单元晶体管mt0到mt7的控制栅极电极,且同一指部fng内的相应nand串ns中的第i存储器单元晶体管mti(i=0到7)由同一字线wli(i=0到7)共同连接。即,块blk的同一行中的存储器单元晶体管mti的控制栅极电极连接到同一字线wli。

80.每一nand串ns连接到字线wli,且还连接到位线。每一nand串ns中的每一存储器单元可通过识别字线wli及选择栅极线sgd0到sgd3的地址及识别位线的地址来识别。如上文描述,同一块blk中的存储器单元(存储器单元晶体管mt)的数据被共同擦除。同时,数据读取及数据写入在物理扇区mg的单元中执行。一个物理扇区mg包含连接到一个字线wli且属于一个指部fng的多个存储器单元。

81.控制器200在连接到一个指部fng内的一个字线wli的所有nand串ns的单元中执行写入(编程)。因此,其中控制器200执行编程的数据量的单元是4个位x位线的数目。

82.在读取操作及编程操作期间,一个字线wli及一个选择栅极线sgd根据物理地址来选择,且一个物理扇区mg被选择。在本文中的描述中,在必要时,将数据写入到存储器单元被称为编程。

83.如图3及4中说明,控制器200及nand快闪存储器100传输/接收多个信号。因此,控制器200与nand快闪存储器100之间的接合线的数目增加。此外,随着配置nand快闪存储器

100的每一快闪存储器芯片微型化,堆叠的快闪存储器芯片的数目也趋向于增加。因此,当在来自控制器200的接合线中出现例如断开连接、短路或类似物的缺陷时,识别有缺陷的位置变得明显困难。

84.在根据本实施例的存储器系统10中,对应于传输到多个第一接线w1/从多个第一接线w1接收到的每一信号的电流通过第二接线w2从每一快闪存储器芯片中的第一垫p1返回到控制器200,如在根据第一及第二实施例的半导体系统1及1a中那样,使得控制器200可容易且准确地识别在个别第一接线w1中是否出现缺陷。

85.虽然已描述某些实施例,但这些实施例已仅举例来说呈现且不希望限制本公开的范围。实际上,本文中描述的新颖实施例可以各种其它形式体现;此外,可在不背离本公开的精神的情况下对本文中描述的实施例的形式作出各种省略、替代及改变。所附权利要求书及其等效物希望涵盖如将落在本公开的范围及精神内的此类形式或修改。

86.符号说明

87.1、1a:半导体系统

88.2:半导体芯片

89.3:控制器

90.4:整流电路

91.5:开关电路

92.6:反相器

93.10:存储器系统

94.12:主机总线

95.100:nand快闪存储器

96.110:存储器单元阵列

97.120:行解码器

98.130:驱动器电路

99.140:列控制电路

100.150:寄存器组

101.160:定序器

102.170:控制器i/f电路

103.200:控制器

104.210:主机接口(i/f)电路

105.220:内置存储器(随机存取存储器(ram))

106.230:处理器(中央处理单元(cpu))

107.240:缓冲器存储器

108.250:nand接口(i/f)电路

109.260:错误检查及校正(ecc)电路

110.300:主机装置。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。