存储器件

1.本技术享受以日本特许申请2021-144742号(申请日:2021年9月6日)和美国特许申请17/537395(申请日:2021年11月29日)为基础申请的优先权。本技术通过参照该基础申请而包含基础申请的全部内容。

技术领域

2.实施方式涉及存储器件。

背景技术:

3.已知使用阻变元件来作为存储元件的存储器件。阻变元件与开关元件串联连接而作为存储单元发挥功能。开关元件可使用两端子型的开关元件。

技术实现要素:

4.本发明要解决的技术问题在于提供能够抑制开关元件的劣化的存储器件。

5.实施方式的存储器件具备:存储单元,其包括串联连接的阻变元件和开关元件;和控制电路。上述控制电路构成为执行第1动作、第2动作以及第3动作,上述第1动作是基于第1电流使上述阻变元件为第1电阻值的动作,上述第2动作是基于第2电流使上述阻变元件为与上述第1电阻值不同的第2电阻值的动作,上述第3动作是基于第3电流判定上述阻变元件是为上述第1电阻值、还是为上述第2电阻值的动作。上述控制电路构成为在至少一个动作中,向上述存储单元交替地流动具有互不相同的极性的两个电流。

附图说明

6.图1是表示包括第1实施方式涉及的存储器件的存储系统的构成的一个例子的框图。

7.图2是表示第1实施方式涉及的存储单元阵列的电路结构的一个例子的电路图。

8.图3是表示第1实施方式涉及的阻变元件的构成的一个例子的剖视图。

9.图4是表示第1实施方式涉及的存储器件中的一系列动作的一个例子的流程图。

10.图5是表示第1实施方式涉及的存储器件中的写入动作的一个例子的时序图。

11.图6是表示第1实施方式涉及的存储器件中的写入动作的一个例子的时序图。

12.图7是表示第1实施方式涉及的存储器件中的读取动作的一个例子的时序图。

13.图8是表示第1实施方式的变形例涉及的存储器件中的一系列动作的一个例子的流程图。

14.图9是表示第1实施方式的变形例涉及的存储器件中的伴随着读取动作的写入动作的第1例的时序图。

15.图10是表示第1实施方式的变形例涉及的存储器件中的伴随着读取动作的写入动作的第2例的时序图。

16.图11是表示第1实施方式的变形例涉及的存储器件中的伴随着读取动作的写入动

作的第3例的时序图。

17.图12是表示第2实施方式涉及的存储器件中的一系列动作的一个例子的流程图。

18.图13是表示第2实施方式涉及的存储器件中的写入动作的一个例子的时序图。

19.图14是表示第2实施方式涉及的存储器件中的写入动作的一个例子的时序图。

20.图15是表示第2实施方式涉及的存储器件中的读取动作的一个例子的时序图。

21.图16是表示第2实施方式的变形例涉及的存储器件中的一系列动作的一个例子的流程图。

22.图17是表示第2实施方式的变形例涉及的存储器件中的伴随着读取动作的写入动作的第1例的时序图。

23.图18是表示第2实施方式的变形例涉及的存储器件中的伴随着读取动作的写入动作的第2例的时序图。

24.图19是表示第2实施方式的变形例涉及的存储器件中的伴随着读取动作的写入动作的第3例的时序图。

25.图20是表示第2实施方式的变形例涉及的存储器件中的伴随着读取动作的写入动作的第4例的时序图。

26.图21是表示第3实施方式涉及的存储器件中的一系列动作的一个例子的流程图。

27.图22是表示第4实施方式涉及的存储器件中的一系列动作的一个例子的流程图。

28.图23是表示第5实施方式涉及的存储控制器的构成的一个例子的框图。

29.图24是表示第5实施方式涉及的存储控制器中的一系列动作的一个例子的流程图。

30.图25是表示第5实施方式涉及的存储器件中的刷新动作的一个例子的时序图。

31.图26是表示第5实施方式的变形例涉及的存储控制器中的一系列动作的一个例子的流程图。

32.图27是表示其他变形例涉及的存储器件中的写入动作的一个例子的时序图。

33.图28是表示其他变形例涉及的存储器件中的写入动作的一个例子的时序图。

34.图29是表示其他变形例涉及的存储器件中的写入动作的一个例子的时序图。

35.图30是表示其他变形例涉及的存储器件中的写入动作的一个例子的时序图。

36.标号说明

37.1存储系统;2存储器件;3存储控制器;3a正选择数;3b负选择数;10存储单元阵列;11行选择电路;12列选择电路;13译码电路;14写入电路;15读出电路;16电压生成电路;17输入输出电路;18控制电路;21、23铁磁性层;22非磁性层。

具体实施方式

38.以下,参照附图对几个实施方式进行说明。此外,在以下的说明中,对具有相同的功能和结构的构成要素赋予共同的参照标号。另外,在对具有共同的参照标号的多个构成要素进行区别的情况下,对该共同的参照标号附加后缀来进行区别。

39.1.第1实施方式

40.对第1实施方式进行说明。

41.1.1构成

42.1.1.1存储系统

43.首先,对包括第1实施方式涉及的存储器件的存储系统的构成进行说明。图1是表示包括第1实施方式涉及的存储器件的存储系统的构成的一个例子的框图。

44.存储系统1为存储装置。存储系统1执行数据的写入动作和读取动作。存储系统1包括存储器件2和存储控制器3。

45.存储器件2例如为磁存储器件(mram:magnetoresistive random access memory)。存储器件2以非易失的方式存储数据。存储器件2包括磁阻效应元件来作为存储元件。磁阻效应元件是通过磁隧道结(mtj:magnetic tunnel junction)来具有磁阻效应(magnetoresistance effect)的阻变元件的一种。磁阻效应元件也被称为mtj元件。

46.存储控制器3例如由如soc(system-on-a-chip,片上系统)那样的集成电路构成。存储控制器3根据来自外部的未图示的主机设备的要求,对存储器件2执行写入动作和读取动作等。在写入动作时,存储控制器3向存储器件2发送要写入的数据。另外,在读取动作时,存储控制器3接收从存储器件2读出的数据。

47.1.1.2存储器件

48.下面,接着参照图1对第1实施方式涉及的存储器件的内部构成进行说明。

49.存储器件2具备存储单元阵列10、行选择电路11、列选择电路12、译码电路13、写入电路14、读出电路15、电压生成电路16、输入输出电路17以及控制电路18。

50.存储单元阵列10是存储器件2中的数据的存储部。存储单元阵列10具备多个存储单元mc。多个存储单元mc各自与行(row)和列(column)的组相关联。处于同一行的存储单元mc连接于相同的字线wl,处于同一列的存储单元mc连接于相同的位线bl的组。

51.行选择电路11是对存储单元阵列10的行进行选择的电路。行选择电路11经由字线wl而与存储单元阵列10连接。来自译码电路13的地址add的译码结果(行地址)被提供给行选择电路11。行选择电路11对与基于了地址add的译码结果的行对应的字线wl进行选择。在以下中,所被选择了的字线wl称为选择字线wl。另外,选择字线wl以外的字线wl称为非选择字线wl。

52.列选择电路12是对存储单元阵列10的列进行选择的电路。列选择电路12经由位线bl而与存储单元阵列10连接。来自译码电路13的地址add的译码结果(列地址)被提供给列选择电路12。列选择电路12对与基于了地址add的译码结果的列对应的位线bl进行选择。在以下中,所被选择了的位线bl称为选择位线bl。另外,选择位线bl以外的位线bl称为非选择位线bl。

53.此外,由选择字线wl和选择位线bl确定了的存储单元mc称为选择存储单元mc。选择存储单元mc以外的存储单元mc称为非选择存储单元mc。能够经由选择字线wl和选择位线bl来向选择存储单元mc流动预定电流。

54.译码电路13是对来自输入输出电路17的地址add进行译码的译码器。译码电路13向行选择电路11和列选择电路12提供地址add的译码结果。地址add包括所被选择的列地址和行地址。

55.写入电路14例如包括写入驱动器(未图示)。写入电路14在写入动作中向存储单元mc写入数据。

56.读出电路15例如包括感测放大器(未图示)。读出电路15在读取动作中从存储单元

mc读出数据。

57.电压生成电路16使用从存储器件2的外部(未图示)提供的电源电压,生成用于存储单元阵列10的各种动作的电压。例如,电压生成电路16生成写入动作时所需要的各种电压,并输出给写入电路14。另外,例如电压生成电路16生成读取动作时所需要的各种电压,并输出至读出电路15。

58.输入输出电路17负责与存储控制器3的通信。输入输出电路17向译码电路13传送来自存储控制器3的地址add。输入输出电路17向控制电路18传送来自存储控制器3的命令cmd。输入输出电路17在存储控制器3与控制电路18之间收发各种控制信号cnt。输入输出电路17向写入电路14传送来自存储控制器3的数据dat。输入输出电路17向存储控制器3输出从读出电路15传送了的数据dat。

59.控制电路18例如包括如cpu(central processing unit,中央处理单元)那样的处理器和rom(read only memory,只读存储器)。控制电路18基于控制信号cnt和命令cmd,对存储器件2内的行选择电路11、列选择电路12、译码电路13、写入电路14、读出电路15、电压生成电路16以及输入输出电路17的动作进行控制。

60.1.1.3存储单元阵列

61.接着,对第1实施方式涉及的存储器件的存储单元阵列的电路结构进行说明。

62.图2是表示第1实施方式涉及的存储单元阵列的电路结构的一个例子的电路图。在图2中,字线wl和位线bl各自由包括索引(“<>”)的后缀来分类并进行表示。

63.存储单元阵列10包括多个存储单元mc、多条字线wl以及多条位线bl。在图2的例子中,多个存储单元mc包括(m 1)

×

(n 1)个存储单元mc<0,0>、mc<0,1>、

……

、mc<0,n>、mc<1,0>、

……

、以及mc<m,n>(m和n为2以上的整数)。此外,在图2的例子中,示出了m和n为2以上的整数的情况,但不限于此。m和n也可以是0或者1。多条字线wl包括(m 1)条字线wl<0>、wl<1>、

……

、以及wl<m>。多条位线bl包括(n 1)条位线bl<0>、bl<1>、

……

、以及bl<n>。

64.多个存储单元mc被配置为矩阵状。存储单元mc与一条字线wl和一条位线bl的组相关联。即,存储单元mc<i,j>(0≤i≤m、0≤j≤n)连接于字线wl<i>、位线bl<j>。存储单元mc<i,j>包括开关元件sw<i,j>和阻变元件se<i,j>。开关元件sw<i,j>和阻变元件se<i,j>串联连接。

65.开关元件sw为两端子型的开关元件。两端子型的开关元件在不包括第3个端子这一点与晶体管等的三端子型的开关元件不同。更具体而言,例如在被施加于所对应的存储单元mc的电压小于阈值电压vth的情况下,开关元件sw作为电阻值大的绝缘体而将电流切断(成为断开状态)。在被施加于所对应的存储单元mc的电压为阈值电压vth以上的情况下,开关元件sw作为电阻值小的导电体而使电流流动(成为导通状态)。开关元件sw无论被施加于两端子间的电压是什么极性(不依赖于流动的电流的方向),都根据被施加于所对应的存储单元mc的电压的大小,对使电流流动或者将电流切断进行切换。

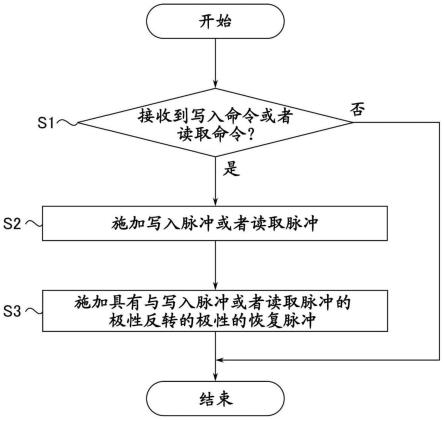

66.通过如以上那样的构成,当存储单元mc被选择时,选择存储单元mc内的开关元件sw成为导通状态。由此,能够向选择存储单元mc内的阻变元件se流动电流。

67.阻变元件se为存储元件。阻变元件se能够基于开关元件sw为导通状态时流动的电流,将电阻值切换为低电阻状态和高电阻状态。阻变元件se通过该电阻状态的变化,以非易

失的方式存储数据。

68.1.1.4阻变元件

69.接着,对第1实施方式涉及的阻变元件的构成进行说明。

70.图3是表示第1实施方式涉及的阻变元件的构成的一个例子的剖视图。在图3中示出阻变元件se为磁阻效应元件(mtj元件)的情况下的构成的一个例子。在为磁阻效应元件的情况下,阻变元件se包括铁磁性层21、非磁性层22以及铁磁性层23。铁磁性层21、非磁性层22以及铁磁性层23层叠在半导体基板(未图示)的上方。

71.铁磁性层21为具有铁磁性的导电膜。铁磁性层21被作为存储层(storage layer)来使用。铁磁性层21在与层叠面垂直的方向上具有易磁化轴方向。铁磁性层21的磁化方向为可变。铁磁性层21含有铁(fe)。铁磁性层21也可以还含有钴(co)和镍(ni)中的至少一种元素。另外,铁磁性层21也可以还含有硼(b)。更具体而言,例如铁磁性层21也可以含有铁钴硼(fecob)或者硼化铁(feb)。

72.在铁磁性层21的膜面上设置有非磁性层22。非磁性层22为具有非磁性的绝缘膜。非磁性层22被作为隧道势垒层(tunnel barrier layer)来使用。非磁性层22设置在铁磁性层21与铁磁性层23之间,与这些两个铁磁性层一起形成磁隧道结。另外,非磁性层22在铁磁性层21的结晶化处理中也作为成为用于使结晶质的膜从与铁磁性层21的界面开始成长的核的种材料来发挥功能。非磁性层22具有膜面取向为(001)面的nacl结晶构造。非磁性层22例如含有氧化镁(mgo)。

73.对于非磁性层22,在位于与设置有铁磁性层21的膜面相反一侧的非磁性层22的膜面上设置有铁磁性层23。铁磁性层23为具有铁磁性的导电膜。铁磁性层23被作为参考层(reference layer)来使用。铁磁性层23在与膜面垂直的方向上具有易磁化轴方向。铁磁性层23的磁化方向被固定。在图3的例子中,铁磁性层23的磁化方向朝向铁磁性层21的方向。此外,“磁化方向被固定”意味着磁化方向不根据能够使铁磁性层21的磁化方向反转的大小的力矩而变化。铁磁性层23例如含有从钴铂(copt)、钴镍(coni)以及钴钯(copd)中选择的至少一种化合物。

74.磁阻效应元件能够根据存储层和参考层的磁化方向的相对关系是为平行、还是为反平行,取低电阻状态和高电阻状态中的任一状态。在以下中,对使用自旋注入写入方式来作为使磁阻效应元件的电阻状态变化的方式的情况进行说明。在自旋注入写入方式中,通过向磁阻效应元件流动写入电流,产生自旋力矩。并且,通过所产生的自旋力矩,对相对于参考层的磁化方向的存储层的磁化方向进行控制。

75.当从存储层朝向参考层(在图3中的箭头a1的方向上)来向磁阻效应元件流动写入电流iw0时,存储层和参考层的磁化方向的相对关系成为平行。在平行状态的情况下,磁阻效应元件被设定为低电阻状态。低电阻状态例如与数据“0”相关联。低电阻状态也被称为“p(parallel)状态”。

76.另外,当从参考层朝向存储层(在图3中的箭头a2的方向上)来向磁阻效应元件流动比写入电流iw0大的写入电流iw1时,存储层和参考层的磁化方向的相对关系成为反平行。在反平行状态的情况下,磁阻效应元件被设定为高电阻状态。高电阻状态例如与数据“1”相关联。高电阻状态也被称为“ap(anti-parallel)状态”。

77.另外,当向磁阻效应元件流动读出电流ir时,存储层和参考层的磁化方向不变化。

读出电路15基于读出电流ir,判定磁阻效应元件的电阻状态是为p状态、还是为ap状态。由此,读出电路15能够从存储单元mc读出数据。

78.在以下中,为了便于说明,将用于在箭头a1的方向上流动电流的信号的极性作为正(positive)。将用于在箭头a2的方向上流动电流的信号的极性作为负(negative)。读出电流ir的极性设为正。

79.此外,电阻状态与数据的对应关系不限定于上述的例子。例如,p状态和ap状态也可以分别与数据“1”和“0”相关联。另外,读出电流ir的极性也可以为负。

80.1.2动作

81.接着,对第1实施方式涉及的存储器件中的一系列动作进行说明。例如根据来自存储控制器3的命令,执行存储器件2中的一系列动作。

82.1.2.1流程图

83.图4是表示第1实施方式涉及的存储器件中的一系列动作的一个例子的流程图。

84.当从存储控制器3接收命令时(开始),存储器件2的控制电路18判定所接收到的命令是否为写入命令或者读取命令(s1)。

85.在所接收到的命令为写入命令或者读取命令的情况下(s1;是),行选择电路11和列选择电路12向选择存储单元mc施加写入脉冲或者读取脉冲(s2)。具体而言,在所接收到的命令为写入命令的情况下,行选择电路11和列选择电路12向选择存储单元mc施加写入脉冲。在所接收的命令为读取命令的情况下,行选择电路11和列选择电路12向选择存储单元mc施加读取脉冲。

86.在s2的处理之后,行选择电路11和列选择电路12向选择存储单元mc施加具有与写入脉冲或者读取脉冲的极性反转的极性的恢复(recovery)脉冲(s3)。具体而言,在s2的处理中施加了写入脉冲的情况下,行选择电路11和列选择电路12向选择存储单元mc施加具有与写入脉冲的极性反转的极性的恢复脉冲。在s2的处理中施加了读取脉冲的情况下,行选择电路11和列选择电路12向选择存储单元mc施加具有与读取脉冲的极性反转的极性的恢复脉冲。

87.在s3的处理之后或者在所接收到的命令不为写入命令和读取命令中的任何命令的情况下(s1;否),存储器件2中的一系列动作成为结束(结束,end)。

88.此外,脉冲是指在有限的期间中被施加于选择存储单元mc的信号。脉冲包括被施加于选择存储单元mc的电压信号。脉冲包括根据电压信号而在选择存储单元mc中流动的电流信号。

89.1.3.2时序图

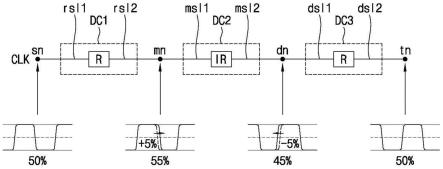

90.图5和图6是表示第1实施方式涉及的存储器件中的写入动作的一个例子的时序图。图7是表示第1实施方式涉及的存储器件中的读取动作的一个例子的时序图。图5所示的写入动作与使阻变元件se为p状态的动作(数据“0”的写入动作)对应。图6所示的写入动作与使阻变元件se为ap状态的动作(数据“1”的写入动作)对应。

91.在写入数据“0”的情况下,选择存储单元mc内的开关元件sw通过被施加写入电压vw0(未图示)而成为导通状态。由此,在整个期间(跨期间)dw0对选择存储单元mc施加写入电流iw0。之后,选择存储单元mc内的开关元件sw通过被施加电压vrec_w0(未图示)而成为导通状态。由此,在整个期间drec_w0对选择存储单元mc施加电流irec_w0。期间dw0与期

间drec_w0之间的期间可以设为任意长度。相对于写入电流iw0具有正极性,电流irec_w0具有负极性。

92.在写入数据“1”的情况下,选择存储单元mc内的开关元件sw通过被施加写入电压vw1(未图示)而成为导通状态。由此,在整个期间dw1对选择存储单元mc施加写入电流iw1。之后,选择存储单元mc内的开关元件sw通过被施加电压vrec_w1(未图示)而成为导通状态。由此,在整个期间drec_w1施加电流irec_w1。期间dw1与期间drec_w1之间的期间可以设为任意长度。写入电流iw1比写入电流iw0大,并且,具有与写入电流iw0反转的极性。期间dw1比期间dw0长。相对于写入电流iw1具有负极性,电流irec_w1具有正极性。

93.在读出数据的情况下,选择存储单元mc内的开关元件sw通过被施加读出电压vr(未图示)而成为导通状态。由此,在整个期间dr对选择存储单元mc施加读出电流ir。之后,选择存储单元mc内的开关元件sw通过被施加电压vrec_r(未图示)而成为导通状态。由此,在整个期间drec_r施加电流irec_r。期间dr与期间drec_r之间的期间可以设为任意长度。读出电流ir比写入电流iw0以及iw1小。期间dr比期间dw0以及dw1短。相对于读出电流ir具有正极性,电流irec_r具有负极性。

94.电流irec_w0、irec_w1以及irec_r各自比写入电流iw0以及iw1小。电流irec_w0、irec_w1以及irec_r各自也可以比读出电流ir小。电流irec_w0、irec_w1以及irec_r也可以彼此相等。电流irec_w0、irec_w1以及irec_r也可以彼此不同。

95.期间drec_w0、drec_w1以及drec_r各自比期间dw0以及dw1短。期间drec_w0、drec_w1以及drec_r各自也可以比期间dr短。期间drec_w0、drec_w1以及drec_r也可以彼此相等。期间drec_w0、drec_w1以及drec_r也可以彼此不同。

96.另外,电压vrec_w0、vrec_w1以及vrec_r各自比写入电压vw0以及vw1小。电压vrec_w0、vrec_w1以及vrec_r各自也可以比读出电压vr小。电压vrec_w0、vrec_w1以及vrec_r也可以彼此相等。电压vrec_w0、vrec_w1以及vrec_r也可以彼此不同。

97.1.3第1实施方式涉及的效果

98.根据第1实施方式,存储器件2在数据“0”的写入动作中,将具有互不相同的极性的电流iw0和irec_w0交替地按该顺序施加于选择存储单元mc。存储器件2在数据“1”的写入动作中,将具有互不相同的极性的电流iw1和irec_w1交替地按该顺序施加于选择存储单元mc。存储器件2在读取动作中,将具有互不相同的极性的电流ir和irec_r交替地按该顺序施加于选择存储单元mc。由此,每当执行写入动作和读取动作时,能够通过具有互不相同的极性的两个信号使选择存储单元mc内的开关元件sw交替地为导通状态。因此,能够抑制使开关元件sw为导通状态的信号的极性偏于正和负中的一方。因此,能够对开关元件sw的耐久性的劣化进行抑制。

99.1.4第1实施方式的变形例

100.此外,在上述的第1实施方式中,对在全部的写入动作和读取动作中施加恢复脉冲的情况进行了说明,但不限于此。例如,在预先知道写入动作和读取动作的执行顺序的情况下,也可以省略恢复脉冲。

101.1.4.1流程图

102.图8是表示第1实施方式的变形例涉及的存储器件中的一系列动作的一个例子的流程图。

103.当从存储控制器3接收命令时(开始),控制电路18判定所接收到的命令是否为写入命令(s11)。

104.在所接收到的命令不为写入命令的情况下(s11;否),存储器件2中的一系列动作成为结束(结束)。

105.在所接收到的命令为写入命令的情况下(s11;是),控制电路18在写入动作之前执行读取动作。行选择电路11和列选择电路12向选择存储单元mc施加读取脉冲(s12)。

106.读出电路15基于在s12的处理中所施加了的读取脉冲,从选择存储单元mc读出数据。控制电路18判定所读出的数据与通过所接收到的写入命令来所要写入的数据是否不同(s13)。

107.在所读出的数据与所要写入的数据一致的情况下(s13;否),行选择电路11和列选择电路12向选择存储单元mc施加具有与读取脉冲的极性反转的极性的恢复脉冲(s14)。在s14的处理之后,存储器件2中的一系列动作成为结束(结束)。

108.在所读出的数据与所要写入的数据不同的情况下(s13;是),控制电路18判定与所要写入的数据对应的写入脉冲的极性是否与所读出的数据所对应的读取脉冲的极性相同(s15)。

109.在写入脉冲的极性与读取脉冲的极性不同的情况下(s15;否),行选择电路11和列选择电路12向选择存储单元mc施加写入脉冲(s16)。在s16的处理之后,存储器件2中的一系列动作成为结束(结束)。

110.在写入脉冲的极性与读取脉冲的极性相同的情况下(s15;是),行选择电路11和列选择电路12施加具有与读取脉冲的极性反转的极性的恢复脉冲(s17)。

111.在s17的处理之后,行选择电路11和列选择电路12向选择存储单元mc施加写入脉冲(s18)。

112.在s18的处理之后,行选择电路11和列选择电路12向选择存储单元mc施加具有与写入脉冲的极性反转的极性的恢复脉冲(s19)。在s19的处理之后,存储器件2中的一系列动作成为结束(结束)。

113.1.5.2时序图

114.图9是表示第1实施方式的变形例涉及的存储器件中的伴随着读取动作的写入动作的第1例的时序图。图10是表示第1实施方式的变形例涉及的存储器件中的伴随着读取动作的写入动作的第2例的时序图。图11是表示第1实施方式的变形例涉及的存储器件中的伴随着读取动作的写入动作的第3例的时序图。第1例对应于所读出的数据与所要写入的数据相同的情况。第2例对应于所读出的数据与所要写入的数据不同、且写入脉冲的极性与读取脉冲的极性相同的情况。第3例对应于所读出的数据与所要写入的数据不同、且写入脉冲的极性与读取脉冲的极性不同的情况。

115.在第1例~第3例的任何例子中都首先在整个期间dr对选择存储单元mc施加读出电流ir。

116.在第1例中,与所要写入的数据相同的数据已经存储于选择存储单元mc。即,不需要施加写入脉冲。因此,在期间dr之后,在整个期间drec_r对选择存储单元mc施加电流irec_r。并且,写入脉冲和接在写入脉冲后面的恢复脉冲被省略。

117.在第2例子中例如设想如下情况:相对于所读出的数据为“1”,所要写入的数据为“0”。即,在第2例中,对选择存储单元mc施加具有与读取脉冲的极性相同的正极性的写入脉冲。因此,在期间dr之后,在整个期间drec_r对选择存储单元mc施加电流irec_r。并且,在期间drec_r之后,在整个期间dw0对选择存储单元mc施加了写入电流iw0之后,在整个期间drec_w0对选择存储单元mc施加电流irec_w0。

118.在第3例中例如设想如下情况:相对于所读出的数据为“0”,所要写入的数据为“1”。即,在第3例中,对选择存储单元mc施加具有与读取脉冲的极性不同的负极性的写入脉冲。因此,接在读取脉冲后面的恢复脉冲和接在写入脉冲后面的恢复脉冲被省略。并且,在期间dr之后,在整个期间dw1对选择存储单元mc施加写入电流iw1。

119.1.4.3第1实施方式的变形例涉及的效果

120.根据第1实施方式的变形例,存储器件2在写入动作之前执行读取动作。由此,能够省略不需要的写入动作。另外,在需要写入动作的情况下,当读取脉冲的极性和写入脉冲的极性互不相同时,存储器件2省略预定在该读取脉冲与写入脉冲之间的恢复脉冲(接在读取脉冲后面的恢复脉冲)和接着写入脉冲后面的恢复脉冲。由此,能够在省略不需要的恢复动作的同时,横跨连续的读取动作和写入动作而抑制相同极性的脉冲连续。因此,能够抑制开关元件的耐久性的劣化。

121.2.第2实施方式

122.接着,对第2实施方式进行说明。第2实施方式在恢复脉冲与写入脉冲以及读取脉冲的执行顺序成为相反这一点与第1实施方式不同。在以下中,主要对与第1实施方式不同的构成和动作进行说明。关于与第1实施方式同等的构成和动作,适当省略说明。

123.2.1流程图

124.图12是表示第2实施方式涉及的存储器件中的一系列动作的一个例子的流程图。图12与第1实施方式中的图4对应。

125.当从存储控制器3接收命令时(开始),控制电路18判定所接收到的命令是否为写入命令或者读取命令(s21)。

126.在所接收到的命令为写入命令或者读取命令的情况下(s21;是),行选择电路11和列选择电路12向选择存储单元mc施加具有与写入脉冲或者读取脉冲的极性反转的极性的恢复脉冲(s22)。具体而言,在所接收到的命令为写入命令的情况下,行选择电路11和列选择电路12向选择存储单元mc施加具有与根据该写入命令施加的写入脉冲的极性反转的极性的恢复脉冲。在所接收到的命令为读取命令的情况下,行选择电路11和列选择电路12向选择存储单元mc施加具有与根据该读取命令施加的读取脉冲的极性反转的极性的恢复脉冲。

127.在s22的处理之后,行选择电路11和列选择电路12向选择存储单元mc施加写入脉冲或者读取脉冲(s23)。具体而言,在所接收到的命令为写入命令的情况下,行选择电路11和列选择电路12向选择存储单元mc施加写入脉冲。在所接收到的命令为读取命令的情况下,行选择电路11和列选择电路12向选择存储单元mc施加读取脉冲。

128.在s23的处理之后或者在所接收到的命令不是写入命令和读取命令的任何命令的情况下(s21;否),存储器件2中的一系列动作成为结束(结束)。

129.2.2时序图

130.图13和图14是表示第2实施方式涉及的存储器件中的写入动作的一个例子的时序

图。图15是表示第2实施方式涉及的存储器件中的读取动作的一个例子的时序图。图13~图15分别与第1实施方式中的图5~图7对应。

131.在写入数据“0”的情况下,在整个期间drec_w0向选择存储单元mc施加了写入电流irec_w0之后,在整个期间dw0向选择存储单元mc施加电流iw0。

132.在写入数据“1”的情况下,在整个期间drec_w1向选择存储单元mc施加了写入电流irec_w1之后,在整个期间dw1向选择存储单元mc施加电流iw1。

133.在读出数据的情况下,在整个期间drec_r向选择存储单元mc施加了读出电流irec_r之后,在整个期间dr向选择存储单元mc施加电流ir。

134.2.3第2实施方式涉及的效果

135.根据第2实施方式,存储器件2在数据“0”的写入动作中将具有互不相同的极性的电流irec_w0和iw0交替地按该顺序施加于选择存储单元mc。存储器件2在数据“1”的写入动作中,将具有互不相同的极性的电流irec_w1和iw1交替地按该顺序施加于选择存储单元mc。存储器件2在读取动作中,将具有互不相同的极性的电流irec_r和ir交替地按该顺序施加于选择存储单元mc。由此,与第1实施方式同样地,每当执行写入动作和读取动作时,能够通过具有互不相同的极性的两个信号使选择存储单元mc内的开关元件sw交替地为导通状态。因此,能够对开关元件sw的耐久性的劣化进行抑制。

136.2.4第2实施方式的变形例

137.此外,在上述的第2实施方式中,对在全部的写入动作和读取动作中施加恢复脉冲的情况进行了说明,但不限于此。例如,与第1实施方式的变形例同样地,在预先知道写入动作和读取动作的执行顺序的情况下,也可以省略恢复脉冲。

138.2.4.1流程图

139.图16是表示第2实施方式的变形例涉及的存储器件中的一系列动作的一个例子的流程图。图16与第1实施方式的变形例中的图8对应。

140.当从存储控制器3接收命令时(开始),控制电路18判定所接收到的命令是否为写入命令(s31)。

141.在所接收到的命令不为写入命令的情况下(s31;否),存储器件2中的一系列动作成为结束(结束)。

142.在所接收到的命令为写入命令的情况下(s31;是),控制电路18判定与所要写入的数据对应的写入脉冲的极性是否与所读出的数据所对应的读取脉冲的极性相同(s32)。

143.在写入脉冲的极性与读取脉冲的极性相同的情况下(s32;是),行选择电路11和列选择电路12向选择存储单元mc施加具有与读取脉冲的极性反转的极性的恢复脉冲(s33)。

144.在写入脉冲的极性与读取脉冲的极性不同的情况下(s32;否)或者在s33的处理之后,行选择电路11和列选择电路12向选择存储单元mc施加读取脉冲(s34)。

145.读出电路15基于在s34的处理中所施加了的读取脉冲,从选择存储单元mc读出数据。控制电路18判定所读出的数据是否与通过所接收到的写入命令来所要写入的数据不同(s35)。

146.在所读出的数据与所要写入的数据一致的情况下(s35;否),控制电路18判定与所要写入的数据对应的写入脉冲的极性是否与所读出的数据所对应的读取脉冲的极性相同(s36)。

147.在写入脉冲的极性与读取脉冲的极性相同的情况下(s36;是),存储器件2中的一系列动作成为结束(结束)。

148.在写入脉冲的极性与读取脉冲的极性不同的情况下(s36;否),行选择电路11和列选择电路12向选择存储单元mc施加具有与读取脉冲的极性反转的极性的恢复脉冲(s37)。在s37的处理之后,存储器件2中的一系列动作成为结束(结束)。

149.在所读出的数据与所要写入的数据不同的情况下(s35;是),控制电路18判定与所要写入的数据对应的写入脉冲的极性是否与所读出的数据所对应的读取脉冲的极性相同(s38)。

150.在写入脉冲的极性与读取脉冲的极性相同的情况下(s38;是),行选择电路11和列选择电路12施加具有与写入脉冲的极性反转的极性的恢复脉冲(s39)。

151.在写入脉冲的极性与读取脉冲的极性不同的情况下(s38;否)或者在s39的处理之后,行选择电路11和列选择电路12向选择存储单元mc施加写入脉冲(s40)。

152.在s40的处理之后,存储器件2中的一系列动作成为结束(结束)。

153.2.4.2时序图

154.图17是表示第2实施方式的变形例涉及的存储器件中的伴随着读取动作的写入动作的第1例的时序图。图18是表示第2实施方式的变形例涉及的存储器件中的伴随着读取动作的写入动作的第2例的时序图。图19是表示第2实施方式的变形例涉及的存储器件中的伴随着读取动作的写入动作的第3例的时序图。图20是表示第2实施方式的变形例涉及的存储器件中的伴随着读取动作的写入动作的第4例的时序图。图17和图18与第1实施方式的变形例中的图9对应。图19和图20分别与第1实施方式的变形例中的图10和图11对应。

155.在第1例~第4例的任何例子中均首先判定读取脉冲的极性与写入脉冲的极性是一致、还是不同。

156.在第1例和第3例子中设想所要写入的数据为“0”的情况。即,在第1例和第3例中,被施加于选择存储单元mc的写入脉冲的极性与读取脉冲的极性一致。因此,在整个期间drec_r向选择存储单元mc施加了电流irec_r之后,在整个期间dr向选择存储单元mc施加读出电流ir。

157.在第2例和第4例中设想所要写入的数据为“1”的情况。即,在第2例和第4例中,被施加于选择存储单元mc的写入脉冲的极性与读取脉冲的极性不同。因此,先于读取脉冲的恢复脉冲被省略。因此,在整个期间dr对选择存储单元mc施加读出电流ir。

158.在施加了读取脉冲之后,判定所读出的数据与通过所接收到的写入命令来所要写入的数据是否不同。

159.在第1例中,与所要写入的数据相同的数据“0”已经被存储于选择存储单元mc。即,不需要施加写入脉冲。因此,在期间dr之后,先于写入脉冲的恢复脉冲和写入脉冲被省略。

160.在第2例中,与所要写入的数据相同的数据“1”已经被存储于选择存储单元mc。即,不需要施加写入脉冲,另一方面,要求施加与读取脉冲对应的恢复脉冲。因此,在期间dr之后,先于写入脉冲的恢复脉冲和写入脉冲被省略。并且,在整个期间drec_r对选择存储单元mc施加电流irec_r。

161.在第3例中例如设想如下情况:相对于所读出了的数据为“1”,所要写入的数据为“0”。即,在第3例中,对选择存储单元mc施加具有与读取脉冲的极性相同的正极性的写入脉

冲。因此,在期间dr之后,在整个期间drec_w0对选择存储单元mc施加电流irec_w0之后,在整个期间dw0对选择存储单元mc施加写入电流iw0。

162.在第4例中例如设想如下情况:相对于所读出的数据为“0”,所要写入的数据为“1”。即,在第4例中,对存储单元mc施加具有与读取脉冲的极性不同的负的极性的写入脉冲。因此,先于写入脉冲的恢复脉冲被省略。并且,在期间dr之后,在整个期间dw1对选择存储单元mc施加写入电流iw1。

163.2.4.3第2实施方式的变形例涉及的效果

164.根据第2实施方式的变形例,存储器件2在写入动作之前执行读取动作。由此,能够省略不需要的写入动作。另外,在读取脉冲的极性与写入脉冲的极性互不相同的情况下,存储器件2省略预定在先于该读取脉冲的恢复脉冲以及读取脉冲与写入脉冲之间的恢复脉冲(先于写入脉冲的恢复脉冲)。由此,能够在省略不需要的恢复动作的同时,跨连续的读取动作和写入动作而抑制相同极性的脉冲连续。因此,能够抑制开关元件的耐久性的劣化。

165.3.第3实施方式

166.接着,对第3实施方式进行说明。第3实施方式与第1实施方式的不同点在于,在写入数据“1”的写入脉冲之前施加与该写入脉冲对应的恢复脉冲。在以下中,主要对与第1实施方式和第2实施方式不同的构成和动作进行说明。关于与第1实施方式和第2实施方式同等的构成和动作,适当省略说明。

167.3.1流程图

168.图21是表示第3实施方式涉及的存储器件中的一系列动作的一个例子的流程图。图21与第1实施方式中的图4对应。

169.当从存储控制器3接收命令时(开始),控制电路18判定所接收到的命令是否为满足条件a的写入命令或者读取命令(s41)。条件a是指写入命令对应于具有与读取脉冲的极性相同的极性的写入脉冲。

170.在所接收到的命令是满足条件a的写入命令或者读取命令的情况下(s41;是),行选择电路11和列选择电路12向选择存储单元mc施加写入脉冲或者读取脉冲(s42)。

171.在s42的处理之后,行选择电路11和列选择电路12向选择存储单元mc施加具有与写入脉冲或者读取脉冲的极性反转的极性的恢复脉冲(s43)。

172.在所接收到的命令不是满足条件a的写入命令、和读取命令中的任何命令的情况下(s41;否),控制电路18判定所接收到的命令是否为满足条件b的写入命令(s44)。条件b是指写入命令对应于具有与读取脉冲的极性反转的极性的写入脉冲。

173.在所接收到的命令为满足条件b的写入命令的情况下(s44;是),行选择电路11和列选择电路12向选择存储单元mc施加具有与写入脉冲的极性反转的极性的恢复脉冲(s45)。

174.在s45的处理之后,行选择电路11和列选择电路12向选择存储单元mc施加写入脉冲(s46)。

175.在s43的处理之后、s46的处理之后或者所接收的命令不为满足条件b的写入命令的情况下(s44;no),存储器件2中的一系列动作成为结束(结束)。

176.3.2第3实施方式涉及的效果

177.根据第3实施方式,存储器件2在数据“0”的写入动作中,将具有互不相同的极性的

电流iw0和irec_w0交替地按该顺序施加于选择存储单元mc。存储器件2在数据“1”的写入动作中,将具有互不相同的极性的电流irec_w1和iw1交替地按该顺序施加于选择存储单元mc。存储器件2在读取动作中,将具有互不相同的极性的电流ir和irec_r交替地按该顺序施加于选择存储单元mc。由此,每当执行写入动作和读取动作时,通过具有互不相同的极性的两个信号使选择存储单元mc内的开关元件sw交替地为导通状态。而且,即使是在连续地执行数据“0”的写入动作或者读取动作和数据“1”的写入动作的情况下,也能够通过具有互不相同的极性的两个信号使选择存储单元mc内的开关元件sw交替地为导通状态。因此,能够抑制开关元件sw的耐久性的劣化。

178.4.第4实施方式

179.接着,对第4实施方式进行说明。第4实施方式在恢复脉冲和写入脉冲及读取脉冲的执行顺序成为相反这一点与第3实施方式不同。在以下中,主要对与第3实施方式不同的构成和动作进行说明。关于与第3实施方式同等的构成和动作,适当省略说明。

180.4.1流程图

181.图22是表示第4实施方式涉及的存储器件中的一系列动作的一个例子的流程图。图22与第3实施方式中的图21对应。

182.当从存储控制器3接收命令时(开始),控制电路18判定所接收到的命令是否为满足条件a的写入命令或者读取命令(s51)。

183.在所接收到的命令为满足条件a的写入命令或者读取命令的情况下(s51;是),行选择电路11和列选择电路12向选择存储单元mc施加具有与写入脉冲或者读取脉冲的极性反转的极性的恢复脉冲(s52)。

184.在s52的处理之后,行选择电路11和列选择电路12向选择存储单元mc施加写入脉冲或者读取脉冲(s53)。

185.在所接收到的命令不为满足条件a的写入命令、和读取命令的任何命令的情况下(s51;否),控制电路18判定所接收到的命令是否为满足条件b的写入命令(s54)。

186.在所接收到的命令为满足条件b的写入命令的情况下(s54;是),行选择电路11和列选择电路12向选择存储单元mc施加写入脉冲(s55)。

187.在s55的处理之后,行选择电路11和列选择电路12向选择存储单元mc施加具有与写入脉冲的极性反转的极性的恢复脉冲(s56)。

188.在s53的处理之后、s56的处理之后或者所接收到的命令不是满足条件b的写入命令的情况下(s54;否),存储器件2中的一系列动作成为结束(结束)。

189.4.2第4实施方式涉及的效果

190.根据第4实施方式,存储器件2在数据“0”的写入动作中,将具有互不相同的极性的电流irec_w0和iw0交替地按该顺序施加于选择存储单元mc。存储器件2在数据“1”的写入动作中,将具有互不相同的极性的电流iw1和irec_w1交替地按该顺序施加于选择存储单元mc。存储器件2在读取动作中,将具有互不相同的极性的电流irec_r和ir交替地按该顺序施加于选择存储单元mc。由此,与第3实施方式同样地,即使是在连续地执行数据“0”的写入动作或者读取动作和数据“1”的写入动作的情况下,也能够通过具有互不相同的极性的两个信号使选择存储单元mc内的开关元件sw交替地为导通状态。因此能够抑制开关元件sw的耐久性的劣化。

191.5.第5实施方式

192.接着,对第5实施方式进行说明。第5实施方式在写入动作和读取动作以外的动作中施加恢复脉冲这一点与第1实施方式~第4实施方式不同。在以下中,主要对与第1实施方式~第4实施方式不同的构成和动作进行说明。关于与第1实施方式~第4实施方式同等的构成和动作,适当省略说明。

193.5.1存储控制器的构成

194.图23是表示第5实施方式涉及的存储控制器的构成的一个例子的框图。存储控制器3存储正选择数3a和负选择数3b。

195.正选择数3a是在存储单元阵列10内的多个存储单元mc的选择时使用了具有正极性的脉冲的次数。更具体而言,正选择数3a是数据“0”的写入动作和读取动作的总数。

196.负选择数3b是在存储单元阵列10内的多个存储单元mc的选择时使用了具有负极性的脉冲的次数。更具体而言,负选择数3b是数据“1”的写入动作的总数。

197.存储控制器3例如按存储单元阵列10内的预定的存储区域而对正选择数3a和负选择数3b进行管理。由此,存储控制器3能够掌握为了使开关元件sw为导通状态而使用了的脉冲的极性的偏倚(不均)。

198.此外,正选择数3a和负选择数3b之和是写入动作和读取动作的总数。由此,存储控制器3能够掌握将开关元件sw设为了导通状态的次数的总数。

199.5.2存储控制器的动作(流程图)

200.图24是表示第5实施方式涉及的存储控制器中的一系列动作的一个例子的流程图。

201.当从外部的主机设备接收到写入数据之意的要求或者读出数据之意的要求时(开始),存储控制器3向存储器件2发送写入命令或者读取命令(s51)。

202.存储控制器3判定与写入命令对应的写入脉冲或者与读取命令对应的读取脉冲的极性是否为正(s52)。

203.在写入脉冲或者读取脉冲的极性为正的情况下(s52;是),存储控制器3使正选择数3a递增(s53)。具体而言,在发送了指示执行数据“0”的写入动作的写入命令或者读取命令的情况下,存储控制器3使正选择数3a递增。

204.在写入脉冲或者读取脉冲的极性为负的情况下(s52;是),存储控制器3使负选择数3b进行递增(s54)。具体而言,在发送了指示执行数据“1”的写入动作的写入命令的情况下,存储控制器3使负选择数3b进行递增。

205.在s53的处理之后或者s54的处理之后,存储控制器3判定正选择数3a与负选择数3b之差是否为阈值以上(s55)。阈值为正整数。

206.在正选择数3a与负选择数3b之差为阈值以上的情况是(s55;是),存储控制器3发送刷新命令(s56)。刷新命令是对存储器件2指示执行刷新动作的命令。刷新动作是用于对与使开关元件sw为导通状态时所使用的脉冲的极性的偏倚相伴的开关元件sw的耐久性的劣化进行抑制的动作。

207.在s56的处理之后,存储控制器3将正选择数3a和负选择数3b复位为“0”(s57)。

208.在正选择数3a与负选择数3b之差小于阈值的情况下(s55;否)或者在s57的处理之后,存储控制器3中的一系列动作成为结束(结束)。

209.5.3存储器件的动作(时序图)

210.图25是表示第5实施方式涉及的存储器件中的刷新动作的一个例子的时序图。在图25中示出基于来自存储控制器3的刷新命令而施加于选择存储单元mc的电流信号。

211.当接收到刷新命令时,存储器件2执行刷新动作。具体而言,选择存储单元mc内的开关元件sw通过被施加电压vrec_p(未图示)而成为导通状态。由此,在整个期间drec_p对选择存储单元mc施加写入电流irec_p。之后,选择存储单元mc内的开关元件sw通过被施加电压vrec_n(未图示)而成为导通状态。由此,在整个期间drec_n对选择存储单元mc施加电流irec_n。期间drec_p与期间drec_n之间的期间可以设为任意长度。相对于写入电流irec_p具有正极性,电流irec_n具有负极性。

212.电流irec_p和irec_n各自比写入电流iw0和iw1小。电流irec_p和irec_n各自也可以比读出电流ir小。电流irec_p和irec_n也可以彼此相等。电流irec_p和irec_n也可以互不相同。

213.期间drec_p和drec_n各自比期间dw0和dw1短。期间drec_p和drec_n各自也可以比期间dr短。期间drec_p和drec_n也可以相互相等。期间drec_p和drec_n也可以互不相同。

214.另外,电压vrec_p和vrec_n各自比写入电压vw0和vw1小。电压vrec_n和vrec_p各自也可以比读出电压vr小。电压vrec_p和vrec_n也可以彼此相等。电压vrec_p和vrec_n也可以互不相同。

215.此外,在图25中示出了在刷新动作中在整个期间drec_p施加了写入电流irec_p之后、在整个期间drec_n施加电流irec_n的情况,但不限于此。例如,也可以在刷新动作中,在整个期间drec_n施加了写入电流irec_n之后,在整个期间drec_p施加电流irec_p。

216.5.4第5实施方式涉及的效果

217.根据第5实施方式,当接收到刷新命令时,存储器件2执行刷新动作。在刷新动作中,存储器件2交替地施加具有互不相同的极性的电流irec_p和irec_n。由此,能够与在写入动作和读取动作中是否施加恢复脉冲无关地,执行通过具有互不相同的极性的两个信号使选择存储单元mc内的开关元件sw交替地为导通状态的动作。因此,能够缓和与使开关元件sw为导通状态的信号的极性的偏倚相伴的开关元件sw的特性的劣化。

218.另外,在正选择数3a与负选择数3b之差为阈值以上的情况下,存储控制器3向存储器件2发送刷新命令。由此,存储控制器3能够在使开关元件sw为导通状态的信号的极性的偏倚变得显著之前,定期地对存储器件2指示执行刷新动作。因此,能够抑制开关元件sw的耐久性的劣化。

219.5.5第5实施方式的变形例

220.此外,在上述的第5实施方式中,对基于正选择数3a与负选择数3b之差来判定是否执行刷新动作的情况进行了说明,但不限于此。例如,也可以基于写入动作和读取动作的总数来判定是否执行刷新动作。

221.5.5.1存储控制器的动作(流程图)

222.图26是表示第5实施方式的变形例涉及的存储控制器中的一系列动作的一个例子的流程图。

223.当从外部的主机设备接收到写入或者读出数据之意的要求时(开始),存储控制器3向存储器件2发送写入命令或者读取命令(s61)。

224.存储控制器3使写入动作和读取动作的总数进行递增(s62)。

225.存储控制器3判定写入动作和读取动作的总数是否为阈值以上(s63)。阈值为正整数。

226.在写入动作和读取动作的总数为阈值以上的情况下(s63;是),存储控制器3发送刷新命令(s64)。

227.存储控制器3将写入动作和读取动作的总数复位为“0”(s65)。

228.在写入动作和读取动作的总数小于阈值的情况下(s63;否)或者在s65的处理之后,存储控制器3中的一系列动作成为结束(结束)。

229.5.5.2第5实施方式的变形例涉及的效果

230.根据第5实施方式的变形例,在写入动作和读取动作的总数为阈值以上的情况下,存储控制器3向存储器件2发送刷新命令。由此,与第5实施方式同样地,存储控制器3能够在使开关元件sw为导通状态的信号的极性的偏倚变得显著之前,定期地对存储器件2指示执行刷新动作。因此,能够抑制开关元件sw的耐久性的劣化。

231.6.其他

232.在上述的第1实施方式~第5实施方式中,以对如mram那样的磁存储器件应用恢复脉冲的情况为例进行了说明,但不限于此。例如,对与mram同样的阻变存储器、例如pcram(phase-change randomaccess memory,相变随机访问存储器)和reram(resistive random access memory,电阻型随机访问存储器)等的阻变存储器也可以应用恢复脉冲。

233.在pcram和reram等的阻变存储器中,在写入动作时被施加于阻变元件se的脉冲的极性不根据数据而变化。在以下中,说明对pcram应用恢复脉冲的情况来作为一个例子。

234.恢复脉冲也可以相对于写入脉冲而被以与第1实施方式同样的顺序进行施加。图27和图28是表示其他变形例涉及的存储器件中的写入动作的一个例子的时序图。图27和图28分别与第1实施方式中的图5和图6对应。

235.在写入数据“0”的情况下,选择存储单元mc内的开关元件sw通过被施加写入电压vw0’(未图示)而成为导通状态。由此,在整个期间dw0’对选择存储单元mc施加写入电流iw0’。之后,选择存储单元mc内的开关元件sw通过被施加电压vrec_w0’(未图示)而成为导通状态。由此,在整个期间drec_w0’对选择存储单元mc施加电流irec_w0’。期间dw0’与期间drec_w0’之间的期间可以设为任意长度。相对于写入电流iw0’具有正极性,电流irec_w0’具有负极性。

236.在写入数据“1”的情况下,选择存储单元mc内的开关元件sw通过被施加写入电压vw1’(未图示)而成为导通状态。由此,在整个期间dw1’对选择存储单元mc施加写入电流iw1’。之后,选择存储单元mc内的开关元件sw通过被施加电压vrec_w1’(未图示)而成为导通状态。由此,在整个期间drec_w1’对选择存储单元mc施加电流irec_w1’。期间dw1’与期间drec_w1’之间的期间可以设为任意长度。写入电流iw1’比写入电流iw0’大,并且,具有与写入电流iw0’相同的极性。期间dw1’比期间dw0’短。相对于写入电流iw1’具有正极性,电流irec_w1’具有负极性。

237.读出数据的情况下的动作与第1实施方式中的图7是同等的。

238.另外,恢复脉冲也可以相对于写入脉冲而被以与第2实施方式同样的顺序进行施加。图29和图30是表示其他变形例涉及的存储器件中的写入动作的一个例子的时序图。图29和图30分别与第2实施方式中的图13和图14对应。

239.也可以在写入数据“0”的情况下,在整个期间drec_w0’对选择存储单元mc施加电流irec_w0’之后,在整个期间dw0’对选择存储单元mc施加写入电流iw0’。

240.也可以在写入数据“1”的情况下,在整个期间drec_w1’对选择存储单元mc施加了电流irec_w1’之后,在整个期间dw1’对选择存储单元mc施加写入电流iw1’。

241.在该情况下,读出数据的情况下的动作与第2实施方式中的图14是同等的。

242.此外,电流irec_w0’和irec_w1’各自比写入电流iw0’和iw1’小。电流irec_w0’和irec_w1’各自也可以比读出电流ir小。电流irec_w0’和irec_w1也可以彼此相等。电流irec_w0’和irec_w1’也可以互不相同。

243.期间drec_w0’和drec_w1’各自比期间dw0’和dw1’短。期间drec_w0’和drec_w1’各自也可以比期间dr短。期间drec_w0’和drec_w1’也可以相互相等。期间drec_w0’和drec_w1’也可以互不相同。

244.另外,电压vrec_w0’和vrec_w1’各自比写入电压vw0’和vw1’小。电压vrec_w0’和vrec_w1’各自也可以比读出电压vr小。电压vrec_w0’和vrec_w1’也可以相互相等。电压vrec_w0’和vrec_w1’也可以互不相同。

245.通过如上所述那样进行动作,关于mram以外的阻变存储器也可以应用恢复脉冲。

246.以上对本发明的几个实施方式进行了说明,但这些实施方式是作为例子提示的,并不是意在限定发明的范围。这些新的实施方式能够以其他各种各样的方式来实施,能够在不脱离发明的宗旨的范围内进行各种省略、置换、变更。这些实施方式及其变形包含在发明的范围、宗旨内,并且,包含在权利要求书记载的发明及其等同的范围内。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。