1.本实用新型涉及用于非易失性可编程存储器的写入保护装置以及用于断路器的包括该写入保护装置的脱扣单元。

背景技术:

2.目前,在诸如电子电力领域中,电力电子设备中的各种装置的大量参数存储中非易失性存储器中,但是由于应用场景的更换、设备更新等,相关工作人员需要对非易失性存储器中参数编程以适应新的应用场景。考虑到数据用于实现电力电子设备中的各种装置的运行,如果不对存储这些参数的编程造成加以限制,可能会影响数据安全甚至影响电力电子设备的正常运行。因此,需要提出一种控制非易失性存储器的编程操作的写入保护装置,以确保诸如参数的数据在非易失性存储器中的安全性。

技术实现要素:

3.本实用新型的目的是提供一种控制对非易失性可编程存储器的参数写入的写入保护装置。

4.根据本实用新型的一方面,提供了一种用于非易失性可编程存储器的写入保护装置,其特征在于,写入保护装置包括:信号接收单元,连接至参数写入装置,用于从参数写入装置接收脉冲信号,参数写入装置用于向非易失性可编程存储器写入参数;以及电平生成单元,与信号接收单元连接,用于基于脉冲信号生成存储器写入使能电平,并且在未接收到脉冲信号的情况下生成存储器写入禁用电平;电平输出单元,连接至电平生成单元和非易失性可编程存储器,用于将存储器写入使能电平或存储器写入禁用电平输出到非易失性可编程存储器。

5.可选地,电平生成单元包括含有第一限流电阻、第二限流电阻和储能电容的充放电单元,第一限流电阻的第一端连接至信号接收单元的输出端,第二限流电阻与储能电容并联连接,第二限流电阻与储能电容并联连接的第一节点连接至第一限流电阻的第二端并且作为充放电单元的输出端,从而输出第一电平,并且第二限流电阻与储能电容并联连接的第二节点连接至地。

6.可选地,储能电容由并联连接的多个电容器构成。

7.可选地,信号接收单元包括反向保护单元,反向保护单元具有用于实现单向导通的器件,以用于避免反向电流。

8.可选地,单向导通器件包括二极管,具有用于接收脉冲信号的阳极以及作为信号接收单元的输出端的阴极。

9.可选地,电平生成单元包括用于实现电平反向的电平转换单元,电平转换单元连接至充放电单元的输出端。

10.可选地,电平转换单元包括可控型器件,可控型器件包括:第一极,连接至第一节点,用于基于来自第一节点的第一电平控制可控型器件通断;第二极,连接至直流电压源,

或者“包含”等类似的词语意指出现该词前面的元件或者物件涵盖出现在该词后面列举的元件或者物件及其等同,而不排除其他元件或者物件。“耦接”、“连接”或者“相连”等类似的词语并非限定于物理的或者机械的连接,而是可以包括电性的连接,不管是直接的还是间接的。“上”、“下”、“左”、“右”等仅用于表示相对位置关系,当被描述对象的绝对位置改变后,则该相对位置关系也可能相应地改变。

23.为了便于讨论写入保护装置,以电力电子设备的断路器中的脱扣单元为例进行讨论。在最基本最简单的脱扣单元中,通常不设置非易失性可编程存储器,并且只能借助于若干旋钮来调节特定的参数,例如,在基本脱扣单元中仅可以利用三个旋钮来编辑三个参数。然而,在实际应用中,脱扣单元的脱扣曲线存在大量的参数需要调整、诸如长延时(例如,s的量级)、短延时 (例如,ms的量级)、瞬态的保护电流值、脱扣时间的设定及微调等。在这种情况下,提出了一种脱扣单元,包括微控制处理器、液晶显示器、非易失性可编程存储器,并且通过微控制处理器来选择性地控制非易失性可编程存储器的写入状态。虽然包含微控制处理器的脱扣单元可以选择性编辑所有的参数,但是脱扣单元由于选用了复杂微控制处理器导致电子组件的成本较高。为了实现对所有参数的编辑的控制并且降低成本,本实用新型通过参数写入装置和写入保护装置而无需微控制处理器和液晶显示器就可以受控地编写存储在非易失性可编程存储器中的所有参数。

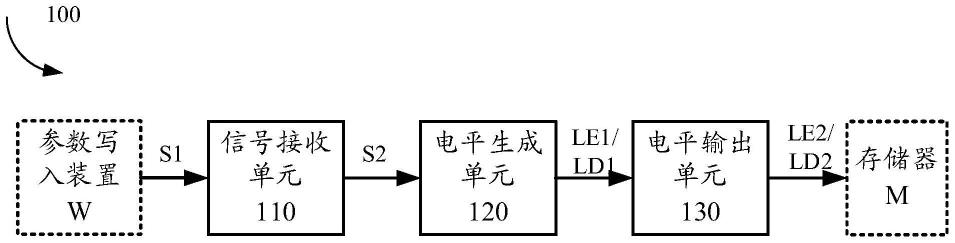

24.图1示出了根据本实用新型的一个实施例的用于非易失性可编程存储器m的写入保护装置100的示意图。写入保护装置包括信号接收单元110、电平生成单元120和电平输出单元130。信号接收单元110与参数写入装置w 连接,并且电平输出单元与非易失性存储器m连接。

25.信号接收单元110可以连接至参数写入装置w,用于从参数写入装置 w接收脉冲信号s1,参数写入装置w用于向非易失性可编程存储器m写入参数。信号接收单元110用于接收脉冲信号s1。在一些示例中,信号接收单元110可以配置为导线,以直接传输脉冲信号s1。在一些示例中,信号接收单元110还可以配置为对接收到的脉冲信号s1进一步处理,以向电平生成单元120发送处理过的脉冲信号s2。在一些示例中,信号接收单元 110包括反向保护单元(图中未示出),反向保护单元具有用于实现单向导通的器件,以用于避免反向电流。在一些示例中,单向导通器件可以包括二极管。例如,二极管具有用于接收脉冲信号s1的阳极以及作为信号接收单元110的输出端的阴极。

26.例如,在使用脱扣器的情况下,参数写入装置w可以是断路器测试装置或断路器测试模块用于写入脱扣曲线的所有参数。具体地,参数写入装置 w与主机(未示出)接口连接并且从主机接收写入指令向存储器m写入参数。具体地,在要对存储器m编程时,参数写入装置w的特定管脚会向信号接收单元110发送脉冲信号s1;在不对存储器m编程或参数写入装置w 未连接到写入保护装置100时,信号接收单元110仅接收到低电平信号或地信号。参数写入装置w可选地外置于所述写入保护装置100。替代地,参数写入装置w也可以包括在写入保护装置100内。本实用新型对此不做限制。

27.电平生成单元120可以连接至信号接收单元110,用于基于脉冲信号s1 或s2生成存储器写入使能电平le1,并且在未接收到脉冲信号s1或s2的情况下生成存储器写入禁用电平ld1。

28.电平输出单元130可以连接至电平生成单元120和非易失性可编程存储器m,用于

将存储器写入使能电平le1/le2或存储器写入禁用电平 ld1/ld2输出到非易失性可编程存储器。在一些示例中,信号输出单元130 可以配置为导线,以直接存储器写入使能电平或禁用电平le1/ld1。在一些示例中,信号输出单元130还可以配置为对接收到的存储器写入使能电平 le1或禁用电平ld1进一步处理,以向存储器传输经处理的存储器写入使能电平或禁用电平le2/ld2。在一些示例中,电平输出单元130包括滤波单元,用于过滤存储器写入使能电平或禁用电平中的低频噪声,以降低甚至消除周围环境对电平信号的干扰,从而更加可靠地使能/禁用存储器m的写入操作。

29.在一些示例中,非易失性可编程存储器m可以是指掉电后不易丢失的存储器芯片且可以具有写入有效和写入无效两种模式,诸如只读模式和读写模式两者。在一些示例中,非易失性可编程存储器m可以包括可编程存储器(prom)、可擦可编程只读存储器(eprom)、带电可擦可编程只读存储器(eeprom)、闪速存储器(flash)或诸如此类。非易失性可编程存储器m具有写入保护管脚,用于基于写入使能电平或写入禁用电平来设定写入/编程操作是否有效。

30.根据本实用新型描述的各个实施例借助于参数写入装置w并通过简单地设置独立的写入保护装置100来切换非易失性可编程存储器的写入是否有效的两个状态。特别是,研究人员发现,诸如断路器测试模块btm的参数写入装置w可以选用管脚(例如,pin3),该管脚可以实现在向非易失性可编程存储器m写入参数时输出脉冲信号s1。因此,借助于参数写入装置可以有效地避免非易失性可编程存储器总是处于写入有效的状态,从而避免非易失性可编程存储器中的数据可能受到外部干扰而产生错误造成诸如脱扣单元的电力电子设备无法运行的后果。在此基础上,本实用新型的各个实施例借助于参数写入装置来控制向非易失性可编程存储器写入参数,可以实现更低成本、更简单的电路设计来确保非易失性可编程存储器中的参数的更高的安全性,从而对非易失性可编程存储器进行写入保护。

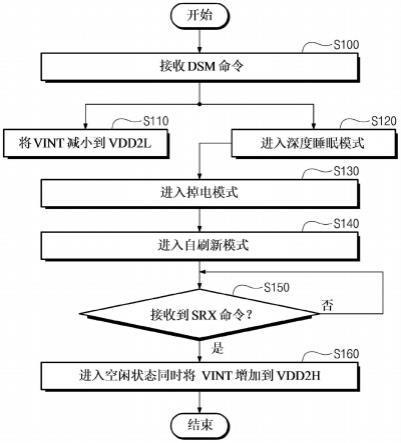

31.图2示出了根据本实用新型的一个实施例的写入保护装置100中的电平生成单元120的三个实施例(a)、(b)、(c)的示意图。在一些示例中,电平生成单元120可以包括充放电单元122,如图3的(a)所示。在一些示例中,电平生成单元120可以包括充放电单元122和电平转换单元124,如图 3的(b)所示。在一些示例中,电平生成单元120还可以依次包括充放电单元122、过压保护单元126和电平转换单元124,如图3的(c)所示。

32.例如,在不具有电平转换单元124的情况下,当充放电单元122从信号接收单元110接收脉冲信号s1/s2时,充放电单元122生成存储器写入使能电平。当充放电单元122没有接收到脉冲信号时,充放电单元122生成存储器写入禁用电平。在一些示例中,在具有电平转换单元124的情况下,充放电单元122可以用于将来自信号接收单元110的脉冲信号s1/s2经由限流电流和储能电容的配合来生成与存储器写入使能电平或存储器写入禁用电平对应的第一电平,从而达到负载平衡。例如,文中的存储器写入使能电平可以是持续的高电平或低电平。在一些示例中,充放电单元122通过储能电容和限流电阻的组合将脉冲信号转换为电平信号,特别是经由储能电容不断充电而形成持续的高电平。在具有过压保护单元126的情况下,充放电单元122 中的储能电容和限流电流的组合可以将电平信号稳定在特定电平值,该特定电平值取决于过压保护单元126中的稳压二极管的值。在该情况下,电平信号的幅值不大于稳压二极管的最大稳压值。由于漏电流或环境温度的存在,可以通过稳压二极管和充放电单元的组合来稳定高电平的幅值以减少电平幅值的波动。经调整的电平幅值应

大于诸如mosfet晶体管的可控型器件q1 的门极的驱动电压阈值。本文中。脉冲信号是指具有一定占空比的周期性矩形方波。在一些实施例中,理想情况下,脉冲信号的占空比至少为 1/20,000。在一些示例中,特别是在考虑到电子器件的漏电流、环境温度等影响且脉宽由此展宽的情况下,脉冲信号的占空比至少为1/20,特别地至少为1/10。

33.在一些示例中,电平转换单元124可以用于实现电平反向以将由充放电单元122生成的第一电平转换为使能或禁用电平,以符合使非易失性可编程存储器m使能或禁用写入的电平状态。在一些示例中,电平转换单元124 可以利用反相器来实现。在一些示例中,电平可以利用可控型器件来实现,特别是可控型器件的控制极接收由充放电单元生成的第一电平并且用于基于该第一电平控制可控型器件的通断,在可控型器件导通的情况下,电平转换单元输出存储器写入使能电平,另外,在可控型器件关断的情况下,电平转换单元输出存储器写入禁用电平。在一些示例中,可控型器件可以是控制导通的晶体管。例如,可控型器件可以是金属氧化物半导体场效应管 (mosfet)、绝缘栅双极型晶体管(igbt)、互补金属氧化物半导体 (cmos)、三极管等。

34.在一些示例中,过压保护单元126可以用于限幅由充放电单元122生成的第一电平,以避免过高的电压可能会损坏电平转换单元124中的电子器件,特别是可控型器件。

35.图3示出了根据本实用新型的另一个实施例的写入保护装置400的电路图。图3的写入保护装置300、信号输入单元310、充放电单元322、过压保护单元326、电平转换单元324、信号输出单元330与图1和图2中的写入保护装置100、信号输入单元310、充放电单元122、过压保护单元126、电平转换单元124、信号输出单元130对应,上文描述同样可以使用到图3 的结构。

36.如图3所示,信号接收单元310可以是二极管。二极管具有用于接收脉冲信号s1的阳极以及作为信号输入单元310的输出端的阴极。脉冲信号s1 可以是由参数写入装置w(图3中未示出)在向存储器m写入参数时输入。

37.在一些示例中,充放电单元322可以包括第一限流电阻r1、第二限流电阻r2和储能电容c1、c2、c3。第一限流电阻r1的第一端连接至二极管 d1的输出端。第二限流电阻r2可以与储能电容c1、c2、c3并联连接,第二限流电阻r2与储能电容c1、c2、c3并联连接的第一节点n1连接至第一限流电阻r1的第二端并且作为充放电单元322的输出端,从而输出第一电平,并且第二限流电阻r2与储能电容c1、c2、c3并联连接的第二节点 n2连接至地。例如,储能电容c1、c2、c3由并联连接的多个电容器构成,如图所示为3个,但是附图中所述的储能电容仅是示意性的,还可以存在其他可能的电容数量。替代地,储能电容也可以由单个电容构成。

38.电平转换单元326包括可控型器件q1,可控型器件q1包括第一极、第二极和第三极。第一极连接至第一节点n1,用于基于来自第一节点n1的第一电平控制可控型器件q1通断。第二极连接至直流电压源vdd,用于在可控型器件q1导通的情况下,输出存储器写入使能电平le,并且在可控型器件q1关断的情况下,输出存储器写入禁用电平ld。并且第三极连接至地。可选地,第二极经由电阻r3连接至直流电压源vdd。例如,可控型器件q1可以是晶体管,例如如前文所述的mosfet,特别是n型 mosfet。例如,当第一节点n1的输入控制信号为高电平时,mosfet q1 的栅极接收到高电平使得mosfet q1导通,将漏极的输出电平下拉至与地信号相关联的低电平。另外,当第一节点n1的输入控制信号为低电平时, mosfet q1的栅极接收到低电平使得mosfet q1关断,将漏极的输出电平上拉下拉至与直流电源信号vdd

相关联的高电平。在该情况下,写入存储器使能电平是低电平,并且写入存储器禁用电平是高电平。

39.在一些示例中,过压保护单元326包括稳压二极管z1。稳压二极管z1 与储能电容c1、c2、c3并联。也就是说,稳压二极管z1的阴极连接至可控型器件q1的第一极并且其阳极连接至地。在一些示例中,稳压二极管还可以与电容c4并联。该电容c4有助于进一步吸收多余高频能量,以进一步保护可控型器件q1以避免充放电模块生成的过高电压幅值施加在可控型器件q1的控制极以对器件造成损坏,并且减低干扰。

40.在一些示例中,电平输出单元320中的滤波单元包括滤波电阻r4和滤波电容c5。滤波电阻r4的第一端连接至电平生成单元324的输出端,即可控型器件q1的第二极。并且滤波电阻r4的第二端连接至非易失性可编程存储器m并且经由滤波电容c5连接至地。通过滤波电阻r4和滤波电容c5 的组合可以对由电平生成单元120输出的使能/禁用电平进行滤波,以避免噪声干扰。信号噪声可以包括背景噪声、环境噪声等,从而确保输入到非易失性可编程存储器m的电平更加稳定。滤波电阻r4和滤波电容c5的具体数值可以取决于干扰程度来进行调节,本技术对此不做限制。

41.图4示出了图3所示的写入保护装置300中各个测试点的波形示意图。图4分别示出了图3中的写入保护装置300中信号输入的第一测试点p1、位于二极管d1的第二端处的第二测试点p2、位于第一节点处的第三测试点 p3以及位于可控型器件q1的第二极处的第四测试点p4的波形图。该波形图可以是经由仿真软件获得。

42.从图4中可以看到,在写入保护阶段(t《t1),参数写入装置w没有输入脉冲信号,此时第一测试点p1保持低电平。对应地,第二测试点p2和第三测试点p3均为低电平,然后经由电平转换单元424后,第四测试点p4获得存储器写入禁用电平,即高电平。

43.在写入阶段(t1≤t),参数写入装置w输出连续的脉冲信号s1,即第一测试点获得连续脉冲信号。对应地,第二测试点p2是经由信号接收单元 410生成的第二脉冲信号s2。第二脉冲信号s2的幅值和接收到的脉冲信号 s1的幅值之差为二极管d1的导通压降。第三测试点p3经由充放电电路中储能电容和限流负载快速趋于平衡以在t3时刻稳定在高电平处。并且,由此生成的高电平幅值较为稳定,波动较小。然后经由电平转换单元424后,第四测试点p4在t2时刻跳变为存储器写入使能电平,即低电平。注意到t2 时刻为检测到p3的高电平幅值达到可控型器件q1的导通阈值的时刻。并且t2时刻早于t3时刻,这意味着不需要等待充放电模块的储能负载完全平衡后才能生成适用于存储器写入保护管脚的电平,而是在检测到的p3的高电平幅值达到可控型器件q1的导通阈值时就能生成写入存储器使能电平,如低电平。同样,电平的快速转换可以实现更加高效的写入编程操作。上述储能和负载的平衡过程适用于比较宽的脉宽,以在较短的时间内快速获得存储器写入使能电平来实现写入操作。该时间通常在ms量级。例如,为了使储能和负载较快地趋于平衡,脉冲的占空比不低于为1/20,例如脉冲的周期为20ms,脉冲的脉宽为1ms。

44.图5示出了根据本实用新型的一个实施例的脱扣单元50的示意图。如图5所示,脱扣单元50用于执行脱扣操作以保护断路器。脱扣单元包括:如前文所述的写入保护装置500,用于保护对非易失性可编程存储器的写入操作;参数写入装置w,连接至写入保护装置500且主机h,用于向写入保护装置500输入用于向非易失性可编程存储器m写入参数的脉冲信号s1;以及非易失性可编程存储器m,连接至写入保护装置500,用于从写入保护装置500

基于参数写入装置w接收存储器写入使能电平或存储器写入禁用电平。图5中的写入保护装置500可以与图1和图2中所述的写入保护装置 100以及图3中的写入保护装置400对应,上文具体描述。参数写入保护装置w可以与主机接口连接,以接收主机对存储器m的写入命令来执行对存储器m的写入或编程操作,参数写入保护装置w、存储器m可以参考上文中关于对应装置或存储器的具体描述,上文描述同样适用于图5的脱扣单元 50中的写入保护装置500。

45.主机h可以是可以执行各种编程、写入、读取等操作的处理器。本实用新型所描述的处理器、控制系统、控制电路等硬件配置可以通过各种合适的硬件手段实现,包括但不限于fpga、asic、soc、离散门或晶体管逻辑、离散的硬件组件、或它们之间的任意组合。

46.本实用新型中涉及的电路、器件、装置、设备、系统的方框图仅作为示例性的例子并不意图要求或暗示必须按照方框图示出的方式进行连接、布置、配置。如本领域技术人员将认识到的,可以按任意方式连接、布置、配置这些电路、器件、装置、设备、系统,只要能够实现所期望的目的即可。

47.本领域技术人员应该理解,上述的具体实施例仅是例子而非限制,可以根据设计需求和其它因素对本实用新型的实施例进行各种修改、组合、部分组合和替换,只要它们在所附权利要求或其等同的范围内,即属于本实用新型所要保护的权利范围。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。